# SEMTECH

# SC420A High Speed, Combi-Sense<sup>™</sup>, Synchronous Power MOSFET Driver for Mobile Applications

## POWER MANAGEMENT

#### Description

The SC420A is a cost effective Dual MOSFET Driver, incorporating Semtech's patented Combi-Sense<sup>™</sup> technology, designed for switching High and Low side Power MOSFETs in Step-down Switching regulators. A 30ns max propagation delay from input transition to the gate of the power FET's guarantees operation at high switching frequencies. Internal overlap protection circuit prevents shoot-through from Vin to GND in the main and synchronous MOSFETs.

High current drive capability allows fast switching, thus reducing switching losses at high frequencies without causing thermal stress on the driver.

The high voltage CMOS process allows operation up to 27 Volts, making the SC420A suitable for adaptor powered applications. Under-voltage-lockout and over-temperature shutdown features are included for proper and safe operation. The SC420A is offered in a space saving MLP-12 package.

## Features

- High efficiency

- Shutdown mode for increased power saving

- Fast rise and fall times (10ns typical with 3000pF load)

- 5V gate drive

- Ultra-low (<30ns) propagation delay (BG going low)</li>

- Adaptive and programmable non-overlapping gate drives provide shoot-through protection

- Floating top drive switches up to 27V

- High frequency operation allows use of small inductors and low cost ceramic capacitors

- ♦ Under-voltage lockout

- ◆ Low quiescent current

- MLP packaging provides superior thermal performance in a small footprint

## Applications

- ◆ High efficiency portable and notebook computers

- Battery powered applications

#### evision Anril 1 2004

# Absolute Maximum Ratings

Exceeding the specifications below may result in permanent damage to the device, or device malfunction. Operation outside of the parameters specified in the Electrical Characteristics section is not implied.

| Parameter                                             | Symbol                | Conditions                           | Min       | Max       | Units |

|-------------------------------------------------------|-----------------------|--------------------------------------|-----------|-----------|-------|

| VIN2 Supply Voltage                                   | VIN2                  |                                      |           | 30        | V     |

| BST to PGND                                           |                       |                                      |           | 40        | V     |

| BST to DRN                                            |                       |                                      |           | VIN + 2   | V     |

| DRN to PGND                                           |                       | t <sub>PULSE</sub> <100ns            | - 5       | 34        | V     |

|                                                       |                       | static                               | - 2       | 30        |       |

| TG                                                    |                       |                                      | DRN - 0.3 | BST + 0.3 | V     |

| BG                                                    |                       |                                      | - 0.3     | VIN + 0.3 | V     |

| VPN to PGND                                           | VPN                   |                                      |           | 30        | V     |

| VIN to PGND                                           | VIN                   |                                      |           | 7         | V     |

| EN, CO, CDELAY                                        |                       |                                      | - 0.3     | VIN + 0.3 | V     |

| Continuous Power Dissipation                          | P <sub>D</sub>        | Tamb = 25 °C,T <sub>J</sub> = 125 °C |           | 0.66      | W     |

|                                                       |                       | Tcase = 25 °C, $T_J = 125$ °C        |           | 2.56      |       |

| Thermal Resistance Junction to Case                   | $\theta^{\text{JC}}$  |                                      |           | 3         | °C/W  |

| Thermal Resistance Junction to Ambient <sup>(1)</sup> | $\theta_{JA}$         |                                      |           | 48        | °C/W  |

| Operating Junction Temperature<br>Range               | TJ                    |                                      | - 40      | 125       | °C    |

| Storange Temperature Range                            | T <sub>stg</sub>      |                                      | - 65      | 150       | °C    |

| Peak IR Reflow (10 - 40 sec)                          | T <sub>IRreflow</sub> |                                      |           | 260       | °C    |

Note:

(1) Performance when used according to manufacturing guidelines, refer to Applications Information section for more information

#### Electrical Characteristics

Unless specified:  $-40^{\circ}C \le T_{\downarrow} \le 125^{\circ}C$ ;  $V_{\downarrow\nu} = 5V$ ;  $0V \le V_{DRN} \le 25V$

| Parameter                             | Symbol                      | Conditions            | Min  | Тур | Max | Units |  |

|---------------------------------------|-----------------------------|-----------------------|------|-----|-----|-------|--|

| Power Supply                          |                             |                       |      |     |     |       |  |

| Supply Voltage                        | VIN                         |                       | 4.75 | 5   | 6   | V     |  |

|                                       | VIN2                        |                       |      |     | 27  | V     |  |

| Quiescent Current, Operating (static) | $IQ_{op}$                   | CO = 0V, EN ><br>2.2V |      | 2.3 |     | mA    |  |

| Quiescent Current, Shutdown           | $\mathrm{IQ}_{\mathrm{sd}}$ | CO = 0V, EN = 0V      |      | 0.2 | 20  | μA    |  |

# Electrical Characteristics (Cont.)

Unless specified: -40°C  $\leq$  T<sub>J</sub> $\leq$  125°C; V<sub>IN</sub> = 5V; 0V  $\leq$  V<sub>DRN</sub> $\leq$  25V

| Parameter                           | Symbol               |              | Conditions                 | Min | Тур | Мах  | Units |

|-------------------------------------|----------------------|--------------|----------------------------|-----|-----|------|-------|

| Under Voltage Lockout               |                      |              |                            |     |     |      | L     |

| Start Threshold (ramping up)        | VIN                  |              |                            | 4.1 | 4.3 | 4.55 | V     |

| Hysteresis                          | Vhys                 |              |                            | 100 | 200 | 350  | mV    |

| Under-Voltage Lockout<br>Time Delay |                      |              |                            |     |     |      |       |

| VIN ramping up (2)                  | tpdh <sub>uvLo</sub> |              |                            |     | 2   |      | μs    |

| VIN ramping down (2)                | tpd <sub>LUVLO</sub> |              |                            |     | 2   |      | μs    |

| EN                                  | •                    |              |                            | •   | •   |      |       |

| High Level Input Voltage            | V <sub>IH</sub>      |              |                            | 2.0 |     |      | V     |

| Low Level Input Voltage             | VL                   |              |                            |     |     | 0.8  | V     |

| СО                                  |                      | ł            |                            |     |     |      | Ļ     |

| High Level Input Voltage            |                      |              |                            | 2.0 |     |      | V     |

| Low Level Input Voltage             |                      |              |                            |     |     | 0.8  | V     |

| Thermal Shutdown                    |                      |              |                            |     |     |      |       |

| Over Temperature Trip Point         | T <sub>OTP</sub>     |              |                            |     | 165 |      | °C    |

| Hysteresis (2)                      | T <sub>HYST</sub>    |              |                            |     | 10  |      | ٥C    |

| High Side Driver (TG)               |                      |              |                            |     |     |      |       |

| Peak Output Current (3)             | I <sub>РКН</sub>     |              |                            | 1.5 | 1.7 | 1.9  | А     |

| Output Resistance <sup>(3)</sup>    | R <sub>SRC_TG</sub>  | l =<br>100mA | $V_{BST}$ - $V_{DRN}$ = 5V | 1.8 | 2.2 | 2.6  | 0     |

|                                     | R <sub>SINK_TG</sub> |              | $V_{BST}$ - $V_{DRN}$ = 5V | 0.6 | 0.8 | 1.0  | Ω     |

| Rise Time <sup>(3)</sup>            | tr <sub>TG</sub>     | CL = 3nF,    | $V_{BST} - V_{DRN} = 5V$   | 12  | 16  | 20   | ns    |

| Fall Time (3)                       | tf <sub>rg</sub>     |              |                            | 10  | 14  | 18   | ns    |

## Electrical Characteristics (Cont.)

Unless specified:  $-40^{\circ}C \le T_{J} \le 125^{\circ}C$ ;  $V_{IN} = 5V$ ;  $0V \le V_{DRN} \le 25V$

| Parameter                                          | Symbol                | Conditions                     |                          | Min  | Тур | Мах  | Units |  |

|----------------------------------------------------|-----------------------|--------------------------------|--------------------------|------|-----|------|-------|--|

| Propagation Delay, TG Going<br>High <sup>(3)</sup> | tpdhTG                | CTG = 3nF,BG = 0V              |                          | 30   | 36  | 42   | ns    |  |

| Propagation Delay, TG Going Low <sup>(3)</sup>     | tpdITG                | СТ                             | G = 3nF,DRN = 0V         | 20   | 28  | 36   | ns    |  |

| Low-Side Driver (BG)                               |                       |                                |                          |      |     |      |       |  |

| Peak Output Current (3)                            | I <sub>PKL</sub>      |                                |                          | 1.8  | 2.0 | 2.2  | А     |  |

| Output Resistance (3)                              | R <sub>SRC_BG</sub>   | l = 100mA                      |                          | 1.8  | 2.2 | 2.6  | Ω     |  |

|                                                    | $R_{SINK_{BG}}$       | 1 = 100MA                      |                          | 0.55 | 0.7 | 0.95 | 52    |  |

| Rise Time <sup>(3)</sup>                           | tr <sub>BG</sub>      |                                | C <sub>BG</sub> = 3nF    | 5    | 10  | 15   | ns    |  |

| Fall Time (3)                                      | tf <sub>BG</sub>      | C <sub>BG</sub> = 3nF          |                          | 2    | 5   | 8    | ns    |  |

| Propagation Delay,BG Going<br>High <sup>(3)</sup>  | tpdh <sub>BG</sub>    | C <sub>BG</sub> =3nF, DRN = 0V |                          | 21   | 28  | 35   | ns    |  |

| Propagation Delay,BG Going Low <sup>(3)</sup>      | tpdl <sub>BG</sub>    | C <sub>BG</sub> = 3nF          |                          | 20   | 25  | 30   | ns    |  |

| Shoot-thru Protection (CDELA                       | Y)                    |                                |                          | ·    |     |      |       |  |

| Shoot-thru Protection Delay<br>Time <sup>(2)</sup> | tspd                  |                                | C <sub>CDELAY</sub> open | 15   | 20  | 30   | ns    |  |

| Programmed Delay                                   |                       |                                |                          |      | 1   |      | ns/pF |  |

| CDELAY charge current                              |                       |                                |                          | 350  | 500 | 650  | μA    |  |

| Virtual Phase Node (VPN)                           |                       |                                |                          |      |     |      |       |  |

| Output Resistance                                  | R <sub>src_vpn</sub>  |                                |                          |      | 65  |      | Ω     |  |

|                                                    | R <sub>SINK_VPN</sub> |                                |                          |      | 90  |      |       |  |

| Leakage                                            | I <sub>LEAK_VPN</sub> | V <sub>IN2</sub> =27V          |                          |      |     | 600  | nA    |  |

Notes:

(2) Guaranteed by design

(3) Temperature =  $25^{\circ}$ C

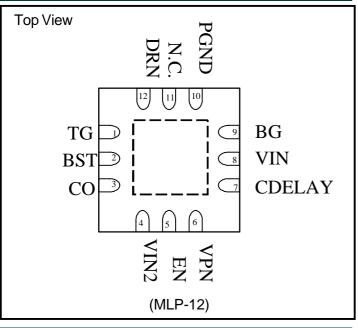

## Pin Configuration

# Ordering Information

| Device <sup>(1)</sup>       | Package | Temp Range (T <sub>.</sub> ) |  |  |

|-----------------------------|---------|------------------------------|--|--|

| SC420AIMLTRT <sup>(3)</sup> | MLP-12  | -40° to 125°C                |  |  |

Note:

(1) Only available in tape and reel packaging. A reel contains 3000 devices.

(2) This device is ESD sensitive. Use of standard ESD handling precautions is required.

(3) Lead Free package compliant with J-STD-020B. Qualified to support maximum IR reflow temperature of 260°C for 30 seconds.

#### **Pin Descriptions**

| Pin<br># | Pin<br>Name | Pin Function                                                                                                                                                                                                                     |  |  |  |

|----------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1        | TG          | Output gate drive for the switching (high-side) MOSFET.                                                                                                                                                                          |  |  |  |

| 2        | BST         | Bootstrap pin. A capacitor is connected between BST and DRN pins to develop the floating bootstrap voltage for the high-side MOSFET. The capacitor value is typically between $0.1\mu$ F and $1\mu$ F (ceramic).                 |  |  |  |

| 3        | СО          | Logic level PWM input signal to the SC420 supplied by external controller.                                                                                                                                                       |  |  |  |

| 4        | VIN2        | Input power (VBAT) to the DC/DC converter. Used as supply reference for internal Combi-Sense ™ circuitry. Connect as close as possible to Drain of TOP switching MOSFET.                                                         |  |  |  |

| 5        | EN          | Active high logic level input signal. A logic High enables TG and BG switching. A low level disables outputs and reduces quiescent current to IQ $_{\rm SD}$                                                                     |  |  |  |

| 6        | VPN         | Virtual Phase Node. Connect an RC between this pin and the output sense point to Enable Combi-<br>Sense ™operation.                                                                                                              |  |  |  |

| 7        | CDELAY      | The capacitance connected between this pin and GND sets the additional propagation delay for BG going low to TG going high. Total propagation delay =20ns + 1ns/pF. If no capacitor is connected, the propragation delay = 20ns. |  |  |  |

| 8        | VIN         | Input supply for the bottom drive and the Logic. A $1\mu$ F-10 $\mu$ F Ceramic Capacitor must be connected from this pin to PGND, placed less than 0.5" from SC420.                                                              |  |  |  |

| 9        | BG          | Output drive for the synchronous (bottom) MOSFET.                                                                                                                                                                                |  |  |  |

| 10       | PGND        | Ground. Keep this pin close to the synchronous MOSFETs source.                                                                                                                                                                   |  |  |  |

| 11       | N.C.        | No Connect                                                                                                                                                                                                                       |  |  |  |

| 12       | DRN         | This pin connects to the junction of the switching and synchronous MOSFETs . This pin can be subjected to a -2V minimum relative to PGND without affecting operation.                                                            |  |  |  |

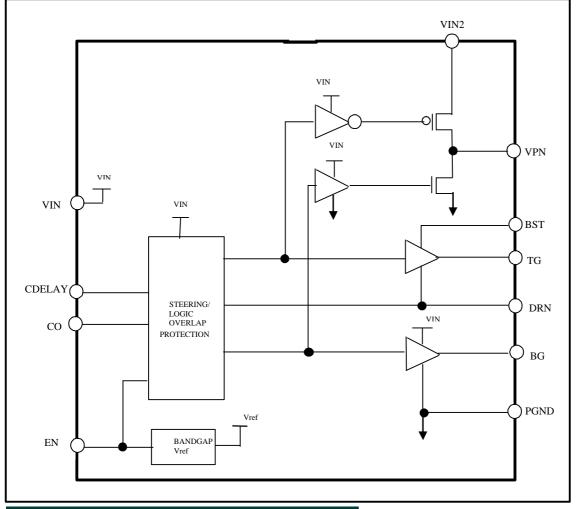

## Block Diagram

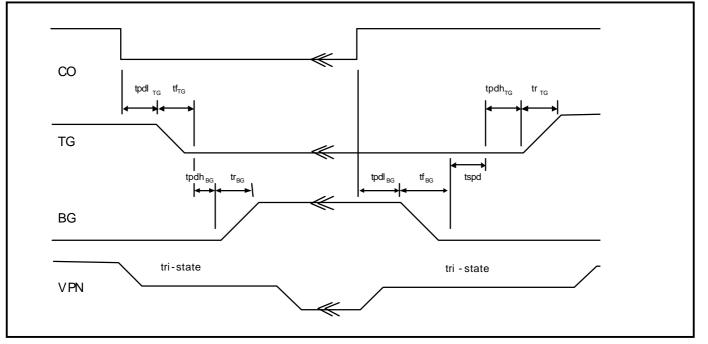

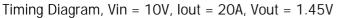

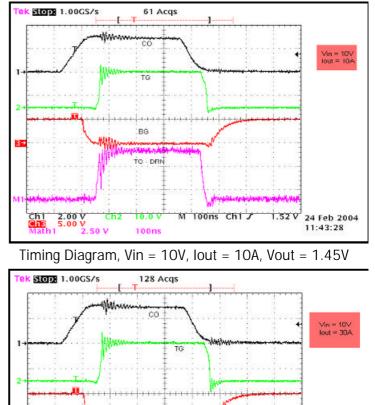

Timing Diagram

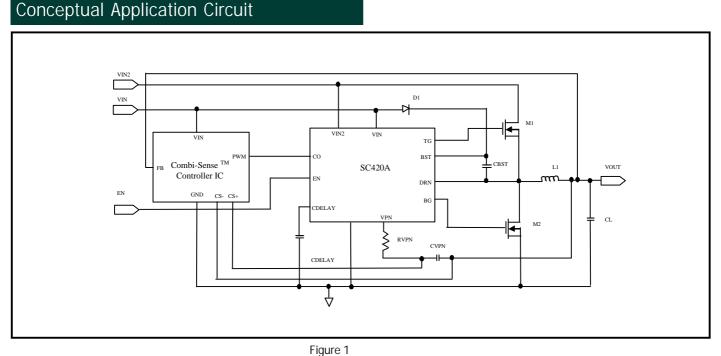

# Applications Information

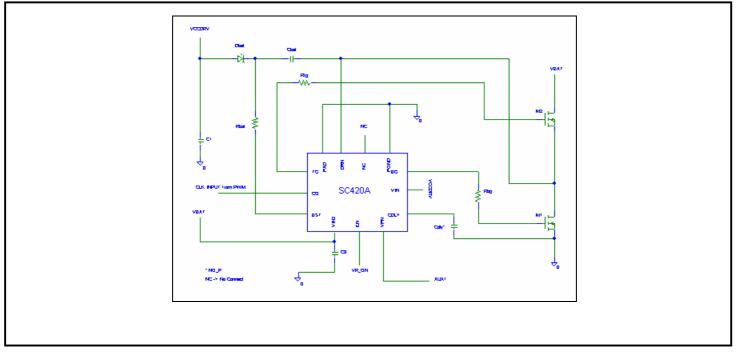

Fig 1: Typical Applications Schematic

Fig 2: Typical SC420A components

7

#### Applications Information

#### Combi-Sense (Lossless current sense)

Combi-Sense is a method to sense the output current on a combination of power devices. There is no sense resistor and the current is sensed on: Top MOSFET, bottom MOSFET and output inductor.

An internal phase node VPN sends a signal which is integrated by the Combi-Sense network. This network consists of a resistor and capacitor in series, connected between VPN and the DRN pins. The resulting signal is large, clean and not duty cycle sensitive. It can be used directly for close loop current mode control and current limit.

#### Fast Switching Drives

As the switching frequency of PWM controllers is increased to reduce power supply volume and cost, fast rise and fall times are necessary to minimize switching losses (TOP MOSFET) and reduce dead-time (BOTTOM MOSFET) losses. While low Rds\_On MOSFET's present a power saving, the MOSFETs die area is larger and the effective input capacitance of the MOSFET is increased. Often a 50% decrease in Rds\_On doubles the effective input gate charge, which must be supplied by the driver. The Rds On power savings can be offset by the switching and dead-time losses with a suboptimum driver. While discrete solution can achieve reasonable drive capability, implementing shoot-through, programmable delay and other housekeeping functions necessary for safe operation can become cumbersome and costly. The SC420A presents a total solution for the high-speed, high power density applications. Wide input supply range of 4.5V-25V allows use in battery powered applications, new high voltage, distributed power supplies.

#### Shoot Through Protection

The control input (CO) to the SC420A is typically supplied by a PWM controller that regulates the power supply output. The timing diagram demonstrates the sequence of events by which the top and bottom drive signals are applied. The shoot-through protection is implemented by holding the bottom FET off until the voltage at the phase node (intersection of top FET source, the output inductor and the bottom FET drain) has dropped below 1V. This assures that the top FET has turned off and that a direct current path does not exist between the

input supply and ground, a shoot-through condition during which both the top and bottom FET's could be on momentarily. The top FET is also prevented from turning on until the bottom FET is off. The top FET turn-on delay is internally set to 30ns (typical) and may be programmably extended by an external capacitor on the Cdelay pin, the delay is increased by 1ns/pf.

The EN (enable) pin may be used to turn both TG and BG drives off. This lowers power consumption by reducing the quiescent current draw of the SC420A to IQsd.

#### CO Undriven

If the CO pin is undriven it will be pulled to GND by an internal pull down resistor. This will switch the BG pin high and the TG pin low.

Over Temperature Shutdown

The SC420A will shutdown by pulling both driver's low if its junction temperature,  $T_{j}$ , exceeds 165°C. The drivers will resume operation when  $T_{j}$  declines below 155°C.

#### Supply Voltage

The SC42OA can operate from 4.75V to 6V. The  $V_{\rm IN}$  pin bypass capacitor must also be less than 0.5in away from the SC42OA. The ground node of this capacitor, the SC42OA PGND pin and the Source of the bottom FET must be very close to each other, preferably with common PCB copper land with multiple vias to the ground plane (if used). The parallel Schottky (if used) must be physically next to the Bottom FET's drain and source pins. Any trace or lead inductance in these connections will drive current away from the Schottky and allow it to flow through the FET's Body diode, thus reducing efficiency.

Preventing Inadvertent Bottom Gate Turn-on

At high VIN2 input voltages, (12V and greater) a fast turnon of the top FET creates a positive going spike on the Bottom FET's gate through the Miller capacitance, Crss of the bottom FET. The voltage appearing on the gate due to this spike is:

$$V_{SPIKE} = \frac{Vin * Crss}{(Crss + Ciss)}$$

## Applications Information (Cont.)

Where Ciss is the input gate capacitance of the bottom FET. This is assuming that the impedance of the drive path is too high compared to the instantaneous impedance of the capacitors, since dV/dT and thus the effective frequency is very high. If the BG pin of the SC420A is very close to the bottom FET, Vspike will be reduced depending on trace inductance, rate of rise of current, etc.

A capacitor may be added from the gate of the Bottom FET to its source, preferably less than 0.5in away. This capacitor will be added to Ciss in the above equation to reduce the effective spike voltage.

The bottom MOSFET must be selected with attention paid to the Crss/Ciss ratio. A low ratio reduces the Miller feedback and thus reduces Vspike. Also MOSFETs with higher Turn-on threshold voltages will conduct at a higher voltage and will not turn on during the spike. A zero ohm bottom FET gate resistor will obviously help keeping the gate voltage low during off time.

Ultimately, slowing down the top FET by adding boost resistance will reduce di/dt which will in turn make the effective impedance of the capacitors higher, thus allowing the BG driver to hold the bottom gate voltage low. It does this at the expense of increased switching times (and switching losses) for the top FET.

The top MOSFET source must be close to the bottom MOSFET drain to prevent ringing and the possibility of the phase node going negative. This frequency is determined by:

$$F_{ring} = \frac{1}{(2\Pi * Sqrt (L_{ST} * Coss))} = \frac{1}{2\pi \sqrt{L_{ST} * C_{OSS}}}$$

-Where:

$L_{ST}$  = The effective stray inductance of the top FET added to trace inductance of the connection between top FET's source and the bottom FET's ground connection.

$C_{oss}$  = Drain to Source capacitance of the bottom FET. If there is a Schottky used, the capacitance of the Schottky is added to this value

Although this ringing does not pose any power losses due to a fairly high Q, it could cause the phase node to go too

far negative, thus causing improper operation, double pulsing or at worst driver damage. On the SC420A, the drain node, DRN, can go as far as 2V below ground without affecting operation or sustaining damage.

The ringing is also an EMI nuisance due to its high resonant frequency. Adding a capacitor, typically 1000-2000pf, in parallel with Coss of the bottom FET will often eliminate the EMI issue.

#### Prevent Driver Overvoltage

The negative voltage spikes on the phase node adds to the bootstrap capacitor voltage, thus increasing the voltage between VBST - VDRN. *This is of special importance if higher boost voltages are used.* If the phase node negative spikes are too large, the voltage on the boost capacitor could exceed device's absolute maximum rating of 7V. To eliminate the effect of the ringing on the boost capacitor voltage, place a 1 - 10 Ohm resistor between boost Schottky diode and V<sub>IN</sub> to filter the negative spikes on DRN Pin. Initially populate it by 0 ohm. Alternately, a Silicon diode, such as the commonly available 1N4148 can substitute for the Schottky diode and eliminate the need for the series resistor.

Proper layout will guarantee minimum ringing and eliminate the need for external components. Use of surface mount MOSFETs, while increasing thermal resistance, will reduce lead inductance as well as radiated EMI.

## Applications Information (Cont.)

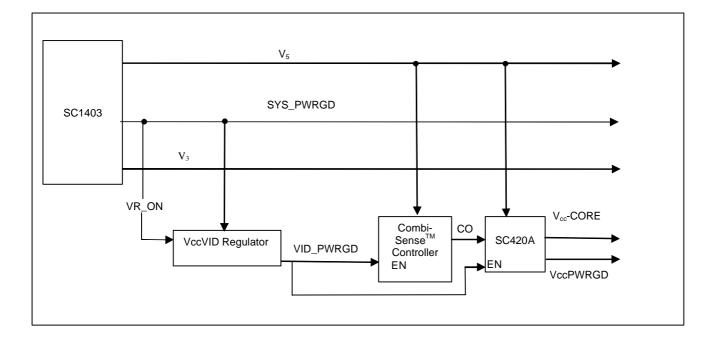

#### Start-up Sequencing

Proper sequencing of the Combi-Sense<sup>™</sup> controller and SC420A driver during both start-up and shut-down is very important. In general, the design must ensure that the driver powers up (during start-up) before the controller does, and that the driver powers down last during shut-down. This ensures that the driver will never issue gate drive pulses that are not well-controlled.

In general it is recommended that the Vcc's for the Combi-Sense Controller and SC420A be connected to the same (5V) supply. If the EN controls are not used (tied high) then the UVLO settings for the controller and driver will guarantee the proper sequencing (the SC420A maximum UVLO value is guaranteed to be lower than the Combi-Sense<sup>™</sup> Controller minimum UVLO value).

For absolute guarantee of proper sequencing it is recommended that the EN controls be used as shown in the following block diagram. With this arrangement the delayed PWRGD signal from the VccVID regulator is used to enable both ICs. The Soft-Start time established for the controller ensures it will come up well after the SC420A. During power-down de-assertion of VID\_PWRGD will ensure simultaneous disabling of the Combi-Sense<sup>™</sup> Controller and SC420A.

#### Manufacturing Guidlines

Detailed information on manufacturing and rework of PCBs using the MLP package can be found in the MLP application note "Comprehensive User's Guide - Micro Lead Frame Package". Please contact your local Semtech representative to obtain a copy of this application note.

## Applications Information (Cont.)

COMPONENT SELECTION FOR SC420A APPLICATION:

High Side MOSFET (LSFET)

The SC42OA is usually used for low duty cycle (  $\sim 10\%$  ) applications. So the Rds (ON) of the high side MOSFET is not a parameter of significant importance. A 10 - 25 mÙ Rds for the HSFET is acceptable depending on the load current. Minimum Qg for the HSFET is important for component selection. Typical range is 10 - 25 nC.

Low Side MOSFET (LSFET)

Rds is the critical selection parameter for LSFET. IT should be as low as possible for reduction of conduction losses and hence increase efficiency. Typical range is 1 - 3 m. Rg is another important parameter for LSFET. It should be as low as possible as this will give better efficiency. Typical range  $0.1 - 2 \Omega$ . Ratio of Qgd/Qgs is third parameter of consideration.

As the duty cycle for the application increases, requirements for the two FETs become more similar; however, switching charge will always be more important to the HSFET since it switches into the full voltage, and the LSFET always switching into the near zero voltage.

Boost Capacitor (Cbst)

Boost capacitor is important for SC420A application as shown in the above figure. It is a good design rule to have boost capacitance at least 100 X the Cgs for the HSFET.

Boost Resistor (Rbst)

Boost resistance is important and depends on the layout. We recommend always designing with the resistor as shown in the above circuit to help minimize EMI when the HSFET turns on. The value required is layout dependant.

#### Bottom Gate Resistor (Rbg)

BG resistance is normally not required, but may be needed for damping for long BG trace runs. We recommend one Rbg for each LSFET only when the maximum length of the BG trace is > 1 inch. Populate with 0  $\Omega$  initially. Top Gate Resistor (Rtg)

TG resistance is not generally required, as Rbst can take care of the rising edge. We recommend one Rtg for each HSFET only when the maximum length of the TG trace > 2 inches. Populate with 0  $\Omega$  initially.

Boost Diode (Dbst)

Boost Diode as shown in the above figure is required and should have a very low forward voltage drop. This increases the amount of charge on Cbst capacitor.

Delay Capacitor (Cdly)

Delay capacitor is not added in a typical application. This option is useful to control the delay between the BG falling and TG rising edges. Cdly is used for very high capacitance LSFETs to ensure BG is below Vth of the FET before TG turns on.

Decoupling capacitors (C1,C3)

These are de-coupling capacitors present in the circuit. Place as close to SC420A as possible. Typical rating is  $1\mu$ F/ 10V for C1 and 0.1 $\mu$ F /25V for C3.

# Applications Information (Cont.)

#### Critical Component Recommendations for SC420A application

| Component                       | Manufacturer                                                                             | Series or Part Number      |  |  |

|---------------------------------|------------------------------------------------------------------------------------------|----------------------------|--|--|

| High Side MOSFET, HSFET         | International Rectifier<br>Fairchild Semiconductor<br>Siliconix<br>Infenion Technologies | Depends on Application     |  |  |

| Low Side MOSFET, LSFET          | International Rectifier<br>Fairchild Semiconductor<br>Siliconix<br>Infenion Technologies | Depends on Application     |  |  |

| Boost Capacitor, Cbst           | Various                                                                                  | X5R or better              |  |  |

| Boost Diode, Dbst               | Various                                                                                  | Schottky, 200mA or greater |  |  |

| Delay Capacitor, Cdly           | Various                                                                                  | NPO Ceramic                |  |  |

| Decoupling Capacitors,<br>C1,C3 | Various                                                                                  | X5R or better              |  |  |

#### Critical Supplier Contacts

| Company                 | Contact                                                                            |

|-------------------------|------------------------------------------------------------------------------------|

| International Rectifier | Web: http://www.irf.com/product-info/<br>Phone: (310) 726-8000                     |

| Panasonic               | Web: http://www.panasonic.com/pic/ecg/<br>Phone: (201) 348-7522                    |

| IRC                     | Web: http://www.irctt.com<br>Phone: (888) 472-4376                                 |

| Kernet                  | Web: http://www.kernet.com/<br>Phone: (864) 963-6300                               |

| Sanyo                   | Web: http://www.sanyovideo.com/<br>Phone: (619) 661-6835                           |

| ТDК                     | Web: http://www.component.tdk.com/components/components.html Phone: (847) 390-4373 |

| Vishay/Dale             | Web: http://www.vishay.com/brands/dale<br>Phone: (402) 564-3131                    |

| Vishay/Siliconix        | Web: http://www.vishay.com/brands/siliconix<br>Phone: (800) 554-5565               |

# SC420A

# POWER MANAGEMENT

#### Applications Information (Cont.)

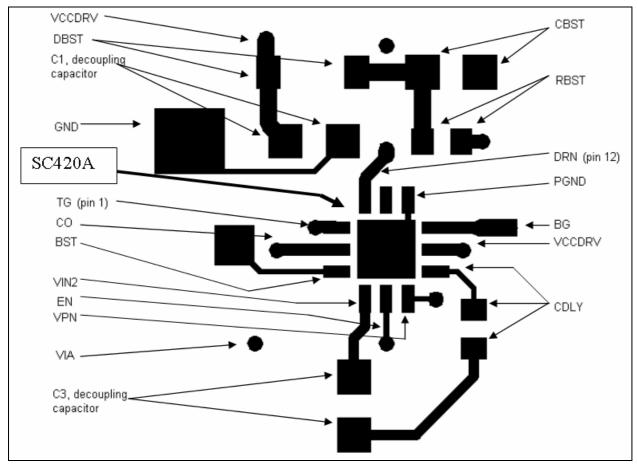

Fig 3: Typical Layout schematic for SC420A Layout Guidelines

As shown in the above layout the traces used for interconnections are not identical to each. The layout using the above traces has significant advantages.

The traces used to interconnect C1, Dbst, Cbst, Rbst, Vcc, GND, and Vbat are wider and heavy. This is done to reduce the resistance and inductance of the current path. As a result the voltage drop of the traces is significantly reduced. This arrangement charges the Cbst capacitor faster. Because of this, the FET gate capacitances are also charged and discharged faster, improving the efficiency of the system. Ceramic X7R capacitors are a good choice for supply bypassing near the chip.

Wider traces are also used for TG and BG connects. This is essential to decrease the delay of signal through the trace and allow rapid charge and discharge of the FET capacitance. Inductance is usually the dominant impedance in the time range of interest (~10ns). As a result, run the TG and BG connections with a minimum aspect ratio (length to width) of 20:1. This results in a 50 mil trace for a one inch connection. In addition, minimize the loop area of the gate drive loop. This is easy with BG, since the return path for the current is GND. In the case of TG, the return path for drivercurrent is DRN, so run these traces together, as closely as possible.

Vias represent significant inductance and are to be avoided wherever possible. BG is especially important because when the HSFET switches off, the high dV/ dt of the DRN node will force current into the LSFET gate via Cgd. A large inductance in the BG trace will prevent the driver from holding BG down at this time.

The signal level traces are not critical because the current levels are much smaller.

We can also see vias (circular dots) present in the layout. The vias are important for interconnection between different layers of the PCB. Also they are important in heat transfer and aid in running the system cooler.

## Applications Information (Cont.)

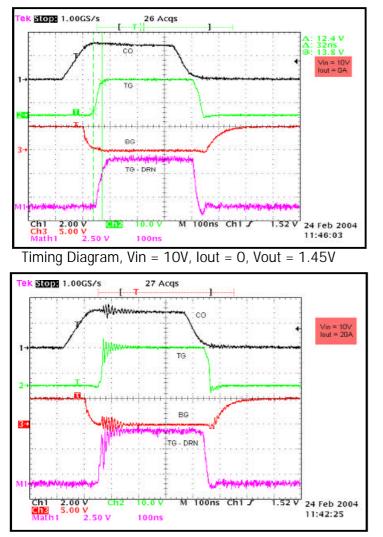

Timing Waveforms measured in a system

The following waveforms were noted using a 3-phase SC2647 Combi-Sense™ PWM controller system. Typical operating conditions for this system are

Input Voltage, Vin = 10 - 25VOutput Current, lout = 0 - 52AOutput Voltage, Vout = 0.8 - 1.85V

| Component                     | Manufacturer            | Series or Part Number                            |  |  |

|-------------------------------|-------------------------|--------------------------------------------------|--|--|

| High Side MOSFET (each phase) | International Rectifier | 2 IRF7811AV's, total gate capacitance = 3.602 nF |  |  |

| Low Side MOSFET (each phase)  | Fairchild Semiconductor | 2 FDS7066's, total gate capacitance = 9.946 nF   |  |  |

| Output inductor (each phase)  | Panasonic               | Series 2334Q, L= 700nH, RL~ 1mohm                |  |  |

| Controller                    | Semtech                 | SC2647                                           |  |  |

List of components used for above application

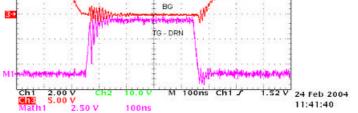

# Outline Drawing - MLP-12

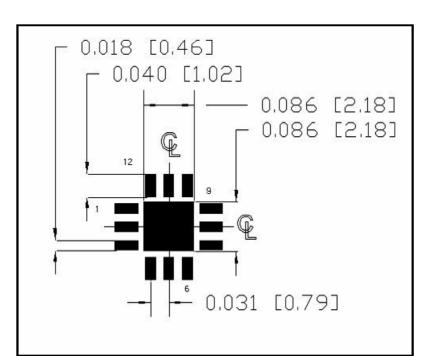

# PCB FOOTPRINT - MLP-12

SC420A Footprint

Note:

This land pattern is for reference purposes only. Consult your manufacturing group to ensure you meet your company's manufacturability guidelines.

# Contact Information

Semtech Corporation Power Management Products Division 200 Flynn Road, Camarillo, CA 93012 Phone: (805)498-2111 FAX (805)498-3804 SC420A