Order Number: MC88LV915T/D Rev 3, 08/2001

# Low Voltage Low Skew CMOS PLL Clock Driver, 3-State

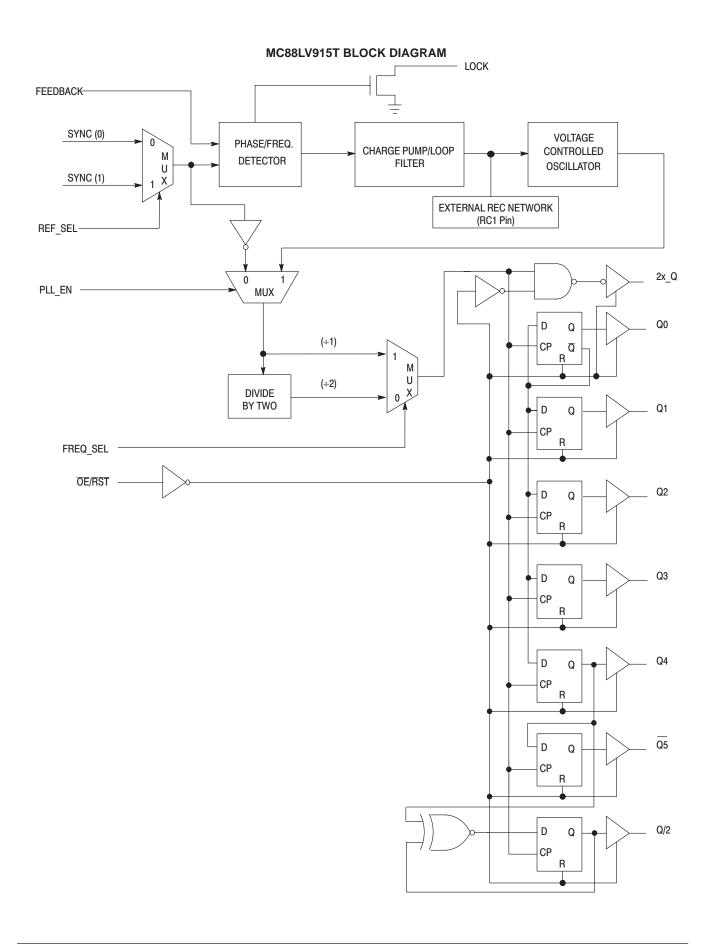

The MC88LV915T Clock Driver utilizes phase–locked loop technology to lock its low skew outputs' frequency and phase onto an input reference clock. It is designed to provide clock distribution for high performance PC's and workstations.

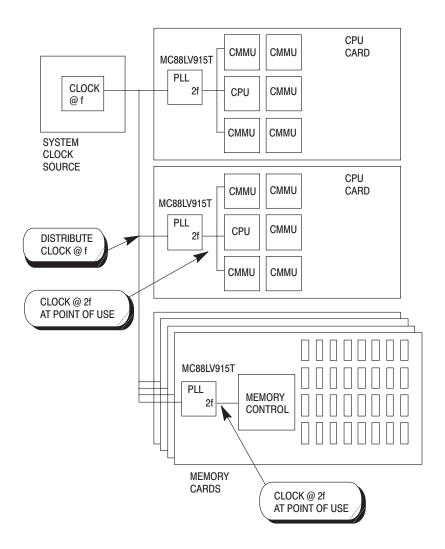

The PLL allows the high current, low skew outputs to lock onto a single clock input and distribute it with essentially zero delay to multiple components on a board. The PLL also allows the MC88LV915T to multiply a low frequency input clock and distribute it locally at a higher (2X) system frequency. Multiple 88LV915's can lock onto a single reference clock, which is ideal for applications when a central system clock must be distributed synchronously to multiple boards (see Figure 4 on Page 9).

# MC88LV915T

LOW SKEW CMOS

PLL CLOCK DRIVER

Five "Q" outputs (Q0–Q4) are provided with less than 500 ps skew between their rising edges. The  $\overline{Q5}$  output is inverted (180° phase shift) from the "Q" outputs. The 2X\_Q output runs at twice the "Q" output frequency, while the Q/2 runs at 1/2 the "Q" frequency.

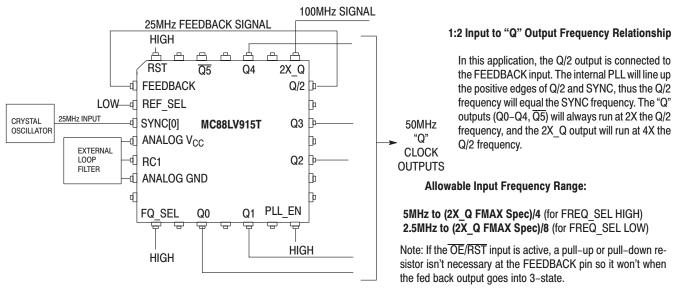

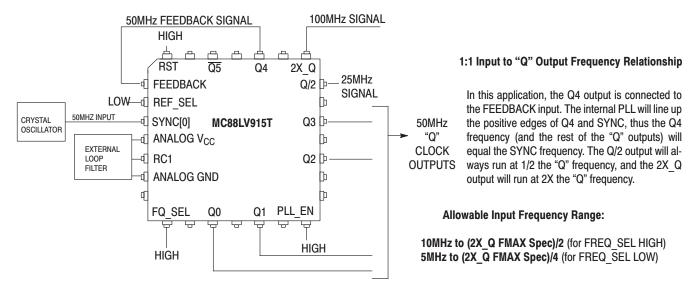

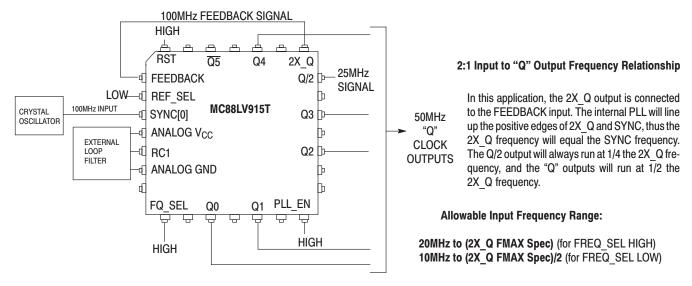

The VCO is designed to run optimally between 20 MHz and the  $2X_Q$   $F_{max}$  specification. The wiring diagrams in Figure 2 detail the different feedback configurations which create specific input/output frequency relationships. Possible frequency ratios of the "Q" outputs to the SYNC input are 2:1, 1:1, and 1:2.

The FREQ\_SEL pin provides one bit programmable divide—by in the feedback path of the PLL. It selects between divide—by–1 and divide—by–2 of the VCO before its signal reaches the internal clock distribution section of the chip (see the block diagram on page 2). In most applications FREQ\_SEL should be held high (÷1). If a low frequency reference clock input is used, holding FREQ\_SEL low (÷2) will allow the VCO to run in its optimal range (>20MHz).

In normal phase–locked operation the PLL\_EN pin is held high. Pulling the PLL\_EN pin low disables the VCO and puts the 88LV915T in a static "test mode". In this mode there is no frequency limitation on the input clock, which is necessary for a low frequency board test environment. The second SYNC input can be used as a test clock input to further simplify board–level testing (see detailed description on page 11).

Pulling the  $\overline{OE/RST}$  pin low puts the clock outputs 2X\_Q, Q0-Q4,  $\overline{Q5}$  and Q/2 into a high impedance state (3-state). After the  $\overline{OE/RST}$  pin goes back high Q0-Q4,  $\overline{Q5}$  and Q/2 will be reset in the low state, with 2X\_Q being the inverse of the selected SYNC input. Assuming PLL\_EN is low, the outputs will remain reset until the 88LV915 sees a SYNC input pulse.

A lock indicator output (LOCK) will go high when the loop is in steady–state phase and frequency lock. The LOCK output will go low if phase–lock is lost or when the PLL\_EN pin is low. The LOCK output will go high no later than 10ms after the 88LV915 sees a SYNC signal and full 5V V<sub>CC</sub>.

#### **Features**

- Five Outputs (Q0-Q4) with Output-Output Skew < 500 ps each being phase and frequency locked to the SYNC input

- The phase variation from part-to-part between the SYNC and FEEDBACK inputs is less than 550 ps (derived from the t<sub>PD</sub> specification, which defines the part-to-part skew)

- Input/Output phase-locked frequency ratios of 1:2, 1:1, and 2:1 are available

- Input frequency range from 5MHz 2X\_Q FMAX spec.

- Additional outputs available at 2X and +2 the system "Q" frequency. Also a Q (180° phase shift) output available

- All outputs have ±36 mA drive (equal high and low) at CMOS levels, and can drive either CMOS or TTL inputs. All inputs are TTL–level compatible. ±88mA I<sub>OL</sub>/I<sub>OH</sub> specifications guarantee 50Ω transmission line switching on the incident edge

- Test Mode pin (PLL\_EN) provided for low frequency testing. Two selectable CLOCK inputs for test or redundancy purposes.

All outputs can go into high impedance (3–state) for board test purposes

- Lock Indicator (LOCK) accuracy indicates a phase-locked state

Yield Surface Modeling and YSM are trademarks of Motorola, Inc.

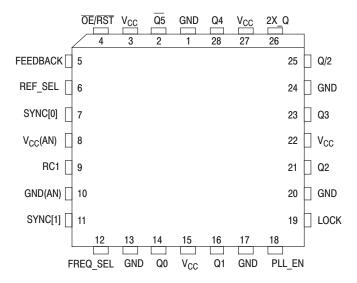

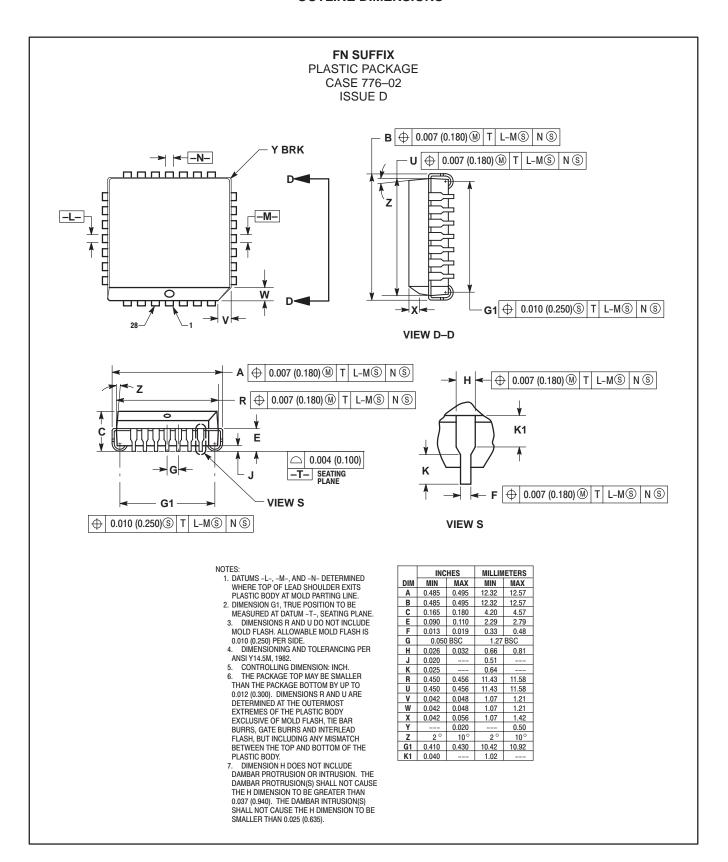

Pinout: 28-Lead PLCC (Top View)

FN SUFFIX PLASTIC PLCC CASE 776-02

#### **PIN SUMMARY**

| Pin Name                                                                                                                                        | Num                                                      | I/O                                                                                           | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYNC[0]<br>SYNC[1]<br>REF_SEL<br>FREQ_SEL<br>FEEDBACK<br>RC1<br>Q(0-4)<br>Q5<br>2x_Q<br>Q/2<br>LOCK<br>OE/RST<br>PLL_EN<br>V <sub>CC</sub> ,GND | 1<br>1<br>1<br>1<br>1<br>5<br>1<br>1<br>1<br>1<br>1<br>1 | Input Input Input Input Input Input Output Output Output Output Input Input Input Input Input | Reference clock input Reference clock input Chooses reference between sync[0] & Sync[1] Doubles VCO Internal Frequency (low) Feedback input to phase detector Input for external RC network Clock output (locked to sync) Inverse of clock output 2 x clock output (Q) frequency (synchronous) Clock output(Q) frequency ÷ 2 (synchronous) Indicates phase lock has been achieved (high when locked) Output Enable/Asynchronous reset (active low) Disables phase–lock for low freq. testing Power and ground pins (note pins 8, 10 are "analog" supply pins for internal PLL only) |

## **MAXIMUM RATINGS\***

| Symbol                             | Parameter                                        | Limits                       | Unit |

|------------------------------------|--------------------------------------------------|------------------------------|------|

| V <sub>CC</sub> , AV <sub>CC</sub> | DC Supply Voltage Referenced to GND              | -0.5 to 7.0                  | V    |

| V <sub>in</sub>                    | DC Input Voltage (Referenced to GND)             | -0.5 to V <sub>CC</sub> +0.5 | V    |

| V <sub>out</sub>                   | DC Output Voltage (Referenced to GND)            | -0.5 to V <sub>CC</sub> +0.5 | V    |

| I <sub>in</sub>                    | DC Input Current, Per Pin                        | ±20                          | mA   |

| l <sub>out</sub>                   | DC Output Sink/Source Current, Per Pin           | ±50                          | mA   |

| Icc                                | DC V <sub>CC</sub> or GND Current Per Output Pin | ±50                          | mA   |

| T <sub>stg</sub>                   | Storage Temperature                              | -65 to +150                  | °C   |

<sup>\*</sup> Maximum Ratings are those values beyond which damage to the device may occur. Functional operation should be restricted to the Recommended Operating Conditions.

## **RECOMMENDED OPERATING CONDITIONS**

| Symbol           | Parameter                     | Limits               | Unit |

|------------------|-------------------------------|----------------------|------|

| V <sub>CC</sub>  | Supply Voltage                | 3.3 ±0.3             | V    |

| V <sub>in</sub>  | DC Input Voltage              | 0 to V <sub>CC</sub> | V    |

| V <sub>out</sub> | DC Output Voltage             | 0 to V <sub>CC</sub> | V    |

| T <sub>A</sub>   | Ambient Operating Temperature | 0 to 70              | °C   |

| ESD              | Static Discharge Voltage      | > 1000               | V    |

# DC CHARACTERISTICS (T<sub>A</sub> = 0°C to 70°C; V<sub>CC</sub> = $3.3V \pm 0.3V$ )

| Symbol           | Parameter                                   | V <sub>CC</sub> | Guaranteed Limits | Unit | Condition                                            |

|------------------|---------------------------------------------|-----------------|-------------------|------|------------------------------------------------------|

| V <sub>IH</sub>  | Minimum High Level Input Voltage            | 3.0<br>3.3      | 2.0<br>2.0        | V    | V <sub>OUT</sub> = 0.1V or<br>V <sub>CC</sub> - 0.1V |

| V <sub>IL</sub>  | Minimum Low Level Input Voltage             | 3.0<br>3.3      | 0.8<br>0.8        | V    | V <sub>OUT</sub> = 0.1V or<br>V <sub>CC</sub> - 0.1V |

| V <sub>OH</sub>  | Minimum High Level Output Voltage           | 3.0<br>3.3      | 2.4<br>2.7        | V    | $V_{IN} = V_{IH}$ or $V_{IL}$<br>$I_{OH} = -24$ mA   |

| V <sub>OL</sub>  | Minimum Low Level Output Voltage            | 3.0<br>3.3      | 0.44<br>0.44      | V    | $V_{IN} = V_{IH}$ or $V_{IL}$<br>$I_{OH} = 24$ mA    |

| I <sub>IN</sub>  | Maximum Input Leakage Current               | 3.6             | ±1.0              | μΑ   | $V_I = V_{CC}$ , GND                                 |

| I <sub>CCT</sub> | Maximum I <sub>CC</sub> /Input              | 3.6             | 2.0               | mA   | $V_{I} = V_{CC} - 2.1V$                              |

| I <sub>OLD</sub> | Minimum Dynamic <sup>3</sup> Output Current | 3.6             | +50               | mA   | V <sub>OLD</sub> = 1.25V                             |

| I <sub>OHD</sub> |                                             | 3.6             | -50               | mA   | V <sub>OHD</sub> =2.35V                              |

| I <sub>CC</sub>  | Maximum Quiescent Supply Current            | 3.6             | TBD               | μА   | $V_I = V_{CC}$ , GND                                 |

- I<sub>OL</sub> is +12mA for the RST\_OUT output.

The PLL\_EN input pin is not guaranteed to meet this specification.

- 3. Maximum test duration 2.0ms, one output loaded at a time.

#### SYNC INPUT TIMING REQUIREMENTS

| Symbol                               | Parameter                                       | Minimum                   | Maximum | Unit |

|--------------------------------------|-------------------------------------------------|---------------------------|---------|------|

| t <sub>RISE/FALL</sub><br>SYNC Input | Rise/Fall Time, SYNC Input<br>From 0.8V to 2.0V | _                         | 5.0     | ns   |

| t <sub>CYCLE</sub> ,<br>SYNC Input   | Input Clock Period<br>SYNC Input                | 1<br>f <sub>2</sub> X_Q/4 | 100     | ns   |

| Duty Cycle                           | Duty Cycle, SYNC Input                          | 50% ±                     | 25%     |      |

# FREQUENCY SPECIFICATIONS (T<sub>A</sub> = 0°C to 70°C; $V_{CC}$ = 3.3V $\pm$ 0.3V)

| Symbol      | Parameter                                     | Guaranteed Minimum | Unit |  |

|-------------|-----------------------------------------------|--------------------|------|--|

| Fmax (2X_Q) | Maximum Operating Frequency, 2X_Q Output      | 100                | MHz  |  |

| Fmax ('Q')  | Maximum Operating Frequency,<br>Q0–Q3 Outputs | 50                 | MHz  |  |

NOTE: Maximum Operating Frequency is guaranteed with the 88LV926 in a phase–locked condition.

## AC CHARACTERISTICS ( $T_A$ =0° C to +70° C, $V_{CC}$ = 3.3V ±0.3V, Load = $50\Omega$ Terminated to $V_{CC}$ /2)

| Symbol                                                         | Parameter                                                                                        | Min                                                                                                                      | Max                                                                                                                      | Unit | Condition                                                                  |

|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------|----------------------------------------------------------------------------|

| t <sub>RISE/FALL</sub><br>Outputs                              | Rise/Fall Time, All Outputs<br>(Between 0.8 to 2.0V)                                             | 0.5                                                                                                                      | 2.0                                                                                                                      | ns   | Into a 50Ω Load<br>Terminated to V <sub>CC</sub> /2                        |

| $t_{\text{PULSE WIDTH}}$ (Q0–Q4, $\overline{\text{Q5}}$ , Q/2) | Output Pulse Width: Q0, Q1, Q2, Q3, Q4, Q5, Q/2 @ V <sub>CC</sub> /2                             | 0.5t <sub>CYCLE</sub> - 0.5 <sup>1</sup>                                                                                 | 0.5t <sub>CYCLE</sub> + 0.5 <sup>1</sup>                                                                                 | ns   | Into a 50Ω Load<br>Terminated to V <sub>CC</sub> /2                        |

| tPULSE WIDTH (2X_Q Output)                                     | Output Pulse Width: 40MHz<br>2X_Q @ 1.5V 66MHz<br>80MHz<br>100MHz                                | 0.5t <sub>CYCLE</sub> - 1.5<br>0.5t <sub>CYCLE</sub> - 1.0<br>0.5t <sub>CYCLE</sub> - 1.0<br>0.5t <sub>CYCLE</sub> - 1.0 | 0.5t <sub>CYCLE</sub> + 0.5<br>0.5t <sub>CYCLE</sub> + 0.5<br>0.5t <sub>CYCLE</sub> + 0.5<br>0.5t <sub>CYCLE</sub> + 0.5 | ns   | Into a 50Ω Load<br>Terminated to V <sub>CC</sub> /2                        |

| tCYCLE<br>(2x_Q Output)                                        | Cycle-to-Cycle Variation 40MHz<br>2x_Q @ V <sub>CC</sub> /2 66MHz<br>80MHz<br>100MHz             | t <sub>CYCLE</sub> - 600ps<br>t <sub>CYCLE</sub> - 300ps<br>t <sub>CYCLE</sub> - 300ps<br>t <sub>CYCLE</sub> - 400ps     | t <sub>CYCLE</sub> + 600ps<br>t <sub>CYCLE</sub> + 300ps<br>t <sub>CYCLE</sub> + 300ps<br>t <sub>CYCLE</sub> + 400ps     |      |                                                                            |

| t <sub>PD</sub> <sup>2</sup>                                   |                                                                                                  | (With 1MΩ from RC1 to An V <sub>CC</sub> )                                                                               |                                                                                                                          | ns   |                                                                            |

| SYNC Feedback                                                  | SYNC Input to Feedback Delay 66MHz (Measured at SYNC0 or 1 and 80MHz FEEDBACK Input Pins) 100MHz | -1.65<br>-1.45<br>-1.25                                                                                                  | -1.05<br>-0.85<br>-0.65                                                                                                  |      |                                                                            |

| <sup>t</sup> SKEWr <sup>3</sup><br>(Rising) See Note 4         | Output-to-Output Skew Between Outputs Q0-Q4, Q/2 (Rising Edges Only)                             | _                                                                                                                        | 500                                                                                                                      | ps   | All Outputs Into a Matched 50Ω Load Terminated to V <sub>CC</sub> /2       |

| <sup>t</sup> SKEWf <sup>3</sup><br>(Falling)                   | Output-to-Output Skew Between Outputs Q0-Q4 (Falling Edges Only)                                 | _                                                                                                                        | 750                                                                                                                      | ps   | All Outputs Into a<br>Matched 50Ω Load<br>Terminated to V <sub>CC</sub> /2 |

| <sup>†</sup> SKEWall <sup>3</sup>                              | Output-to-Output Skew 2X_Q, Q/2, Q0-Q4 Rising, Q5 Falling                                        | _                                                                                                                        | 750                                                                                                                      | ps   | All Outputs Into a<br>Matched 50Ω Load<br>Terminated to V <sub>CC</sub> /2 |

| tLOCK <sup>4</sup>                                             | Time Required to Acquire Phase–Lock<br>From Time SYNC Input Signal is<br>Received                | 1.0                                                                                                                      | 10                                                                                                                       | ms   | Also Time to LOCK<br>Indicator High                                        |

| t <sub>PZL</sub> 5                                             | Output Enable Time OE/RST to 2X_Q, Q0-Q4, Q5, and Q/2                                            | 3.0                                                                                                                      | 14                                                                                                                       | ns   | Measured With the PLL_EN Pin Low                                           |

| t <sub>PHZ</sub> ,t <sub>PLZ</sub> 5                           | Output Disable Time OE/RST to 2X_Q, Q0-Q4, Q5, and Q/2                                           | 3.0                                                                                                                      | 14                                                                                                                       | ns   | Measured With the PLL_EN Pin Low                                           |

T<sub>CYCLE</sub> in this spec is 1/Frequency at which the particular output is running.

The T<sub>PD</sub> specification's min/max values may shift closer to zero if a larger pullup resistor is used.

Inc. T<sub>PD</sub> specification's minimax values may shift closer to zero if a larger pullup resistor is used.

Under equally loaded conditions and at a fixed temperature and voltage.

With V<sub>CC</sub> fully powered—on, and an output properly connected to the FEEDBACK pin. t<sub>LOCK</sub> maximum is with C1 = 0.1μF, t<sub>LOCK</sub> minimum is with C1 = 0.01μF.

<sup>5.</sup> The t<sub>PZL</sub>, t<sub>PHZ</sub>, t<sub>PLZ</sub> minimum and maximum specifications are estimates, the final guaranteed values will be available when 'MC' status is reached.

# **Applications Information for All Versions**

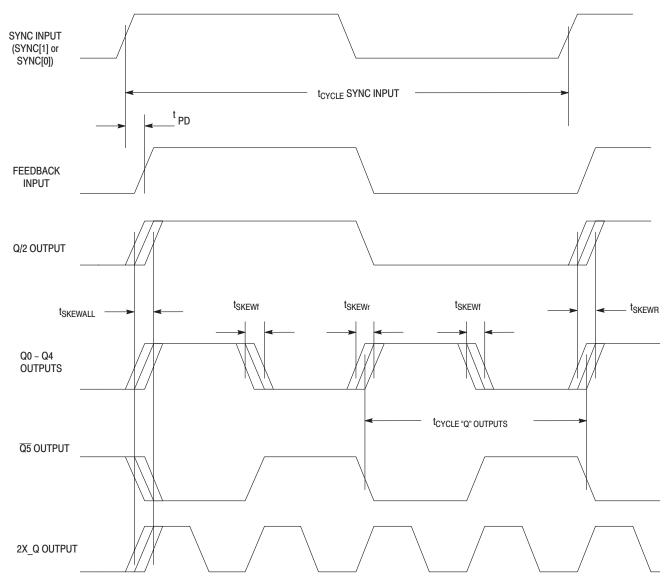

Figure 1. Output/Input Switching Waveforms and Timing Diagrams

(These waveforms represent the hook-up configuration of Figure 2a on page 7)

## **Timing Notes:**

- The MC88LV915T aligns rising edges of the FEEDBACK input and SYNC input, therefore the SYNC input does not require a 50% duty cycle.

- All skew specs are measured between the  $V_{CC}/2$  crossing point of the appropriate output edges. All skews are specified as 'windows', not as a  $\pm$  deviation around a center point.

- If a "Q" output is connected to the FEEDBACK input (this situation is not shown), the "Q" output frequency would match the SYNC input frequency, the 2X\_Q output would run at twice the SYNC frequency, and the Q/2 output would run at half the SYNC frequency.

Figure 2a. Wiring Diagram and Frequency Relationships With Q/2 Output Feed Back

Figure 2b. Wiring Diagram and Frequency Relationships With Q4 Output Feed Back

Figure 2c. Wiring Diagram and Frequency Relationships with 2X\_Q Output Feed Back

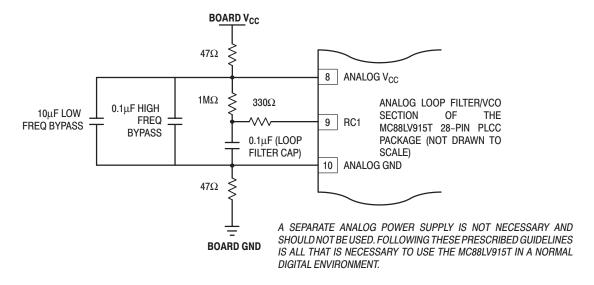

Figure 3. Recommended Loop Filter and Analog Isolation Scheme for the MC88LV915T

#### **Notes Concerning Loop Filter and Board Layout Issues**

- Figure 3 shows a loop filter and analog isolation scheme which will be effective in most applications. The following guidelines should be followed to ensure stable and jitter–free operation:

- 1a.All loop filter and analog isolation components should be tied as close to the package as possible. Stray current passing through the parasitics of long traces can cause undesirable voltage transients at the RC1 pin.

- 1b.The  $47\Omega$  resistors, the  $10\mu F$  low frequency bypass capacitor, and the  $0.1\mu F$  high frequency bypass capacitor form a wide bandwidth filter that will minimize the 88LV915T's sensitivity to voltage transients from the system digital  $V_{CC}$  supply and ground planes. This filter will typically ensure that a 100mV step deviation on the digital  $V_{CC}$  supply will cause no more than a 100pS phase deviation on the 88LV915T outputs. A 250mV step deviation on  $V_{CC}$  using the recommended filter values should cause no more than a 250pS phase deviation; if a  $25\mu F$  bypass capacitor is used (instead of  $10\mu F$ ) a 250mV  $V_{CC}$  step should cause no more than a 100pS phase deviation.

If good bypass techniques are used on a board design near components which may cause digital  $V_{CC}$  and ground noise, the above described  $V_{CC}$  step deviations should not occur at the 88LV915T's digital  $V_{CC}$  supply. The purpose

- of the bypass filtering scheme shown in Figure 3 is to give the 88LV915T additional protection from the power supply and ground plane transients that can occur in a high frequency, high speed digital system.

- 1c.There are no special requirements set forth for the loop filter resistors (1M $\Omega$  and 330 $\Omega$ ). The loop filter capacitor (0.1 $\mu$ F) can be a ceramic chip capacitior, the same as a standard bypass capacitor.

- 1d.The 1M reference resistor injects current into the internal charge pump of the PLL, causing a fixed offset between the outputs and the SYNC input. This also prevents excessive jitter caused by inherent PLL dead–band. If the VCO (2X\_Q output) is running above 40MHz, the 1M $\Omega$  resistor provides the correct amount of current injection into the charge pump (2–3 $\mu$ A). For the TFN55, 70 or 100, if the VCO is running below 40MHz, a 1.5M $\Omega$  reference resistor should be used (instead of 1M $\Omega$ ).

- 2. In addition to the bypass capacitors used in the analog filter of Figure 3, there should be a  $0.1\mu F$  bypass capacitor between each of the other (digital) four  $V_{CC}$  pins and the board ground plane. This will reduce output switching noise caused by the 88LV915T outputs, in addition to reducing potential for noise in the 'analog' section of the chip. These bypass capacitors should also be tied as close to the 88LV915T package as possible.

Figure 4. Representation of a Potential Multi-Processing Application Utilizing the MC88LV915T for Frequency Multiplication and Low Board-to-Board Skew

## MC88LV915T System Level Testing Functionality

3–state functionality has been added to the 100MHz version of the MC88LV915T to ease system board testing. Bringing the  $\overline{\text{OE/RST}}$  pin low will put all outputs (except for LOCK) into the high impedance state. As long as the PLL\_EN pin is low, the Q0–Q4, Q5, and the Q/2 outputs will remain reset in the low state after the  $\overline{\text{OE/RST}}$  until a falling SYNC edge is seen. The 2X\_Q output will be the inverse of the SYNC signal in this mode. If the 3–state functionality will be used, a pull–up or pull–down resistor must be tied to the FEEDBACK input pin to prevent it from floating when the fedback output goes into high impedance.

With the PLL\_EN pin low the selected SYNC signal is gated directly into the internal clock distribution network, bypassing and disabling the VCO. In this mode the outputs are directly driven by the SYNC input (per the block diagram). This mode can also be used for low frequency board testing.

Note: If the outputs are put into 3–state during normal PLL operation, the loop will be broken and phase–lock will be lost. It will take a maximum of 10mS (tLOCK spec) to regain phase–lock after the OE/RST pin goes back high.

#### **OUTLINE DIMENSIONS**

# **NOTES**

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

MOTOROLA and the Stylized M Logo are registered in the US Patent & Trademark Office. All other product or service names are the property of their respective owners. © Motorola, Inc. 2001.

#### How to reach us:

USA/EUROPE/Locations Not Listed: Motorola Literature Distribution; P.O. Box 5405, Denver, Colorado 80217. 1–303–675–2140 or 1–800–441–2447

JAPAN: Motorola Japan Ltd.; SPS, Technical Information Center, 3-20-1, Minami-Azabu. Minato-ku, Tokyo 106-8573 Japan. 81-3-3440-3569

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Centre, 2 Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong. 852–26668334

Technical Information Center: 1-800-521-6274

HOME PAGE: http://www.motorola.com/semiconductors/

MC88LV915T/D