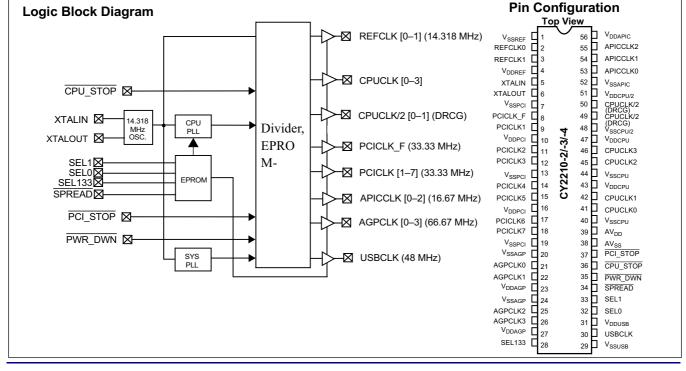

# 133 MHz Spread Spectrum Clock Synthesizer/Driver with AGP, USB, and DRCG Support

| Features                                                                                                                             | Benefits                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| Mixed 2.5V and 3.3V Operation                                                                                                        | Usable with Pentium <sup>®</sup> II and Pentium <sup>®</sup> III processors                      |

| <ul> <li>Compliant to Intel<sup>®</sup> CK133 (CY2210-3) &amp; CK133W<br/>(CY2210-2) synthesizer and driver specification</li> </ul> |                                                                                                  |

| <ul> <li>Multiple output clocks at different frequencies</li> </ul>                                                                  | Single-chip main motherboard clock generator                                                     |

| <ul> <li>Four CPU clocks, up to 133 MHz</li> </ul>                                                                                   | <ul> <li>Driven together, support 4 CPUs and a chipset</li> </ul>                                |

| <ul> <li>— Eight synchronous PCI clocks, 1 free-running</li> </ul>                                                                   | <ul> <li>— Support for 4 PCI slots and chipset</li> </ul>                                        |

| <ul> <li>— Two CPU/2 clocks, at one-half the CPU frequency</li> <li>— Four AGP clocks at 66 MHz</li> </ul>                           | <ul> <li>Drives up to two main memory clock generators, including<br/>DRCG (CPUCLK/2)</li> </ul> |

| — Three synchronous APIC clocks, at 16.67 MHz                                                                                        | <ul> <li>— Support for multiple AGP slots</li> </ul>                                             |

| — One USB clock at 48 MHz                                                                                                            | <ul> <li>— Support multiprocessing systems</li> </ul>                                            |

| — Two reference clocks at 14.318 MHz                                                                                                 | <ul> <li>— Supports USB frequencies and I/O chip</li> </ul>                                      |

| Spread Spectrum clocking                                                                                                             | Enables reduction of EMI in some systems                                                         |

| <ul> <li>— 32.5-kHz modulation frequency @ 133 MHz</li> </ul>                                                                        |                                                                                                  |

| <ul> <li>— 33.1-kHz modulation frequency @ 100 MHz for<br/>CY2210-02/03</li> </ul>                                                   |                                                                                                  |

| <ul> <li>— 33.4-kHz modulation frequency @ 100 MHz for<br/>CY2210-04</li> </ul>                                                      |                                                                                                  |

| <ul> <li>— EPROM programmable percentage of spreading. Default<br/>is –0.6%, which is recommended by Intel</li> </ul>                |                                                                                                  |

| Power-down features                                                                                                                  | Supports mobile systems                                                                          |

| Three Select inputs                                                                                                                  | Supports up to eight CPU clock frequencies                                                       |

| Low-skew and low-jitter outputs                                                                                                      | Meets tight system timing requirements at high frequency                                         |

| OE and Test Mode support                                                                                                             | Enables ATE and "bed of nails" testing                                                           |

| 56-pin SSOP package                                                                                                                  | Widely available, standard package enables lower cost                                            |

Rev 1.0, November 25, 2006

2200 Laurelwood Road, Santa Clara, CA 95054

Tel:(408) 855-0555

Fax:(408) 855-0550

## Pin Summary

| Name                   | Pins                      | Description                                                 |

|------------------------|---------------------------|-------------------------------------------------------------|

| V <sub>SSREF</sub>     | 1                         | 3.3V Reference ground                                       |

| V <sub>DDREF</sub>     | 4                         | 3.3V Reference voltage supply                               |

| V <sub>SSPCI</sub>     | 7, 13, 19                 | 3.3V PCI ground                                             |

| V <sub>DDPCI</sub>     | 10, 16                    | 3.3V PCI voltage supply                                     |

| V <sub>SSAGP</sub>     | 20, 24                    | 3.3V AGP ground                                             |

| V <sub>DDAGP</sub>     | 23, 27                    | 3.3V AGP voltage supply                                     |

| V <sub>SSUSB</sub>     | 29                        | 3.3V USB ground                                             |

| V <sub>DDUSB</sub>     | 31                        | 3.3V USB voltage supply                                     |

| V <sub>SSCPU</sub>     | 40, 44                    | 2.5V CPU ground                                             |

| V <sub>DDCPU</sub>     | 43, 47                    | 2.5V CPU voltage supply                                     |

| V <sub>SSCPU</sub> /2  | 48                        | 2.5V CPU/2 ground                                           |

| V <sub>DDCPU</sub> /2  | 51                        | 2.5V CPU/2 voltage supply                                   |

| V <sub>SSAPIC</sub>    | 52                        | 2.5V APIC ground                                            |

| V <sub>DDAPIC</sub>    | 56                        | 2.5V APIC voltage supply                                    |

| AV <sub>SS</sub>       | 38                        | Analog ground to PLL and Core                               |

| AV <sub>DD</sub>       | 39                        | Analog voltage supply to PLL and Core                       |

| XTALIN <sup>[1]</sup>  | 5                         | Reference crystal input                                     |

| XTALOUT <sup>[1]</sup> | 6                         | Reference crystal feedback                                  |

| CPUCLK [0-3]           | 41, 42, 45, 46            | CPU clock outputs                                           |

| PCICLK [1–7]           | 9, 11, 12, 14, 15, 17, 18 | PCI clock outputs, synchronously running at 33.33 MHz       |

| PCICLK_F               | 8                         | Free running PCI clock                                      |

| CPUCLK/2               | 49, 50                    | CPU/2 clock outputs, drive memory clock generator           |

| AGPCLK [0–3]           | 21, 22, 25, 26            | AGP clock outputs, running at 66.66 MHz                     |

| APICCLK [0-2]          | 53, 54, 55                | APIC clock outputs, running at 16.67 MHz                    |

| REFCLK [0-1]           | 2, 3                      | Reference clock outputs, 14.318 MHz                         |

| USBCLK                 | 30                        | 48-MHz USB clock output                                     |

| CPU_STOP               | 36                        | Active LOW input, disables CPU and AGP clocks when asserted |

| PCI_STOP               | 37                        | Active LOW input, disables PCI clocks when asserted         |

| PWR_DWN                | 35                        | Active LOW input, powers down part when asserted            |

| SPREAD                 | 34                        | Active LOW input, enables spread spectrum when asserted     |

| SEL1                   | 33                        | CPU frequency select input (See Function Table)             |

| SEL0                   | 32                        | CPU frequency select input (See Function Table)             |

| SEL133                 | 28                        | CPU frequency select input (See Function Table)             |

Note:

1. For best accuracy, use a parallel-resonant crystal, C<sub>LOAD</sub> = 18 pF. For crystals with different C<sub>LOAD</sub>, please refer to the application note, "Crystal Oscillator Topics."

## Function Table<sup>[2]</sup>

| SEL133 | SEL1 | SEL0 | CPUCLK<br>(MHz)        | CPUCLK/2<br>(MHz)     | AGPCLK<br>(MHz)       | PCICLK<br>(MHz)       | USBCLK<br>(MHz)       | REFCLK<br>(MHz)       | APICCLK<br>(MHz)      |

|--------|------|------|------------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| 0      | 0    | 0    | Hi-Z                   | Hi-Z                  | Hi-Z                  | Hi-Z                  | Hi-Z                  | Hi-Z                  | Hi-Z                  |

| 0      | 0    | 1    | 100.227 <sup>[3]</sup> | 50.114 <sup>[3]</sup> | 66.818 <sup>[3]</sup> | 33.409 <sup>[3]</sup> | 48.008 <sup>[3]</sup> | 14.318 <sup>[3]</sup> | 16.705 <sup>[3]</sup> |

| 0      | 1    | 0    | 100                    | 50                    | 66.67                 | 33.33                 | OFF                   | 14.318                | 16.67                 |

| 0      | 1    | 1    | 100                    | 50                    | 66.67                 | 33.33                 | 48                    | 14.318                | 16.67                 |

| 1      | 0    | 0    | TCLK/2                 | TCLK/4                | TCLK/4                | TCLK/8                | TCLK/2                | TCLK                  | TCLK/16               |

| 1      | 0    | 1    | N/A                    | N/A                   | N/A                   | N/A                   | N/A                   | N/A                   | N/A                   |

| 1      | 1    | 0    | 133.33                 | 66.67                 | 66.67                 | 33.33                 | OFF                   | 14.318                | 16.67                 |

| 1      | 1    | 1    | 133.33                 | 66.67                 | 66.67                 | 33.33                 | 48                    | 14.318                | 16.67                 |

## **Actual Clock Frequency Values**

| Clock  |        | TargetActualFrequencyFrequency(MHz)(MHz) |        | РРМ     |         |         |       |       |       |

|--------|--------|------------------------------------------|--------|---------|---------|---------|-------|-------|-------|

| Output | -2     | -3                                       | -4     | -2      | -3      | -4      | -2    | -3    | -4    |

| CPUCLK | 100.0  | 100.0                                    | 100.0  | 99.126  | 99.126  | 100.227 | -8740 | -8740 | +2714 |

| CPUCLK | 133.33 | 133.33                                   | 133.33 | 132.769 | 132.769 | 132.769 | -4208 | -4208 | -4208 |

| USBCLK | 48.0   | 48.0                                     | 48.0   | 48.008  | 48.008  | 48.008  | 167   | 167   | 167   |

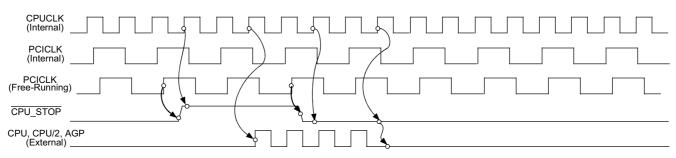

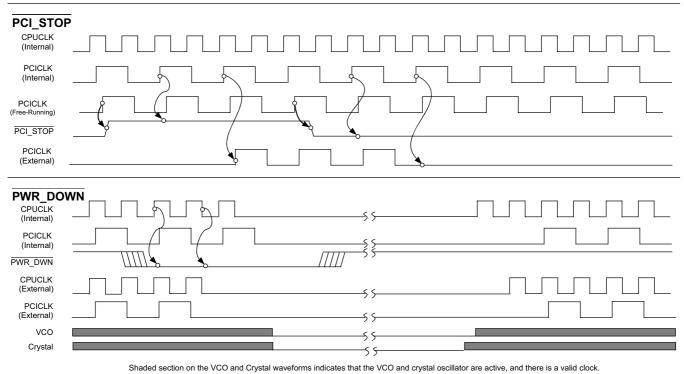

## **Clock Enable Configuration**

| CPU_STOP | PWR_DWN | PCI_STOP | CPUCLK | CPUCLK/2 | AGP | PCI | PCI_F | REF<br>APIC | OSC. | VCOs |

|----------|---------|----------|--------|----------|-----|-----|-------|-------------|------|------|

| Х        | 0       | Х        | LOW    | LOW      | LOW | LOW | LOW   | LOW         | OFF  | OFF  |

| 0        | 1       | 0        | LOW    | ON       | LOW | LOW | ON    | ON          | ON   | ON   |

| 0        | 1       | 1        | LOW    | ON       | LOW | ON  | ON    | ON          | ON   | ON   |

| 1        | 1       | 0        | ON     | ON       | ON  | LOW | ON    | ON          | ON   | ON   |

| 1        | 1       | 1        | ON     | ON       | ON  | ON  | ON    | ON          | ON   | ON   |

#### **Clock Driver Impedances**

|                  |                       |             | Impedance    |                     |              |

|------------------|-----------------------|-------------|--------------|---------------------|--------------|

| Buffer Name      | V <sub>DD</sub> Range | Buffer Type | Minimum<br>Ω | <b>Typical</b><br>Ω | Maximum<br>Ω |

| CPU, CPU/2, APIC | 2.375–2.625           | Type 1      | 13.5         | 29                  | 45           |

| USB, REF         | 3.135–3.465           | Туре 3      | 20           | 40                  | 60           |

| PCI, AGP         | 3.135–3.465           | Type 5      | 12           | 30                  | 55           |

Notes:

2. TCLK is a test clock driven in on the XTALIN input in test mode.

3. Only CY2210-2 supports this option. In CY2210-3, this selection is defined as "N/A" or "Reserved".

## **Maximum Ratings**

| (Above which the useful life may be impaired. For user guide- | Storage Tempe   |

|---------------------------------------------------------------|-----------------|

| lines, not tested.)                                           | Junction Temp   |

| Supply Voltage0.5 to +7.0V                                    | Package Powe    |

| Input Voltage0.5V to V <sub>DD</sub> +0.5                     | Static Discharg |

| Storage Temperature (Non-Condensing)65°C to +150°C               |

|------------------------------------------------------------------|

| Junction Temperature +150°C                                      |

| Package Power Dissipation1W                                      |

| Static Discharge Voltage<br>(per MIL-STD-883, Method 3015)>2000V |

#### **Operating Conditions** Over which Electrical Parameters are Guaranteed

| Parameter                                                                                               | Description                                                                                    | Min.   | Max.     | Unit |

|---------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------|----------|------|

| V <sub>DDREF</sub> , V <sub>DDPCI</sub> , AV <sub>DD</sub> ,<br>V <sub>DDAGP</sub> , V <sub>DDUSB</sub> | 3.3V Supply Voltages                                                                           | 3.135  | 3.465    | V    |

| V <sub>DDCPU</sub> , V <sub>DDCPU/2</sub>                                                               | CPU and CPU/2 Supply Voltage                                                                   | 2.375  | 2.625    | V    |

| V <sub>DDAPIC</sub>                                                                                     | APIC Supply Voltage                                                                            | 2.375  | 2.625    | V    |

| T <sub>A</sub>                                                                                          | Operating Temperature, Ambient                                                                 | 0      | 70       | °C   |

| CL                                                                                                      | Max. Capacitive Load on<br>CPUCLK, CPUCLK/2, USBCLK, REF, APIC<br>PCICLK, AGP                  |        | 20<br>30 | pF   |

| f <sub>(REF)</sub>                                                                                      | Reference Frequency, Oscillator Nominal Value                                                  | 14.318 | 14.318   | MHz  |

| t <sub>PU</sub>                                                                                         | Power-up time for all VDD's to reach minimum specified voltage (power ramps must be monotonic) | 0.05   | 50       | ms   |

### Electrical Characteristics Over the Operating Range

| Parameter          | Description                              | Test Conditions                                                                                      |                         |     | Max. | Unit |

|--------------------|------------------------------------------|------------------------------------------------------------------------------------------------------|-------------------------|-----|------|------|

| V <sub>IH</sub>    | High-level Input Voltage                 | Except Crystal Pads. Threshold voltage for crystal pads = $V_{DD}/2$                                 |                         |     |      | V    |

| V <sub>IL</sub>    | Low-level Input Voltage                  | Except Crystal Pads                                                                                  | Except Crystal Pads     |     |      |      |

| V <sub>OH</sub>    | High-level Output Voltage <sup>[4]</sup> | CPU, CPU/2, APIC                                                                                     | I <sub>OH</sub> = –1 mA | 2.0 |      | V    |

|                    |                                          | USB, REF, PCI, AGP                                                                                   | I <sub>OH</sub> = –1 mA | 2.4 |      |      |

| V <sub>OL</sub>    | Low-level Output Voltage <sup>[4]</sup>  | CPU, CPU/2, APIC                                                                                     | I <sub>OL</sub> = 1 mA  |     | 0.4  | V    |

|                    |                                          | USB, REF, PCI, AGP                                                                                   | I <sub>OL</sub> = 1 mA  |     | 0.4  |      |

| I <sub>IH</sub>    | Input High Current                       | $0 \le V_{IN} \le V_{DD}$                                                                            |                         |     | 10   | μA   |

| IIL                | Input Low Current                        | $0 \le V_{IN} \le V_{DD}$                                                                            |                         |     | 10   | μA   |

| I <sub>OH</sub>    | High-level Output                        | CPU, CPU/2                                                                                           | V <sub>OH</sub> = 2.0V  | -16 | -60  | mA   |

|                    | Current <sup>[4]</sup>                   | APIC                                                                                                 | V <sub>OH</sub> = 2.0V  | -20 | -72  |      |

|                    |                                          | USB, REF                                                                                             | V <sub>OH</sub> = 2.4V  | -15 | -51  |      |

|                    |                                          | AGP, PCI                                                                                             | V <sub>OH</sub> = 2.4V  | -30 | -100 |      |

| I <sub>OL</sub>    | Low-level Output Current <sup>[4]</sup>  | CPU, CPU/2                                                                                           | V <sub>OL</sub> = 0.4V  | 19  | 49   | mA   |

|                    |                                          | APIC                                                                                                 | V <sub>OL</sub> = 0.4V  | 25  | 58   |      |

|                    |                                          | USB, REF                                                                                             | V <sub>OL</sub> = 0.4V  | 10  | 24   |      |

|                    |                                          | AGP, PCI                                                                                             | V <sub>OL</sub> = 0.4V  | 20  | 49   |      |

| I <sub>OZ</sub>    | Output Leakage Current                   | Three-state                                                                                          |                         |     | 10   | μA   |

| I <sub>DD2</sub>   | 2.5V Power Supply Current                | AV <sub>DD</sub> /V <sub>DD33</sub> = 3.465V, V <sub>DD25</sub> = 2.625V, F <sub>CPU</sub> = 133 MHz |                         |     | 90   | mA   |

| I <sub>DD3</sub>   | 3.3V Power Supply Current                | AV <sub>DD</sub> /V <sub>DD33</sub> = 3.465V, V <sub>DD25</sub> = 2.625V, F <sub>CPU</sub> = 133 MHz |                         |     | 160  | mA   |

| I <sub>DDPD2</sub> | 2.5V Shutdown Current                    | AV <sub>DD</sub> /V <sub>DD33</sub> = 3.465V, V <sub>DD25</sub> = 2.625V                             |                         |     | 100  | μA   |

| I <sub>DDPD3</sub> | 3.3V Shutdown Current                    | AV <sub>DD</sub> /V <sub>DDQ3</sub> = 3.465V, V <sub>DD25</sub> = 2.625V                             |                         |     | 200  | μA   |

| Note:              | •                                        |                                                                                                      |                         |     | •    |      |

Note:

4. Parameter is guaranteed by design and characterization. Not 100% tested in production.

| Parameter       | Output              | Description                      | Test Conditions                                                          | Min. | Max. | Unit |

|-----------------|---------------------|----------------------------------|--------------------------------------------------------------------------|------|------|------|

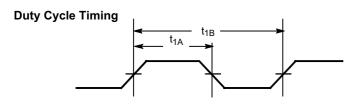

| t <sub>1</sub>  | All                 | Output Duty Cycle <sup>[6]</sup> | t <sub>1A</sub> /t <sub>1B</sub>                                         | 45   | 55   | %    |

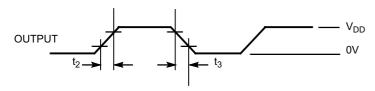

| t <sub>2</sub>  | CPU, CPU/2,<br>APIC | Rising Edge Rate                 | Between 0.4V and 2.0V                                                    | 1.0  | 4.0  | V/ns |

| t <sub>2</sub>  | USB, REF            | Rising Edge Rate                 | Between 0.4V and 2.4V                                                    | 0.5  | 2.0  | V/ns |

| t <sub>2</sub>  | PCI, AGP            | Rising Edge Rate                 | Between 0.4V and 2.4V                                                    | 1.0  | 4.0  | V/ns |

| t <sub>3</sub>  | CPU, CPU/2,<br>APIC | Falling Edge Rate                | Between 2.0V and 0.4V                                                    | 1.0  | 4.0  | V/ns |

| t <sub>3</sub>  | USB, REF            | Falling Edge Rate                | Between 2.4V and 0.4V                                                    | 0.5  | 2.0  | V/ns |

| t <sub>3</sub>  | PCI, AGP            | Falling Edge Rate                | Between 2.4V and 0.4V                                                    | 1.0  | 4.0  | V/ns |

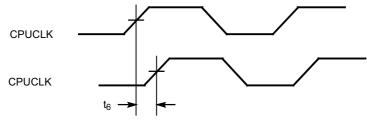

| t <sub>6</sub>  | CPU                 | CPU-CPU Skew                     | Measured at 1.25V                                                        |      | 175  | ps   |

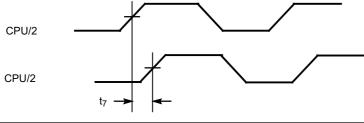

| t <sub>7</sub>  | CPU/2               | CPU/2-CPU/2 Skew                 | Measured at 1.25V                                                        |      | 175  | ps   |

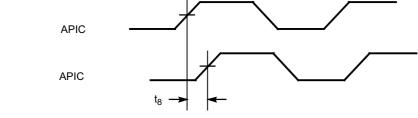

| t <sub>8</sub>  | APIC                | APIC-APIC Skew                   | Measured at 1.25V                                                        |      | 250  | ps   |

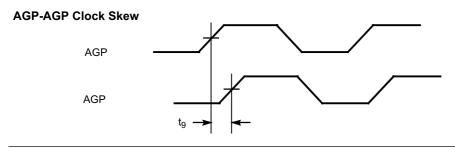

| t <sub>9</sub>  | AGP                 | AGP-AGP Skew                     | Measured at 1.5V                                                         |      | 250  | ps   |

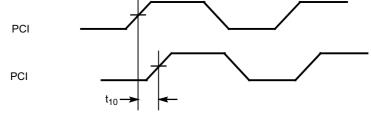

| t <sub>10</sub> | PCI                 | PCI-PCI Skew                     | Measured at 1.5V                                                         |      | 500  | ps   |

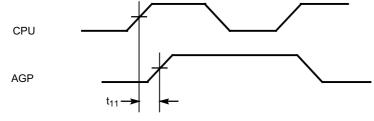

| t <sub>11</sub> | CPU, AGP            | CPU-AGP Clock Skew               | CPU leads. Measured at 1.25V for<br>2.5V clocks and 1.5V for 3.3V clocks | 0    | 1.5  | ns   |

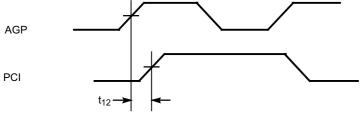

| t <sub>12</sub> | AGP, PCI            | AGP-PCI Clock Skew               | AGP leads. Measured at 1.5V                                              | 1.5  | 4.0  | ns   |

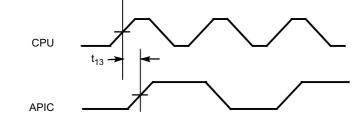

| t <sub>13</sub> | CPU, APIC           | CPU-APIC Clock Skew              | CPU leads. Measured at 1.25V                                             | 1.5  | 4    | ns   |

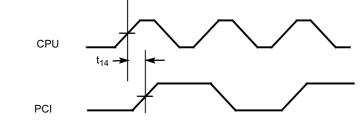

| t <sub>14</sub> | CPU, PCI            | CPU-PCI Clock Skew               | CPU leads. Measured at 1.25V clocks and 1.5V for 3.3V clocks             | 1.5  | 4    | ns   |

|                 | CPU                 | Cycle-Cycle Clock Jitter         | With all outputs running (CY2210-2)                                      |      | 150  | ps   |

|                 | CPU                 | Cycle-Cycle Clock Jitter         | With all outputs running<br>(CY2210-3/-4)                                |      | 250  | ps   |

|                 | CPU                 | Cycle-Cycle Clock Jitter         | With the USB output turned off (CY2210-3/-4)                             |      | 200  | ps   |

|                 | CPU/2               | Cycle-Cycle Clock Jitter         |                                                                          |      | 250  | ps   |

|                 | APIC                | Cycle-Cycle Clock Jitter         |                                                                          |      | 500  | ps   |

|                 | USB                 | Cycle-Cycle Clock Jitter         |                                                                          |      | 500  | ps   |

|                 | AGP                 | Cycle-Cycle Clock Jitter         |                                                                          |      | 500  | ps   |

|                 | REF                 | Cycle-Cycle Clock Jitter         |                                                                          |      | 1000 | ps   |

|                 | CPU, PCI            | Settle Time                      | CPU and PCI clock stabilization from power-up                            |      | 3    | ms   |

## Switching Characteristics<sup>[4, 5]</sup> Over the Operating Range

Notes:

5. All parameters specified with loaded outputs.

6. Duty cycle is measured at 1.5V when V<sub>DD</sub> = 3.3V. When V<sub>DD</sub> = 2.5V, duty cycle is measured at 1.25V.

## **Switching Waveforms**

#### All Outputs Rise/Fall Time

#### **CPU-CPU Clock Skew**

#### CPU/2 - CPU/2 Clock Skew

#### **APIC-APIC Clock Skew**

## Switching Waveforms (continued)

#### **PCI-PCI Clock Skew**

#### **CPU-AGP Clock Skew**

#### AGP - PCI Clock Skew

#### **CPU-APIC Clock Skew**

## Switching Waveforms (continued)

Notes:

<u>CPUCLK on</u> and CPUCLK off latency is 2 or 3 CPUCLK cycles.

<u>CPU\_STOP</u> may be applied asynchronously. It is synchronized internally.

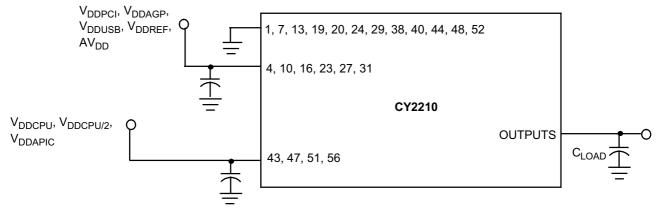

## **Test Circuit**

Note that Each supply pin must have an individual decoupling capacitor.

Note that All capacitors must be placed as close to the pins as is physically possible.

## **Ordering Information**

| Ordering Code     | Package<br>Name | Package Type | Operating<br>Range |

|-------------------|-----------------|--------------|--------------------|

| CY2210PVC-2/-3/-4 | O56             | 56-Pin SSOP  | Commercial         |

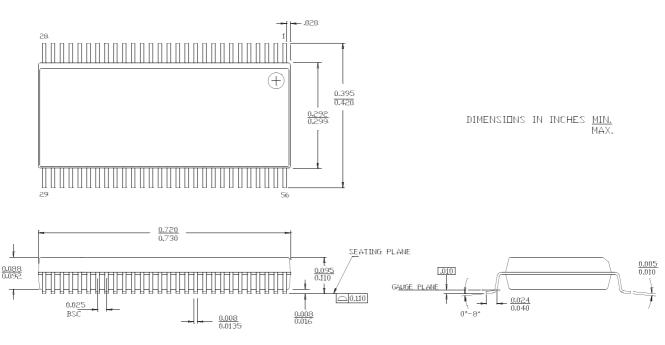

## Package Diagram

#### 56-Lead Shrunk Small Outline Package O56

While SLI has reviewed all information herein for accuracy and reliability, Spectra Linear Inc. assumes no responsibility for the use of any circuitry or for the infringement of any patents or other rights of third parties which would result from each use. This product is intended for use in normal commercial applications and is not warranted nor is it intended for use in life support, critical medical instruments, or any other application requiring extended temperature range, high reliability, or any other extraordinary environmental requirements unless pursuant to additional processing by Spectra Linear Inc., and expressed written agreement by Spectra Linear Inc. Spectra Linear Inc. reserves the right to change any circuitry or specification without notice.