### 12V, 3A Step-Down DC/DC Converter

### **General Description**

The AAT1160 is an 800kHz high efficiency step-down DC/DC converter. With a wide input voltage range of 4.0V to 13.2V, the AAT1160 is an ideal choice for dual-cell Lithium-ion battery-powered devices and mid-power-range regulated 12V-powered industrial applications. The internal power switches are capable of delivering up to 3A to the load.

The AAT1160 is a highly integrated device, simplifying system-level design. Minimum external components are required for the converter.

The AAT1160 optimizes efficiency throughout the entire load range. It operates in a combination PWM/Light Load mode for improved light-load efficiency. It can also operate in a forced Pulse Width Modulation (PWM) mode for easy control of the switching noise as well as faster transient response. The high switching frequency allows the use of small external components. The low current shutdown feature disconnects the load from  $V_{\rm IN}$  and drops shutdown current to less than  $1\mu A$ .

The AAT1160 is available in a Pb-free, space-saving, thermally-enhanced 16-pin TDFN34 package and is rated over an operating temperature range of -40°C to +85°C.

#### **Features**

- Input Voltage Range: 4.0V to 13.2V

- Up to 3A Load Current

- Fixed or Adjustable Output:

- Output Voltage: 0.6V to V<sub>IN</sub>

- Low 150µA No-Load Operating Current

- Less than 1µA Shutdown Current

- Up to 96% Efficiency

- Integrated Power Switches

- 800kHz Switching Frequency

- Synchronizable to External Clock

- Forced PWM or Light Load Mode

- Soft Start Function

- Short-Circuit and Over-Temperature Protection

- Minimum External Components

- TDFN34-16 Package

- Temperature Range: -40°C to +85°C

### **Applications**

- Distributed Power Systems

- Industrial Applications

- Laptop Computers

- Portable DVD Players

- Portable Media Players

- Set-Top Boxes

- TFT LCD Monitors and HDTVs

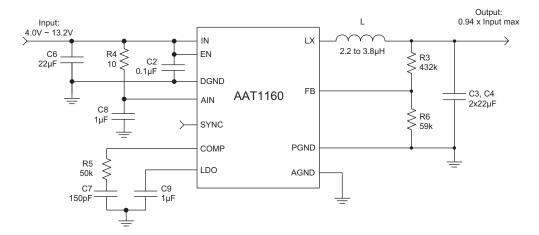

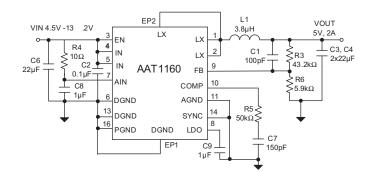

### **Typical Application**

# 12V, 3A Step-Down DC/DC Converter

# **Pin Descriptions**

| Pin #      | Symbol | Function                                                                                                                                                                                                                                                                                                                        |  |  |  |

|------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1, 2, EP2  | LX     | Power switching node. LX is the drain of the internal P-channel switch and N-channel synchronous rectifier. Connect the output inductor to the two LX pins and to EP2. A large exposed copper pad under the package should be used for EP2.                                                                                     |  |  |  |

| 3, 12      | N/C    | Not connected.                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 4, 5       | IN     | ower source input. Connect IN to the input power source. Bypass IN to DGND with a 10µF or greater apacitor. Connect both IN pins together as close to the IC as possible. An additional 100nF ceramic capacitor should also be connected between the two IN pins and DGND, pin 6                                                |  |  |  |

| 6, 13, EP1 | DGND   | Exposed Pad 1 Digital Ground, DGND. The exposed thermal pad (EP1) should be connected to board ground plane and pins 6 and 13. The ground plane should include a large exposed copper pad under the package for thermal dissipation (see package outline).                                                                      |  |  |  |

| 7          | AIN    | nternal analog bias input. AIN supplies internal power to the AAT1160. Connect AIN to the input source oltage and bypass to AGND with a $0.1\mu F$ or greater capacitor. For additional noise rejection, connect the input power source through a $10\Omega$ or lower value resistor.                                           |  |  |  |

| 8          | LDO    | internal LDO bypass node. The output voltage of the internal LDO is bypassed at LDO. The internal circultry of the AAT1160 is powered from LDO. Do not draw external power from LDO. Bypass LDO to AGND with a $1\mu F$ or greater capacitor.                                                                                   |  |  |  |

| 9          | FB     | Output voltage feedback input. FB senses the output voltage for regulation control. For fixed output versions, connect FB to the output voltage. For adjustable versions, drive FB from the output voltage through a resistive voltage divider. The FB regulation threshold is 0.6V.                                            |  |  |  |

| 10         | COMP   | Control compensation node. Connect a series RC network from COMP to AGND, R = 50k and C = 150pF.                                                                                                                                                                                                                                |  |  |  |

| 11         | AGND   | Analog signal ground. Connect AGND to PGND at a single point as close to the IC as possible.                                                                                                                                                                                                                                    |  |  |  |

| 14         | SYNC   | Frequency select and synchronization input. Drive SYNC with a 500kHz to 1.6MHz signal to synchronize the AAT1160 switching frequency to that signal. The Sync pin is also a mode select input. Drive SYNC high or connect to the LDO pin for low-noise forced PWM mode. Drive SYNC low for high-efficiency PWM/Light Load mode. |  |  |  |

| 15         | EN     | Active high enable input. Drive EN high to turn on the AAT1160; drive it low to turn it off. For automatic startup, connect EN to IN through a $4.7 \mathrm{k}\Omega$ resistor. EN must be biased high, biased low, or driven to a logic level by an external source. Do not let the EN pin float when the device is powered.   |  |  |  |

| 16         | PGND   | Power ground. Connect AGND to PGND at a single point as close to the IC as possible.                                                                                                                                                                                                                                            |  |  |  |

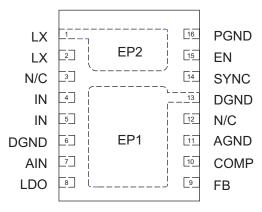

# **Pin Configuration**

TDFN34-16 (Top View)

SwitchReg<sup>™</sup>

## 12V, 3A Step-Down DC/DC Converter

# Absolute Maximum Ratings<sup>1</sup>

| Symbol                             | Description                          | Value                    | Units |

|------------------------------------|--------------------------------------|--------------------------|-------|

| V <sub>IN</sub> , V <sub>AIN</sub> | Input Voltage                        | -0.3 to 14               | V     |

| $V_{LX}$                           | LX to GND Voltage                    | $-0.3$ to $V_{IN} + 0.3$ | V     |

| $V_{FB}$                           | FB to GND Voltage                    | $-0.3$ to $V_{IN} + 0.3$ | V     |

| V <sub>EN</sub>                    | EN to GND Voltage                    | $-0.3$ to $V_{IN} + 0.3$ | V     |

| $V_{SYNC}$                         | SYNC to GND Voltage                  | -0.3 to 6.5              | V     |

| T <sub>J</sub>                     | Operating Junction Temperature Range | -40 to 150               | °C    |

### Thermal Information<sup>2</sup>

| Symbol                | Description                            | Value | Units |

|-----------------------|----------------------------------------|-------|-------|

| P <sub>D</sub>        | Maximum Power Dissipation <sup>3</sup> | 2.7   | W     |

| $\theta_{	exttt{JA}}$ | Thermal Resistance                     | 37    | °C/W  |

<sup>1.</sup> Stresses above those listed in Absolute Maximum Ratings may cause permanent damage to the device. Functional operation at conditions other than the operating conditions specified is not implied. Only one Absolute Maximum Rating should be applied at any one time.

<sup>2.</sup> Mounted on an FR4 board.

<sup>3.</sup> Derate 2.7mW/°C above 25°C.

### 12V, 3A Step-Down DC/DC Converter

### **Electrical Characteristics<sup>1</sup>**

$4.0V < V_{IN} < 13.2V$ .  $C_{IN} = C_{OUT} = 22 \mu F$ ;  $L = 2.2 \mu H$  or  $3.8 \mu H$ ,  $T_A = -40 ^{\circ}C$  to  $+85 ^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = 25 ^{\circ}C$ .

| Symbol                               | escription Conditions                           |                                             | Min                                | Тур  | Max   | Units                   |     |

|--------------------------------------|-------------------------------------------------|---------------------------------------------|------------------------------------|------|-------|-------------------------|-----|

| $V_{IN}$                             | Input Voltage Range                             |                                             |                                    | 4.0  |       | 13.2                    | V   |

|                                      | Toront Harden Valtage Legiscot                  | Rising                                      |                                    |      |       | 4.0                     | V   |

| $V_{\text{UVLO}}$                    | Input Under-Voltage Lockout                     | Hysteresis                                  |                                    |      | 0.3   |                         | V   |

| $I_{Q}$                              | Supply Current                                  | No Load                                     |                                    |      | 150   | 300                     | μΑ  |

| I <sub>SHDN</sub>                    | Shutdown Current                                | $V_{EN} = GND$                              |                                    |      |       | 1                       | μΑ  |

| $V_{OUT}$                            | Output Voltage Range                            |                                             |                                    | 0.6  |       | 0.94<br>V <sub>IN</sub> | V   |

| V <sub>out</sub>                     | Output Voltage Accuracy                         | $I_{OUT} = 0A \text{ to } 3$                | 3A                                 | -2.5 |       | 2.5                     | %   |

| $\Delta V_{LINEREG} / \Delta V_{IN}$ | Line Regulation                                 | $V_{IN} = 4.5V$ to                          | 13.2V                              |      | 0.023 | 0.100                   | %/V |

| $\Delta V_{LOADREG}$                 | Load Regulation                                 | $V_{IN} = 12V$ , $V_{OI}$                   | $_{UT}$ = 5V, $I_{OUT}$ = 0A to 3A |      | 0.4   |                         | %   |

| $V_{FB}$                             | Feedback Reference Voltage (adjustable version) | No Load, T <sub>A</sub> =                   | : 25°C                             | 0.59 | 0.60  | 0.61                    | V   |

| т                                    | FB Leakage Current                              | V = 1.2V                                    | Adjustable Version                 |      |       | 0.2                     |     |

| $I_{FBLEAK}$                         |                                                 | $V_{OUT} = 1.2V$                            | Fixed Version                      |      | 2     |                         | μΑ  |

| Fosc                                 | PWM Oscillator Frequency                        |                                             |                                    | 0.6  | 0.8   | 1                       | MHz |

| F <sub>SYNC</sub>                    | External Clock Frequency Range                  | CMOS Logic C                                | Clock Signal on SYNC Pin           | 0.5  |       | 1.6                     | MHz |

| Ts                                   | Start-Up Time                                   | $I_{OUT} = 3A, V_{OU}$                      | <sub>JT</sub> = 5V                 |      | 2     |                         | ms  |

|                                      | Foldback Frequency                              |                                             |                                    |      | 200   |                         | kHz |

| DC                                   | Maximum Duty Cycle                              |                                             |                                    |      |       | 94                      | %   |

| T <sub>ON</sub>                      | Minimum Turn-On Time                            |                                             |                                    |      | 100   |                         | ns  |

| $T_{SS}$                             | Soft-Start Time                                 |                                             |                                    |      | 2     |                         | ms  |

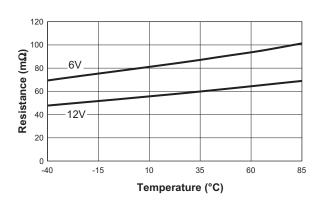

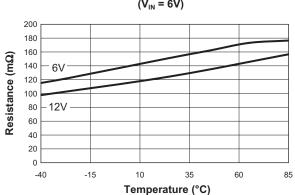

| D                                    | R <sub>DS(ON)H</sub> P-Channel On Resistance    |                                             | $V_{IN} = 12V$                     |      | 0.12  |                         | Ω   |

| R <sub>DS(ON)H</sub>                 | F-Chainer On Resistance                         | $V_{IN} = 6V$                               |                                    |      | 0.15  |                         | 22  |

| R <sub>DS(ON)L</sub>                 | N-Channel On Resistance                         |                                             |                                    |      | 0.06  |                         | Ω   |

| NDS(ON)L                             | N-Chainlei On Resistance                        |                                             |                                    |      | 0.08  |                         | 22  |

| η                                    | Efficiency                                      | $V_{IN} = 12V, V_{OUT} = 5V, I_{OUT} = 3A$  |                                    |      | 90    |                         | %   |

| $I_{LIM}$                            | PMOS Current Limit                              |                                             |                                    | 4.0  | 6.0   |                         | Α   |

| $I_{LXLEAK}$                         | LX Leakage Current                              | $V_{IN} = 13.2V$ , $V_{LX} = 0$ to $V_{IN}$ |                                    |      |       | 1                       | μΑ  |

| T <sub>SD</sub>                      | Over-Temperature Shutdown Threshold             |                                             |                                    | 140  |       | °C                      |     |

| T <sub>HYS</sub>                     | Over-Temperature Shutdown Hysteresis            |                                             |                                    | 25   |       | °C                      |     |

| $V_{ILEN}$                           | EN Logic Low Input Threshold                    | w Input Threshold                           |                                    |      |       | 0.4                     | V   |

| $V_{IHEN}$                           | EN Logic High Input Threshold                   |                                             |                                    | 1.4  |       |                         | V   |

| $V_{ILSYNC}$                         | SYNC Logic Low Input Threshold                  |                                             |                                    |      |       | 0.4                     | V   |

| $V_{IHSYNC}$                         | SYNC Logic High Input Threshold                 |                                             |                                    | 1.62 |       |                         | V   |

| ${ m I}_{\sf EN}$                    | EN Input Current                                | $V_{EN} = 0V, V_{EN} = 13.2V$               |                                    | -1.0 |       | 1.0                     | μΑ  |

<sup>1.</sup> The AAT1160 is guaranteed to meet performance specifications over the -40°C to +85°C operating temperature range and is assured by design, characterization, and correlation with statistical process controls.

### 12V, 3A Step-Down DC/DC Converter

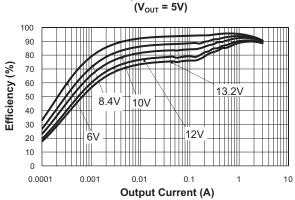

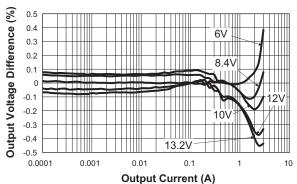

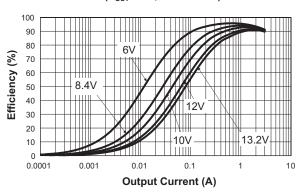

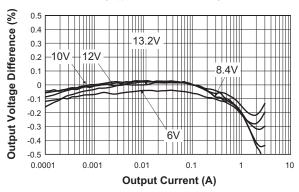

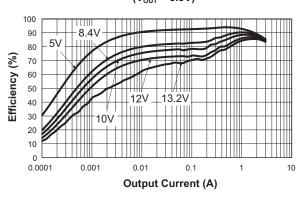

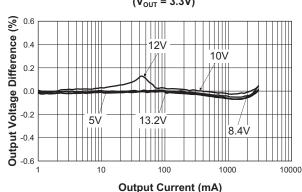

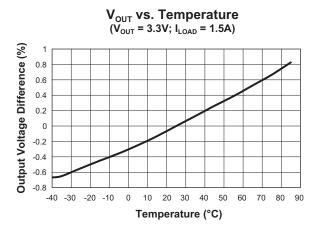

### **Typical Characteristics**

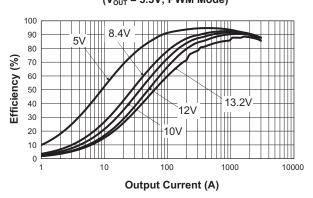

Efficiency vs. Load Current

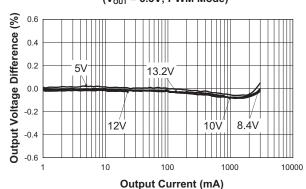

Load Regulation (V<sub>OUT</sub> = 5V)

Efficiency vs. Load Current (V<sub>OUT</sub> = 5V; PWM Mode)

Load Regulation (V<sub>OUT</sub> = 5V; PWM Mode)

Efficiency vs. Load Current (V<sub>OUT</sub> = 3.3V)

Load Regulation (V<sub>OUT</sub> = 3.3V)

# 12V, 3A Step-Down DC/DC Converter

## **Typical Characteristics**

Efficiency vs. Load Current (V<sub>OUT</sub> = 3.3V; PWM Mode)

Load Regulation (V<sub>OUT</sub> = 3.3V; PWM Mode)

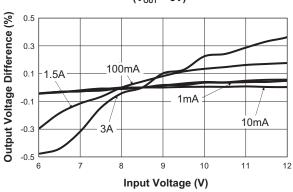

Line Regulation (V<sub>ouт</sub> = 5V)

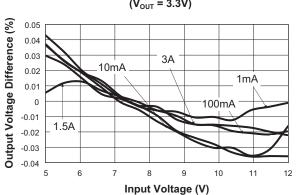

Line Regulation (V<sub>OUT</sub> = 3.3V)

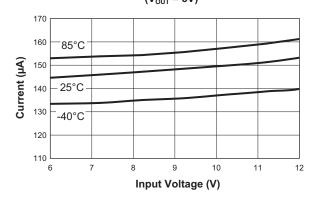

# Switching Current vs. Input Voltage $(V_{OUT} = 5V)$

#### **Switching Current vs. Temperature**

# 12V, 3A Step-Down DC/DC Converter

### **Typical Characteristics**

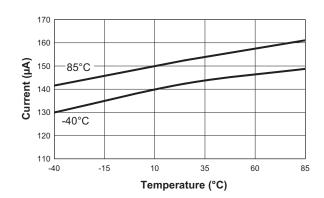

#### N-Channel R<sub>DS(ON)</sub> vs. Temperature

# P-Channel $R_{DS(ON)}$ vs. Temperature $(V_{IN} = 6V)$

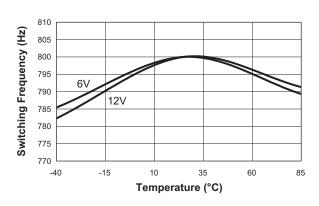

#### Switching Frequency vs. Temperature

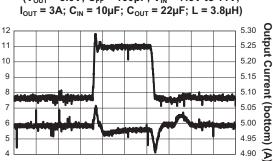

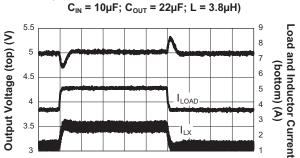

**Line Transient**  $(V_{OUT} = 5.0V; C_{FF} = 100pF; V_{IN} = 7.6V \text{ to } 11V;$

Input Voltage (top) (V)

11

Time (100µs/div)

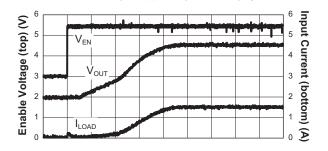

#### Start-Up Time $(V_{OUT} = 5.0V; C_{FF} = 100pF; R_{LOAD} = 1.67\Omega;$ $C_{IN} = 10\mu F; C_{OUT} = 22\mu F; L = 3.8\mu H)$

Time (500µs/div)

Time (100µs/div)

5.05

5.00 4.95

### 12V, 3A Step-Down DC/DC Converter

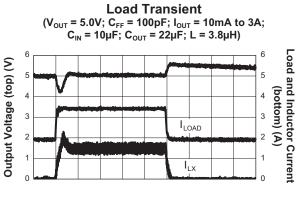

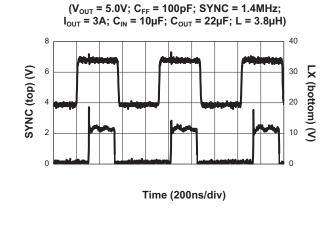

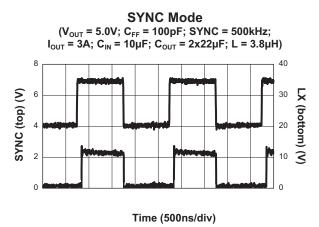

**SYNC Mode**

### **Typical Characteristics**

Time (100µs/div)

### 12V, 3A Step-Down DC/DC Converter

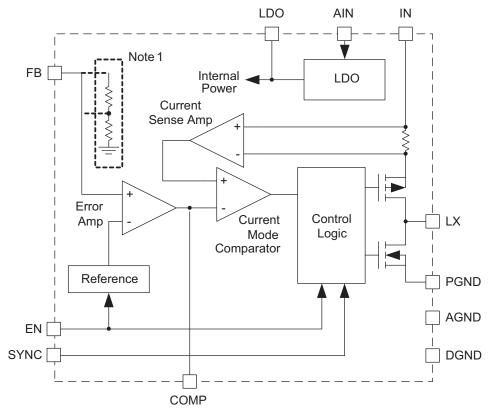

### **Functional Block Diagram**

Note 1: For fixed output voltage versions, FB is connected to the error amplifier through the resistive voltage divider shown.

### **Functional Description**

The AAT1160 is a current-mode step-down DC/DC converter that operates over a wide 4V to 13.2V input voltage range and is capable of supplying up to 3A to the load with the output voltage regulated as low as 0.6V. Both the P-channel power switch and N-channel synchronous rectifier are internal, reducing the number of external components required. The output voltage is adjusted by an external resistor divider; fixed output voltage versions are available upon request. The regulation system is externally compensated, allowing the circuit to be optimized for each application. The AAT1160 includes cycle-by-cycle current limiting, frequency fold-back for improved short-circuit performance, and thermal overload protection to prevent damage in the event of an external fault condition.

#### **Control Loop**

The AAT1160 regulates the output voltage using constant frequency current mode control. The AAT1160 monitors current through the high-side P-channel MOSFET and uses that signal to regulate the output voltage. This provides improved transient response and eases compensation. Internal slope compensation is included to ensure the current "inside loop" stability.

High efficiency is maintained under light load conditions by automatically switching to variable frequency Light Load control. In this condition, transition losses are reduced by operating at a lower frequency at light loads.

### 12V, 3A Step-Down DC/DC Converter

#### **Short-Circuit Protection**

The AAT1160 uses a cycle-by-cycle current limit to protect itself and the load from an external fault condition. When the inductor current reaches the internally set 6.0A current limit, the P-channel MOSFET switch turns off and the N-channel synchronous rectifier is turned on, limiting the inductor and the load current.

During an overload condition, when the output voltage drops below 25% of the regulation voltage (0.15V at FB), the AAT1160 switching frequency drops by a factor of 4. This gives the inductor current ample time to reset during the off time to prevent the inductor current from rising uncontrolled in a short-circuit condition.

#### **Thermal Protection**

The AAT1160 includes thermal protection that disables the regulator when the die temperature reaches 140°C. It automatically restarts when the temperature decreases by 25°C or more.

#### **Frequency Synchronization**

The AAT1160 operates at a fixed 800kHz switching frequency, or it can be synchronized to an external signal. Synchronize switching to an external signal between 500kHz and 1.6MHz by driving SYNC with that signal. In this mode, the rising edge of the signal at SYNC turns on the P-channel switch. When changing switching frequency, the external components  $C_{\text{IN}}$ ,  $C_{\text{OUT}}$  and L must be changed according to the component equations. The external clock duty cycle is limited to a 30% to 90% range.

#### **PWM or Light Load Mode**

The device can be set to operate in forced Pulse Width Modulation (PWM) mode to filter or set the switching noise to a desired frequency by connecting the SYNC to a high logic level. Alternately, a combination PWM/LL (Light Load) mode for improved light load efficiency can be set by connecting the SYNC pin to GND or a low logic level. When connecting SYNC to an external clock signal, the device is always in forced PWM mode.

# **Applications Information**

#### **Setting the Output Voltage**

Figure 1 shows the basic application circuit for the AAT1160 and output setting resistors. Resistors R3 and R6 program the output to regulate at a voltage higher than 0.6V. To limit the bias current required for the external feedback resistor string while maintaining good noise immunity, the minimum suggested value for R6 is  $5.9 \mathrm{k}\Omega$ . Although a larger value will further reduce quiescent current, it will also increase the impedance of the feedback node, making it more sensitive to external noise and interference. Table 1 summarizes the resistor values for various output voltages with R6 set to either  $5.9 \mathrm{k}\Omega$  for good noise immunity or  $59 \mathrm{k}\Omega$  for reduced no load input current.

Figure 1: Typical Application Circuit.

The adjustable feedback resistors, combined with an external feed forward capacitor (C1 in Figure 1), deliver enhanced transient response for extreme pulsed load applications. The addition of the feed forward capacitor typically requires a larger output capacitor C3/C4 for stability. Larger C3/C4 values reduce overshoot and undershoot during startup and load changes. However, do not exceed 470pF to maintain stable operation.

The external resistors set the output voltage according to the following equation:

$$V_{OUT} = 0.6V \left( 1 + \frac{R3}{R6} \right)$$

or

$$R3 = \left(\frac{V_{OUT}}{V_{REF}} - 1\right) \cdot R6$$

SwitchReg<sup>™</sup>

### 12V, 3A Step-Down DC/DC Converter

Table 1 shows the resistor selection for different output voltage settings.

| V <sub>оит</sub> (V) | R6 = 5.9kΩ<br>R3 (kΩ) | R6 = 59kΩ<br>R3 (kΩ) |  |  |

|----------------------|-----------------------|----------------------|--|--|

| 0.8                  | 1.96                  | 19.6                 |  |  |

| 0.9                  | 2.94                  | 29.4                 |  |  |

| 1.0                  | 3.92                  | 39.2                 |  |  |

| 1.1                  | 4.99                  | 49.9                 |  |  |

| 1.2                  | 5.90                  | 59.0                 |  |  |

| 1.3                  | 6.81                  | 68.1                 |  |  |

| 1.4                  | 7.87                  | 78.7                 |  |  |

| 1.5                  | 8.87                  | 88.7                 |  |  |

| 1.8                  | 11.8                  | 118                  |  |  |

| 1.85                 | 12.4                  | 124                  |  |  |

| 2.0                  | 13.7                  | 137                  |  |  |

| 2.5                  | 18.7                  | 187                  |  |  |

| 3.3                  | 26.7                  | 267                  |  |  |

| 5.0                  | 43.2                  | 432                  |  |  |

Table 1: Resistor Selection for Different Output Voltage Settings. Standard 1% Resistors are Substituted for Calculated Values.

#### **Inductor Selection**

For most designs, the AAT1160 operates with inductors of  $2\mu H$  to  $4.7\mu H$ . Low inductance values are physically smaller, but require faster switching, which results in some efficiency loss. The inductor value can be derived from the following equation:

$$L1 = \frac{V_{\text{OUT}} \cdot (V_{\text{IN}} - V_{\text{OUT}})}{V_{\text{IN}} \cdot \Delta I_{\text{L}} \cdot F_{\text{OSC}}}$$

Where  $\Delta I_L$  is inductor ripple current. Large value inductors lower ripple current and small value inductors result in high ripple currents. Choose inductor ripple current approximately 32% of the maximum load current 3A, or  $\Delta I_L = 959$ mA. For output voltages above 3.3V, the mini-

mum recommended inductor is  $3.8\mu H$ . For 3.3V and below, use a 2 to  $2.2\mu H$  inductor. For optimum voltage-positioning load transients, choose an inductor with DC series resistance in the  $15m\Omega$  to  $20m\Omega$  range. For higher efficiency at heavy loads (above 1A), or minimal load regulation (but some transient overshoot), the resistance should be kept below  $18m\Omega$ . The DC current rating of the inductor should be at least equal to the maximum load current plus half the ripple current to prevent core saturation (3A + 526mA). Table 2 lists some typical surface mount inductors that meet target applications for the AAT1160.

Manufacturer's specifications list both the inductor DC current rating, which is a thermal limitation, and the peak current rating, which is determined by the saturation characteristics. The inductor should not show any appreciable saturation under normal load conditions. Some inductors may meet the peak and average current ratings yet result in excessive losses due to a high DCR. Always consider the losses associated with the DCR and its effect on the total converter efficiency when selecting an inductor. For example, the 3.7µH CDR7D43 series inductor selected from Sumida has an 18.9m $\Omega$  DCR and a 4.3ADC current rating. At full load, the inductor DC loss is 170mW which gives only a 1.13% loss in efficiency for a 3A, 5V output.

#### **Input Capacitor Selection**

The input capacitor reduces the surge current drawn from the input and switching noise from the device. The input capacitor impedance at the switching frequency shall be less than the input source impedance to prevent high frequency switching current passing to the input. A low ESR input capacitor sized for maximum RMS current must be used. Ceramic capacitors with X5R or X7R dielectrics are highly recommended because of their low ESR and small temperature coefficients. A 22µF ceramic capacitor is sufficient for most applications.

| Manufacturer | Part Number       | L (µH) | Max DCR<br>(mΩ) | Rated DC<br>Current (A) | Size WxLxH<br>(mm) |

|--------------|-------------------|--------|-----------------|-------------------------|--------------------|

| Sumida       | CDRH103RNP-2R2N   | 2.2    | 16.9            | 5.10                    | 10.3x10.5x3.1      |

| Sumida       | CDR7D43MNNP-3R7NC | 3.7    | 18.9            | 4.3                     | 7.6x7.6x4.5        |

| Coilcraft    | MSS1038-382NL     | 3.8    | 13              | 4.25                    | 10.2x7.7x3.8       |

**Table 2: Typical Surface Mount Inductors.**

To estimate the required input capacitor size, determine the acceptable input ripple level ( $V_{PP}$ ) and solve for C. The calculated value varies with input voltage and is a maximum when  $V_{\rm IN}$  is double the output voltage.

$$C_{IN} = \frac{\frac{V_{O}}{V_{IN}} \cdot \left(1 - \frac{V_{O}}{V_{IN}}\right)}{\left(\frac{V_{PP}}{I_{O}} - ESR\right) \cdot F_{OSC}}$$

$$\frac{V_O}{V_{IN}} \cdot \left(1 - \frac{V_O}{V_{IN}}\right) = \frac{1}{4}$$

for  $V_{IN} = 2 \cdot V_O$

$$C_{IN(MIN)} = \frac{1}{\left(\frac{V_{PP}}{I_{O}} - ESR\right) \cdot 4 \cdot F_{OSC}}$$

Always examine the ceramic capacitor DC voltage coefficient characteristics when selecting the proper value. For example, the capacitance of a  $10\mu\text{F}$ , 16V, X5R ceramic capacitor with 12V DC applied is actually about  $8.5\mu\text{F}$ .

The maximum input capacitor RMS current is:

$$I_{\text{RMS}} = I_{\text{O}} \cdot \sqrt{\frac{V_{\text{O}}}{V_{\text{IN}}} \cdot \left(1 - \frac{V_{\text{O}}}{V_{\text{IN}}}\right)}$$

The input capacitor RMS ripple current varies with the input and output voltage and will always be less than or equal to half of the total DC load current:

$$\sqrt{\frac{V_0}{V_{IN}} \cdot \left(1 - \frac{V_0}{V_{IN}}\right)} = \sqrt{D \cdot (1 - D)} = \sqrt{0.5^2} = \frac{1}{2}$$

for  $V_{IN} = 2 \cdot V_{O}$

$$I_{RMS(MAX)} = \frac{I_0}{2}$$

The term  $\frac{V_O}{V_{IN}} \left(1 - \frac{V_O}{V_{IN}}\right)$  appears in both the input voltage ripple and input capacitor RMS current equations and is at maximum when  $V_O$  is twice  $V_{IN}$ . This is why the input voltage ripple and the input capacitor RMS current ripple are a maximum at 50% duty cycle. The input capacitor provides a low impedance loop for the edges of pulsed current drawn by the AAT1160. Low ESR/ESL X7R and X5R ceramic capacitors are ideal for this function. To minimize stray inductance, the capacitor should be placed as closely as possible to the IC. This keeps the

### 12V, 3A Step-Down DC/DC Converter

high frequency content of the input current localized, minimizing EMI and input voltage ripple. The proper placement of the input capacitor (C6) can be seen in the evaluation board layout in Figure 3. Additional noise filtering for proper operation is accomplished by adding a small 0.1µF capacitor on the IN pins (C2).

A laboratory test set-up typically consists of two long wires running from the bench power supply to the evaluation board input voltage pins. The inductance of these wires, along with the low-ESR ceramic input capacitor, can create a high Q network that may affect converter performance. This problem often becomes apparent in the form of excessive ringing in the output voltage during load transients. Errors in the loop phase and gain measurements can also result. Since the inductance of a short PCB trace feeding the input voltage is significantly lower than the power leads from the bench power supply, most applications do not exhibit this problem. In applications where the input power source lead inductance cannot be reduced to a level that does not affect the converter performance, a high ESR tantalum or aluminum electrolytic should be placed in parallel with the low ESR, ESL bypass ceramic. This dampens the high Q network and stabilizes the system.

### **Output Capacitor Selection**

The output capacitor is required to keep the output voltage ripple small and to ensure regulation loop stability. The output capacitor must have low impedance at the switching frequency. Ceramic capacitors with X5R or X7R dielectrics are recommended due to their low ESR and high ripple current. The output ripple  $V_{\text{OUT}}$  is determined by:

$$\Delta V_{\text{OUT}} \leq \frac{V_{\text{OUT}} \cdot \left(V_{\text{IN}} - V_{\text{OUT}}\right)}{V_{\text{IN}} \cdot F_{\text{OSC}} \cdot L} \cdot \left(\text{ESR} + \frac{1}{8 \cdot F_{\text{OSC}} \cdot C_{\text{OUT}}}\right)$$

The output capacitor limits the output ripple and provides holdup during large load transitions. A  $10\mu F$  to  $47\mu F$  X5R or X7R ceramic capacitor typically provides sufficient bulk capacitance to stabilize the output during large load transitions and has the ESR and ESL characteristics necessary for low output ripple. The output voltage droop due to a load transient is dominated by the capacitance of the ceramic output capacitor. During a step increase in load current, the ceramic output capacitor alone supplies the load current until the loop responds. Within two or three switching cycles, the loop responds and the inductor current increases to match

the load current demand. The relationship of the output voltage droop during the three switching cycles to the output capacitance can be estimated by:

$$C_{OUT} = \frac{3 \cdot \Delta I_{LOAD}}{V_{DROOP} \cdot F_{OSC}}$$

Once the average inductor current increases to the DC load level, the output voltage recovers. The above equation establishes a limit on the minimum value for the output capacitor with respect to load transients. The internal voltage loop compensation also limits the minimum output capacitor value to 22µF. This is due to its effect on the loop crossover frequency (bandwidth), phase margin, and gain margin. Increased output capacitance will reduce the crossover frequency with greater phase margin.

The maximum output capacitor RMS ripple current is given by:

$$I_{RMS(MAX)} = \frac{1}{2 \cdot \sqrt{3}} \cdot \frac{V_{OUT} \cdot (V_{IN(MAX)} - V_{OUT})}{L \cdot F_{OSC} \cdot V_{IN(MAX)}}$$

Dissipation due to the RMS current in the ceramic output capacitor ESR is typically minimal, resulting in less than a few degrees rise in hot-spot temperature.

### **Compensation**

The AAT1160 step-down converter uses peak current mode control with slope compensation scheme to maintain stability with lower value inductors for duty cycles greater than 50%. The regulation feedback loop in the IC is stabilized by the components connected to the COMP pin, as shown in Figure 1.

To optimize the compensation components, the following equations can be used. The compensation resistor  $R_{\text{COMP}}$  (R5) is calculated using the following equation:

$$R_{COMP} (R5) = \frac{2\pi V_{OUT} \cdot C_{OUT} \cdot F_{OSC}}{10G_{EA} \cdot G_{COMP} \cdot V_{FB}}$$

Where  $V_{FB}=0.6V,\ G_{COMP}=40.1734$  and  $G_{EA}=9.091\cdot 10^{-5}.$

### 12V, 3A Step-Down DC/DC Converter

$F_{OSC}$  is the switching frequency and  $C_{OUT}$  is based on the output capacitor calculation. The  $C_{COMP}$  value can be determined from the following equation:

$$C_{\text{COMP}}\left(\text{C7}\right) = \frac{4}{2\pi R_{\text{COMP}}\left(\text{R5}\right) \cdot \left(\frac{F_{\text{OSC}}}{10}\right)}$$

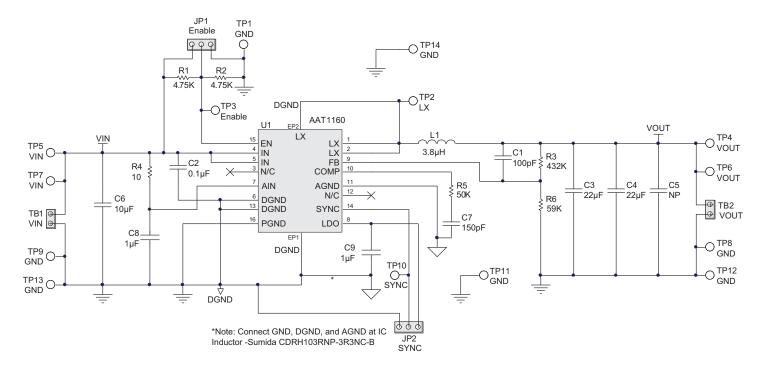

#### **Layout Guidance**

Figure 2 is the schematic for the evaluation board. When laying out the PC board, the following layout guideline should be followed to ensure proper operation of the AAT1160:

- Exposed pad EP1 must be reliably soldered to PGND/ DGND/AGND. The exposed thermal pad should be connected to board ground plane and pins 6, 11, 13, and 16. The ground plane should include a large exposed copper pad under the package for thermal dissipation.

- The power traces, including GND traces, the LX traces and the VIN trace should be kept short, direct and wide to allow large current flow. The L1 connection to the LX pins should be as short as possible. Use several via pads when routing between layers.

- 3. Exposed pad pin EP2 must be reliably soldered to the LX pins 1 and 2. The exposed thermal pad should be connected to the board LX connection and the inductor L1 and also pins 1 and 2. The LX plane should include a large exposed copper pad under the package for thermal dissipation.

- 4. The input capacitors (C2 and C6) should be connected as close as possible to IN (Pins 4 and 5) and DGND (Pin 6) to get good power filtering.

- 5. Keep the switching node LX away from the sensitive FB node.

- 6. The feedback trace for the FB pin should be separate from any power trace and connected as closely as possible to the load point. Sensing along a highcurrent load trace will degrade DC load regulation. The feedback resistors should be placed as close as possible to the FB pin (Pin 9) to minimize the length of the high impedance feedback trace.

- 7. The output capacitors C3, 4, and 5 and L1 should be connected as close as possible and there should not be any signal lines under the inductor.

- The resistance of the trace from the load return to the PGND (Pin 16) should be kept to a minimum. This will help to minimize any error in DC regulation due to differences in the potential of the internal signal ground and the power ground.

SwitchReg<sup>™</sup>

# 12V, 3A Step-Down DC/DC Converter

Figure 2: AAT1160 Evaluation Board Schematic.

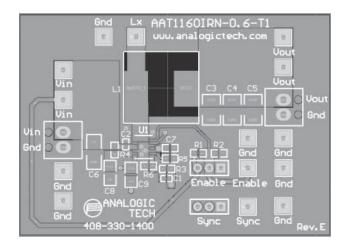

Figure 3: AAT1160 Evaluation Board Component Side Layout.

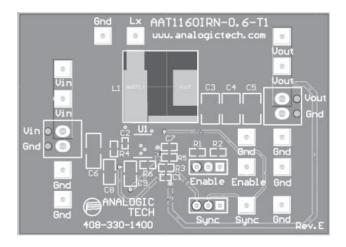

Figure 4: AAT1160 Evaluation Board Solder Side Layout.

### 12V, 3A Step-Down DC/DC Converter

### **Design Example**

### **Specifications**

$V_{OUT}$  5V @ 3A, Pulsed Load  $\Delta I_{LOAD} = 3A$

$V_{IN}$  12V nominal  $F_{OSC}$  800kHz

T<sub>AMB</sub> 85°C in TDFN34-16 Package

#### **Output Inductor**

L1 =

$$\frac{V_{OUT} \cdot (V_{IN} - V_{OUT})}{V_{IN} \cdot \Delta I_L \cdot F_{OSC}}$$

= 3.8µH; see Table 2.

$$\Delta I_L = 0.32 \cdot I_{LOAD}$$

For Coilcraft inductor MSS1038 3.8 $\mu$ H DCR = 13 $m\Omega$  max.

$$\Delta I_1 = \frac{V_{OUT}}{L1 \cdot F_{OSC}} \cdot \left(1 - \frac{V_{O1}}{V_{IN}}\right) = \frac{5V}{3.8 \mu H \cdot 800 kHz} \cdot \left(1 - \frac{5V}{12V}\right) = 959 mA$$

$$I_{PK1} = I_{LOAD} + \frac{\Delta I_1}{2} = 3A + 0.479A = 3.48A$$

$$\mathsf{P}_{\mathsf{L1}} = \mathsf{I}_{\mathsf{LOAD}}^{\phantom{\mathsf{DOAD}}2} \cdot \mathsf{DCR} = 3\mathsf{A}^2 \cdot 13\mathsf{m}\Omega = 117\mathsf{mW}$$

### **Output Capacitor**

$$V_{DROOP} = 0.2V$$

$$C_{\text{OUT}} = \frac{3 \cdot \Delta I_{\text{LOAD}}}{V_{\text{DROOP}} \cdot F_{\text{OSC}}} = \frac{3 \cdot 3A}{0.2V \cdot 800 \text{kHz}} = 56 \mu \text{F}; \text{ use two } 22 \mu \text{F}$$

$$I_{\text{RMS(MAX)}} = \frac{1}{2 \cdot \sqrt{3}} \cdot \frac{(V_{\text{OUT}}) \cdot (V_{\text{IN(MAX)}} - V_{\text{OUT}})}{L \cdot F_{\text{OSC}} \cdot V_{\text{IN(MAX)}}} = \frac{1}{2 \cdot \sqrt{3}} \cdot \frac{5 \text{V} \cdot (12 \text{V} - 5 \text{V})}{3.8 \mu \text{H} \cdot 800 \text{kHz} \cdot 12 \text{V}} = 277 \text{mArms}$$

$$P_{esr} = esr \cdot I_{RMS}^{2} = 5m\Omega \cdot (277mA)^{2} = 384\mu W$$

### **Input Capacitor**

Input Ripple  $V_{PP} = 50 \text{mV}$

$$C_{\text{IN}} = \frac{1}{\left(\frac{V_{\text{PP}}}{I_{\text{LOAD}}} - \text{ESR}\right) \cdot 4 \cdot F_{\text{OSC}}} = \frac{1}{\left(\frac{50 \text{mV}}{3 \text{A}} - 5 \text{m}\Omega\right) \cdot 4 \cdot 800 \text{kHz}} = 26 \mu \text{F}; \text{ use } 22 \mu \text{F}$$

$$I_{RMS(MAX)} = \frac{I_{LOAD}}{2} = 1.5Arms$$

$$P = esr \cdot I_{RMS}^2 = 5m\Omega \cdot (1.5A)^2 = 11.25mW$$

### 12V, 3A Step-Down DC/DC Converter

#### **AAT1160 Losses**

Total losses can be estimated by calculating the dropout ( $V_{IN} = V_O$ ) losses where the power MOSFET  $R_{DS(ON)}$  will be at the maximum value. All values assume an 85°C ambient temperature and a 140°C junction temperature with the TDFN 37°C/W package.

$$\mathsf{P}_{\mathsf{LOSS}} = \mathsf{I}_{\mathsf{LOAD}}^2 \cdot \mathsf{R}_{\mathsf{DS}(\mathsf{ON})\mathsf{H}} = 3\mathsf{A}^2 \cdot 0.12\Omega = 1.08\mathsf{W}$$

$$T_{J(MAX)} = T_{AMB} + \Theta_{JA} \cdot P_{LOSS} = 85^{\circ}C + (37^{\circ}C/W) \cdot 1.08W = 125^{\circ}C$$

The total losses are also investigated at the nominal input voltage (12V). The simplified version of the  $R_{DS(ON)}$  losses assumes that the N-channel and P-channel  $R_{DS(ON)}$  are equal.

$$\mathsf{P}_{\mathsf{TOTAL}} = \mathsf{I}_{\mathsf{LOAD}}^2 \cdot \mathsf{R}_{\mathsf{DS}(\mathsf{ON})} + [(\mathsf{t}_{\mathsf{sw}} \cdot \mathsf{F}_{\mathsf{OSC}} \cdot \mathsf{I}_{\mathsf{LOAD}} + \mathsf{I}_{\mathsf{Q}}) \cdot \mathsf{V}_{\mathsf{IN}}]$$

=

$$3A^2 \cdot 100m\Omega + [(5ns \cdot 800kHz \cdot 3A + 150\mu A) \cdot 12V] = 1.0458W$$

$$T_{J(MAX)} = T_{AMB} + \Theta_{JA} \cdot P_{LOSS} = 85^{\circ}C + (37^{\circ}C/W) \cdot 1.0458W = 124^{\circ}C$$

### 12V, 3A Step-Down DC/DC Converter

### **Ordering Information**

| Package   | Marking <sup>1</sup> | Part Number (Tape and Reel) <sup>2</sup> |

|-----------|----------------------|------------------------------------------|

| TDFN34-16 | XAXYY                | AAT1160IRN-0.6-T1                        |

All AnalogicTech products are offered in Pb-free packaging. The term "Pb-free" means semiconductor products that are in compliance with current RoHS standards, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. For more information, please visit our website at http://www.analogictech.com/pbfree.

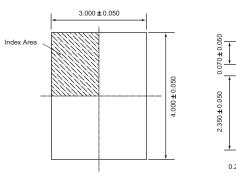

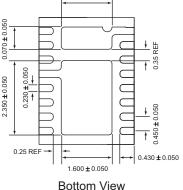

### **Package Information**

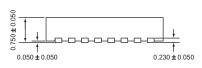

#### **TDFN34-16**

1.600 ± 0.050

Top View

Side View

All dimensions in millimeters.

- 1. XYY = assembly and date code.

- 2. Sample stock is generally held on part numbers listed in **BOLD**.

- The leadless package family, which includes QFN, TQFN, DFN, TDFN and STDFN, has exposed copper (unplated) at the end of the lead terminals due to the manufacturing process. A solder fillet at the exposed copper edge cannot be guaranteed and is not required to ensure a proper bottom solder connection.

#### Advanced Analogic Technologies, Inc.

3230 Scott Boulevard, Santa Clara, CA 95054 Phone (408) 737-4600 Fax (408) 737-4611

© Advanced Analogic Technologies, Inc.

© Advanced Analogic Technologies, Inc.

AnalogicTech cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in an AnalogicTech product. No circuit patent licenses, copyrights, mask work rights, or other intellectual property rights are implied. AnalogicTech reserves the right to make changes to their products or specifications or to discontinue any product or service without notice. Except as provided in AnalogicTech's terms and conditions of sale, AnalogicTech assumes no liability whatsoever, and AnalogicTech disclaims any express or implied warranty relating to the sale and/or use of AnalogicTech products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards. Testing and other quality control techniques are utilized to the extent AnalogicTech deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed. AnalogicTech and the AnalogicTech logo are trademarks of Advanced Analogic Technologies Incorporated. All other brand and product names appearing in this document are registered trademarks or trademarks of their respective holders