## SPDC12L00010

#### 10 A DC/DC converter module

Preliminary Data

#### **Features**

- MTBF 1 000 000 (T<sub>A</sub> = 25 °C)

- 10 A max output current

- Input voltage range from 1.8 V to 14 V

- Supply voltage range from 4.5 V to 14 V

- Fixed or adjustable output voltage down to 0.6 V

- Fixed frequency voltage mode control

- Adjustable switching frequency

- Soft-start and inhibit

- Selectable UVLO threshold (5 V or 12 V bus)

- Master/slave synchronization with 180° phase shift

- Pre-bias start-up capability

- Selectable source/sink or source only capability after soft-start

- Power Good output with programmable delay

- Over voltage protection with selectable latched/not-latched mode

- Thermal shut-down

- Operating temperature range -40 °C ÷ 85 °C

### **Applications**

- Laptop

- Blade servers

- RAID systems

- Network routers

- Cellular base stations

- Industrial equipment

- Test instrumentation

- Medical diagnostic equipment

- Points of load regulation

| Table 1 | Device   | summarv      |

|---------|----------|--------------|

| Iabic   | . Device | Sullilliai v |

| Order code   | Output voltage<br>[V] | Input voltage<br>[V] | •  |         | Notes                 |

|--------------|-----------------------|----------------------|----|---------|-----------------------|

| SPDC12L00010 | 0.6 ÷ 5               | 1.8 ÷ 14             | 40 | 70 ÷ 93 | Progr. output voltage |

Contents SPDC12L00010

## **Contents**

| 1 | Desc  | ription                                               | 4  |

|---|-------|-------------------------------------------------------|----|

| 2 | Pin s | ettings                                               | 5  |

|   | 2.1   | Pin connection and mechanical data (dimensions in mm) | 5  |

|   | 2.2   | Pin description                                       | 5  |

| 3 | Maxi  | mum ratings                                           | 7  |

|   | 3.1   | Absolute maximum ratings                              | 7  |

|   | 3.2   | Thermal data                                          | 7  |

|   | 3.3   | Thermal de-rating                                     | 8  |

| 4 | Elect | rical characteristics1                                | 1  |

| 5 | Appl  | ication information1                                  | 2  |

|   | 5.1   | Input voltage                                         | 12 |

|   | 5.2   | Auxiliary voltage                                     | 12 |

|   | 5.3   | Inhibit function 1                                    | 12 |

|   | 5.4   | Soft-start                                            | 13 |

|   | 5.5   | Multiple units synchronization                        | 13 |

|   | 5.6   | Power good signal and power good delay                | 14 |

|   | 5.7   | Oscillator setting                                    | 14 |

|   | 5.8   | Current sink-mode                                     | 14 |

|   | 5.9   | Under voltage lock out                                | 15 |

|   | 5.10  | Program setting                                       | 15 |

|   | 5.11  | Voltage sensing                                       | 15 |

|   | 5.12  | Output voltage programming                            | 16 |

|   | 5.13  | Additional loop compensation                          | 16 |

|   | 5.14  | Output over voltage protection                        | 17 |

|   | 5.15  | Current limitation                                    | 17 |

|   | 5.16  | Thermal shutdown                                      | 17 |

|   | 5.17  | Signal ground and power ground                        | 18 |

|   | 5.18  | Input capacitors                                      | 18 |

|   |       |                                                       |    |

| SPDC12L0 | 0010  | Con                 | tents |

|----------|-------|---------------------|-------|

|          | 5.19  | Output capacitors   | . 18  |

|          | 5.20  | Phase connection    | . 19  |

| 6        | Pack  | age mechanical data | . 20  |

|          | 6.1   | Soldering           | . 21  |

|          | 6.2   | PCB footprint       | . 22  |

| 7        | Revis | sion history        | . 23  |

**47/**

Description SPDC12L00010

### 1 Description

The ST SPDC12L00010 high density 10 A DC-DC converter is a complete step-down power supply. A single LGA package includes ST switching controller, power FETs, inductor and all the support components. SPDC12L00010 operates over a wide input voltage range of 1.8 V to 14 V, supporting an output range of 0.6 V to 5 V. High level of integration and synchronous rectification allows the SPDC12l00010 to deliver up to 10 A continuous current at up to 93% efficiency, without external heat sink or airflow.

The device is a complete stand alone surface mount power supply, that can be handled and assembled like a standard integrated circuit. Moreover its low profile design permits the SPDC12L00010 to be soldered onto the back side of a printed circuit board, freeing up valuable board space.

SPDC12L00010 is self protected against over voltage and short circuit conditions. A built in adjustable soft-start and inhibit guarantee correct functionality whatever the load is. Pre-bias start up capability is in place as well Power Good output with programmable delay to avoid false signals.

The device is packaged in a thermally enhanced, compact (15 x 15 mm) and low profile (3 mm) over molded land grid array (LGA) package, suitable for automated assembly by standard surface mount equipment. The SPDC12L00010 is Pb-Free and RoHS compliant.

SPDC12L00010 Pin settings

## 2 Pin settings

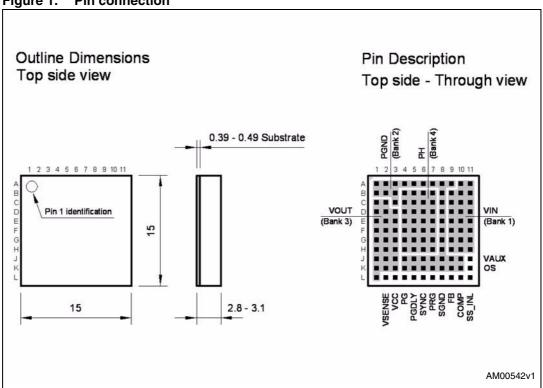

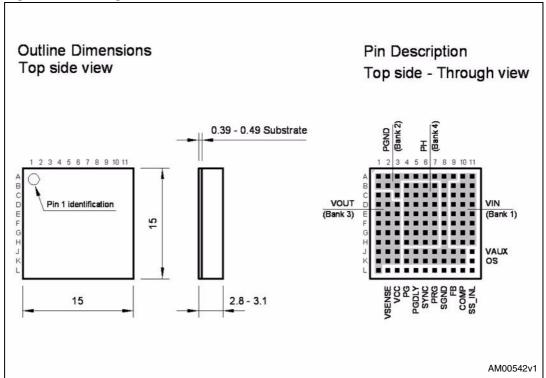

### 2.1 Pin connection and mechanical data (dimensions in mm)

Figure 1. Pin connection

## 2.2 Pin description

Table 2. Pin description

| Name | Function | Description                                                                                                                                                                                    |

|------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J11  | VAUX     | Auxiliary voltage.  Internally regulated 5 V voltage. It is used to supply the internal drivers and the voltage reference.                                                                     |

| K11  | os       | Oscillator set.  Connecting a resistor from this pin to SGND or to VAUX, the switching frequency can be increased or decreased.  In OVP status the pin is pulled to 4.5 V (latched mode only). |

| L2   | VSENSE   | Voltage sense. Using this pin it is possible to recover the voltage drop on Vout track.                                                                                                        |

| L3   | VCC      | VCC. Controller voltage supply pin. The operative voltage range for the internal controller is 4.5 V to 14 V                                                                                   |

Pin settings SPDC12L00010

Table 2. Pin description (continued)

| Name                         | Function | Description                                                                                                                                                                                                                |

|------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L4                           | PG       | Power Good. This pin is an open collector output, with a 10 k $\Omega$ pull-up resistor connected to VAUX. It is pulled low if the output voltage is not within specified thresholds (90%-110%).                           |

| L5                           | PGDLY    | Power Good delay.  A capacitor connected between this pin and SGND, introduce a delay between the internal PG comparator and the external signal rising edge. No delay can be introduced on the falling edge of PG signal. |

| L6                           | SYNC     | Synchronization. This is the master/slave pin. Two or more devices can be synchronized connecting the SYNC pins together.                                                                                                  |

| L7                           | PRG      | Program. This pin allows following settings: - Enable/disable the current sink mode capability after soft-start; - Enable/disable the OVP latch mode; - Setting UVLO threshold for 5 V or 12 V bus.                        |

| L8                           | SGND     | Signal ground. All references are referred to these pins, internally connected to PGND.                                                                                                                                    |

| L9                           | FB       | Feed-back. This pin is connected to the error amplifier inverting input.                                                                                                                                                   |

| L10                          | COMP     | Compensation. This pin is connected to the error amplifier output.                                                                                                                                                         |

| L11                          | SS_INL   | Soft-start_inhibit low The soft-start time is programmed connecting an external capacitor from this pin to SGND; This pin can be used to inhibit the module.                                                               |

| Bank 1 VIN DC input voltage. |          | DC input voltage. See Section 5.18 on page 18 for mandatory condition.                                                                                                                                                     |

| Bank 2                       | PGND     | Return for input/output voltage source.                                                                                                                                                                                    |

| Bank 3                       | VOUT     | Regulated power output. See Section 5.19 on page 18 for mandatory condition.                                                                                                                                               |

| Bank 4                       | PH       | Phase This pins area is foreseen for module power losses dissipation; see Section 5.20 on page 19 for details.                                                                                                             |

SPDC12L00010 Maximum ratings

# 3 Maximum ratings

## 3.1 Absolute maximum ratings

Table 3. Absolute maximum ratings

| Symbol           | Parameter               | Value        | Unit |

|------------------|-------------------------|--------------|------|

| V <sub>K11</sub> | OS to SGND and PGND     | -0.3 to 6    | V    |

| V <sub>L2</sub>  | VSENSE to SGND and PGND | -0.3 to 18   | ٧    |

| $V_{L3}$         | VCC to SGND and PGND    | -0.3 to 18   | ٧    |

| V <sub>L4</sub>  | PG to SGND and PGND     | -0.3 to 18   | ٧    |

| $V_{L5}$         | PGDLY to SGND and PGND  | -0.3 to 6    | ٧    |

| $V_{L6}$         | SYNC to SGND and PGND   | -0.3 to 6    | ٧    |

| V <sub>L7</sub>  | PRG to SGND and PGND    | -0.3 to 6    | ٧    |

| $V_{L9}$         | FB to SGND and PGND     | -0.3 to 6    | ٧    |

| V <sub>L10</sub> | COMP to SGNG and PGND   | -0.3 to 6    | ٧    |

| V <sub>L11</sub> | SS_INL to SGND and PGND | -0.3 to 6    | V    |

| V <sub>i</sub>   | VIN to SGND and PGND    | -0.3 to 18   | V    |

| V <sub>o</sub>   | VOUT to SGND and PGND   | -0.3 to 18   | V    |

| I <sub>o</sub>   | Maximum output current  | Int. limited | Α    |

### 3.2 Thermal data

Table 4. Table 3. Thermal data

| Symbol           | Parameter                   | Value     | Unit |

|------------------|-----------------------------|-----------|------|

| T <sub>STG</sub> | Storage temperature range   | -40 ÷ 105 | °C   |

| T <sub>OP</sub>  | Operating temperature range | -40 ÷ 85  | °C   |

7/24

Maximum ratings SPDC12L00010

### 3.3 Thermal de-rating

The thermal de-rating is obtained reducing the maximum output current, to limit the module temperature to the maximum allowable value.

Since a lot of parameters affect the module power dissipation, the best way to get a precise thermal de-rating is to measure the module temperature in the final application condition.

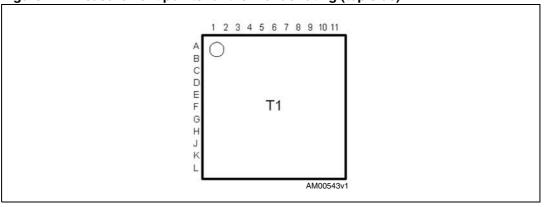

For this purpose, the case top side must be monitored at the central point T1 (see *Figure 2*); the maximum temperature allowable value at T1 is 125 °C.

Figure 2. Measurement points for thermal de-rating (top side)

All data reported in the following tables are valid for free air condition and module placed on 25 cm<sub>2</sub>, 4 layers, 1.6 mm FR4 printed circuit board.

Table 5. Thermal de-rating for Vout = 5.0 V

| Symbol         | Parameter      | Test condition                                | Value | Unit |

|----------------|----------------|-----------------------------------------------|-------|------|

|                |                | V <sub>IN</sub> = 8 V T <sub>A</sub> = 75 °C  | TBD   |      |

| I <sub>o</sub> | Output current | V <sub>IN</sub> = 8 V T <sub>A</sub> = 80 °C  | TBD   | Α    |

|                |                | V <sub>IN</sub> = 8 V T <sub>A</sub> = 85 °C  | TBD   |      |

|                |                | V <sub>IN</sub> = 10 V T <sub>A</sub> = 70 °C | TBD   |      |

| ı              | Output current | V <sub>IN</sub> = 10 V T <sub>A</sub> = 75 °C | TBD   | Α    |

| I <sub>o</sub> |                | V <sub>IN</sub> = 10 V T <sub>A</sub> = 80 °C | TBD   | A    |

|                |                | V <sub>IN</sub> = 10 V T <sub>A</sub> = 85 °C | TBD   |      |

|                | Output current | V <sub>IN</sub> = 12 V T <sub>A</sub> = 60 °C | TBD   |      |

|                |                | V <sub>IN</sub> = 12 V T <sub>A</sub> = 65 °C | TBD   |      |

| I <sub>o</sub> |                | V <sub>IN</sub> = 12 V T <sub>A</sub> = 70 °C | TBD   | Α    |

|                |                | V <sub>IN</sub> = 12 V T <sub>A</sub> = 75 °C | TBD   |      |

|                |                | V <sub>IN</sub> = 12 V T <sub>A</sub> = 80 °C | TBD   |      |

|                |                | V <sub>IN</sub> = 12 V T <sub>A</sub> = 85 °C | TBD   |      |

SPDC12L00010 Maximum ratings

Table 5. Thermal de-rating for Vout = 5.0 V (continued)

| Symbol         | Parameter        | Test condition                                | Value                                         | Unit |  |

|----------------|------------------|-----------------------------------------------|-----------------------------------------------|------|--|

|                |                  |                                               | V <sub>IN</sub> = 14 V T <sub>A</sub> = 50 °C | TBD  |  |

|                |                  | V <sub>IN</sub> = 14 V T <sub>A</sub> = 55 °C | TBD                                           |      |  |

| I <sub>o</sub> | Output current - | V <sub>IN</sub> = 14 V T <sub>A</sub> = 60 °C | TBD                                           | A    |  |

|                |                  | V <sub>IN</sub> = 14 V T <sub>A</sub> = 65 °C | TBD                                           |      |  |

|                |                  | V <sub>IN</sub> = 14 V T <sub>A</sub> = 70 °C | TBD                                           |      |  |

|                |                  | V <sub>IN</sub> = 14 V T <sub>A</sub> = 75 °C | TBD                                           |      |  |

|                |                  | V <sub>IN</sub> = 14 V T <sub>A</sub> = 80 °C | TBD                                           |      |  |

|                |                  | V <sub>IN</sub> = 14 V T <sub>A</sub> = 85 °C | TBD                                           |      |  |

Table 6. Thermal de-rating for Vout = 3.3 V

| Symbol         | Parameter      | Test condition                                | Value | Unit |

|----------------|----------------|-----------------------------------------------|-------|------|

|                | Output ourrent | V <sub>IN</sub> = 8 V T <sub>A</sub> = 80 °C  | TBD   | Α    |

| l <sub>o</sub> | Output current | V <sub>IN</sub> = 8 V T <sub>A</sub> = 85 °C  | TBD   | ^    |

|                |                | V <sub>IN</sub> = 10 V T <sub>A</sub> = 75 °C | TBD   |      |

| Io             | Output current | V <sub>IN</sub> = 10 V T <sub>A</sub> = 80 °C | TBD   | Α    |

|                |                | V <sub>IN</sub> = 10 V T <sub>A</sub> = 85 °C | TBD   |      |

|                | Output current | V <sub>IN</sub> = 12 V T <sub>A</sub> = 70 °C | TBD   |      |

| ı              |                | V <sub>IN</sub> = 12 V T <sub>A</sub> = 75 °C | TBD   | Α    |

| I <sub>o</sub> |                | V <sub>IN</sub> = 12 V T <sub>A</sub> = 80 °C | TBD   |      |

|                |                | V <sub>IN</sub> = 12 V T <sub>A</sub> = 85 °C | TBD   |      |

|                | Output current | V <sub>IN</sub> = 14 V T <sub>A</sub> = 65 °C | TBD   |      |

| I <sub>o</sub> |                | V <sub>IN</sub> = 14 V T <sub>A</sub> = 70 °C | TBD   |      |

|                |                | V <sub>IN</sub> = 14 V T <sub>A</sub> = 75 °C | TBD   | Α    |

|                |                | V <sub>IN</sub> = 14 V T <sub>A</sub> = 80 °C | TBD   |      |

|                |                | V <sub>IN</sub> = 14 V T <sub>A</sub> = 85 °C | TBD   |      |

9/24

Maximum ratings SPDC12L00010

Table 7. Thermal de-rating for Vout = 2.5 V

| Symbol         | Parameter       | Test condition                                | Value                                         | Unit |     |

|----------------|-----------------|-----------------------------------------------|-----------------------------------------------|------|-----|

|                |                 | V <sub>IN</sub> = 10 V T <sub>A</sub> = 80 °C | TBD                                           | Α    |     |

| I <sub>O</sub> | Output current  | V <sub>IN</sub> = 10 V T <sub>A</sub> = 85 °C | TBD                                           | A    |     |

| I <sub>o</sub> | Output current  | V <sub>IN</sub> = 12 V T <sub>A</sub> = 75 °C | TBD                                           |      |     |

|                |                 | V <sub>IN</sub> = 12 V T <sub>A</sub> = 80 °C | TBD                                           | Α    |     |

|                |                 | $V_{IN} = 12 V T_A = 88$                      | V <sub>IN</sub> = 12 V T <sub>A</sub> = 85 °C | TBD  |     |

| I <sub>o</sub> | Outrout suggest | V <sub>IN</sub> = 14 V T <sub>A</sub> = 70 °C | TBD                                           |      |     |

|                |                 | V <sub>IN</sub> = 14 V T <sub>A</sub> = 75 °C | TBD                                           | Α    |     |

|                | 10              | Output current                                | V <sub>IN</sub> = 14 V T <sub>A</sub> = 80 °C | TBD  | , A |

|                |                 | V <sub>IN</sub> = 14 V T <sub>A</sub> = 85 °C | TBD                                           |      |     |

Table 8. Thermal de-rating for Vout = 1.8 V

| Symbol         | Parameter      | Test condition                                | Value | Unit |

|----------------|----------------|-----------------------------------------------|-------|------|

| Io             | Output current | V <sub>IN</sub> = 10 V T <sub>A</sub> = 80 °C | TBD   | Α    |

|                |                | V <sub>IN</sub> = 10 V T <sub>A</sub> = 85 °C | TBD   | A    |

| I <sub>o</sub> | Output current | V <sub>IN</sub> = 12 V T <sub>A</sub> = 80 °C | TBD   | Α    |

|                |                | V <sub>IN</sub> = 12 V T <sub>A</sub> = 85 °C | TBD   | ^    |

| Io             | Output current | V <sub>IN</sub> = 14 V T <sub>A</sub> = 80 °C | TBD   | Α    |

|                |                | V <sub>IN</sub> = 14 V T <sub>A</sub> = 85 °C | TBD   | , A  |

Table 9. Thermal de-rating for Vout = 1.2 V

| Symbol                        | Parameter                                                                                                     | Test condition                                | Value | Unit |

|-------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-------|------|

| I <sub>o</sub> Output current | Output current $ V_{IN} = 14 \text{ V T}_{A} = 80 \text{ °C} $ $V_{IN} = 14 \text{ V T}_{A} = 85 \text{ °C} $ | V <sub>IN</sub> = 14 V T <sub>A</sub> = 80 °C | TBD   | Λ    |

|                               |                                                                                                               | TBD                                           | A     |      |

## 4 Electrical characteristics

Table 10. Electrical characteristics

| Symbol                | Parameter                                         | Test condition                                                                                   | Min   | Тур  | Max   | Unit |

|-----------------------|---------------------------------------------------|--------------------------------------------------------------------------------------------------|-------|------|-------|------|

| V <sub>r</sub>        | Ripple voltage                                    | $V_{IN} = 12 \text{ V}, I_{o} = 10 \text{ A},$ $C_{o} = 2x330 \mu\text{F}$ $BW = 20 \text{ MHz}$ |       | 40   |       | mVpp |

| Io                    | Output current                                    | V <sub>IN</sub> = 1.8 ÷ 14 V                                                                     | 0     |      | 10    | Α    |

| I <sub>ol</sub>       | Current limit                                     | V <sub>IN</sub> = 1.8 ÷ 14 V                                                                     |       | 12   |       | Α    |

| Iq                    | Total quiescent current                           | V <sub>CC</sub> = 12 V, I <sub>0</sub> = 0 A                                                     |       | 65   |       | mA   |

| I <sub>qst-by</sub>   | Total stand-by quiescent current                  | V <sub>SS_INL</sub> < 0.5 V                                                                      |       | 5    |       | mA   |

| I <sub>CCq</sub>      | V <sub>CC</sub> quiescent current                 | $V_{CC} = 12 \text{ V}, I_0 = 0 \text{ A},$<br>OS = open, $V_{SS\_INL} > 0.5 \text{ V}$          |       | 35   |       | mA   |

| I <sub>CCqst-by</sub> | V <sub>CC</sub> stand-by quiescent current        | $V_{CC} = 12 \text{ V}, I_0 = 0 \text{ A},$<br>OS = open, $V_{SS\_INL} < 0.5 \text{ V}$          |       | 5    |       | mA   |

| f <sub>s</sub>        | Switching frequency                               | $V_{CC} = 12 \text{ V}, I_0 = 10 \text{ A},$ $T_A = 0 \div 85 ^{\circ}\text{C}$                  | 678   | 729  | 780   | kHz  |

| $V_{FB}$              | Feedback voltage<br>(Reference voltage)           | T <sub>A</sub> = -40 ÷ 85 °C                                                                     | 0.593 | 0.6  | 0.605 | ٧    |

| V <sub>AUX</sub>      | Auxiliary voltage                                 | $V_{CC} = 5.5 \div 14 \text{ V},$ $I_{AUX} = 1 \div 100 \text{ mA}$                              | 4.5   | 5    | 5.5   | ٧    |

| V <sub>SS_INL</sub>   | Inhibit threshold                                 | Device OFF                                                                                       |       |      | 0.5   | V    |

|                       | Soft-start current                                | V <sub>SS_INL</sub> = 2 V                                                                        | 7     | 10   | 13    | - μΑ |

| I <sub>SS_INL</sub>   |                                                   | $V_{SS\_INL} = 0 \div 0.5 \text{ V}$                                                             | 20    | 30   | 45    |      |

| V <sub>PG</sub>       | Power Good voltage low                            | I <sub>PG</sub> = -5 mA                                                                          |       | 0.5  |       | V    |

| V <sub>PGhth</sub>    | Power Good high threshold (V <sub>FB</sub> /0.6)  | V <sub>FB</sub> rising                                                                           | 108   | 110  | 112   | %    |

| V <sub>PGlth</sub>    | Power Good low threshold (V <sub>FB</sub> /0.6)   | V <sub>FB</sub> falling                                                                          | 88    | 90   | 92    | %    |

| V <sub>OVhth</sub>    | Overvoltage high threshold (V <sub>FB</sub> /0.6) | V <sub>FB</sub> rising                                                                           |       | 120  |       | %    |

| V <sub>OVIth</sub>    | Overvoltage low threshold (V <sub>FB</sub> /0.6)  | V <sub>FB</sub> falling                                                                          |       | 117  |       | %    |

| .,                    | V <sub>CC</sub> turn-on threshold                 | 5 V BUS, V <sub>IN</sub> > 1.7 V                                                                 | 4.0   | 4.2  | 4.4   | V    |

| V <sub>CConth</sub>   |                                                   | 12 V BUS, V <sub>IN</sub> > 1.7 V                                                                | 8.3   | 8.6  | 8.9   |      |

| V <sub>CCoffth</sub>  | V <sub>CC</sub> turn-off threshold                | 5 V BUS, V <sub>IN</sub> > 1.7 V                                                                 | 3.6   | 3.8  | 4.0   | V    |

|                       | ACC ratti-ou ruesuoid                             | 12 V BUS, V <sub>IN</sub> > 1.7 V                                                                | 7.4   | 7.7  | 8.0   | v    |

| V <sub>INhth</sub>    | V <sub>IN</sub> high threshold                    | V <sub>IN</sub> rising                                                                           | 1.1   | 1.25 | 1.47  | V    |

| V <sub>INIth</sub>    | V <sub>IN</sub> low threshold                     | V <sub>IN</sub> falling                                                                          | 0.9   | 1.05 | 1.27  | V    |

### 5 Application information

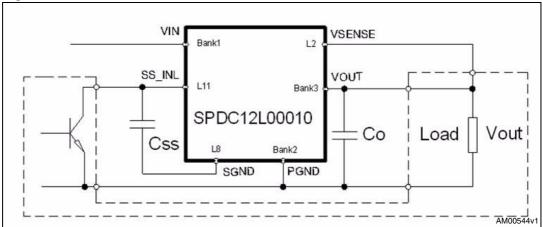

#### 5.1 Input voltage

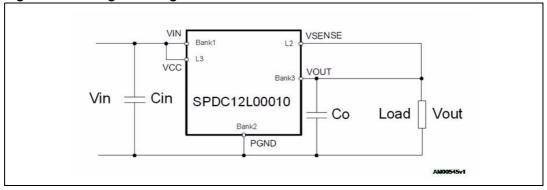

There are two voltage supply pins:

VCC (pin L3), for controller voltage supply;

VIN (bank 1), for power circuit voltage supply.

VCC and VIN can be connected and supplied together;

if VIN is lower than 4.5 V, VCC must be supplied separately.

The recommended maximum operating DC input voltage is 14 V.

### 5.2 Auxiliary voltage

VAUX (pin J11) pin must be used to supply PRG and OS setting resistors.

No capacitor is required.

#### 5.3 Inhibit function

SS\_INL (pin L11) allows putting the device in stand-by mode.

With SS\_INL lower than 0.5 V, the device is disabled and the current consumption is reduced to 5 mA, for VIN = 12 V.

With SS\_INL higher than 0.5 V the device is enabled.

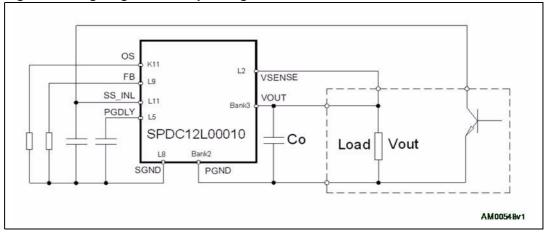

Since SS\_INL has soft-start function, it is mandatory to implement the inhibit function using an open collector device (i.e. small signal transistor), to not influence the module behavior (see *Figure 3*).

Figure 3. Inhibit function

#### 5.4 Soft-start

The soft-start phase begins when both VCC and VIN raise above their turn-on thresholds, otherwise the SS\_INL pin is internally shorted to SGND.

A ramp is generated at SS\_INL pin during start-up, charging the external capacitor CSS with an internal current generator.

The initial value for this current is 30  $\mu$ A and it charges the capacitor up to 0.5 V, after that, it is reduced to 10  $\mu$ A until the final charge value approximately 4 V.

In the meanwhile, the controller internal voltage reference raises to its final value, following the SS\_INL pin voltage slope.

During soft-start, the module provides a constant current protection, limiting the output current at the maximum value, without entering in HICCUP mode.

If there is not current limitation, the output voltage slope follows the SS\_INL pin slope.

The output voltage rise time, can be set choosing proper CSS value.

The soft-start phase ends when the SS\_INL pin voltage reaches 3.5 V.

A capacitor CSS = 3 3 nF is present on the module, to perform a minimum soft-start time, suitable for Co = 10000  $\mu$ F max. output capacitor;

in this condition and with 10 A output current resistor load, the output voltage rise time is around 5ms, but the complete soft-start time is around 10ms.

Using the minimum output capacitor  $Co = 660 \mu F$  and with 10 A resistor load, the output voltage rise time is around 2 ms.

### 5.5 Multiple units synchronization

Using more than one unit on the same circuit, it is possible to synchronize the switching frequency oscillators, connecting all SYNC (pin L6) together.

The device with the higher switching frequency will be the Master, while the other will be the Slaves.

The best way to synchronize two or more devices is to set same switching frequency, in any case, the switching frequencies can differ for a maximum of 50% of the lowest one.

Using and external clock signal, to synchronize one or more devices working at a different switching frequency, it is recommended to follow the below formula:

$$f_{sw} \le f_{ext} \le 1.3 f_{sw}$$

The phase shift between master and slaves is approximately 180°.

#### 5.6 Power Good signal and Power Good delay

The output voltage is monitored by FB (pin L9), if it is not within  $\pm$  10% (typ.) of the programmed value, the PG (pin L4) output is forced low.

The PG signal can be delayed by adding an external capacitor on PGDLY (pin L5), the delay can be calculated with the following formula:

$$PG_{delay} = 0.5 \times C_{PGDLY}(pF)$$

[µs]

#### 5.7 Oscillator setting

The switching frequency is internally fixed to 729 kHz, this value can be slightly varied using an external resistor  $R_{OS}$  connected between OS (pin K11) and SGND (L8) or VAUX (pin J11).

Since the OS pin is maintained at fixed voltage (typ. 1.2), the frequency is increased/decreased proportionally to the current sunk/sourced from/into the pin.

In particular, connecting  $R_{OS}$  to SGND the frequency is increased according the following formula:

$$f_{SW} = 729 + (9.88 \times 10^6 / R_{OS})$$

[kHz]

Connecting R<sub>OS</sub> to VAUX the frequency is reduced according to the following formula:

$$f_{SW} = 729 - (30.1 \times 10^6 / R_{OS})$$

[kHz]

#### 5.8 Current sink-mode

Connecting a proper resistor (see par. *Section 5.10 on page 15*) from PRG (pin L7) to VAUX (pin J11), it is possible to select the sink-mode operation, that means to allow the output current to reverse its polarity into the converter output inductor.

If the sink-mode is enabled, the converter can sink current from the load after soft-start;

If the sink-mode is disabled, the converter never sinks current.

Note:

When output low current operation is required (lout < 2 A), sink-mode operation is recommended, this condition improves output voltage transient response and reduces output voltage ripple.

### 5.9 Under voltage lock out

Connecting a proper resistor (see par. *Section 5.10*) from PRG (pin L7) to VAUX (pin J11), it is possible to select two different thresholds for UVLO:

4.2 V/3.8 V for 5 V input range;

8.6 V/7.7 V for 12 V input range.

### 5.10 Program setting

Connecting a resistor from PRG (pin L7) to VAUX (pin J11), it is possible to select different operation modes, according to the following table:

Table 11. Program setting

| R <sub>PRG</sub> | UVLO.     | OVP         | Sink-mode |

|------------------|-----------|-------------|-----------|

| n.c.             |           | Not latched | Not       |

| 11 kΩ            | 5 V range | Not latched | Yes       |

| 6.2 kΩ           |           | Latched     | Not       |

| 4.3 kΩ           |           | Latched     | Yes       |

| 2.7 kΩ           |           | Not latched | Not       |

| 1.8 kΩ           |           | Not latched | Yes       |

| 1.2 kΩ           |           | Latched     | Not       |

| 0 Ω              |           | Latched     | Yes       |

### 5.11 Voltage sensing

Using VSENSE (pin L2) it is possible to recover the voltage drop on VOUT PCB track.

Connect VSENSE in a point closed to the load (see Figure 4).

Using VSENSE connection, it will not recover the voltage drop on PGND PCB track.

Leaving VSENSE floating, the output voltage will be sensed at VOUT (bank 3).

Figure 4. Voltage sensing

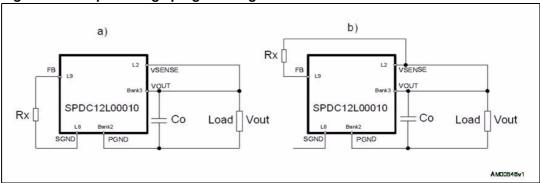

#### 5.12 Output voltage programming

Adding a resistor Rx between FB (pin L9) and SGND (L8) or between FB and VSENSE (pin L2), it is possible to change the output voltage.

Connecting the resistor to SGND the output voltage increase (see Figure 5 a);

Connecting the resistor to VSENSE the output voltage decrease (see *Figure 5* b).

Calculate the resistor for increasing output voltage with the following formula:

$$R_x = 0.6 / (V_{OUT} - 1.2)$$

[k $\Omega$ ] valid for  $V_{OUT} > 1.2$  V

Calculate the resistor for decreasing output voltage with the following formula:

$$R_x = (V_{OUT} - 0.6) / (1.2 - V_{OUT}) [k\Omega]$$

valid for  $0.6 < V_{OUT} < 1.2 V$

The module output voltage is 1.2 V with  $R_{\chi} = n.c.$

Figure 5. Output voltage programming

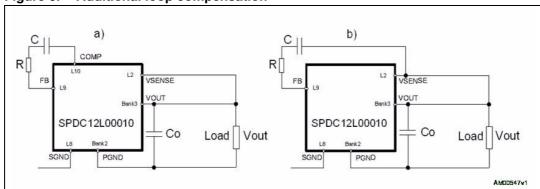

### 5.13 Additional loop compensation

If required by particular load condition, it is possible to change the feedback loop compensation, adding a pole with an external R-C network between FB (pin L9) and COMP (pin L10) (see *Figure 6* a), or adding a zero with an external R-C network between FB and VSENSE (pin L2) (see *Figure 6* b).

Figure 6. Additional loop compensation

#### 5.14 Output over voltage protection

The device provides OVP:

when the voltage sensed on FB (pin L9) reaches a value greater than 20% of reference, the on module low side driver is turned ON and the converter stop switching operation.

If the OVP not latched mode has been set, the on module low side MOSFET is kept ON, as long as the over voltage condition is detected.

If OVP latched mode has been set, the low side MOSFET is turned ON and the OS (pin K11) is forced high (4.5 V typ.), until VCC is toggled.

It must be taken in account that there is an electrical network between the output terminal and FB, therefore the voltage at this pin is not a perfect replica of output voltage.

If the converter is set to sink current, the low side MOSFET could be turned ON before the output voltage exceeds the over voltage threshold (109% typ.), because the error amplifier will change its balance in advance.

If the sink-mode is disabled, the low side MOSFET will be turned ON only when the OVP operate, in this case a delay between the output voltage rising and the FB rising can appear and the OVP can operate late (126% typ.).

#### 5.15 Current limitation

The device realizes the over current protection sensing the current on board high side MOSFET and on board low side MOSFET, therefore two current limits are set:

peak current limit and valley current limit.

The peak current protection is active when the high side MOSFET is turned ON, the valley current protection is enabled when the low side MOSFET is turned ON.

After soft-start is completed, if an over current occurs, the device enters in HICCUP mode:

both high side and low MOSFETs are turned OFF;

the soft-start capacitor is discharged with a 10 μA constant current;

when the voltage on SS\_INL (pin L11) reaches 0.5 V the soft-start phase restart.

During the soft-start phase the OCP provides a constant current protection.

#### 5.16 Thermal shutdown

When the controller junction temperature reaches 150  $\pm$  10 °C, the device shutdown.

Both MOSFET are turned OFF and the soft-start capacitor is discharged.

The device does not restart until the junction temperature goes down to 120  $^{\circ}$ C and until the voltage on the soft-start capacitor reaches 0.5 V.

#### 5.17 Signal ground and power ground

SGND (L8) and PGND (bank 2) are connected together on the module.

Connect to SGND the capacitor for PGDLY and SS\_INL, the resistor for FB and OS.

Connect to PGND the return for SS\_INL.

It is important to not create a ground loop between SGND, PGND and other GND present on the application circuit (see *Figure 7*).

Figure 7. Signal ground and power ground

#### 5.18 Input capacitors

The input capacitor present on the module is not able to sustain the input RMS current.

Connect 2 x 2.2  $\mu$ F 16 V X7R ceramic capacitor (Cin) closed to the input pins VIN and PGND (bank 1 and bank 2), to satisfy minimum functional requirement.

Connect proper low impedance capacitors to reduce the input ripple current, according to the application requirement.

### 5.19 Output capacitors

The output capacitors present on the module are able to sustain output RMS current.

Connect 2 x 330  $\mu$ F POSCAP SANYO capacitor (Co) or equivalent, closed to the output pins VOUT and PGND (bank 3 and bank 2), to guarantee output voltage stability and specified voltage ripple.

#### 5.20 Phase connection

On the module bottom, there is an area relative to PH (bank 4) connection:

this area is internally connected to the high side MOSFET source and to the low side MOSFET drain;

this electrical point is used to dissipate heat generated by the two MOSFETs.

Connect PH (bank 4), to an insulated copper area on the mother board, to ensure proper heat sink.

Since the PH signal contains very fast voltage transients, it is recommended to take in account possible inducted noise on mother board, i.e.: it is advised against to lead under the module printed circuit board tracks with susceptible signals.

## 6 Package mechanical data

In order to meet environmental requirements, ST offers these devices in ECOPACK® packages. These packages have a lead-free second level interconnect. The category of second level interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label. ECOPACK is an ST trademark. ECOPACK specifications are available at: www.st.com

Figure 8. Package mechanical data

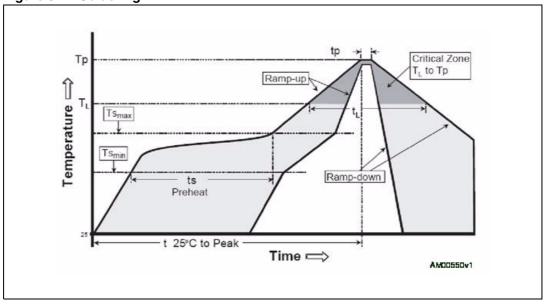

### 6.1 Soldering

Soldering phase has to be execute with care: in order to avoid undesired melting phenomenon, particular attention has to be take on the set up of the peak temperature.

Here following some suggestions for the temperature profile based on IPC/JEDEC J-STD-020C, July 2004 recommendations.

Table 12. Soldering

| Profile feature                                               | PB free assembly |

|---------------------------------------------------------------|------------------|

| Average ramp up rate (T <sub>SMAX</sub> to TP)                | 3 °C / sec max   |

| Preheat                                                       |                  |

| Temperature min (T <sub>S</sub> min)                          | 150 °C           |

| Temperature max (T <sub>S</sub> max)                          | 200 °C           |

| Time ( $t_S$ min to $t_S$ max) ( $t_S$ )                      | 60 – 100 sec     |

| Time maintained above:                                        |                  |

| Temperature T <sub>L</sub>                                    | 217 °C           |

| Time t <sub>L</sub>                                           | 40 – 70 sec      |

| Peak temperature (T <sub>p</sub> )                            | 240 + 0 °C       |

| Time within 5 °C of actual peak temperature (t <sub>P</sub> ) | 10 – 20 sec      |

| Ramp down rate                                                | 6 °C / sec       |

| Time from 25 °C to peak temperature                           | 8 minutes max    |

Figure 9. Soldering

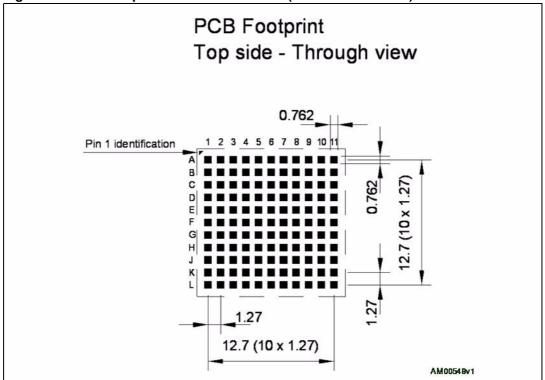

### 6.2 PCB footprint

Use Figure 10 as suggested PCB footprint.

Figure 10. PCB footprint for SPDC12L00010 (dimensions in mm)

SPDC12L00010 Revision history

# 7 Revision history

Table 13. Document revision history

| Date        | Revision | Changes       |

|-------------|----------|---------------|

| 17-Oct-2008 | 1        | First release |

23/24

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2008 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com