# R2A20112SP/DD

### Critical Conduction Mode Interleaved PFC Control IC

REJ03D0904-0200 Preliminary Rev.2.00 Nov 13, 2007

#### **Description**

The R2A20112 controls a boost converter to provide a active power factor correction.

The R2A20112 adopts critical conduction mode for power factor correction and realizes high efficiency and a low switching noise by zero current switching.

Interleaving function improve ripple current on input or output capacitor by 180 degrees phase shift.

The feedback loop open detection, two mode overvoltage protection, overcurrent protection are built in the R2A20112, and can constitute a power supply system of high reliability with few external parts.

#### **Features**

- Maximum Ratings

- Supply voltage Vcc: 24 V

- Operating junction temperature Tjopr: -40 to +150°C

- Electrical characteristics

- VREF output voltage VREF:  $5.0 \text{ V} \pm 3\%$

- UVLO operation start voltage VH: 10.5 V  $\pm$  0.7 V

- UVLO operation shutdown voltage VL:  $9.3 \text{ V} \pm 0.5 \text{ V}$

- UVLO hysteresis voltage Hysuvl: 1.2 V  $\pm$  0.5 V

- Functions

- Boost converter control with critical conduction mode

- Interleaving control

- Two mode overvoltage protection

- Mode1: Dynamic OVP corresponding to a voltage rise by load change

- Mode2: Static OVP corresponding to overvoltage in stable

- Feedback loop open detection

- Master and Slave independence overcurrent protection

- 280 μs restart timer

- Package lineup: Pb-free SOP-16/DILP-16

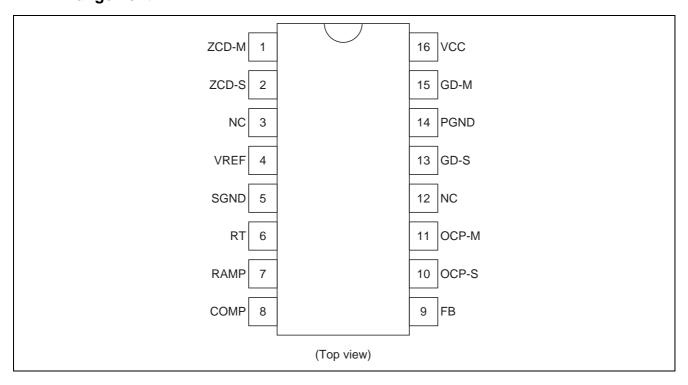

## **Pin Arrangement**

#### **Pin Functions**

| Pin No. | Pin Name | Input/Output | Function                                               |

|---------|----------|--------------|--------------------------------------------------------|

| 1       | ZCD-M    | Input        | Master converter zero current detection input terminal |

| 2       | ZCD-S    | Input        | Slave converter zero current detection input terminal  |

| 3       | N.C.     | _            | Open                                                   |

| 4       | VREF     | Output       | Reference voltage output terminal                      |

| 5       | SGND     | _            | Ground for small signal circuit                        |

| 6       | RT       | Input/Output | Oscillator frequency setting terminal                  |

| 7       | RAMP     | Input/Output | Ramp waveform setting terminal                         |

| 8       | COMP     | Output       | Error amplifier output terminal                        |

| 9       | FB       | Input        | Error amplifier input terminal                         |

| 10      | OCP-S    | Input        | Slave converter overcurrent detection terminal         |

| 11      | OCP-M    | Input        | Master converter overcurrent detection terminal        |

| 12      | N.C.     | _            | Open                                                   |

| 13      | GD-S     | Output       | Slave converter Power MOSFET drive terminal            |

| 14      | PGND     | _            | Ground for power stage                                 |

| 15      | GD-M     | Output       | Master converter Power MOSFET drive terminal           |

| 16      | VCC      | Input        | Supply voltage terminal                                |

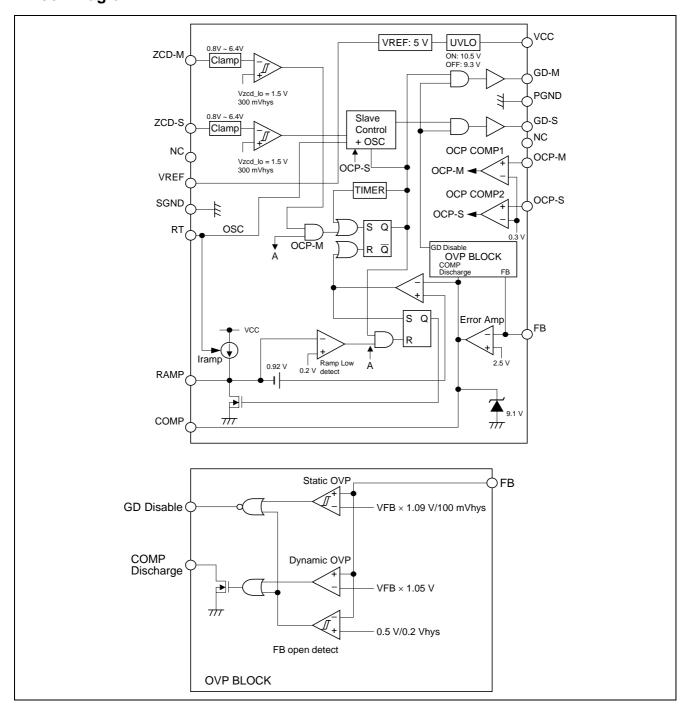

#### **Block Diagram**

### **Absolute Maximum Ratings**

$(Ta = 25^{\circ}C)$

| Item                           | Symbol    | Ratings          | Unit | Note |

|--------------------------------|-----------|------------------|------|------|

| Supply voltage                 | Vcc       | -0.3 to 24       | V    |      |

| GD-M Peak current              | lpk-gdm   | ±200             | mA   | 3    |

| GD-M DC current                | ldc-gdm   | ±10              | mA   |      |

| GD-S Peak current              | lpk-gds   | ±200             | mA   | 3    |

| GD-S DC current                | ldc-gds   | ±10              | mA   |      |

| ZCD terminal current           | Izcd      | ±10              | mA   |      |

| RT terminal current            | Irt       | -200             | μΑ   |      |

| Vref terminal current          | Iref      | <b>-</b> 5       | mA   |      |

| COMP terminal current          | Icomp     | ±1               | mA   |      |

| Terminal voltage               | Vt-group1 | -0.3 to Vcc      | V    | 4    |

|                                | Vt-group2 | -0.3 to Vref     | V    | 5    |

| Vref terminal voltage          | Vt-ref    | -0.3 to Vref+0.3 | V    |      |

| Power dissipation              | Pt        | 1                | W    | 6    |

| Operating junction temperature | Tj-opr    | -40 to +150      | °C   |      |

| Storage temperature            | Tstg      | -55 to +150      | °C   |      |

Notes: 1. Rated voltages are with reference to the SGND terminal.

- 2. For rated currents, inflow to the IC is indicated by (+), and outflow by (-).

- 3. Shows the transient current when driving a capacitive load.

- 4. This is the rated voltage for the following pins: RAMP, FB

- 5. This is the rated voltage for the following pins: RT, OCP-M , OCP-S

- 6. In case of R2A20112DD (DILP):  $\theta$ ja = 120°C/W In case of R2A20112SP (SOP):  $\theta$ ja = 120°C/W

This value is a thing mounting on  $40 \times 40 \times 1.6$  [mm], a glass epoxy board of wiring density 10%.

#### **Electrical Characteristics**

$(Ta = 25^{\circ}C, Vcc = 12 \text{ V}, RT = 22 \text{ k}\Omega, OCP = GND, CRAMP = 680 pF, RZCD-GND = 51 \text{ k}\Omega, FB = COMP)$

| Item   |                                 | Symbol    | Min  | Тур  | Max  | Unit   | Test Conditions                        |

|--------|---------------------------------|-----------|------|------|------|--------|----------------------------------------|

| Supply | UVLO Turn-on threshold          | Vuvlh     | 9.8  | 10.5 | 11.2 | V      |                                        |

|        | UVLO Turn-off threshold         | VuvII     | 8.8  | 9.3  | 9.8  | V      |                                        |

|        | UVLO hysteresis Standby current |           | 0.7  | 1.2  | 1.7  | V      |                                        |

|        |                                 |           | _    | 120  | 200  | μА     | Vcc = 8.9 V, ZCD = Open                |

|        | Operating current               | Icc       | _    | 4.9  | 7.0  | mA     |                                        |

| VREF   | Output voltage                  | Vref      | 4.85 | 5.00 | 5.15 | V      | Isource = -1 mA                        |

|        | Line regulation                 | Vref-line | _    | 5    | 20   | mV     | Isource = -1 mA,<br>Vcc = 10 V to 24 V |

|        | Load regulation                 | Vref-load | _    | 5    | 20   | mV     | Isource = -1 mA to -5 mA               |

|        | Temperature stability           | dVref     | _    | ±80  | _    | ppm/°C | Ta = -40 to 125°C *1                   |

Note: 1. Design spec.

## **Electrical Characteristics** (cont.)

$(Ta = 25^{\circ}C, Vcc = 12 \text{ V}, RT = 22 \text{ k}\Omega, OCP = GND, CRAMP = 680 \text{ pF}, RZCD-GND = 51 \text{ k}\Omega, FB = COMP)$

|           | Item                      | Symbol      | Min  | Тур  | Max  | Unit | Test Conditions                                                              |

|-----------|---------------------------|-------------|------|------|------|------|------------------------------------------------------------------------------|

| Error     | Feedback voltage          | Vfb         | 2.40 | 2.50 | 2.60 | V    | FB-COMP short, RAMP = 0 V                                                    |

| amplifier | Input bias current        | Ifb         | -0.5 | 0    | 0.5  | μΑ   | Measured pin: FB                                                             |

|           | Open loop gain            | Av          | _    | 60   | _    | dB   | *1                                                                           |

|           | Upper clamp voltage       | Vclamp-comp | 8.0  | 9.1  | 10.6 | V    | FB = 2.0 V, COMP: Open                                                       |

|           | Low voltage               | VI-comp     | _    | 0.1  | 0.3  | V    | FB = 3.0 V, COMP: Open                                                       |

|           | Source current            | Isrc-comp   | _    | -120 | _    | μА   | FB = 1.5 V, COMP = 2.5 V                                                     |

|           | Sink current 1            | Isnkcomp1   | _    | 120  | _    | μА   | *1                                                                           |

|           | Sink current 2            | Isnkcomp2   | _    | 300  | _    | μА   | FB = 3.5 V, COMP = 2.5 V                                                     |

|           | Transconductance          | gm          | 150  | 200  | 290  | μS   | $FB = 2.45 \text{ V} \leftrightarrow 2.55 \text{ V},$ $COMP = 2.5 \text{ V}$ |

| RAMP      | RAMP charge current       | Ic-ramp     | 130  | 150  | 170  | μА   | RAMP = 0 V to 7 V                                                            |

|           | RAMP discharge current    | ld-ramp     | 7    | 16   | 29   | mA   | FB = 1 V, COMP = 2 V,<br>RAMP = 0 V to 1.5 V to 1 V                          |

|           | Low voltage               | VI-ramp     | _    | 17   | 200  | mV   | FB = 1 V, COMP = 3 V,<br>RAMP = 0 V to 2.5 V to open<br>Isink = 100 μA       |

| Zero      | Upper clamp voltage       | Vzcdh       | 5.8  | 6.4  | 7.0  | V    | Isource = -3 mA                                                              |

| current   | Lower clamp voltage       | Vzcdl       | 0.3  | 0.8  | 1.3  | V    | Isink = 3 mA                                                                 |

| detector  | ZCD low threshold voltage | Vzcd_lo     | 1.05 | 1.50 | 1.75 | V    | *1                                                                           |

|           | ZCD hysteresis            | Hyszcd      | 180  | 300  | 390  | mV   | *1                                                                           |

|           | Input bias current        | Izcd        | -1   | _    | 1    | μА   | 1.2 V < Vzcd < 5 V                                                           |

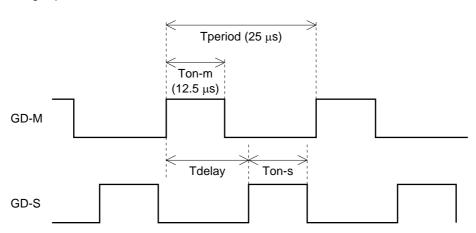

| Slave     | Phase delay               | Phase       | 160  | 180  | 200  | deg. | *1, *2                                                                       |

| control   | On time ratio             | Ton-ratio   | -5   | _    | 5    | %    | *1, *2                                                                       |

| Restart   | Restart time delay        | Tstart      | 210  | 280  | 350  | μS   | Cramp = 3300 pF<br>FB = 2.0 V, COMP = 5 V                                    |

Note: 1. Design spec.

2.

Phase =

$$\frac{\text{Tdelay}}{\text{Tperiod}} \times 360 \text{ [deg.]}$$

Ton-ratio =

$$\left(1 - \frac{\text{Ton-s}}{\text{Ton-m}}\right) \times 100 \, [\%]$$

# **Electrical Characteristics** (cont.)

$(Ta = 25^{\circ}C, Vcc = 12 \text{ V}, RT = 22 \text{ k}\Omega, OCP = GND, CRAMP = 680 \text{ pF}, RZCD-GND = 51 \text{ k}\Omega, FB = COMP)$

| Item                    |                                  | Symbol    | Min   | Тур   | Max   | Unit | Test Conditions              |

|-------------------------|----------------------------------|-----------|-------|-------|-------|------|------------------------------|

| Gate                    | Gate Master gate drive rise time |           | _     | 30    | 100   | ns   | CL = 100 pF, Cramp = 3300 pF |

| drive                   |                                  |           |       |       |       |      | FB = 2.0 V, COMP = 5 V       |

|                         | Slave gate drive rise time       | tr-gds    | _     | 30    | 100   | ns   | CL = 100 pF, Cramp = 3300 pF |

|                         |                                  |           |       |       |       |      | FB = 2.0 V, COMP = 5 V       |

|                         | Master gate drive fall time      | tf-gdm    | _     | 30    | 100   | ns   | CL = 100 pF, Cramp = 3300 pF |

|                         |                                  |           |       |       |       |      | FB = 2.0 V, COMP = 5 V       |

|                         | Slave gate drive fall time       | tf-gds    | _     | 30    | 100   | ns   | CL = 100 pF, Cramp = 3300 pF |

|                         |                                  |           |       |       |       |      | FB = 2.0 V, COMP = 5 V       |

|                         | Master gate drive low            | Vol1-gdm  | _     | 0.05  | 0.2   | V    | Isink = 2 mA                 |

|                         | voltage                          | Vol2-gdm  | _     | 0.03  | 0.7   |      | Isink = 1 mA, VCC = 5 V      |

|                         | Master gate drive high voltage   | Voh-gdm   | 11.5  | 11.9  | _     | V    | Isource = -2 mA              |

|                         | Slave gate drive low             | Vol1-gds  | _     | 0.05  | 0.2   | V    | Isink = 2 mA                 |

|                         | voltage                          | Vol2-gds  | _     | 0.03  | 0.7   |      | Isink = 1 mA, VCC = 5 V      |

|                         | Slave gate drive high voltage    | Voh-gds   | 11.5  | 11.9  | _     | V    | Isource = -2 mA *1           |

| Over current protection | OCP threshold voltage            | Vocp      | 0.27  | 0.3   | 0.33  | V    |                              |

| Over                    | Dynamic OVP threshold            | Vdovp     | VFB×  | VFB×  | VFB×  | V    |                              |

| voltage                 | voltage                          |           | 1.035 | 1.050 | 1.065 |      |                              |

| protection              | Static OVP threshold             | Vsovp     | VFB×  | VFB×  | VFB×  | V    | COMP = Open                  |

|                         | voltage                          |           | 1.075 | 1.090 | 1.105 |      |                              |

|                         | Static OVP hysteresis            | Hys-sovp  | 50    | 100   | 150   | mV   | COMP = Open                  |

|                         | FB open detect threshold voltage | Vfbopen   | 0.45  | 0.50  | 0.55  | V    | COMP = Open                  |

|                         | FB open detect hysteresis        | Hysfbopen | 0.16  | 0.20  | 0.24  | V    | COMP = Open                  |

Note: 1. Design spec.

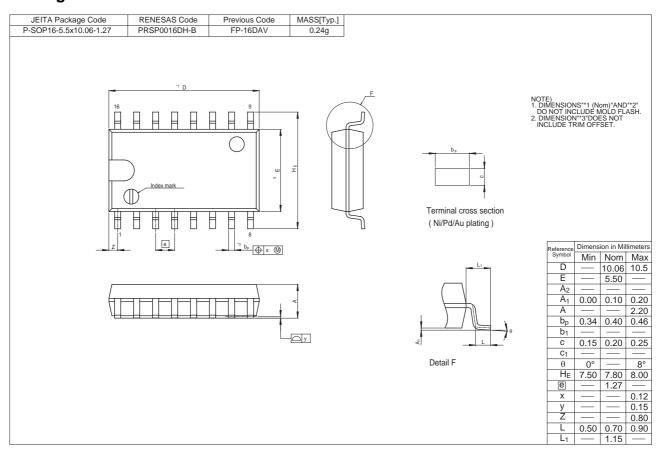

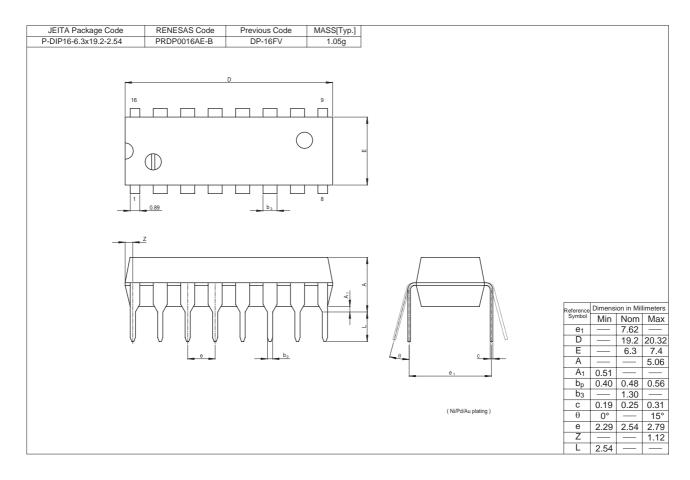

#### **Package Dimensions**

#### Renesas Technology Corp. Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

- Renesas Technology Corp. Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

Notes:

1. This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information in this document nor grants any license to any intellectual property rights or any other rights of Renesas or any third party with respect to the information in this document.

2. Renesas shall have no liability for damages or infringement of any intellectual property or other rights arising out of the use of any information in this document, but not limited to, product data, diagrams, charts, programs, algorithms, and application circuit examples.

3. You should not use the products or the technology described in this document for the purpose of military applications such as the development of weapons of mass and regulations, and procedures required by such laws and regulations and procedures required by such laws and regulations, and procedures required by such laws and regulations and procedures required by such laws and regulations, and procedures required by such laws and regulations, and procedures required by such laws and regulations. All procedures required by such laws and regulations and procedures required by such laws and regulations, and procedures required by such laws and regulations. All procedures required by such laws and regulations and procedures required by such laws and regulations, and procedures required by such laws and regulations, and procedures are such as a second required by the products of the date of th

**RENESAS SALES OFFICES**

http://www.renesas.com

Refer to "http://www.renesas.com/en/network" for the latest and detailed information.

Renesas Technology America, Inc.

450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500, Fax: <1> (408) 382-7501

Renesas Technology Europe Limited

Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K.

Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900

Renesas Technology (Shanghai) Co., Ltd.

Unit 204, 205, AZIACenter, No. 1233 Lujiazui Ring Rd, Pudong District, Shanghai, China 200120 Tel: <86> (21) 5877-1818, Fax: <86> (21) 6887-7898

Renesas Technology Hong Kong Ltd.

7th Floor, North Tower, World Finance Centre, Harbour City, 1 Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel: <852> 2265-6688, Fax: <852> 2730-6071

Renesas Technology Taiwan Co., Ltd. 10th Floor, No.99, Fushing North Road, Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 2713-2999

Renesas Technology Singapore Pte. Ltd.

1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65> 6213-0200, Fax: <65> 6278-8001

Renesas Technology Korea Co., Ltd. Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, Korea Tel: <82> (2) 796-3115, Fax: <82> (2) 796-2145

Renesas Technology Malaysia Sdn. Bhd

Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jalan Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: <603> 7955-9390, Fax: <603> 7955-9510