# DAC1001D125

## Dual 10-bit DAC, up to 125 Msps

Rev. 01 — 24 November 2008

**Product data sheet**

### 1. General description

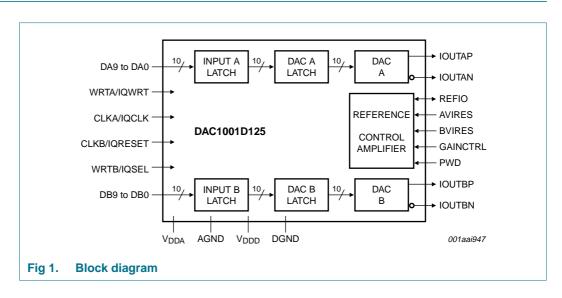

The DAC1001D125 is a dual-port high-speed 2-channel CMOS Digital-to-Analog Converter (DAC), optimized for high dynamic performance with low power dissipation. The Supporting an update rate of up to 125 Msps, the DAC1001D125 is suitable for Direct IF applications.

Separate write inputs allow data to be written to the two DAC ports independently of one another. Two separate clocks control the update rate of each DAC port.

The DAC1001D125 can interface two separate data ports or one single interleaved high-speed data port. In Interleaved mode, the input data stream is demultiplexed into its original I and Q data and latched. The I and Q data is then converted by the two DACs and updated at half the input data rate.

Each DAC port has a high-impedance differential current output, suitable for both single-ended and differential analog output configurations.

The DAC1001D125 is pin compatible with the AD9763, DAC2900 and DAC5652.

#### 2. Features

- Dual 10-bit resolution

- 125 Msps update rate

- Single 3.3 V supply

- Dual-port or Interleaved data modes

- 1.8 V, 3.3 V and 5 V compatible digital inputs

- Internal and external reference

- 2 mA to 20 mA full-scale output current

Industrial temperature range of

- Typical 185 mW power dissipation

- 16 mW power-down

- SFDR: 80 dBc;  $f_0 = 1$  MHz;  $f_s = 52$  Msps

- SFDR: 77 dBc; f<sub>o</sub> = 10.4 MHz; f<sub>s</sub> = 78 Msps

- SFDR: 72 dBc; f<sub>o</sub> = 1 MHz; f<sub>s</sub> = 52 Msps; -12 dBFS

- LQFP48 package

- Industrial temperature range of –40 °C to +85 °C

## 3. Applications

- Quadrature modulation

- Medical/test instrumentation

- Direct IF applications

- Direct digital frequency synthesis

- Arbitrary waveform generator

## 4. Ordering information

Table 1. Ordering information

| Type number   | Package |                                                                                          |          |

|---------------|---------|------------------------------------------------------------------------------------------|----------|

|               | Name    | Description                                                                              | Version  |

| DAC1001D125HL | LQFP48  | plastic low profile quad flat package; 48 leads; body $7 \times 7 \times 1.4 \text{ mm}$ | SOT313-2 |

## 5. Block diagram

## 6. Pinning information

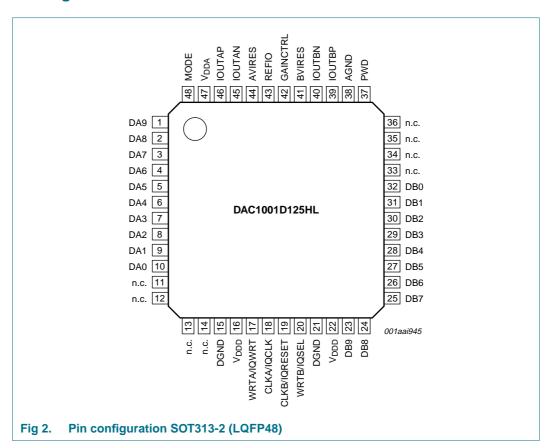

#### 6.1 Pinning

## 6.2 Pin description

Table 2. Pin description

|        | •   |         |                               |

|--------|-----|---------|-------------------------------|

| Symbol | Pin | Type[1] | Description                   |

| DA9    | 1   | I       | DAC A, data input bit 9 (MSB) |

| DA8    | 2   | ļ       | DAC A, data input bit 8       |

| DA7    | 3   | I       | DAC A, data input bit 7       |

| DA6    | 4   | ļ       | DAC A, data input bit 6       |

| DA5    | 5   | I       | DAC A, data input bit 5       |

| DA4    | 6   | I       | DAC A, data input bit 4       |

| DA3    | 7   | I       | DAC A, data input bit 3       |

| DA2    | 8   | I       | DAC A, data input bit 2       |

| DA1    | 9   | I       | DAC A, data input bit 1       |

| DA0    | 10  | I       | DAC A, data input bit 0 (LSB) |

| n.c.   | 11  |         | not connected                 |

| n.c.   | 12  |         | not connected                 |

| n.c.   | 13  |         | not connected                 |

Table 2.

Pin description ...continued

| Table 2. Pin des | scription | .continuea |                                                       |

|------------------|-----------|------------|-------------------------------------------------------|

| Symbol           | Pin       | Type[1]    | Description                                           |

| n.c.             | 14        |            | not connected                                         |

| DGND             | 15        | G          | digital ground                                        |

| $V_{DDD}$        | 16        | S          | digital supply voltage                                |

| WRTA/IQWRT       | 17        | 1          | input write port A/input write IQ in Interleaved mode |

| CLKA/IQCLK       | 18        | I          | input clock port A/input clock IQ in Interleaved mode |

| CLKB/IQRESET     | 19        | I          | input clock port B/reset IQ in Interleaved mode       |

| WRTB/IQSEL       | 20        | Į          | input write port B/select IQ in Interleaved mode      |

| DGND             | 21        | G          | digital ground                                        |

| $V_{DDD}$        | 22        | S          | digital supply voltage                                |

| DB9              | 23        | I          | DAC B, data input bit 9 (MSB)                         |

| DB8              | 24        | I          | DAC B, data input bit 8                               |

| DB7              | 25        | I          | DAC B, data input bit 7                               |

| DB6              | 26        | I          | DAC B, data input bit 6                               |

| DB5              | 27        | I          | DAC B, data input bit 5                               |

| DB4              | 28        | I          | DAC B, data input bit 4                               |

| DB3              | 29        | I          | DAC B, data input bit 3                               |

| DB2              | 30        | I          | DAC B, data input bit 2                               |

| DB1              | 31        | I          | DAC B, data input bit 1                               |

| DB0              | 32        | l          | DAC B, data input bit 0 (LSB)                         |

| n.c.             | 33        |            | not connected                                         |

| n.c.             | 34        |            | not connected                                         |

| n.c.             | 35        |            | not connected                                         |

| n.c.             | 36        |            | not connected                                         |

| PWD              | 37        | I          | power-down mode                                       |

| AGND             | 38        | S          | analog ground                                         |

| IOUTBP           | 39        | 0          | DAC B current output                                  |

| IOUTBN           | 40        | 0          | complementary DAC B current output                    |

| BVIRES           | 41        | I          | adjust DAC B for full-scale output current            |

| GAINCTRL         | 42        | I          | gain control mode                                     |

| REFIO            | 43        | I/O        | reference I/O                                         |

| AVIRES           | 44        | l          | adjust DAC A for full-scale output current            |

| IOUTAN           | 45        | 0          | complementary DAC A current output                    |

| IOUTAP           | 46        | 0          | DAC A current output                                  |

| $V_{DDA}$        | 47        | S          | analog supply voltage                                 |

| MODE             | 48        | I          | select between Dual-port or Interleaved mode          |

<sup>[1]</sup> Type description: S = Supply; G = Ground; I = Input; O = Output; I/O = Input/Output.

## 7. Limiting values

Table 3. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol           | Parameter                 | Conditions                                                | Min             | Max             | Unit |

|------------------|---------------------------|-----------------------------------------------------------|-----------------|-----------------|------|

| $V_{DDD}$        | digital supply voltage    |                                                           | <u>[1]</u> –0.3 | +5.0            | V    |

| $V_{DDA}$        | analog supply voltage     |                                                           | <u>[1]</u> –0.3 | +5.0            | V    |

| $\Delta V_{DD}$  | supply voltage difference | between analog and digital supply voltage                 | -150            | +150            | mV   |

| $V_{I}$          | input voltage             | digital inputs referenced to DGND                         | -0.3            | +5.5            | V    |

|                  |                           | pins REFIO, AVIRES, BVIRES referenced to AGND             | -0.3            | +5.5            | V    |

| V <sub>O</sub>   | output voltage            | pins IOUTAP, IOUTAN, IOUTBP and IOUTBN referenced to AGND | -0.3            | $V_{DDA} + 0.3$ | V    |

| T <sub>stg</sub> | storage temperature       |                                                           | -55             | +150            | °C   |

| T <sub>amb</sub> | ambient temperature       |                                                           | -40             | +85             | °C   |

| Tj               | junction temperature      |                                                           | -               | 125             | °C   |

<sup>[1]</sup> All supplies are connected together.

#### 8. Thermal characteristics

Table 4. Thermal characteristics

| Symbol               | Parameter                                   | Conditions  | Тур  | Unit |

|----------------------|---------------------------------------------|-------------|------|------|

| $R_{th(j-a)}$        | thermal resistance from junction to ambient | in free air | 89.3 | K/W  |

| R <sub>th(c-a)</sub> | thermal resistance from case to ambient     | in free air | 60.6 | K/W  |

### 9. Characteristics

Table 5.

Characteristics

$V_{DDD} = V_{DDA} = 3.3 \ V$ ; AGND and DGND connected together;  $I_{O(fs)} = 20 \ mA$  and  $T_{amb} = -40 \ ^{\circ}C$  to +85  $^{\circ}C$ ; typical values measured at  $T_{amb} = 25 \ ^{\circ}C$ .

| Symbol           | Parameter                            | Conditions                                                                             | Min  | Тур  | Max       | Unit |

|------------------|--------------------------------------|----------------------------------------------------------------------------------------|------|------|-----------|------|

| Supplies         |                                      |                                                                                        |      |      |           |      |

| $V_{DDD}$        | digital supply voltage               |                                                                                        | 3.0  | 3.3  | 3.65      | V    |

| $V_{DDA}$        | analog supply voltage                |                                                                                        | 3.0  | 3.3  | 3.65      | V    |

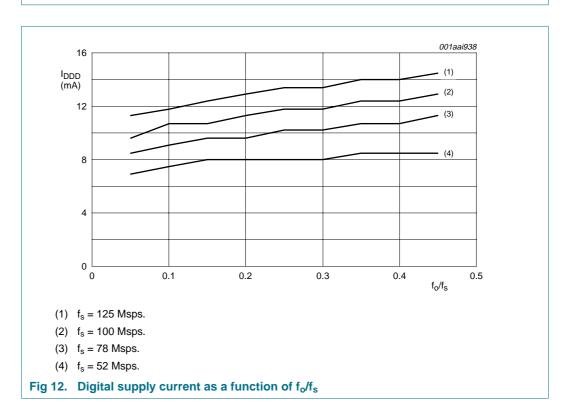

| I <sub>DDD</sub> | digital supply current               | $f_s$ = 65 Msps, $f_o$ = 1 MHz,<br>$V_{DD}$ = 3.0 V to 3.6 V                           | -    | 6    | 7         | mA   |

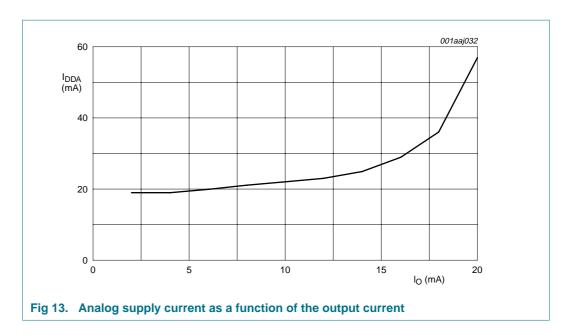

| I <sub>DDA</sub> | analog supply current                | $f_s = 65 \text{ Msps}, f_o = 1 \text{ MHz}, V_{DD} = 3.0 \text{ V to } 3.6 \text{ V}$ | -    | 50   | 65        | mA   |

| P <sub>tot</sub> | total power dissipation              | $f_{s}$ = 65 Msps, $f_{o}$ = 1 MHz,<br>V <sub>DD</sub> = 3.0 V to 3.6 V                | -    | 185  | 260       | mW   |

| $P_{pd}$         | power dissipation in power-down mode |                                                                                        | -    | 16.5 | -         | mW   |

| Digital in       | puts                                 |                                                                                        |      |      |           |      |

| V <sub>IL</sub>  | LOW-level input voltage              |                                                                                        | DGND | -    | 0.9       | V    |

| V <sub>IH</sub>  | HIGH-level input voltage             |                                                                                        | 1.3  | -    | $V_{DDD}$ | V    |

DAC1001D125\_1 © NXP B.V. 2008. All rights reserved.

Table 5.

Characteristics ...continued

$V_{DDD} = V_{DDA} = 3.3 \ V$ ; AGND and DGND connected together;  $I_{O(fs)} = 20 \ mA$  and  $T_{amb} = -40 \ ^{\circ}C$  to +85  $^{\circ}C$ ; typical values measured at  $T_{amb} = 25 \ ^{\circ}C$ .

| Symbol              | Parameter                       | Conditions                                                     |            | Min   | Тур   | Max   | Unit      |

|---------------------|---------------------------------|----------------------------------------------------------------|------------|-------|-------|-------|-----------|

| I <sub>IL</sub>     | LOW-level input current         | $V_{IL} = 0.9 V$                                               |            | -     | 5     | -     | μΑ        |

| I <sub>IH</sub>     | HIGH-level input current        | V <sub>IH</sub> = 1.3 V                                        |            | -     | 5     | -     | μΑ        |

| C <sub>i</sub>      | input capacitance               |                                                                | <u>[1]</u> | -     | 5     | -     | pF        |

| Analog o            | outputs: pins IOUTAP, IOUTAN, I | OUTBP and IOUTBN                                               |            |       |       |       |           |

| $I_{O(fs)}$         | full-scale output current       | differential outputs                                           |            | 2     | -     | 20    | mA        |

| $V_{O}$             | output voltage                  | compliance range                                               |            | -1    | -     | +1.25 | V         |

| $R_{o}$             | output resistance               |                                                                | <u>[1]</u> | -     | 150   | -     | $k\Omega$ |

| Co                  | output capacitance              |                                                                | <u>[1]</u> | -     | 3     | -     | pF        |

| Referenc            | e voltage input/output: pin REF | FIO                                                            |            |       |       |       |           |

| V <sub>O(ref)</sub> | reference output voltage        |                                                                | <u>[1]</u> | 1.25  | 1.26  | 1.27  | V         |

| I <sub>O(ref)</sub> | reference output current        |                                                                |            | -     | 100   | -     | nA        |

| Vi                  | input voltage                   | compliance range                                               |            | 1.0   | -     | 1.26  | V         |

| R <sub>i</sub>      | input resistance                |                                                                |            | -     | 1     | -     | $M\Omega$ |

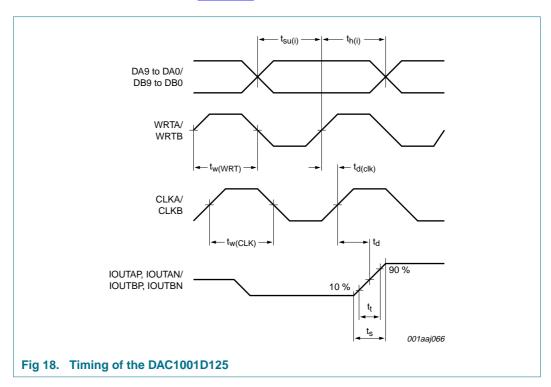

| Input tim           | ing; see <u>Figure 18</u>       |                                                                |            |       |       |       |           |

| fs                  | sampling frequency              |                                                                |            | -     | -     | 125   | Msps      |

| t <sub>w(WRT)</sub> | WRT pulse width                 | pins WRTA, WRTB                                                |            | 2     | -     | -     | ns        |

| t <sub>w(CLK)</sub> | CLK pulse width                 | pins CLKA, CLKB                                                |            | 2     | -     | -     | ns        |

| t <sub>h(i)</sub>   | input hold time                 |                                                                |            | 1     | -     | -     | ns        |

| t <sub>su(i)</sub>  | input set-up time               |                                                                |            | 1.8   | -     | -     | ns        |

| Output ti           | ming: pins IOUTAP, IOUTAN, IO   | UTBP and IOUTBN                                                |            |       |       |       |           |

| t <sub>d</sub>      | delay time                      |                                                                |            | -     | 1     | -     | ns        |

| t <sub>t</sub>      | transition time                 | rising or falling transition<br>(10 % to 90 % or 90 % to 10 %) | [1]        | -     | 0.6   | -     | ns        |

| t <sub>s</sub>      | settling time                   | ±1 LSB                                                         | <u>[1]</u> | -     | 16    | -     | ns        |

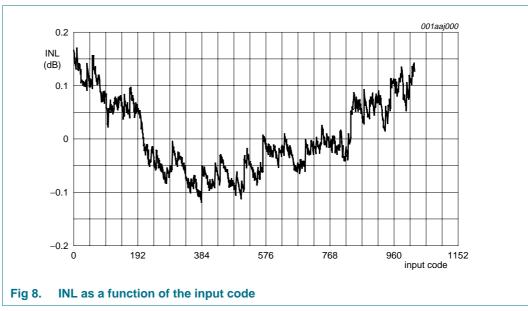

| Static lin          | earity                          |                                                                |            |       |       |       |           |

| INL                 | integral non-linearity          | 25 °C                                                          |            | ±0.1  | ±0.13 | ±0.18 | LSB       |

|                     |                                 | –40 °C to +85 °C                                               |            | ±0.08 | -     | ±0.18 | LSB       |

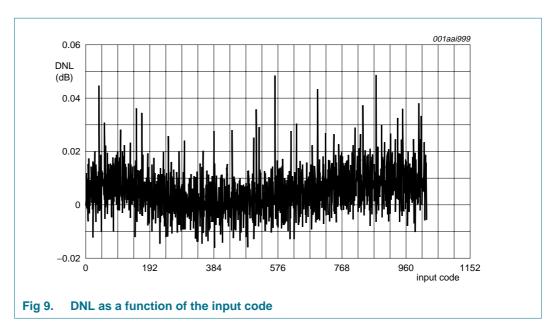

| DNL                 | differential non-linearity      | –40 °C to +85 °C                                               |            | ±0.03 | ±0.05 | ±0.07 | LSB       |

| Static ac           | curacy (relative to full-scale) |                                                                |            |       |       |       |           |

| E <sub>offset</sub> | offset error                    |                                                                |            | -0.02 | -     | +0.02 | %         |

| E <sub>G</sub>      | gain error                      | with external reference                                        |            | -1.9  | ±1.5  | +2.5  | %         |

|                     |                                 | with internal reference                                        |            | -2.9  | ±2.1  | +2.9  | %         |

| ΔG                  | gain mismatch                   | between DAC A and DAC B                                        |            | -0.36 | ±0.5  | +0.36 | %         |

Table 5.

Characteristics ...continued

$V_{DDD} = V_{DDA} = 3.3 \ V$ ; AGND and DGND connected together;  $I_{O(fs)} = 20 \ mA$  and  $T_{amb} = -40 \ ^{\circ}C$  to +85  $^{\circ}C$ ; typical values measured at  $T_{amb} = 25 \ ^{\circ}C$ .

| Symbol          | Parameter                         | Conditions                                                                                             | Min | Тур    | Max | Unit  |

|-----------------|-----------------------------------|--------------------------------------------------------------------------------------------------------|-----|--------|-----|-------|

| Dynamic         | performance                       |                                                                                                        |     |        |     |       |

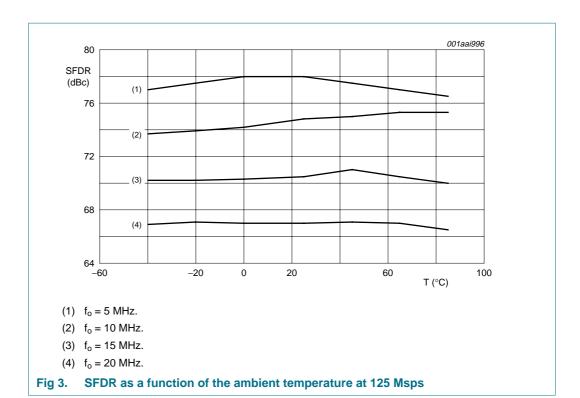

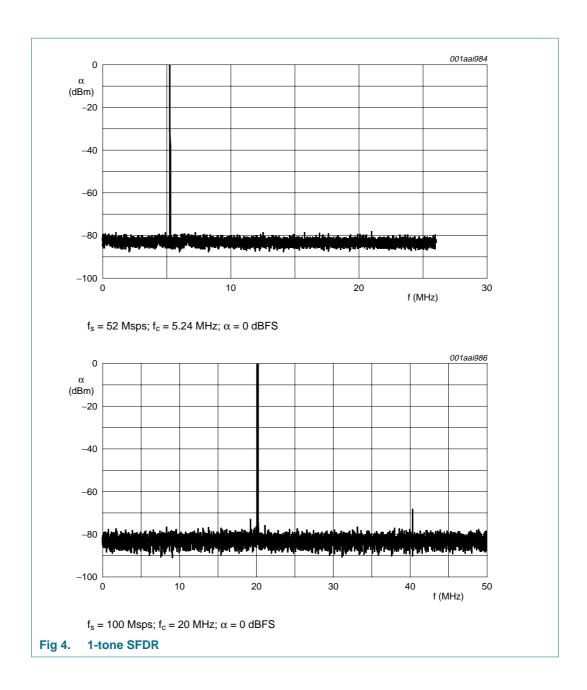

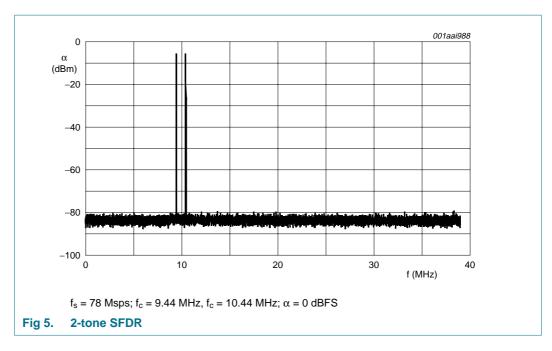

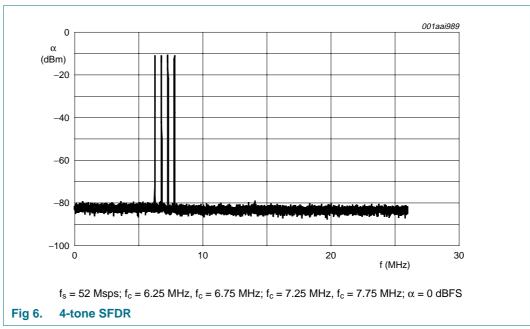

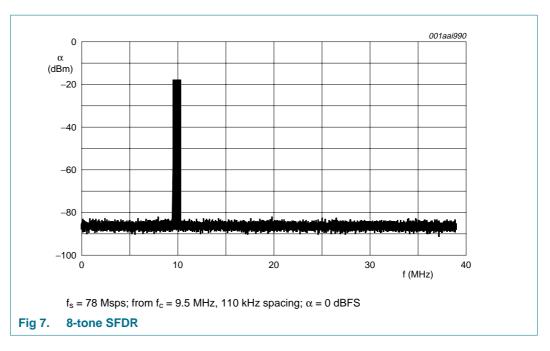

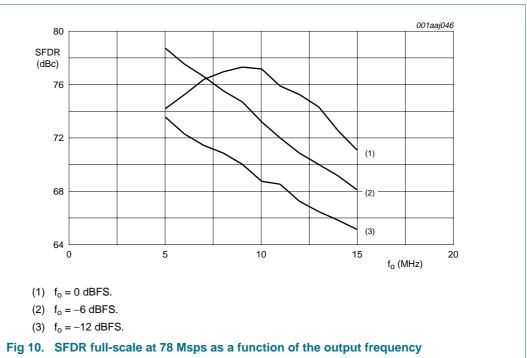

| SFDR            | spurious free dynamic range       | B = Nyquist                                                                                            |     |        |     |       |

|                 |                                   | $f_s = 52 \text{ Msps}; f_o = 1 \text{ MHz}$                                                           |     |        |     |       |

|                 |                                   | 0 dBFS                                                                                                 | -   | 80     | -   | dBc   |

|                 |                                   | -6 dBFS                                                                                                | -   | 78     | -   | dBc   |

|                 |                                   | -12 dBFS                                                                                               | -   | 72     | -   | dBc   |

|                 |                                   | f <sub>s</sub> = 52 Msps; 0 dBFS                                                                       |     |        |     |       |

|                 |                                   | f <sub>o</sub> = 5.24 MHz                                                                              | -   | 78     | -   | dBc   |

|                 |                                   | f <sub>s</sub> = 78 Msps; 0 dBFS                                                                       |     |        |     |       |

|                 |                                   | f <sub>o</sub> = 10.4 MHz                                                                              | -   | 77     | -   | dBc   |

|                 |                                   | f <sub>o</sub> = 15.7 MHz                                                                              | -   | 70     | -   | dBc   |

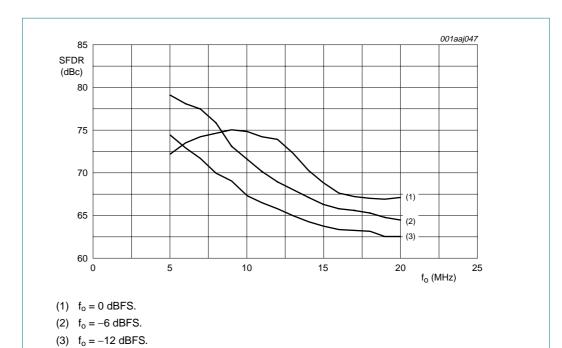

|                 |                                   | f <sub>s</sub> = 100 Msps; 0 dBFS                                                                      |     |        |     |       |

|                 |                                   | f <sub>o</sub> = 5.04 MHz                                                                              | -   | 76     | -   | dBc   |

|                 |                                   | f <sub>o</sub> = 20.2 MHz                                                                              | 60  | 68     | -   | dBc   |

|                 | f <sub>s</sub> = 125 Msps; 0 dBFS |                                                                                                        |     |        |     |       |

|                 |                                   | f <sub>o</sub> = 20.1 MHz                                                                              | -   | 67     | -   | dBc   |

|                 |                                   | Within a Window                                                                                        |     |        |     |       |

|                 |                                   | $f_s = 52 \text{ Msps}$ ; $f_o = 1 \text{ MHz}$ ; 2 MHz span                                           | -   | 87     | -   | dBc   |

|                 |                                   | $f_s$ = 52 Msps; $f_o$ = 5.24 MHz;<br>10 MHz span                                                      | -   | 85     | -   | dBc   |

|                 |                                   | $f_s = 78 \text{ Msps}; f_o = 5.26 \text{ MHz};$<br>10 MHz span                                        | -   | 88     | -   | dBc   |

|                 |                                   | $f_s = 125 \text{ Msps}; f_o = 5.04 \text{ MHz};$<br>10 MHz span                                       | 78  | 88     | -   | dBc   |

| THD             | total harmonic distortion         | $f_s = 52 \text{ Msps}; f_o = 1 \text{ MHz}$                                                           | -   | -77    | -   | dBc   |

|                 |                                   | $f_s = 78 \text{ Msps}; f_o = 5.26 \text{ MHz}$                                                        | -   | -75    | -   | dBc   |

|                 |                                   | $f_s = 100 \text{ Msps}; f_o = 5.04 \text{ MHz}$                                                       | -   | -73    | -   | dBc   |

|                 |                                   | $f_s = 125 \text{ Msps}; f_o = 20.1 \text{ MHz}$                                                       | -   | -63    | -59 | dBc   |

| MTPR            | multitone power ratio             | $f_s = 65 \text{ Msps};$<br>2 MHz < $f_o$ < 2.99 MHz; 8 tones at<br>110 kHz spacing at 0 dB full-scale | -   | 80     | -   | dBc   |

| NSD             | noise spectral density            | $f_s = 100 \text{ Msps}; f_o = 5.04 \text{ MHz}$                                                       | -   | -148.5 | -   | dBm/H |

| α <sub>cs</sub> | channel separation                | $f_s = 78 \text{ Msps}; f_o = 10.4 \text{ MHz}$                                                        | -   | 88.0   | -   | dBc   |

|                 |                                   | $f_s = 125 \text{ Msps}; f_o = 20.1 \text{ MHz}$                                                       | -   | 83.5   | -   | dBc   |

<sup>[1]</sup> Guaranteed by design.

Fig 11. SFDR full-scale at 125 Msps as a function of the output frequency

### 10. Application information

#### 10.1 General description

The DAC1001D125 is a dual 10-bit DAC operating up to 125 Msps. Each DAC consists of a segmented architecture, comprising a 7-bit thermometer sub-DAC and a 3-bit binary weighted sub-DAC.

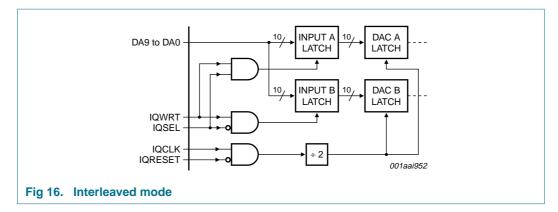

Two modes are available for the digital input depending on the status of the pin MODE. In Dual-port mode, each DAC uses its own data input line at the same frequency as the update rate. In Interleaved mode, both DACs use the same data input line at twice the update rate.

Each DAC generates on pins IOUTAP/IOUTAN and IOUTBP/IOUTBN two complementary current outputs. This provides a full-scale output current ( $I_{O(fs)}$ ), up to 20 mA. A single common or two independent full-scale current controls can be selected for both channels using pin GAINCTRL. An internal reference is available for the reference current, which is externally adjustable using pin REFIO.

The DAC1001D125 operates at 3.3 V and has separate digital and analog power supplies. Pin PWD is used to power-down the device. The digital input is 1.8 V compliant, 3.3 V compliant and 5 V tolerant.

#### 10.2 Input data

The DAC1001D125 input follows a straight binary coding where DA9 and DB9 are the Most Significant Bits (MSB) and DA0 and DB0 are the Least Significant Bits (LSB).

The setting applied to pin MODE defines whether the DAC1001D125 operates in Dual-port mode or in Interleaved mode (see Table 6).

Table 6. Mode selection

| Mode | Function         | DA9 to DA0 | DB9 to DB0 | Pin 17 | Pin 18 | Pin 19  | Pin 20 |

|------|------------------|------------|------------|--------|--------|---------|--------|

| 0    | Interleaved mode | active     | off        | IQWRT  | IQCLK  | IQRESET | IQSEL  |

| 1    | Dual-port mode   | active     | active     | WRTA   | CLKA   | CLKB    | WRTB   |

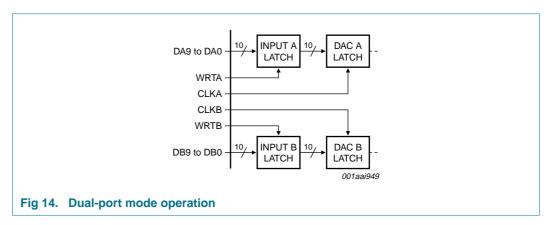

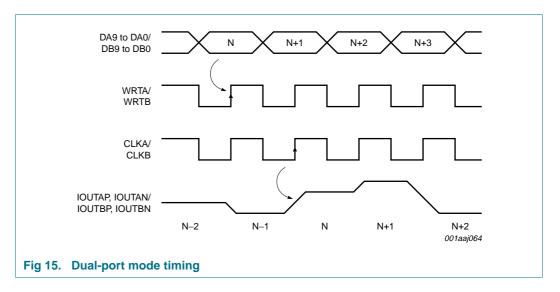

#### 10.2.1 Dual-port mode

The data and clock circuit for Dual-port mode operation is shown in Figure 14.

Each DAC has its own independent data and clock inputs. The data enters the input latch on the rising edge of the WRTA/WRTB signal and is transferred to the DAC latch. The output is updated on the rising edge of the CLKA/CLKB signal.

#### 10.2.2 Interleaved mode

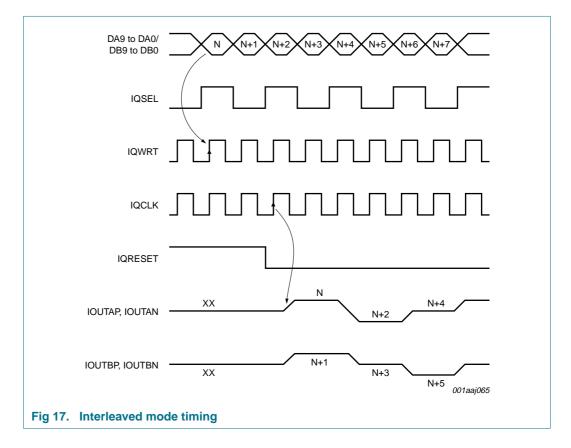

The data and clock circuit for Interleaved mode operation is illustrated in Figure 16.

In Interleaved mode, both DACs use the same data and clock inputs at twice the update rate. Data enters the latch on the rising edge of IQWRT. The data is sent to either latch A or latch B, depending on the value of IQSEL. The IQSEL transition must occur when IQWRT and IQCLK are LOW.

The IQCLK is divided by 2 internally and the data is transferred to the DAC latch. It is updated on its rising edge. When IQRESET is HIGH, IQCLK is disabled, see Figure 17.

#### 10.3 Timing

The DAC1001D125 can operate at an update rate of 125 Msps, which generates an input data rate of 125 MHz in Dual-port mode and 250 MHz in Interleaved mode. The timing of the DAC1001D125 is shown in Figure 18.

The typical performances are measured at 50 % duty cycle but any timing within the limits of the characteristics will not alter the performance.

- A configuration resulting in the same timing for the signals WRTA/WRTB and CLKA/CLKB, can be achieved either by synchronizing them or by connecting them together.

- The rising edge of the CLKA/CLKB signal can also be placed in a range from half a

period in front of the rising edge of the WRTA/WRTB signal to half a period minus 1 ns

after the rising edge of the WRTA/WRTB signal.

A typical set-up time of 0 ns and a hold time of 0.6 ns enable the DAC1001D125 to be easily integrated into any application.

#### 10.4 DAC transfer function

The full-scale output current for each DAC is the sum of the two complementary current outputs:

$$I_{O(fs)} = I_{IOUTP} + I_{IOUTN} \tag{1}$$

The output current depends on the digital input data:

$$I_{IOUTP} = I_{O(fs)} \times \left(\frac{DATA}{1024}\right)$$

$I_{IOUTN} = I_{O(fs)} \times \left(\frac{(1023 - DATA)}{1024}\right)$

DAC1001D125\_1 © NXP B.V. 2008. All rights reserved.

<u>Table 7</u> shows the output current as a function of the input data, when  $I_{O(fs)} = 20$  mA.

Table 7. DAC transfer function

| Data  | DA9/DB9 to DA0/DB0 | IOUTAP/IOUTBP | IOUTAN/IOUTBN |

|-------|--------------------|---------------|---------------|

| 0     | 00 0000 0000       | 0 mA          | 20 mA         |

|       |                    |               |               |

| 8192  | 10 0000 0000       | 10 mA         | 10 mA         |

|       |                    |               |               |

| 16383 | 11 1111 1111       | 20 mA         | 0 mA          |

#### 10.5 Full-scale current adjustment

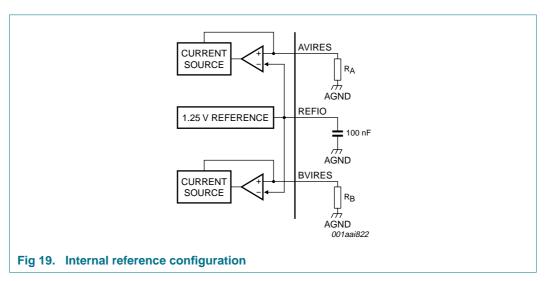

The DAC1001D125 integrates one 1.25 V reference and two current sources to adjust the full-scale current in both DACs.

The internal reference configuration is shown in Figure 19.

The bias current is generated by the output of the internal regulator connected to the inverting input of the internal operational amplifiers. The external resistors  $R_A$  and  $R_B$  are connected to pins AVIRES and BVIRES, respectively. This configuration is optimal for temperature drift compensation because the band gap can be matched with the voltage on the feedback resistors.

The relationship between full-scale output current  $(I_{O(fs)})$  at the output of channel A or channel B and the resistor is:

$$I_{O(fs)} = \frac{24V_{REFIO}}{R_A} \tag{2}$$

The output current of the two DACs is typically fixed to 20 mA when both resistors  $R_A$  and  $R_B$  are set to 1.5 k $\Omega$ . The operational range of DAC1001D125 is from 2 mA to 20 mA.

It is recommended to decouple pin REFIO with a 100 nF capacitor.

An external reference can also be used for applications requiring higher accuracy or precise current adjustment. Due to the high input impedance of pin REFIO, applying an external source disables the band gap.

#### 10.6 Gain control

Table 8 shows how to select the different gain control modes.

Table 8. Gain control

| GAINCTRL | Mode                     | DAC A<br>full-scale control | DAC B<br>full-scale control |

|----------|--------------------------|-----------------------------|-----------------------------|

| 0        | independent gain control | AVIRES                      | BVIRES                      |

| 1        | common gain control      | AVIRES                      | AVIRES                      |

In independent gain mode, both full-scale currents can be adjusted independently using resistors  $R_A$  on pin AVIRES and  $R_B$  on pin BVIRES.

In common gain mode, both full-scale currents are adjusted with the same resistor and divided by two in both DACs.

#### 10.7 Analog outputs

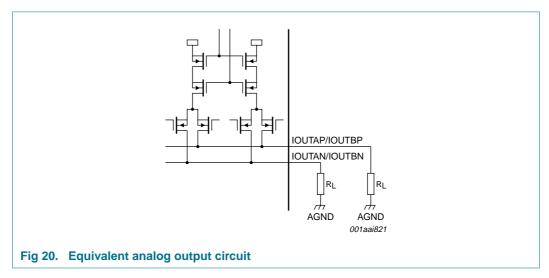

See <u>Figure 20</u> for the analog output circuit of one DAC. This circuit consists of a parallel combination of PMOS current sources and associated switches for each segment.

Cascode source configuration enables the output impedance of the source to be increased, thus improving the dynamic performance by reducing distortion.

The DAC1001D125 can be used either with:

- a differential output, coupled to a transformer (or operational amplifier) to reduce even-order harmonics and noise

- or a single-ended output for applications requiring unipolar voltage.

The typical configuration is to use 1 V p-p level on each output IOUTAP/IOUTBP and IOUTAN/IOUTBN but several combinations can be used as far as they respect the voltage compliance range.

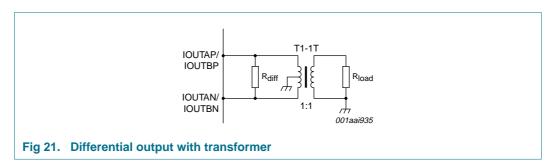

#### 10.7.1 Differential output using transformer

The use of a differentially coupled transformer output (see <u>Figure 21</u>) provides optimum distortion performance. In addition, it helps to match the impedance and provides electrical isolation.

The center tap is grounded to allow the DC current flow to/from both outputs. If the center tap is open, the differential resistor must be replaced by two resistors connected to ground.

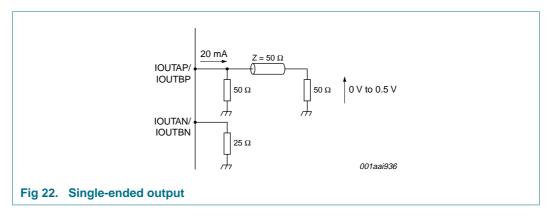

#### 10.7.2 Single-ended output

Using a single load resistor on one current output will provide an unipolar output range, typically from 0 V to 0.5 V with a 20 mA full-scale current at a 50  $\Omega$  load.

The resistor on the other current output is 25  $\Omega$ .

#### 10.8 Power-down function

The DAC1001D125 has a power-down function to reduce the power consumption when it is not active.

Table 9. Power-down

| PWD | Device function | Power dissipation (typ) |

|-----|-----------------|-------------------------|

| 0   | active          | 185 mW                  |

| 1   | not active      | 16.5 mW                 |

### 10.9 Alternative parts

The following alternative parts are also available.

Table 10. Alternative parts

Pin compatible

| Type number | Description     | Sampling frequency |

|-------------|-----------------|--------------------|

| DAC1401D125 | dual 14-bit DAC | up to 125 Msps     |

| DAC1201D125 | dual 12-bit DAC | up to 125 Msps     |

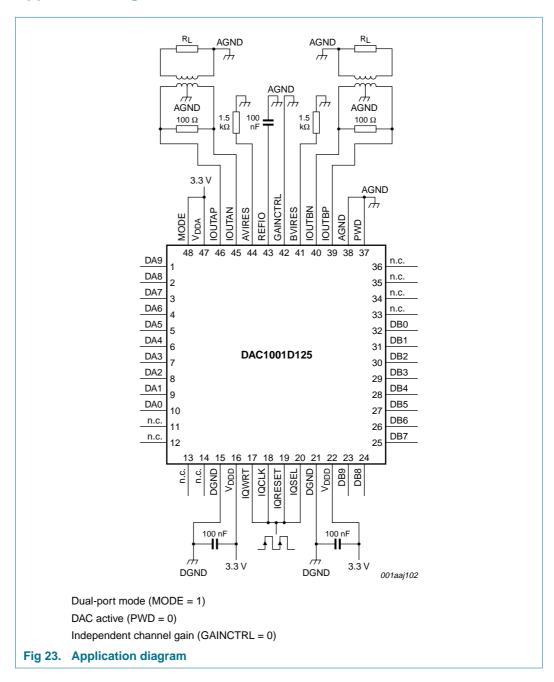

### 10.10 Application diagram

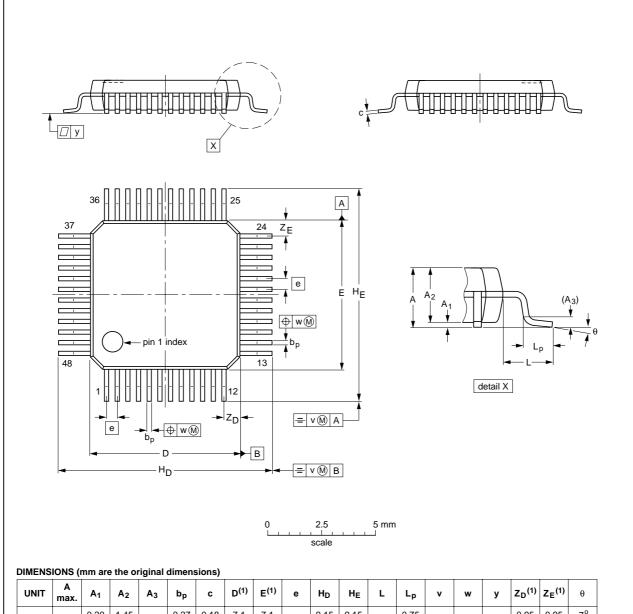

## 11. Package outline

LQFP48: plastic low profile quad flat package; 48 leads; body 7 x 7 x 1.4 mm

SOT313-2

| UNIT | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | A <sub>3</sub> | bp           | C            | D <sup>(1)</sup> | E <sup>(1)</sup> | е   | H <sub>D</sub> | HE           | L | Lp           | ٧   | w    | у   | Z <sub>D</sub> <sup>(1)</sup> | Z <sub>E</sub> <sup>(1)</sup> | θ        |

|------|-----------|----------------|----------------|----------------|--------------|--------------|------------------|------------------|-----|----------------|--------------|---|--------------|-----|------|-----|-------------------------------|-------------------------------|----------|

| mm   | 1.6       | 0.20<br>0.05   | 1.45<br>1.35   | 0.25           | 0.27<br>0.17 | 0.18<br>0.12 | 7.1<br>6.9       | 7.1<br>6.9       | 0.5 | 9.15<br>8.85   | 9.15<br>8.85 | 1 | 0.75<br>0.45 | 0.2 | 0.12 | 0.1 | 0.95<br>0.55                  | 0.95<br>0.55                  | 7°<br>0° |

#### Note

1. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

| OUTLINE  |        | REFER  | EUROPEAN | ISSUE DATE |            |                                 |  |

|----------|--------|--------|----------|------------|------------|---------------------------------|--|

| VERSION  | IEC    | JEDEC  | JEITA    |            | PROJECTION | ISSUE DATE                      |  |

| SOT313-2 | 136E05 | MS-026 |          |            |            | <del>00-01-19</del><br>03-02-25 |  |

Fig 24. Package outline SOT313-2 (LQFP48)

DAC1001D125\_1 © NXP B.V. 2008. All rights reserved.

### 12. Abbreviations

Table 11. Abbreviations

| Acronym | Description                        |

|---------|------------------------------------|

| BW      | BandWidth                          |

| dBFS    | deciBel Full Scale                 |

| DDS     | Direct Digital frequency Synthesis |

| IF      | Intermediate Frequency             |

| LSB     | Least Significant Bit              |

| MSB     | Most Significant Bit               |

| SFDR    | Spurious-Free Dynamic Range        |

## 13. Revision history

#### Table 12. Revision history

| Document ID   | Release date | Data sheet status  | Change notice | Supersedes |

|---------------|--------------|--------------------|---------------|------------|

| DAC1001D125_1 | 20081124     | Product data sheet | -             | -          |

### 14. Legal information

#### 14.1 Data sheet status

| Document status[1][2]          | Product status[3] | Definition                                                                            |

|--------------------------------|-------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet   | Development       | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet | Qualification     | This document contains data from the preliminary specification.                       |

| Product [short] data sheet     | Production        | This document contains the product specification.                                     |

- [1] Please consult the most recently issued document before initiating or completing a design.

- [2] The term 'short data sheet' is explained in section "Definitions"

- [3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL <a href="http://www.nxp.com">http://www.nxp.com</a>.

#### 14.2 Definitions

Draft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

#### 14.3 Disclaimers

**General** — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

**Suitability for use** — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or

malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) may cause permanent damage to the device. Limiting values are stress ratings only and operation of the device at these or any other conditions above those given in the Characteristics sections of this document is not implied. Exposure to limiting values for extended periods may affect device reliability.

Terms and conditions of sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at <a href="http://www.nxp.com/profile/terms">http://www.nxp.com/profile/terms</a>, including those pertaining to warranty, intellectual property rights infringement and limitation of liability, unless explicitly otherwise agreed to in writing by NXP Semiconductors. In case of any inconsistency or conflict between information in this document and such terms and conditions, the latter will prevail.

**No offer to sell or license** — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

#### 14.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

#### 15. Contact information

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: <a href="mailto:salesaddresses@nxp.com">salesaddresses@nxp.com</a>

DAC1001D125\_1 © NXP B.V. 2008. All rights reserved.

### 16. Contents

| 1                  | General description                   | 1    |

|--------------------|---------------------------------------|------|

| 2                  | Features                              | 1    |

| 3                  | Applications                          | 1    |

| 4                  | Ordering information                  | 2    |

| 5                  | Block diagram                         | 2    |

| 6                  | Pinning information                   | 3    |

| 6.1                | Pinning                               | 3    |

| 6.2                | Pin description                       |      |

| 7                  | Limiting values                       | 5    |

| 8                  | Thermal characteristics               | 5    |

| 9                  | Characteristics                       | 5    |

| 10                 | Application information               | . 14 |

| 10.1               | General description                   | . 14 |

| 10.2               | Input data                            | . 14 |

| 10.2.1             | Dual-port mode                        |      |

| 10.2.2             | Interleaved mode                      |      |

| 10.3               | Timing                                |      |

| 10.4               | DAC transfer function                 |      |

| 10.5               | Full-scale current adjustment         |      |

| 10.6               | Gain control                          |      |

| 10.7               | Analog outputs                        |      |

| 10.7.1             | Differential output using transformer |      |

| 10.7.2             | Single-ended output                   |      |

| 10.8<br>10.9       | Power-down function                   |      |

| 10.9<br>10.10      | Alternative parts                     |      |

| 10.10<br><b>11</b> | Package outline                       |      |

| 11<br>12           | _                                     |      |

| 12                 | Abbreviations                         |      |

|                    | Revision history                      |      |

| 14                 | Legal information                     |      |

| 14.1               | Data sheet status                     |      |

| 14.2               | Definitions                           |      |

| 14.3               | Disclaimers                           |      |

| 14.4               | Trademarks                            |      |

| 15                 | Contact information                   |      |

| 16                 | Contents                              | . 25 |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.