# SANYO Semiconductors DATA SHEET

#### Overview

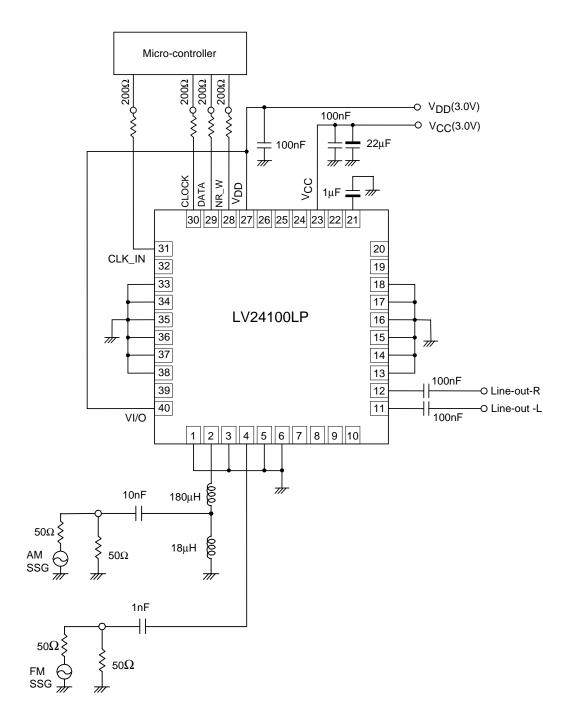

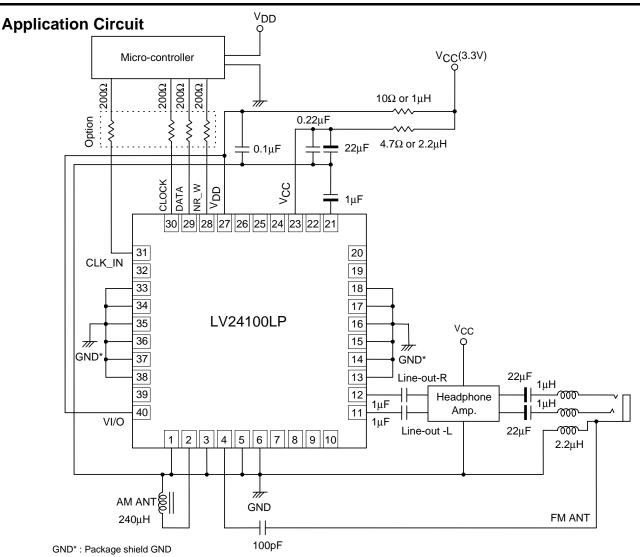

The LV24100LP is an innovative FM/AM tuner IC that is capable of configuring an FM/AM radio with just one external component. Since all the FM/AM radio functions are incorporated into a compact VQLP package with dimensions of only 5mm×0.8mm, this IC can easily incorporate FM/AM tuner function into mobile phones, PDA, MP3 player and other small mobile sets where space is always at a premium.

#### **Functions**

- FM Tuner

- AM Tuner

- MPX stereo decoder

- Tuning

#### **Features**

- No external components required except for an AM bar antenna.

- No alignments necessary

- Improved selectivity with low FMIF frequency (110kHz)

- Built-in adjacent channel interference total reduction (no 114kHz, no 190kHz)

- New tuning system

- Very high sensitivity reception with low-noise mixer input circuit

- Built-in low power standby mode eliminates the need for a power switch circuit.

- Composite output for RDS applications

- 3-wire bus interface (data, clock, and NR-W) featured

- Digital AFC function provided

- Soft muting and stereo blend functions (8-step software control)

- Support for manual search, automatic search, and auto preset

- Support for reception of worldwide bands

(reception of all bands in Japan, Europe, and the US enabled by changes in the program.)

- Any and all SANYO Semiconductor Co.,Ltd. products described or contained herein are, with regard to "standard application", intended for the use as general electronics equipment (home appliances, AV equipment, communication device, office equipment, industrial equipment etc.). The products mentioned herein shall not be intended for use for any "special application" (medical equipment whose purpose is to sustain life, aerospace instrument, nuclear control device, burning appliances, transportation machine, traffic signal system, safety equipment etc.) that shall require extremely high level of reliability and can directly threaten human lives in case of failure or malfunction of the product or may cause harm to human bodies, nor shall they grant any guarantee thereof. If you should intend to use our products for applications outside the standard applications, please consult with us prior to the intended use. If there is no consultation or inquiry before the intended use, our customer shall be solely responsible for the use.

- Specifications of any and all SANYO Semiconductor Co.,Ltd. products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

## **Specifications**

#### **Maximum Ratings** at $Ta = 25^{\circ}C$

| Parameter                   | Symbol                | Conditions                              | Ratings              | Unit |

|-----------------------------|-----------------------|-----------------------------------------|----------------------|------|

| Maximum supply voltage      | V <sub>CC</sub> max   | Analog block supply voltage             | 5.0                  | V    |

|                             | V <sub>DD</sub> max   | Digital block supply voltage            | 4.5                  | V    |

| Digital input voltage       | V <sub>IN</sub> 1 max | Clock, Data, NR_W                       | V <sub>DD</sub> +0.3 | V    |

|                             | V <sub>IN</sub> 2 max | External_clk_in                         | V <sub>DD</sub> +0.3 | V    |

| Allowable power dissipation | Pd max                | Ta≤70°C, Mounted on a specified board * | 140                  | mW   |

| Operating temperature       | Topr                  |                                         | -20 to +70           | °C   |

| Storage temperature         | Tstg                  |                                         | -40 to +125          | °C   |

Note: Mounted on a specified board: 40mm×50mm×0.8mm, glass epoxy

#### **Operating Condition** at $Ta = 25^{\circ}C$

| Parameter                      | Symbol             | Conditions                   | Ratings    | Unit |

|--------------------------------|--------------------|------------------------------|------------|------|

| Recommended supply voltage     | V <sub>CC</sub>    | Analog block supply voltage  | 3.0        | V    |

|                                | V <sub>DD</sub>    | Digital block supply voltage | 3.0        | V    |

| Operating supply voltage range | V <sub>CC</sub> op |                              | 3.0 to 4.8 | V    |

|                                | V <sub>DD</sub> op |                              | 3.0 to 4.0 | V    |

|                                | V <sub>IO</sub> op | Interface voltage            | 1.8 to 4.0 | V    |

Note: The V<sub>IO</sub> application voltage must be either equivalent to V<sub>DD</sub> or the V<sub>DD</sub> value or less. (V<sub>IO</sub>  $\leq$  V<sub>DD</sub>)

#### Interface Block Allowable Operation Range at Ta = -20 to $+70^{\circ}C$ , $V_{IO} = 3.0V$ , $V_{SS} = 0V$

| Parameter                                 | Symbol Conditions |                                            |                    | Ratings |                 |      |  |

|-------------------------------------------|-------------------|--------------------------------------------|--------------------|---------|-----------------|------|--|

| Parameter                                 | Symbol            | Conditions                                 | min                | typ     | max             | Unit |  |

| Supply voltage                            | V <sub>DD</sub>   |                                            | 2.5                |         | 4.0             | V    |  |

| Digital block input                       | VIH               | High level input voltage range             | 0.7V <sub>DD</sub> |         | V <sub>DD</sub> | V    |  |

|                                           | VIL               | Low level input voltage range              | 0                  |         | 0.6             | V    |  |

| Digital block output                      | IOL               | Output current at Low level                | 2.0                |         |                 | mA   |  |

|                                           | VOL               | Output voltage at Low level IOL=2mA        |                    |         | 0.6             | V    |  |

| Clock input operating frequency           | fclk              | (Pin29) clock frequency for 3wire_bus      |                    |         | 0.7             | MHz  |  |

| External clock operating frequency        | fclk_ext          | (Pin31) clock frequency for external input | 32k                |         | 14M             | Hz   |  |

| External clock operating voltage Vclk_ext |                   | (Pin31) clock voltage for external input   | 0.7V <sub>DD</sub> |         | V <sub>DD</sub> | V    |  |

Note: External clock input (pin31) allows also input of the sine wave signal. Frequency deviation is need 250ppm.

## $\textbf{Operating Characteristics} \text{ at } Ta=25^{\circ}C, \ V_{CC}=3.0V, \ V_{DD}=3.0V, \ V_{IO}=3.0V, \ V_{SS}=0V, \ Soft \ Mute/Soft \ Stereo=off, \ Soft \ Mute/Soft \ Mute/Soft \ Stereo=off, \ Soft \ Mute/Soft \ Stereo=off, \ Soft \ Mute/Soft \ Mute/Soft \ Stereo=off, \ Soft \ Mute/Soft \ Mute/$

#### with the specified test circuit. Output level setting means control register Block 2, Register 07h Bit 6(VOLSH)=0, Register 09h Bit 0 (nAUBST) =0.

| Parameter                                                                                    | Symbol               | Conditions                                                                 | Ratings  |      |     | Unit  |

|----------------------------------------------------------------------------------------------|----------------------|----------------------------------------------------------------------------|----------|------|-----|-------|

| i aldifieter                                                                                 | Symbol               | Conditions                                                                 | min      | typ  | max | Offic |

| Current drain (in operation)                                                                 | ICCA_FM              | Measurement at pin 23 with FM 60dBµV monaural input of the analog section. |          | 14   | 17  |       |

|                                                                                              | ICCA_AM              | Measurement at pin 23 with AM $80dB\mu V$ input of the analog section.     | 9        | 12   | 15  | mA    |

|                                                                                              | ICCD                 | Measurement at pins 27 and 40 with FM 60dBµV input in the digital block.   | 0.1      | 0.5  | 0.8 |       |

| Current drain (in standby)                                                                   | ICCA_stb             | Measurement at pin 23 in the standby mode of the analog block.             |          | 3    | 30  |       |

|                                                                                              | ICCD_stb             | Measurement at pins 27 and 40 in the standby mode of the digital block.    |          | 3    | 30  | μΑ    |

| FM receive band                                                                              | F_range              | In the PCB mounting conditions                                             | 76       |      | 108 | MHz   |

| FM receiving characteristics MONO<br>: fc=80MHz, fm=1kHz, 22.5kHz dev. V <sub>IN</sub> =6    | 0dBµV, Audio filter= | -IHF_BPF                                                                   |          |      |     |       |

| 3dB sensitivity                                                                              | -3dB LS              | 22.5kHz dev. output standard, input -3dB.                                  |          | 5    | 11  | dBµV  |

| Practical sensitivity 1                                                                      | QS1                  | Input level with S/N=30dB                                                  |          | 10   | 16  | dBμV  |

| Practical sensitivity 2 (Reference)                                                          | QS2                  | Input level with S/N=26dB                                                  |          | 1.25 |     | μV    |

| Demodulator output                                                                           | VO                   | Pin11 output                                                               | 50       | 70   | 110 | mV    |

| Channel balance                                                                              | СВ                   | Pin11/pin12 output                                                         | -2       | 0    | 2   | dB    |

| Signal-to-noise ratio                                                                        | S/N                  | Pin11 output                                                               | 48       | 58   |     | dB    |

| Total harmonic distortion 1 (MONO)                                                           | THD1                 | Pin11 output, 22.5kHz dev.                                                 |          | 0.4  | 1.5 | %     |

| Total harmonic distortion 2 (MONO)                                                           | THD2                 | Pin11 output, 75kHz dev.                                                   |          | 1.3  | 3.0 | %     |

| Field intensity display level                                                                | FS                   | Input level at which FS3 changes to FS4                                    | 35       |      | 49  | dBµV  |

| Mute attenuation                                                                             | Mute-Att             | Pin 11 output                                                              | 60       | 70   |     | dB    |

| FM receive characteristic STEREO chara<br>: fc=80MHz, fm=1kHz, V $_{IN}$ 60dB $\mu$ V, L+R=9 |                      | Pilot=10% (7.5kHz dev.), Audio filter = IHF_BPF+1                          | 5kHz_LPF | -    |     |       |

| Separation                                                                                   | SEP                  | L-mod, Pin11/pin12 output                                                  | 20       | 35   |     | dB    |

| Total harmonic distortion (Main)                                                             | THD-ST               | Main-mod (for L+R input), Pin11 output                                     |          | 1.3  | 3.0 | %     |

| AM receive characteristic<br>: fc=1.2MHz, fm=1kHz, 30% mod, Audio filt                       | er = IHF_BPF         |                                                                            |          |      |     |       |

| Demodulation output 1                                                                        | V <sub>O</sub> 1     | V <sub>IN</sub> =30dBµV, Pin11 output                                      | 35       | 55   | 80  | mVrm  |

| Demodulation output 2                                                                        | V <sub>O</sub> 2     | V <sub>IN</sub> =80dBµV, Pin11 output                                      | 30       | 50   | 75  | mVrm  |

| Signal-to-noise ratio 1                                                                      | S/N1                 | V <sub>IN</sub> =30dBµV, Pin11 output                                      | 14       | 21   |     | dB    |

| Signal-to-noise ratio 2                                                                      | S/N2                 | VIN=80dBµV, Pin11 output                                                   | 40       | 45   |     | dB    |

| Total harmonic distortion                                                                    | THD                  | VIN=80dBµV, Pin11 output                                                   |          | 1.0  | 3.0 | %     |

| Field intensity display level                                                                | FS                   | Input level at which FS3 changes to FS4                                    | 35       |      | 49  | dBµV  |

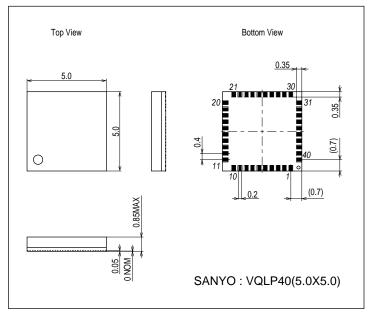

# Package Dimensions

unit : mm (typ) 3302A

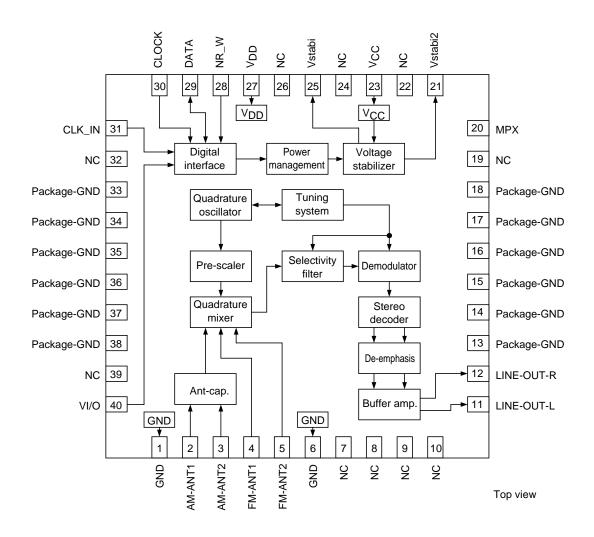

## **Block Diagram and Pin Assigment**

# **Pin Discription**

| Pin | Name               | I/O | Description                                     | Remarks                       | DC Voltage            |

|-----|--------------------|-----|-------------------------------------------------|-------------------------------|-----------------------|

| 1   | GND                |     | Analog and Digital GND                          |                               |                       |

| 2   | AM-ANT1            | 1   | AM Antenna input                                |                               |                       |

| 3   | AM-ANT2            | I   | AM Antenna GND                                  |                               |                       |

| 4   | FM-ANT1            | 1   | FM Antenna input                                |                               |                       |

| 5   | FM-ANT2            | I   | FM Antenna GND                                  |                               |                       |

| 6   | GND                |     | Analog and Digital GND                          |                               |                       |

| 7   | NC                 |     |                                                 |                               |                       |

| 8   | NC                 |     |                                                 |                               |                       |

| 9   | NC                 |     |                                                 |                               |                       |

| 10  | NC                 |     |                                                 |                               |                       |

| 11  | LINE-OUT-L         | 0   | Radio Lch Line-output                           |                               | 1.2V                  |

| 12  | LINE-OUT-R         | 0   | Radio Rch Line-output                           |                               | 1.2V                  |

| 13  | Package-shield GND |     | GND for Package-shield                          |                               |                       |

| 14  | Package-shield GND |     | GND for Package-shield                          |                               |                       |

| 15  | Package-shield GND |     | GND for Package-shield                          |                               |                       |

| 16  | Package-shield GND |     | GND for Package-shield                          |                               |                       |

| 17  | Package-shield GND |     | GND for Package-shield                          |                               |                       |

| 18  | Package-shield GND |     | GND for Package-shield                          |                               |                       |

| 19  | NC                 |     |                                                 |                               |                       |

| 20  | MPX                |     | MPX-signal output                               |                               | V <sub>CC</sub> -0.3V |

| 21  | Vstabi2            |     | 2 <sup>nd</sup> Stabilizer voltage              |                               | 3.0V                  |

| 22  | NC                 |     |                                                 |                               |                       |

| 23  | V <sub>CC</sub>    |     | Analog supply voltage                           |                               |                       |

| 24  | NC                 |     |                                                 |                               |                       |

| 25  | Vstabi.            |     | Stabilizer voltage                              |                               | 2.4V                  |

| 26  | NC                 |     |                                                 |                               |                       |

| 27  | V <sub>DD</sub>    |     | Digital supply voltage                          |                               |                       |

| 28  | NR_W               | 1   | Digital interface Read/Write                    |                               |                       |

| 29  | DATA               | I/O | Digital interface DATA                          |                               |                       |

| 30  | CLOCK              | I   | Digital interface Clock                         |                               |                       |

| 31  | CLK_IN             | I   | Reference clock-source input<br>for measurement | Connect to GND<br>if not used |                       |

| 32  | NC                 |     |                                                 |                               |                       |

| 33  | Package-shield GND |     | GND for Package-shield                          |                               |                       |

| 34  | Package-shield GND |     | GND for Package-shield                          |                               |                       |

| 35  | Package-shield GND |     | GND for Package-shield                          |                               |                       |

| 36  | Package-shield GND |     | GND for Package-shield                          |                               |                       |

| 37  | Package-shield GND |     | GND for Package-shield                          |                               |                       |

| 38  | Package-shield GND |     | GND for Package-shield                          |                               |                       |

| 39  | NC                 |     |                                                 |                               |                       |

| 40  | VI/O               | Ī   | Digital interface supply voltage                |                               |                       |

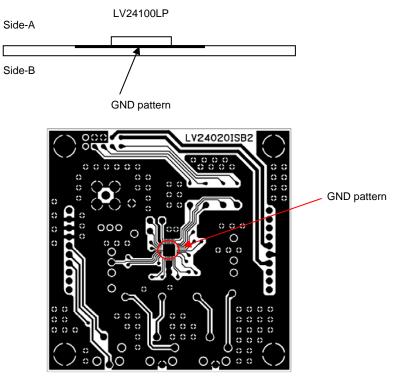

#### The PCB mounting conditions which cover FM receiving frequency range 76MHz to 108MHz

This IC Package is printed inductor backside of the package for local oscillation. It is necessary to place GND pattern right under the IC package for covering received frequency range 76MHz to 108MHz. This IC is measured under this condition for received frequency range. Then, the GND pattern must be placed at the center of the IC.

#### Printed circuit board

LV24100LP Evaluation board side-A

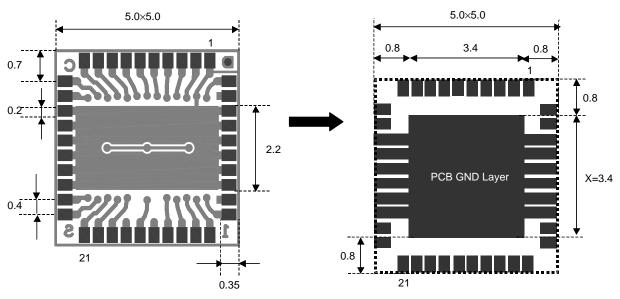

#### **PCB** layout recommendations

Substrate layout of LV24100LP

PCB pattern light under of LV24100LP

At the GND pattern light under of LV24100LP, X=3.4mm is recommended. The limit of X is min=2.2mm and max=3.6mm same as GND shield size of LV24100LP. Please do not arrange other wirings as much as possible within 0.4mm under the GND pattern.

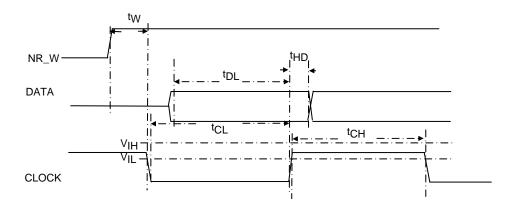

# Serial Data Timing

• Write timing

| Symbol          | Conditions                                |     | Unit |     |      |

|-----------------|-------------------------------------------|-----|------|-----|------|

|                 | Conditions                                | min | typ  | max | Unit |

| t <sub>W</sub>  | Delay from command to data                | 750 |      |     | ns   |

| <sup>t</sup> DL | Delay from data stable to data latch time | 750 |      |     | ns   |

| <sup>t</sup> HD | Data Hold time                            | 750 |      |     | ns   |

| <sup>t</sup> CH | Clock High-level time                     | 750 |      |     | ns   |

| <sup>t</sup> CL | Clock Low-level time                      | 750 |      |     | ns   |

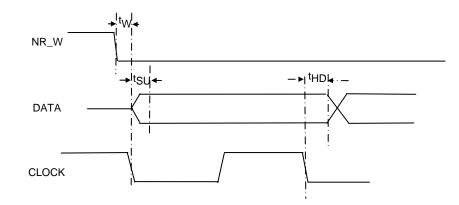

## Read timing

| Cumb al | Conditions |                                                | Linit |     |     |      |

|---------|------------|------------------------------------------------|-------|-----|-----|------|

|         | Symbol     | Conditions                                     | min   | typ | max | Unit |

| ty      | N          | Delay from command to 1 <sup>st</sup> data bit | 350   |     |     | ns   |

| tg      | SU         | Data Setup time                                |       |     | 350 | ns   |

| Т       | HD         | Data hold time                                 |       |     | 350 | ns   |

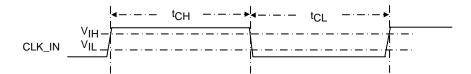

#### • External clock timing (Pin 31)

| Symbol          |                                |                    | 11.5 |                 |      |

|-----------------|--------------------------------|--------------------|------|-----------------|------|

|                 | Conditions                     | min                | typ  | max             | Unit |

| <sup>t</sup> CH | Clock High-level time          | 36                 | -    | 15625           | ns   |

| <sup>t</sup> CL | Clock Low-level time           | 36                 | -    | 15625           | ns   |

| fext            | External clock frequency       | 32                 | -    | 14000           | kHz  |

| VIH             | High level input voltage level | 0.7V <sub>DD</sub> | -    | V <sub>DD</sub> | V    |

| VIL             | Low level input voltage level  | 0                  | -    | 0.6             | V    |

#### **Digital Interface**

#### • 3-wire bus (For communication line)

Access to the LV24100 is done through the 3-wire bus.

| CLOCK | Data strobe, input to the LV24100                 |  |  |  |

|-------|---------------------------------------------------|--|--|--|

| NR_W  | ommand (Read or write data), input to the LV24100 |  |  |  |

|       | Bi-directional pin:                               |  |  |  |

| DATA  | Written data in to the LV24100 when NR_W is high, |  |  |  |

|       | Read data from the LV24100 when NR_W is low.      |  |  |  |

The LV24100 can be configured to generate interrupt through the DATA-line. When interrupt mode is selected, care should be taken that the DATA-line connection to the application micro-controller also supports interrupt.

When the required timing window for frequency measurements is not generated by the application micro-controller, an external clock must be connected to CLK\_IN pin of the LV24100.

#### Register map

The LV24100 registers are divided in 3 blocks:

| Block 01h | Status and measurement |

|-----------|------------------------|

| Block 02h | FM Control             |

| Block 03h | AM control             |

To access a register in a block, the block must be first selected by writing the block number to the BLK\_SEL register. Block selection can be skipped for subsequent accesses to other registers in the same block.

# The mapping is as follows:

| Block | Address | Register name | Access | Operation                                 |

|-------|---------|---------------|--------|-------------------------------------------|

| 01h   | 00h     | CHIP_ID       | R      | Chip identification                       |

|       | 01h     | BLK_SEL       | W      | Block Select                              |

|       | 02h     | MSRC_SEL      | W      | Measure source select                     |

|       | 03h     | FM_OSC        | W      | DAC control for FM-RF oscillator          |

|       | 04h     | SD_OSC        | W      | DAC control for stereo decoder oscillator |

|       | 05h     | IF_OSC        | W      | DAC control for IF oscillator             |

|       | 06h     | CNT_CTRL      | W      | Counter control                           |

|       | 07h     | NA            | -      |                                           |

|       | 08h     | IRQ_MSK       | W      | Interrupt mask                            |

|       | 09h     | FM_CAP        | W      | CAP bank control for RF-frequency         |

|       | 0Ah     | CNT_L         | R      | Counter value low byte                    |

|       | 0Bh     | CNT_H         | R      | Counter value high byte                   |

|       | 0Ch     | CTRL_STAT     | R      | Control status                            |

|       | 0Dh     | RADIO_STAT    | R      | Radio station status                      |

|       | 0Eh     | IRQ_ID        | R      | Interrupt identify                        |

|       | 0Fh     | IRQ_OUT       | W      | Set Interrupt on DATA-line                |

| 02h   | 01h     | BLK_SEL       | W      | Access register 01h of block 1            |

|       | 02h     | RADIO_CTRL1   | W      | Radio control 1                           |

|       | 03h     | IF_CENTER     | W      | IF Center Frequency                       |

|       | 04h     | AM_CAP        | W      | All to be set to "0"                      |

|       | 05h     | IF_BW         | W      | IF Bandwidth                              |

|       | 06h     | RADIO_CTRL2   | W      | Radio control 2                           |

|       | 07h     | RADIO_CTRL3   | W      | Radio control 3                           |

|       | 08h     | STEREO_CTRL   | W      | Stereo control                            |

|       | 09h     | AUDIO_CTRL1   | W      | Audio control 1                           |

|       | 0Ah     | AUDIO_CTRL2   | W      | Audio control 2                           |

|       | 0Bh     | PW_SCTRL      | W      | Power and soft control                    |

| 03h   | 01h     | BLK_SEL       | W      | Access register 01h of block 1            |

|       | 02h     | AM_ACAP       | W      | AM antenna capacitor                      |

|       | 03h     | AM_FE         | W      | AM front end control                      |

|       | 04h     | AM_CTRL       | W      | AM control                                |

Not mentioned registers are not defined and should not be accessed.

# **Register Description**

| Block x, Regi   | ster 01h-BLK_SEI         | L-Block Select     | Register(Write      | e only)             |    |   |  |

|-----------------|--------------------------|--------------------|---------------------|---------------------|----|---|--|

| 7               | 6                        | 5                  | 4                   | 3                   | 2  | 1 |  |

|                 |                          |                    | BN                  | [7:0]               |    |   |  |

| Bit 7-0:        | BN[7:0]: 8-bit blo       | ock number. For L' | V24100, the followi | ng numbers are vali | d: |   |  |

|                 | 01h.                     |                    |                     |                     |    |   |  |

|                 | 02h.                     |                    |                     |                     |    |   |  |

|                 | 03h.                     |                    |                     |                     |    |   |  |

| Note: This regi | ster can be accessed fro | om any block       |                     |                     |    |   |  |

#### Block 1, Register 00h-CHIP\_ID-Chip Identify Register(Read only)

| 7        | 6                                       | 5                    | 4      | 3 | 2 | 1 | 0 |  |  |

|----------|-----------------------------------------|----------------------|--------|---|---|---|---|--|--|

|          | ID[7:0]                                 |                      |        |   |   |   |   |  |  |

| Bit 7-0: | it 7-0: <b>ID[7:0]</b> : 8-bit chip ID. |                      |        |   |   |   |   |  |  |

|          | For LV2410                              | 0, value 7 should be | e read |   |   |   |   |  |  |

#### Block 1, Register 02h-MSRC\_SEL-Measurement Source Select Register(Write-only)

| 7              | 6                                         | 5                     | 4                    | 3                  | 2      | 1      | 0      |  |  |  |

|----------------|-------------------------------------------|-----------------------|----------------------|--------------------|--------|--------|--------|--|--|--|

| MSR_O          | AFC_LVL                                   | AFC_SPD               | MSS_RF16             | MSS_AM             | MSS_SD | MSS_FM | MSS_IF |  |  |  |

| Bit 7:         | MSR_O: Outpu                              | t measure source to   | DATA-pin             |                    |        |        | •      |  |  |  |

|                | 0 = Measuri                               | ng source not availa  | ble at DATA-pin (no  | ormal operation).  |        |        |        |  |  |  |

|                | 1 = Measurii                              | ng source available   | at DATA-pin (test n  | node).             |        |        |        |  |  |  |

| Bit 6:         | AFC_LVL: AFC                              | C trigger level       |                      |                    |        |        |        |  |  |  |

|                | 0 = AFC is a                              | lways active (trigge  | r at 0dBμV)          |                    |        |        |        |  |  |  |

|                | 1 = AFC is c                              | only active when fiel | d strength is above  | 20dBµV             |        |        |        |  |  |  |

| Bit 5:         | AFC_SPD: AFC                              | C speed               |                      |                    |        |        |        |  |  |  |

|                | 0 = AFC adj                               | usts with 3Hz speed   | 1                    |                    |        |        |        |  |  |  |

|                | 1 = AFC adj                               | usts with 8kHz spee   | ed (test mode)       |                    |        |        |        |  |  |  |

| Bit 4:         | <b>MSS_RF16</b> : RF                      | /16 measurement.      |                      |                    |        |        |        |  |  |  |

|                | 0 = Disable                               | RF/16 oscillator me   | asurement            |                    |        |        |        |  |  |  |

|                | 1 = Enable F                              | RF/16 oscillator mea  | asurement            |                    |        |        |        |  |  |  |

| Bit 3:         | MSS_AM: AM antenna frequency measurement. |                       |                      |                    |        |        |        |  |  |  |

|                | 0 = Disable                               | AM antenna measu      | rement               |                    |        |        |        |  |  |  |

|                | 1 = Enable A                              | AM antenna measur     | ement                |                    |        |        |        |  |  |  |

| Bit 2:         | MSS_SD: Stere                             | eo decoder oscillato  | r measurement        |                    |        |        |        |  |  |  |

|                | 0 = Disable :                             | stereo decoder osci   | llator measurement   |                    |        |        |        |  |  |  |

|                | 1 = Enable s                              | tereo decoder oscil   | lator measurement    |                    |        |        |        |  |  |  |

| Bit 1:         | MSS_FM: FM F                              | RF oscillator measu   | rement               |                    |        |        |        |  |  |  |

|                | 0 Disable FN                              | ARF oscillator mea    | surement             |                    |        |        |        |  |  |  |

|                | 1 = Enable F                              | FM RF oscillator me   | asurement            |                    |        |        |        |  |  |  |

| Bit 0:         | MSS_IF: IF osc                            | illator measuremen    | t                    |                    |        |        |        |  |  |  |

|                | 0 = Disable                               | IF oscillator measur  | ement                |                    |        |        |        |  |  |  |

|                | 1 = Enable I                              | F oscillator measure  | ement                |                    |        |        |        |  |  |  |

| Note: Only one | of the measurement                        | source MSS_xx bits    | may be set at a tim  | ne.                |        |        |        |  |  |  |

| The FM R       | F frequency is divide                     | d by 256 or 16 befo   | re it goes to the me | asuring circuitry. |        |        |        |  |  |  |

#### Block 1, Register 03h-FM\_OSC-FM RF Oscillator Register(Write-only)

| 7                 | 6                                                                                   | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------------------|-------------------------------------------------------------------------------------|---|---|---|---|---|---|--|--|

|                   | FMOSC[7:0]                                                                          |   |   |   |   |   |   |  |  |

| Bit 7-0:          | Bit 7-0: <b>FMOSC[7:0]</b> : DAC value to control the FM RF oscillator (fine step)  |   |   |   |   |   |   |  |  |

| Note: Positive DA | Note: Positive DAC control (i.e. the frequency increases with the register's value) |   |   |   |   |   |   |  |  |

| See also FI       | See also FM_CAP register                                                            |   |   |   |   |   |   |  |  |

#### Block 1, Register 04h-SD\_OSC-Stereo Decoder Oscillator Register(Write-only)

| 7                 | 6                                                                                  | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------------------|------------------------------------------------------------------------------------|---|---|---|---|---|---|--|--|--|

|                   | SDOSC[7:0]                                                                         |   |   |   |   |   |   |  |  |  |

| Bit 7-0:          | Bit 7-0: <b>SDOSC[7:0]</b> : DAC value to control the stereo decoder oscillator    |   |   |   |   |   |   |  |  |  |

| Note: Positive DA | Note: Positive DAC control(i.e. the frequency increases with the register's value) |   |   |   |   |   |   |  |  |  |

0

| Block 1, Regist   | Block 1, Register 05h-IF_OSC-IF Oscillator Register(Write-only) |                    |                       |        |  |  |  |  |  |  |  |

|-------------------|-----------------------------------------------------------------|--------------------|-----------------------|--------|--|--|--|--|--|--|--|

| 7                 | 7 6 5 4 3 2 1 0                                                 |                    |                       |        |  |  |  |  |  |  |  |

|                   | IFOSC[7:0]                                                      |                    |                       |        |  |  |  |  |  |  |  |

| Bit 7-0:          | Bit 7-0: IFOSC[7:0]: DAC value to control the IF oscillator     |                    |                       |        |  |  |  |  |  |  |  |

| Note: Positive DA | AC control (i.e. the fi                                         | requency increases | with the register's v | /alue) |  |  |  |  |  |  |  |

#### Block 1, Register 06h-CNT\_CTRL-Counters Control Register(Write-only)

| 7        | 6              | 5                    | 4                     | 3                   | 2      | 1       | 0       |

|----------|----------------|----------------------|-----------------------|---------------------|--------|---------|---------|

| CNT1_CLR | CTAB2          | CTAB1                | CTAB0                 | SWP_CNT_L           | CNT_EN | CNT_SEL | CNT_SET |

| Bit 7:   | CNT1_CLR: CI   | ear counter 1 bit    |                       |                     |        |         |         |

|          | 0 = Normal r   | mode                 |                       |                     |        |         |         |

|          | 1 = Clear an   | id keep counter 1 ii | n reset mode          |                     |        |         |         |

| Bit 6-4: | CTAB[2:0]: Tal | b select for counter | 2 measuring interv    | al bits             |        |         |         |

|          | Valu           | <u>le Dec</u> .      | Stop value            |                     |        |         |         |

|          | 000            | b 0                  | Stop after 2 counts   | ;                   |        |         |         |

|          | 001            | b 1                  | Stop after 8 counts   | ;                   |        |         |         |

|          | 010            | b 2                  | Stop after 32 count   | ts                  |        |         |         |

|          | 011            | b 3                  | Stop after 128 cou    | nts                 |        |         |         |

|          | 100            | b 4                  | Stop after 512 cou    | nts                 |        |         |         |

|          | 101            | b 5                  | Stop after 2048 co    | unts                |        |         |         |

|          | 110            | b 6                  | Stop after 8192 co    | unts                |        |         |         |

|          | 111            | b 7                  | Stop after 32768 c    | ounts               |        |         |         |

| Bit 3:   | SWP_CNT_L:     | Swap counter 1 an    | d counter 2 bit(Activ | /e low)             |        |         |         |

|          | 0 = Clock so   | ource 1 to counter 2 | , clock source 2 to   | counter 1(swapping) |        |         |         |

|          | 1 = Clock so   | ource 1 to counter 1 | , clock source 2 to   | counter 2(no swap)  |        |         |         |

| Bit 2:   | CNT_EN: Enab   | le the currently sel | ected counter bit     |                     |        |         |         |

|          | 0 = Disable    | counter(stop count   | ing)                  |                     |        |         |         |

|          | 1 = Enable o   | counter(counting m   | ode)                  |                     |        |         |         |

| Bit 1:   | CNT_SEL: cou   | nter select bit      |                       |                     |        |         |         |

|          | 0 = Select co  | ounter 1 for measu   | rement                |                     |        |         |         |

|          | 1 = Select co  | ounter 2 for measu   | rement                |                     |        |         |         |

| Bit 0:   | CNT_SET: Set   | counters bit         |                       |                     |        |         |         |

|          | 0 = Normal r   | mode                 |                       |                     |        |         |         |

|          | 1 = Set both   | counter 1 and cou    | nter 2 to FFFFh and   | d keep them set     |        |         |         |

#### Block 1, Register 08h-IRQ\_MSK-Interrupt Mask Register(Write-only)

| 7        | 6                                        | 5                                    | 4                    | 3                     | 2      | 1     | 0       |  |  |  |  |

|----------|------------------------------------------|--------------------------------------|----------------------|-----------------------|--------|-------|---------|--|--|--|--|

| Reserved | IM_MS                                    | Rese                                 | erved                | IRQ_LVL               | IM_AFC | IM_FS | IM_CNT2 |  |  |  |  |

| Bit 7:   | Reserved: Mus                            | Reserved: Must be programmed with 0. |                      |                       |        |       |         |  |  |  |  |

| Bit 6:   | IM_MS: Mono/Stereo interrupt mask bit    |                                      |                      |                       |        |       |         |  |  |  |  |

|          | 0 = Disable mono/stereo change interrupt |                                      |                      |                       |        |       |         |  |  |  |  |

|          | 1 = Enable r                             | nono/stereo change                   | e interrupt          |                       |        |       |         |  |  |  |  |

| Bit 5:   | Reserved: Mus                            | st be programmed v                   | vith 0.              |                       |        |       |         |  |  |  |  |

| Bit 4:   | Reserved: Mus                            | st be programmed v                   | vith 0.              |                       |        |       |         |  |  |  |  |

| Bit 3:   | IRQ_LVL: Inter                           | rrupt level select bit               |                      |                       |        |       |         |  |  |  |  |

|          | 0 = Drive DA                             | ATA-line from low to                 | high when interrup   | ot occurs(active high | )      |       |         |  |  |  |  |

|          | 1 = Drive DA                             | ATA-line from high t                 | o low when interrup  | ot occurs(active low) |        |       |         |  |  |  |  |

| Bit 2:   | IM_AFC: AFC                              | out of range interru                 | pt mask bit          |                       |        |       |         |  |  |  |  |

|          | 0 = Disable                              | AFC out of range in                  | iterrupt             |                       |        |       |         |  |  |  |  |

|          | 1 = Enable /                             | AFC out of range in                  | terrupt              |                       |        |       |         |  |  |  |  |

| Bit 1:   | IM_FS: Field st                          | rength change inter                  | rrupt mask bit       |                       |        |       |         |  |  |  |  |

|          | 0 = Disable                              | field strength chang                 | je interrupt         |                       |        |       |         |  |  |  |  |

|          | 1 = Enable f                             | ield strength chang                  | e interrupt          |                       |        |       |         |  |  |  |  |

| Bit 0:   | IM_CNT2: Cou                             | nter 2 counting don                  | e interrupt mask bit |                       |        |       |         |  |  |  |  |

|          | 0 = Disable                              | counter 2 counting                   | done interrupt       |                       |        |       |         |  |  |  |  |

|          | 1 = Enable o                             | counter 2 counting of                | done interrupt       |                       |        |       |         |  |  |  |  |

| Block 1, Regi   | ster 09h-FM_CA          | P-FM RF Cap        | acitor Bank Re        | gister(Write-on     | uly) |   |   |

|-----------------|-------------------------|--------------------|-----------------------|---------------------|------|---|---|

| 7               | 6                       | 5                  | 4                     | 3                   | 2    | 1 | 0 |

|                 |                         |                    | FMCA                  | P[7:0]              |      |   |   |

| Bit 7-0:        | FMCAP[7:0]: C/          | AP bank value to o | control the FM RF fr  | equency (coarse ste | eps) |   |   |

| Note: 7½ bit CA | AP value (Bit[7:6]: Com | bination 10b and   | 01b results in the sa | me CAP-range)       |      |   |   |

| Negative        | control: de RF frequen  | cy decreases whe   | n increasing the reg  | ister's value       |      |   |   |

| See also        | FM_OSC register         |                    |                       |                     |      |   |   |

#### Block 1, Register 0Ah-CNT\_L-Counter Value Low Register(Read-only)

|   | 7            | 6            | 5                   | 4                     | 3 | 2 | 1 | 0 |  |  |

|---|--------------|--------------|---------------------|-----------------------|---|---|---|---|--|--|

|   | CNT_LSB[7:0] |              |                     |                       |   |   |   |   |  |  |

| В | it 7-0:      | CNT_LSB[7:0] | : Lower 8-bit value | of the 16 bit counter | r |   |   |   |  |  |

#### Block 1, Register 0Bh-CNT\_H-Counter Value High Register(Read-only)

| 7        | 6            | 5                    | 4                    | 3  | 2 | 1 | 0 |  |  |  |  |

|----------|--------------|----------------------|----------------------|----|---|---|---|--|--|--|--|

|          | CNT_MSB[7:0] |                      |                      |    |   |   |   |  |  |  |  |

| Bit 7-0: | CNT_MSB[7:0  | ]: Upper 8-bit value | of the 16 bit counte | Pr |   |   |   |  |  |  |  |

#### Block 1, Register 0Ch-CTRL\_STAT-Control Status Register(Read-only)

| 7                | 6                                       | 5                    | 4                     | 3               | 2     | 1       | 0       |  |  |

|------------------|-----------------------------------------|----------------------|-----------------------|-----------------|-------|---------|---------|--|--|

| REV3             | REV2                                    | REV1                 | REV0                  | Rese            | erved | COV_FLG | AFC_FLG |  |  |

| Bit 7-4:         | REV[3:0]: should be read as 0Dh         |                      |                       |                 |       |         |         |  |  |

| Bit 3-2:         | Reserved[1:0]                           | : should be read as  | all 1                 |                 |       |         |         |  |  |

| Bit 1:           | COV_FLG: cou                            | inter overflow flag  |                       |                 |       |         |         |  |  |

|                  | 0 = No overflow of the internal counter |                      |                       |                 |       |         |         |  |  |

|                  | 1 = The last                            | counting loop caus   | es overflow of the ir | nternal counter |       |         |         |  |  |

| Bit 0:           | AFC_FLG: AF                             | C out of range bit   |                       |                 |       |         |         |  |  |

|                  | 0 = AFC is v                            | vithin control range |                       |                 |       |         |         |  |  |

|                  | 1 = AFC is o                            | out of control range |                       |                 |       |         |         |  |  |

| Note: Reading th | is register will clear                  | AFC, count 2 done    | interrupt.            |                 |       |         |         |  |  |

| COV_FLG          | is clear when CLR_                      | CNT1 bit of CNT_C    | TRL register is high  | ı               |       |         |         |  |  |

#### Block 1, Register 0Dh-RADIO\_STAT-Radio Station Status Register(Read-only)

| 7                | 6                                           | 5                    | 4                    | 3  | 2 | 1 | 0 |  |  |  |  |  |  |

|------------------|---------------------------------------------|----------------------|----------------------|----|---|---|---|--|--|--|--|--|--|

| RSS_MS           |                                             | RSS_FS               |                      |    |   |   |   |  |  |  |  |  |  |

| Bit 7:           | RSS_MS: Radio station mono/stereo state bit |                      |                      |    |   |   |   |  |  |  |  |  |  |

|                  | 0 = Mono                                    |                      |                      |    |   |   |   |  |  |  |  |  |  |

|                  | 1 = Stereo                                  |                      |                      |    |   |   |   |  |  |  |  |  |  |

| Bit 6-0:         | RSS_FS[6:0]: R                              | adio station field s | strength bits        |    |   |   |   |  |  |  |  |  |  |

|                  | 1111111b = F                                | ield strength less   | then 10dBμV          |    |   |   |   |  |  |  |  |  |  |

|                  | 0111111b = F                                | ield strength betw   | veen 10 to 20dBµV    |    |   |   |   |  |  |  |  |  |  |

|                  | 0011111b = F                                | ield strength betw   | veen 20 to 30dBµV    |    |   |   |   |  |  |  |  |  |  |

|                  | 0001111b = F                                | ield strength betw   | veen 30 to 40dBµV    |    |   |   |   |  |  |  |  |  |  |

|                  | 0000111b = F                                | ield strength betw   | veen 40 to 50dBµV    |    |   |   |   |  |  |  |  |  |  |

|                  | 0000011b = F                                | ield strength betw   | veen 50 to 60dBµV    |    |   |   |   |  |  |  |  |  |  |

|                  | 0000001b = F                                | ield strength betw   | veen 60 to 70dBµV    |    |   |   |   |  |  |  |  |  |  |

|                  | 0000000b = F                                | ield strength abov   | ve 70dBμV            |    |   |   |   |  |  |  |  |  |  |

| Note: Reading th | nis register will clear fi                  | eld strength and n   | nono/stereo interrup | ot |   |   |   |  |  |  |  |  |  |

#### Block 1, Register 0Eh-IRQ\_ID-Interrupt Identify Register(Read-only)

| 7      | 6                                    | 5                      | 4                     | 3                   | 2     | 1     | 0        |  |  |  |

|--------|--------------------------------------|------------------------|-----------------------|---------------------|-------|-------|----------|--|--|--|

| Rese   | erved                                | II_CNT2                | Reserved              | II_AFC              | Rese  | erved | II_FS_MS |  |  |  |

| Bit 7: | Reserved: sho                        | uld be read as 1       |                       |                     |       |       |          |  |  |  |

| Bit 6: | Reserved: sho                        | uld be read as 1       |                       |                     |       |       |          |  |  |  |

| Bit 5: | II_CNT2: Coun                        | ter 2 counting done    | flag                  |                     |       |       |          |  |  |  |

|        | 0 = No cour                          | ting 2 counting don    | e interrupt           |                     |       |       |          |  |  |  |

|        | 1 = Measuring with counter 2 is done |                        |                       |                     |       |       |          |  |  |  |

| Bit 4: | Reserved: sho                        | uld be read as 0       |                       |                     |       |       |          |  |  |  |

| Bit 3: | II_AFC: AFC o                        | ut of range interrup   | t bit                 |                     |       |       |          |  |  |  |

|        | 0 = No AFC                           | interrupt              |                       |                     |       |       |          |  |  |  |

|        | 1 = AFC fail                         | s to hold the RF-fre   | quency in range       |                     |       |       |          |  |  |  |

| Bit 2: | Reserved: sho                        | uld be read as 0       |                       |                     |       |       |          |  |  |  |

| Bit 1: | Reserved: sho                        | uld be read as 0       |                       |                     |       |       |          |  |  |  |

| Bit 0: | II_FS_MS: Fiel                       | d strength and Mon     | o/stereo interrupt bi | it                  |       |       |          |  |  |  |

|        | 0 = No char                          | ge in either the field | d strength or the mo  | no/stereo mode      |       |       |          |  |  |  |

|        | 1 = Change                           | in field strength bits | s detected or mono/   | stereo mode has cha | anged |       |          |  |  |  |

#### Block 1, Register OFh-IRQ\_OUT-Set Interrupt Out Register(Write Only)

|   | 7 6 5 4 3 2 1 0                                                                   |                                                                                              |  |  |  |  |  |  |  |  |  |

|---|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

|   | IRQO_VAL[7:0]                                                                     |                                                                                              |  |  |  |  |  |  |  |  |  |

| ĺ | Bit 7-0:                                                                          | Bit 7-0: IRQO_VAL[7:0]: Write any value to this register will select the interrupt as output |  |  |  |  |  |  |  |  |  |

|   | on the DATA-line of the LV24100 (the DATA-line can then be used as interrupt pin) |                                                                                              |  |  |  |  |  |  |  |  |  |

#### Block 2, Register 02h-RADIO\_CTRL1-Radio Control 1 Register(Write-only)

| 7              | 6                    | 5                      | 4                   | 3                | 2                  | 1                   | 0           |

|----------------|----------------------|------------------------|---------------------|------------------|--------------------|---------------------|-------------|

| EN_MEAS        | EN_AFC               | Reserved               | AM_CD2              | DIR_AFC          | RST_AFC            | AM_CD1              | AM_CD0      |

| Bit 7:         | EN_MEAS: En          | able measurement       | bit                 |                  |                    |                     |             |

|                | 0 = Normal           | mode                   |                     |                  |                    |                     |             |

|                | 1 = Measure          | ement mode             |                     |                  |                    |                     |             |

| Bit 6:         | EN_AFC: Enab         | ble AFC bit            |                     |                  |                    |                     |             |

|                | 0 = Disable          | AFC                    |                     |                  |                    |                     |             |

|                | 1 = Enable           | AFC                    |                     |                  |                    |                     |             |

| Bit 5:         | EN_RF16:Enal         | ble RF16 Divider bit   | t                   |                  |                    |                     |             |

|                | 0 = Disable          | RF16                   |                     |                  |                    |                     |             |

|                | 1 = Enable I         | RF16                   |                     |                  |                    |                     |             |

| Bit 4:         | AM_CD2: AM           | clock divider bit 2. S | Should be kept at 1 | in FM mode       |                    |                     |             |

| Bit 3:         | DIR_AFC: AFC         | C direction bit        |                     |                  |                    |                     |             |

|                | 0 = AFC nor          | rmal direction         |                     |                  |                    |                     |             |

|                | 1 = AFC rev          | erse direction (for t  | est purpose)        |                  |                    |                     |             |

| Bit 2:         | RST_AFC: Re:         |                        |                     |                  |                    |                     |             |

|                | 0 = Normal           | operation              |                     |                  |                    |                     |             |

|                |                      | FC to the middle of    | •                   |                  |                    |                     |             |

| Bit 1:         | AM_CD1: AM           | clock divider bit 1. S | Should be kept at 1 | in FM mode       |                    |                     |             |

| Bit 0:         |                      | clock divider bit 0. S |                     |                  |                    |                     |             |

| Note: The AM_C | D[2:0] bits are used | to scale the FM-RF     | F frequency down to | AM-RF frequency. | In FM mode, the AM | I divider should be | turned off. |

|                | AM                   | _CD[2:0]               | Divider factor      | Approx. AN       | I-RF (in kHz)      |                     |             |

|                |                      | 0                      | 48                  | 1354             | 2291               |                     |             |

|                |                      | 1                      | 64                  | 1015             | 1718               |                     |             |

|                |                      | 2                      | 80                  | 812              | 1375               |                     |             |

|                |                      | 3                      | 96                  | 677              | 1145               |                     |             |

|                |                      | 4                      | 128                 | 507              | 859                |                     |             |

|                |                      | 5                      | 160                 | 406              | 687                |                     |             |

|                |                      | 6                      | 192                 | 338              | 572                |                     |             |

|                |                      | 0                      |                     |                  |                    |                     |             |

#### Block 2, Register 03h-IFCEN\_OSC-IF Center Frequency Oscillator Register(Write-only)

| 7        | 7 6 5 4 3 2 1 0                                            |  |  |  |  |  |  |  |  |  |  |

|----------|------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

|          | IFCOSC[7:0]                                                |  |  |  |  |  |  |  |  |  |  |

| Bit 7-0: | Bit 7-0: IFCENT[7:0]: value for centering the IF frequency |  |  |  |  |  |  |  |  |  |  |

| 7           | 6                 | 5                  | 4                | 3      | 2 | 1 | 0 |

|-------------|-------------------|--------------------|------------------|--------|---|---|---|

|             |                   |                    | AM_CA            | P[7:0] |   |   |   |

| Bit 7-0:    | AM_CAP[7:0]:all   | bit to be set to 0 |                  |        |   |   |   |

|             |                   |                    |                  |        |   |   |   |

|             |                   |                    |                  |        |   |   |   |

| Rock 2, Reg | ister 05h-IF_BW-L | F Bandwidth F      | Register(Write-a | only)  |   |   |   |

# 7 6 5 4 3 2 1 IFBW[7:0] Bit 7-0: IFBW[7:0]: Value for IF bandwidth

#### Block 2, Register 06h-RADIO\_CTRL2-Radio Control 2 Register(Write-only)

| 7      | 6                        | 5                                | 4                 | 3        | 2        | 1     | 0        |

|--------|--------------------------|----------------------------------|-------------------|----------|----------|-------|----------|

| VREF2  | VREF                     | STABI_BP                         | IF_PM_L           | DCFB_SPD | DCFB_OFF | AGCSP | Reserved |

| Bit 7: | VREF2: V <sub>REF2</sub> | 2 control bit                    |                   |          |          |       |          |

|        | 0 = VREF2 i              | is ON                            |                   |          |          |       |          |

|        | 1 = VREF <sub>2</sub> i  | is OFF                           |                   |          |          |       |          |

| Bit 6: | VREF: V <sub>REF</sub> c | ontrol bit                       |                   |          |          |       |          |

|        | 0 = VREF is              | ON                               |                   |          |          |       |          |

|        | 1 = VREF is              | OFF                              |                   |          |          |       |          |

| Bit 5: | STABI_BP: Vo             | ltage stabilizer bypa            | ass bit           |          |          |       |          |

|        | 0 = Internal             | voltage is V <sub>stabi</sub> (n | ormal operation)  |          |          |       |          |

|        | 1 = Internal             | voltage is V <sub>CC</sub> (sta  | bilizer bypassed) |          |          |       |          |

| Bit 4: | IF_PM_L: IF PI           | LL mute bit                      |                   |          |          |       |          |

|        | 0 = IF PLL n             | nute on (presetting              | IF mode)          |          |          |       |          |

|        | 1 = IF PLL n             | nute off (normal ope             | eration mode)     |          |          |       |          |

| Bit 3: | DCFB_SPD: D              | C feedback speed                 |                   |          |          |       |          |

|        | 0 = normal s             | speed                            |                   |          |          |       |          |

|        | 1 = high spe             | ed (test mode)                   |                   |          |          |       |          |

| Bit 2: | DCFB_OFF: D              | C feedback control               |                   |          |          |       |          |

|        | 0 = Enable [             | DC feedback (FM m                | iode)             |          |          |       |          |

|        | 1 = Turn off             | the DC feedback (A               | M mode)           |          |          |       |          |

| Bit 1: | AGCSP: AGC :             | speed control bit                |                   |          |          |       |          |

|        | 0 = Normal               | speed                            |                   |          |          |       |          |

|        | 1 = High spe             | eed (test mode)                  |                   |          |          |       |          |

| Bit 0: | Reserved: sho            | uld be written with (            | )                 |          |          |       |          |

#### Block 2, Register 07h-RADIO\_CTRL3-Radio Control 3 Register(Write-only)

| 7                | 6                             | 5                     | 4       | 3     | 2     | 1        | 0 |  |  |

|------------------|-------------------------------|-----------------------|---------|-------|-------|----------|---|--|--|

| AGC_SLVL         | VOLSH                         | Reserved              | AMUTE_L | SE_FM | SE_AM | Reserved |   |  |  |

| Bit 7:           | AGC_SLVL: A                   | GC set level bit      |         |       |       |          |   |  |  |

|                  | This bit mus                  | t be set to 1         |         |       |       |          |   |  |  |

| Bit 6:           | VOLSH: Volume level shift bit |                       |         |       |       |          |   |  |  |

|                  | 0 = Normal                    | volume level          |         |       |       |          |   |  |  |

|                  | 1 = Extra vo                  | lume of 12dB          |         |       |       |          |   |  |  |

| Bit 5:           | Reserved: sho                 | uld be written with 0 | )       |       |       |          |   |  |  |

| Bit 4:           | AMUTE_L: Aud                  | dio mute bit          |         |       |       |          |   |  |  |

|                  | 0 = Audio m                   | uted                  |         |       |       |          |   |  |  |

|                  | 1 = Audio no                  | ot muted              |         |       |       |          |   |  |  |

| Bit 3:           | SE_FM: FM rad                 | dio select bit        |         |       |       |          |   |  |  |

|                  | 0 = Disable                   | FM radio              |         |       |       |          |   |  |  |

|                  | 1 = Enable F                  | M radio               |         |       |       |          |   |  |  |

| Bit 2:           | SE_AM: AM ra                  | dio select bit        |         |       |       |          |   |  |  |

|                  | 0 = Disable                   | AM radio              |         |       |       |          |   |  |  |

|                  | 1 = Enable A                  | AM radio              |         |       |       |          |   |  |  |

| Bit 1:           | Reserved: sho                 | uld be written with 0 | )       |       |       |          |   |  |  |

| Bit 0:           | Reserved: sho                 | uld be written with 0 | )       |       |       |          |   |  |  |

| Note: Do not set | bit 3 and 2 on at the         | same time.            |         |       |       |          |   |  |  |

| 7        | 6                       | 5                      | 4                    | 3       | 2         | 1     | 0    |  |  |  |

|----------|-------------------------|------------------------|----------------------|---------|-----------|-------|------|--|--|--|

| FRCST    |                         | FMCS[2:0]              |                      | DLT_TNE | PILOTCANC | SD_PM | ST_M |  |  |  |

| Bit 7:   | FRCST: Force            | stereo bit             |                      |         |           |       |      |  |  |  |

|          | 0 = Normal              | mode                   |                      |         |           |       |      |  |  |  |

|          | 1 = Force st            | ereo mode for test     |                      |         |           |       |      |  |  |  |

| Bit 6-4: | FMCS[2:0]: FN           | I channel separatio    | n bits               |         |           |       |      |  |  |  |

|          | 0…7=FM cł               | nannel separation le   | vel                  |         |           |       |      |  |  |  |

| Bit 3:   | DLT_TNE: Del            | ta tune bit            |                      |         |           |       |      |  |  |  |

|          | 0 = Decrease delta tune |                        |                      |         |           |       |      |  |  |  |

|          | 1 = Normal              | delta tune             |                      |         |           |       |      |  |  |  |

| Bit 2:   | PILOTCANC:              | Pilot cancellation bit |                      |         |           |       |      |  |  |  |

|          | 0 = No pilot            | cancellation           |                      |         |           |       |      |  |  |  |

|          | 1 = Pilot car           | ncellation enabled     |                      |         |           |       |      |  |  |  |

| Bit 1:   | SD_PM: Stere            | o decoder PLL mute     | e bit                |         |           |       |      |  |  |  |

|          | 0 = Stereo d            | decoder PLL not mu     | ted(normal operation | on)     |           |       |      |  |  |  |

|          | 1 = Stereo d            | decoder PLL is mute    | ed(presetting mode)  | )       |           |       |      |  |  |  |

| Bit 0:   | ST_M: FM ster           | eo/mono mode bit       |                      |         |           |       |      |  |  |  |

|          | 0 = Stereo r            | node                   |                      |         |           |       |      |  |  |  |

|          | 1 = Mono m              | ode                    |                      |         |           |       |      |  |  |  |

#### Block 2, Register 09h-AUDIO\_CTRL1-Audio Control 1 Register(Write-only)

| 7        | 6 5 4 3 2 1                                 |                      |     |  |  |  |  |  |  |  |

|----------|---------------------------------------------|----------------------|-----|--|--|--|--|--|--|--|

| Reserved |                                             |                      |     |  |  |  |  |  |  |  |

| Bit 7-1: | Bit 7-1: Reserved: should be written with 0 |                      |     |  |  |  |  |  |  |  |

| Bit 0:   | nAUBST: Audi                                | o output level boost | bit |  |  |  |  |  |  |  |

|          | 0 = Boost output level with 3dB             |                      |     |  |  |  |  |  |  |  |

|          | 1 = No output level boosting                |                      |     |  |  |  |  |  |  |  |

#### Block 2, Register 0Ah-AUDIO\_CTRL2-Audio Control 2 Register(Write-only)

| 7        | 6                                  | 5                     | 4 | 3 | 2        | 1 | 0 |

|----------|------------------------------------|-----------------------|---|---|----------|---|---|

| Rese     | erved                              | DEEMP                 |   |   | Reserved |   |   |

| Bit 7-6: | Reserved: sho                      | uld be written with 1 |   |   |          |   |   |

| Bit 5:   | DEEMP: De-er                       | nphasis bit           |   |   |          |   |   |

|          | 0 = De-emp                         | hasis 50µs.           |   |   |          |   |   |

|          | 1 = De-emphasis 75μs.              |                       |   |   |          |   |   |

| Bit 4-0: | Reserved: should be written with 0 |                       |   |   |          |   |   |

#### Block 2, Register 0Bh-PW\_SCTRL-Power and Soft Control Register(Write-only)

| 7              | 6                                       | 5                     | 4          | 3       | 2 | 1        | 0      |  |  |  |

|----------------|-----------------------------------------|-----------------------|------------|---------|---|----------|--------|--|--|--|

|                | SS_CTRL                                 |                       |            | SM_CTRL |   | Reserved | PW_RAD |  |  |  |

| Bit 7-5:       | SS_CTRL: Soft                           | t stereo control bits | (8 levels) |         |   |          |        |  |  |  |

|                | 000b = Minir                            | mal soft stereo(off)  |            |         |   |          |        |  |  |  |

|                | 111b = Maxi                             | imal soft stereo leve | el         |         |   |          |        |  |  |  |

| Bit 4-2:       | SM_CTRL: Soft audio mute bits(8 levels) |                       |            |         |   |          |        |  |  |  |

|                | 000b = Minir                            | mal soft audio mute   | (off)      |         |   |          |        |  |  |  |

|                | 111b = Maxi                             | imal soft audio mute  | e level    |         |   |          |        |  |  |  |

| Bit 1:         | Reserved: sho                           | uld be written with ( | )          |         |   |          |        |  |  |  |

| Bit 0:         | PW_RAD: Rad                             | io circuitry power bi | t          |         |   |          |        |  |  |  |

|                | 0 = Radio ci                            | rcuitry is switched C | DFF.       |         |   |          |        |  |  |  |

|                | 1 = Switch ra                           | adio circuitry ON     |            |         |   |          |        |  |  |  |

| Note: PW_RAD i | s 0 at power up                         |                       |            |         |   |          |        |  |  |  |

#### Block 3, Register 02h-AM\_ACAP-AM Antenna Capacitor Bank Register(Write-only)

| 7 6 5 4 3 2 1 0 |                                                                                |                       |                      |                     |             |  |  |  |  |  |

|-----------------|--------------------------------------------------------------------------------|-----------------------|----------------------|---------------------|-------------|--|--|--|--|--|

| AMCAP[7:0]      |                                                                                |                       |                      |                     |             |  |  |  |  |  |

| Bit 7-0:        | Bit 7-0: AMCAP[7:0]: CAP bank value to control the AM antenna frequency        |                       |                      |                     |             |  |  |  |  |  |

| Note: AM antenn | a capacitor bank is o                                                          | controlled by 10 bits | . The upper 2 bits a | are located in AM_F | E register. |  |  |  |  |  |

| Negative co     | Negative control: de frequency decreases when increasing the register's value. |                       |                      |                     |             |  |  |  |  |  |

| Block 3, Regi | ster 03h-AM_FE- | -AM Front End                                       | Register(Wri | te-only) |   |        |        |  |  |  |

|---------------|-----------------|-----------------------------------------------------|--------------|----------|---|--------|--------|--|--|--|

| 7             | 6               | 5                                                   | 4            | 3        | 2 | 1      | 0      |  |  |  |

| AGC_LVL       |                 |                                                     | AGC_GAIN     |          |   | AMCAP9 | AMCAP8 |  |  |  |

| Bit 7-5:      | AGC_LVL[2:0]:   | AGC_LVL[2:0]: AGC level bits                        |              |          |   |        |        |  |  |  |

| Bit 4:        | AAGC_EG: AM     | AAGC_EG: AM AGC extra gain                          |              |          |   |        |        |  |  |  |