# **STB5701**

# 350 to 400 MHz FSK/ASK receiver (ST-RECORD01 family)

Preliminary Data

### **Features**

- Multiband receiver: 350MHz to 400MHz

- FSK/ASK modulation selection

- Programmable multichannel

- High dynamic range with On-Chip AGC

- PLL and fully VCO integrated

- Image Rejection Mixer integrated

- Start Code Detector block (SCD)

- I2C serial interface (standard mode/fast mode)

- BiCMOS SiGe technology

- VQFN package 5 x 5 mm

# **Applications**

- 350 to 400 MHz ISM Band System

- Set Top Box

# **Description**

This device is a single chip FSK/ASK receiver optimized for licence-free ISM band operations from 350MHz to 400 MHz. It can easily be configured to provide the optimal solution for the user's application like Set Top Box and 350/400 MHz ISM Band Systems.

Table 1. Device summary

| Paskago | Order codes |             |

|---------|-------------|-------------|

| Package | Tray        | Tape & Reel |

| QFN32L  | STB5701     | STB5701TR   |

Contents STB5701

# **Contents**

| 1 | Bloc | k diagra  | am and pin configuration                     | 6  |

|---|------|-----------|----------------------------------------------|----|

| 2 | Elec | trical sp | pecifications                                | 13 |

|   | 2.1  | Absolu    | ute maximum ratings                          | 13 |

|   | 2.2  | Therm     | nal data                                     | 13 |

| 3 | Elec | trical ch | naracteristics                               | 14 |

| 4 | Fund | ctional   | description                                  | 17 |

|   | 4.1  | Genera    | al description                               | 17 |

|   | 4.2  | Progra    | ammable Phase Locked Loop synthesizer (PLL)  | 18 |

|   |      | 4.2.1     | Divider (a-counter, m-counter and prescaler) | 18 |

|   |      | 4.2.2     | Reference divider                            | 19 |

|   |      | 4.2.3     | Phase Frequency Detector                     | 19 |

|   |      | 4.2.4     | Loop filter                                  | 20 |

|   | 4.3  | Receiv    | ver section                                  | 20 |

|   |      | 4.3.1     | Low Noise Amplifier (LNA)                    | 20 |

|   |      | 4.3.2     | Image Rejection Mixer                        | 21 |

|   |      | 4.3.3     | ASK/FSK demodulator and data filter          | 21 |

|   |      | 4.3.4     | Min /Max peak detector                       | 23 |

|   |      | 4.3.5     | Data slicer                                  | 23 |

|   | 4.4  | Digital   | control and source selection                 | 23 |

|   |      | 4.4.1     | State pin                                    | 24 |

|   |      | 4.4.2     | Data pin                                     | 24 |

|   |      | 4.4.3     | MODE register                                | 24 |

|   | 4.5  | Start c   | code detection example                       | 25 |

|   | 4.6  | Regist    | ers list                                     | 26 |

|   | 4.7  | Regist    | er summary                                   | 26 |

|   | 4.8  | _         | ed display description                       |    |

| 5 | Pack | age inf   | ormation                                     | 32 |

|   | 5.1  | ECOP      | ACK <sup>®</sup> packages                    | 32 |

|   | 5.2  |           | 2L (5mm x 5mm) information                   |    |

|   |      |           | , - ,                                        |    |

| STB5701 |                  | Conte | nts |

|---------|------------------|-------|-----|

| 6       | Revision history |       | 34  |

List of tables STB5701

# List of tables

| rable r.  | Device summary                           | !    |

|-----------|------------------------------------------|------|

| Table 2.  | Pin description                          | 6    |

| Table 3.  | Bill of material                         | . 11 |

| Table 4.  | Absolute maximum ratings (Tamb = 25oC)   | . 12 |

| Table 5.  | Thermal data                             | . 12 |

| Table 6.  | Electrical characteristics               | . 13 |

| Table 7.  | I2C reserved addresses                   | . 25 |

| Table 8.  | I2C address breakdown                    | . 25 |

| Table 9.  | I2C mapped top level registers - summary | . 25 |

| Table 10. | I2C mapped SCD registers - summary       | . 25 |

| Table 11. | DIG_config register format               | . 26 |

| Table 12. | RF_Config register format                | . 26 |

| Table 13. | PLL_A register                           | . 27 |

| Table 14. | PLL_M register format                    | . 27 |

| Table 15. | PLL_R register format                    | . 27 |

| Table 16. | SCD_config register format               | . 27 |

| Table 17. | SCD_status register format               | . 28 |

| Table 18. | SCD_code register format                 | . 28 |

| Table 19. | SCD_code_lenth register format           | . 28 |

| Table 20. | SCD_symbol_min_time register format      | . 28 |

| Table 21. | SCD_symbol_max_time register format      | . 29 |

| Table 22. | SCD_symbol_nom_time register format      | . 29 |

| Table 23. | SCD_prescaler register format            | . 29 |

| Table 24. | Interrupt_enable register format         |      |

| Table 25. | Interrupt_clear register format          | . 30 |

| Table 26. | Timeout register format                  | . 30 |

| Table 27. | QFN32L (5mm x 5mm) mechanical data       | . 32 |

| Table 28. | Document revision history                | . 33 |

|           |                                          |      |

STB5701 List of figures

# **List of figures**

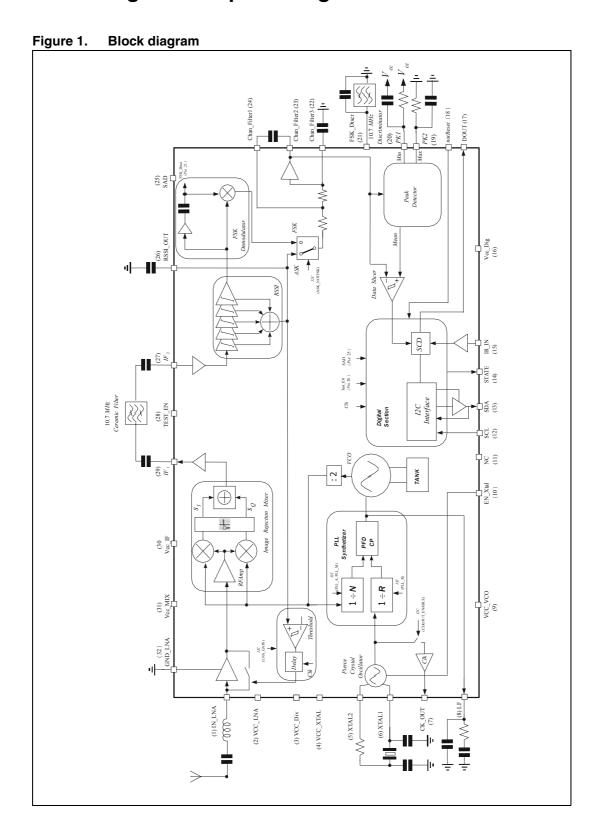

| Figure 1. | Block diagram                     | . 5 |

|-----------|-----------------------------------|-----|

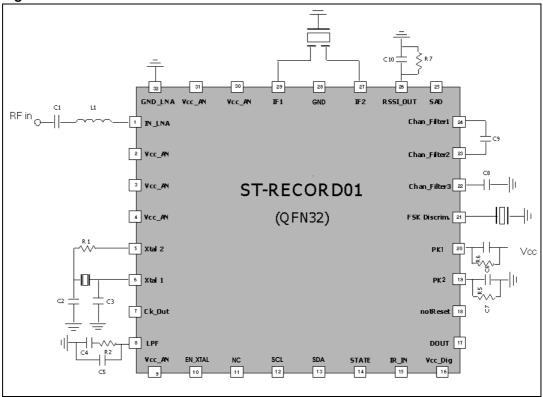

| Figure 2. | Test circuit                      | 10  |

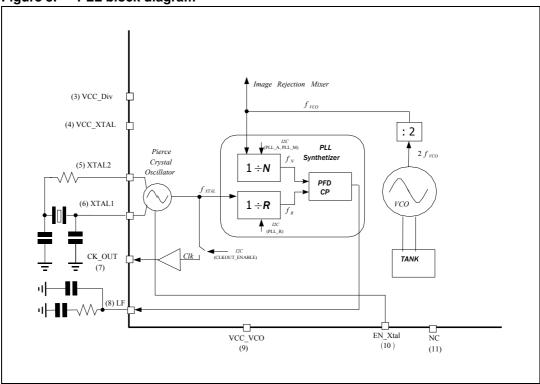

| Figure 3. | PLL block diagram                 | 17  |

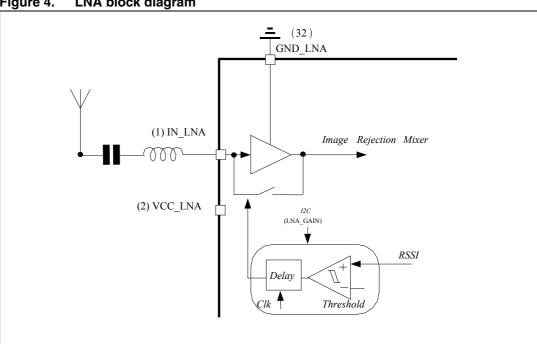

| Figure 4. | LNA block diagram                 | 19  |

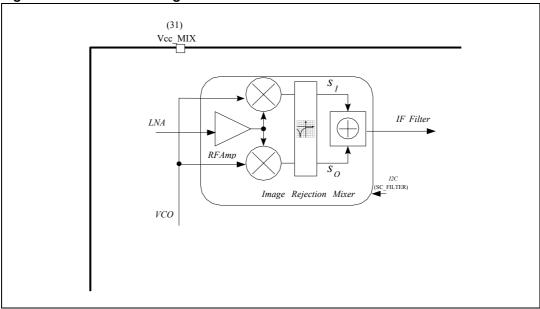

| Figure 5. | Mixer block diagram               | 20  |

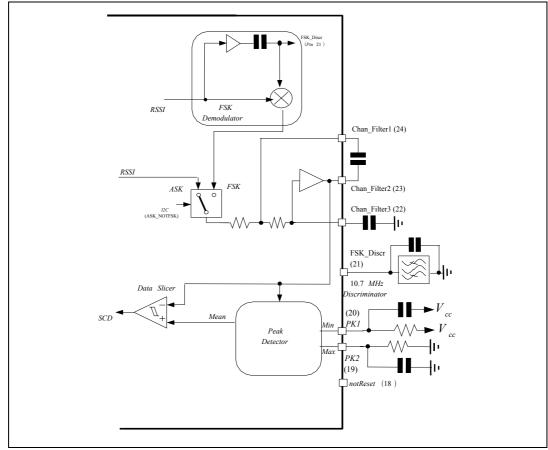

| Figure 6. | ASK/FSK demodulator block diagram | 21  |

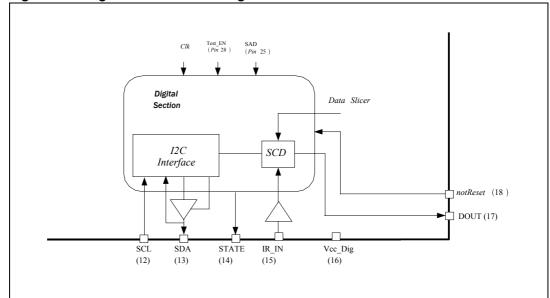

| Figure 7. | Digital section block diagram     | 22  |

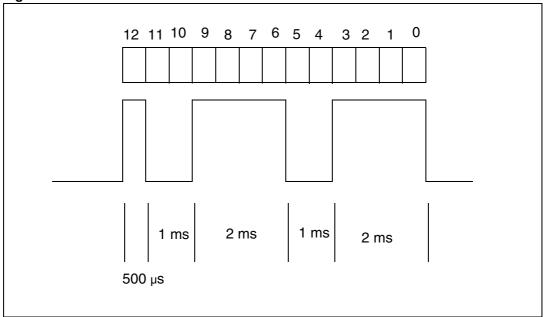

| Figure 8. | START code                        | 24  |

| Figure 9. | QFN32L (5mm x 5mm) dimensions     | 31  |

5/

# 1 Block diagram and pin configuration

Table 2. Pin description

| Pin | Name     | I/O<br>type | I/O schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Description                        |

|-----|----------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| 32  | GND_LNA  | GND         | DI, LINA Free GND, LINA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Low Noise Amplifier ground         |

| 1   | IN_LNA   | Ţ           | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Low Noise Amplifier input          |

| 2   | Vcc_LNA  | Vcc         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Low Noise Amplifier supply voltage |

| 3   | Vcc_Div  | Vcc         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Divider supply voltage             |

| 4   | Vcc_XTAL | Vcc         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Crystal supply voltage             |

| 5   | XTAL2    | 0           | XTAL2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2 <sup>nd</sup> Crystal input      |

| 6   | XTAL1    | I           | FCC FCC XTALL TO THE TOTAL TO THE TOTAL TO | 1 <sup>st</sup> Crystal input      |

| 7   | CK_OUT   | 0           | The cx_out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Clock output                       |

| 8   | LPF      | I/O         | LPF Proc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Loop filter                        |

| 9   | Vcc_VCO  | Vcc         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | VCO supply voltage                 |

| 10  | EN_XTAL  | I           | EN, Xual                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Crystal oscillator enable          |

| 11  | NC       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Not connected                      |

Table 2. Pin description (continued)

| Pin | Name     | I/O<br>type | I/O schematic                           | Description                    |

|-----|----------|-------------|-----------------------------------------|--------------------------------|

| 12  | SCL      | 1           | SCI.                                    | I2C clock                      |

| 13  | SDA      | -           | SDA DE FEE                              | I2C data In/Out                |

| 14  | STATE    | 0           | Fice STATE                              | High when selecting UHF        |

| 15  | IR_IN    | -           | FCC FCC FCC                             | From external IR source        |

| 16  | Vcc_Dig  | Vcc         |                                         | Digital section supply voltage |

| 17  | DOUT     | 0           | DOUT                                    | Digital serial output          |

| 18  | NotReset | I           | Fice Fice Fice Fice Fice Fice Fice Fice | Global reset, active low       |

Table 2. Pin description (continued)

| Pin | Name         | I/O<br>type | I/O schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Description           |

|-----|--------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| 19  | PK2          | I/O         | V <sub>cc</sub> PK2 V <sub>cc</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Max. peak detector    |

| 20  | PK1          | I/O         | Fee Property of the Property o | Min. peak detector    |

| 21  | FSK_Discrim  | I/O         | FSK_Discr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | FSK discriminator     |

| 22  | Chan_Filter3 | I/O         | Chan_Fiber3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Channel filter        |

| 23  | Chan_Filter2 | I/O         | Chan Filter2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Channel filter        |

| 24  | Chan_Filter1 | I/O         | Chan_Filter1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Channel filter        |

| 25  | SAD          | ı           | SAD - Fee                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | I2C address selection |

Table 2. Pin description (continued)

| Pin | Name     | I/O<br>type | I/O schematic | Description                            |

|-----|----------|-------------|---------------|----------------------------------------|

| 26  | RSSI_OUT | 0           | Vcc           | Radio strength signal indicator output |

| 27  | IF2      | 1           | F2 — Figure 1 | External IF filter input               |

| 28  | Test_EN  | ı           | TEST_EN Pec   | Test mode enable                       |

| 29  | IF1      | 0           | Vec Vec       | External IF filter output              |

| 30  | Vcc_IF   | Vcc         |               | IF supply voltage                      |

| 31  | Vcc_MIX  | Vcc         |               | Mixer supply voltage                   |

| EP  | GND      | GND         |               | Ground                                 |

Figure 2. Test circuit

Table 3. Bill of material

| Component | Size | Manufacturer | Part number           | Description                    |

|-----------|------|--------------|-----------------------|--------------------------------|

| C1        | 0603 | MURATA       | Series GRM39          | LNA Input matching             |

| C2        | 0603 | MURATA       | Series GRM39          | Crystal load capacitor         |

| C3        | 0603 | MURATA       | Series GRM39          | Crystal load capacitor         |

| C4        | 0603 | MURATA       | Series GRM39          | Loop filter capacitor          |

| C5        | 0603 | MURATA       | Series GRM39          | Loop filter capacitor          |

| C6        | 0603 | MURATA       | Series GRM39          | Peak detector capacitor        |

| C7        | 0603 | MURATA       | Series GRM39          | Peak detector capacitor        |

| C8        | 0603 | MURATA       | Series GRM39          | FSK Discriminator Tuning       |

| C9        | 0603 | MURATA       | Series GRM39          | Channel filter capacitor       |

| C10       | 0603 | MURATA       | Series GRM39          | Channel filter capacitor       |

| C11       | 0603 | MURATA       | Series GRM39          | RSSI output low path capacitor |

| C12       | 0603 | MURATA       | Series GRM39          | IF Filter DC Block             |

| C13       | 0603 | MURATA       | Series GRM39          | IF Filter DC Block             |

| R1        | 0603 | NEOHM        | Series CRG0603        | Resistor load capacitor        |

| R2        | 0603 | NEOHM        | Series CRG0603        | Loop filter resistor           |

| R3        | 0603 | NEOHM        | Series CRG0603        | Peak detector resistor         |

| R4        | 0603 | NEOHM        | Series CRG0603        | Peak detector resistor         |

| R5        | 0603 | NEOHM        | Series CRG0603        | RSSI output resistor           |

| R6        | 0603 | NEOHM        | Series CRG0603        | IF Filter Matching             |

| R7        | 0603 | NEOHM        | Series CRG0603        | IF Filter Matching             |

| L1        | 0603 | MURATA       | LQP18M                | LNA input matching             |

| X1        | CS10 | CITIZEN      | CS10-<br>27.000MABJTR | Crystal                        |

| F1        |      | Toko         | SK107M2N-A0-20X       | Ceramic filter                 |

| F2        |      | Toko         | CDF107F-AO-022        | Ceramic resonator              |

# 2 Electrical specifications

# 2.1 Absolute maximum ratings

Stressing the device above the rating listed in the "Absolute maximum ratings" table may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the Operating sections of this specification is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability. Refer also to the STMicroelectronics SURE Program and other relevant quality document

**Table 4.** Absolute maximum ratings  $(T_{amb} = 25^{\circ}C)$

| Symbol           | Parameter            | Value        | Unit |

|------------------|----------------------|--------------|------|

| V <sub>CC</sub>  | Supply voltage       | 4.5          | V    |

| T <sub>j</sub>   | Junction temperature | -40 to 150   | °C   |

| T <sub>stg</sub> | Storage temperature  | -55 to + 150 | οС   |

### 2.2 Thermal data

Table 5. Thermal data

| Symbol         | Parameter                              | Value  | Unit |

|----------------|----------------------------------------|--------|------|

| T <sub>a</sub> | Operating temperature                  | 0 + 70 | °C   |

| $\theta_{th}$  | Thermal resistance junction to ambient | 40     | °C/W |

Electrical characteristics STB5701

# 3 Electrical characteristics

(V $_{CC}$  = 3.3 V, Z $_{\rm s}$  = 50  $\Omega$ , Ta = 25  $^{\rm o}$ C, unless otherwise specified).

Table 6. Electrical characteristics

| Symbol                  | Parameters                            | Test conditions                                                                                       |                                                                                                                                                                      | Min.    | Тур.     | Max.   | Unit       |

|-------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------|--------|------------|

| Vcc                     | Supply voltage                        |                                                                                                       |                                                                                                                                                                      | 2.7     | 3.3      | 3.6    | V          |

| f <sub>rx</sub>         | Receive frequency range               |                                                                                                       |                                                                                                                                                                      | 350     |          | 400    | MHz        |

| Δf                      | FSK frequency deviation               |                                                                                                       |                                                                                                                                                                      | 25      | 37.5     | 50     | kHz        |

| I <sub>rx_FSK</sub>     | FSK receive<br>current<br>consumption | High g                                                                                                | ain LNA                                                                                                                                                              |         | 25       |        | mA         |

| I <sub>cc_standby</sub> | Standby current consumption           | RF Enable<br>bit=0                                                                                    | En_Xtal<br>(PIN 10) high /<br>floating                                                                                                                               |         | 5        |        | mA         |

|                         | , , , , , , , , , , , , , , , , , , , | J. C                                                                                                  | En_Xtal (PIN 10)<br>low                                                                                                                                              |         | 20       |        | μΑ         |

|                         | FSK data rate                         | (Manchest                                                                                             | er encoding)                                                                                                                                                         |         | 2        | 10     | kbps       |

| RLin                    | Input return loss                     |                                                                                                       |                                                                                                                                                                      |         | 10       |        | dB         |

|                         | Max RF power input                    |                                                                                                       |                                                                                                                                                                      |         |          | 0      | dBm        |

| P <sub>min</sub>        | Input sensitivity                     | 2 kbps<br>manchester<br>encoding<br>BER ≤10 <sup>-3</sup><br>BW = 300KHz<br>FSK 37.5 KHz<br>deviation | $RF_1 = 369.5MHz$<br>$RF_2 = 371.1MHz$<br>$RF_3 = 375.3MHz$<br>$RF_4 = 376.9MHz$<br>$RF_5 = 388.3MHz$<br>$RF_6 = 391.5MHz$<br>$RF_7 = 394.3MHz$<br>$RF_8 = 395.9MHz$ |         | -109     |        | dBm        |

|                         |                                       |                                                                                                       | RF <sub>X</sub> +/-30KHz                                                                                                                                             |         | -103     |        | dBm        |

|                         | Channel<br>blocking <sup>(1)</sup>    |                                                                                                       | IMHz<br>6MHz                                                                                                                                                         |         | 50<br>50 |        | dBc<br>dBc |

|                         | Image Rejection                       |                                                                                                       |                                                                                                                                                                      |         | 35       |        | dB         |

| I2C I/O p               | ins                                   |                                                                                                       |                                                                                                                                                                      |         |          |        |            |

| V <sub>IH</sub>         | Input logic<br>voltage high           |                                                                                                       |                                                                                                                                                                      | 0.7 Vcc |          | 3.6    | V          |

| V <sub>IL</sub>         | Input logic<br>voltage low            |                                                                                                       |                                                                                                                                                                      | -0.5    |          | 0.3Vcc | V          |

Table 6. Electrical characteristics (continued)

| Symbol              | Parameters                                                                                                              | Test conditions | Min.                  | Тур. | Max. | Unit |

|---------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------|------|------|------|

| V <sub>OL</sub>     | Output logic voltage low                                                                                                |                 |                       |      | 0.4  | V    |

| V <sub>HYST</sub>   | Hysteresis of<br>schmitt trigger<br>for inputs                                                                          |                 | 0.05 Vcc              |      |      | ٧    |

| t <sub>of</sub>     | Output fall time<br>from V <sub>IHmin</sub> to<br>V <sub>ILmax</sub> with a<br>bus capacitance<br>from 10pF to<br>400pF |                 | 20+ 0.1C <sub>b</sub> |      | 250  | ns   |

| l <sub>i</sub>      | Input current<br>each I/O pin with<br>an input voltage<br>between 0.1V <sub>cc</sub><br>and 0.9V <sub>cc</sub>          |                 | -10                   |      | 10   | μΑ   |

| C <sub>i</sub>      | Capacitance for each I/O pin                                                                                            |                 |                       |      | 10   | pF   |

| C <sub>b</sub>      | Capacitive load for each bus line                                                                                       |                 |                       |      | 400  | pF   |

| I2C Stan            | dard mode                                                                                                               |                 | 1                     |      | l    |      |

| f <sub>SCL</sub>    | SCL clock<br>frequency                                                                                                  |                 | 0                     |      | 100  | kHz  |

| t <sub>SU_STA</sub> | Setup time for START condition                                                                                          |                 | 4.7                   |      |      | μs   |

| t <sub>HD_STA</sub> | Hold time for START condition                                                                                           |                 | 4                     |      |      | μs   |

| t <sub>HIGH</sub>   | SCL high time                                                                                                           |                 | 4                     |      |      | μs   |

| $t_{LOW}$           | SCL low time                                                                                                            |                 | 4.7                   |      |      | μs   |

| t <sub>SU_DAT</sub> | DATA setup time                                                                                                         |                 | 250                   |      |      | ns   |

| t <sub>HD_DAT</sub> | DATA hold time                                                                                                          |                 | 0                     |      | 3.45 | μs   |

| t <sub>R</sub>      | SDA, SCL rise time                                                                                                      |                 |                       |      | 1000 | ns   |

| t <sub>F</sub>      | SDA, SCL fall time                                                                                                      |                 |                       |      | 300  | ns   |

| t <sub>SU_STO</sub> | Setup time for STOP condition                                                                                           |                 | 4                     |      |      | μs   |

| t <sub>BUF</sub>    | Bus free time<br>between STOP<br>and START<br>condition                                                                 |                 | 4.7                   |      |      | μs   |

Electrical characteristics STB5701

Table 6. Electrical characteristics (continued)

| Symbol              | Parameters                                              | Test conditions | Min. | Тур. | Max. | Unit |

|---------------------|---------------------------------------------------------|-----------------|------|------|------|------|

| I2C Fast            | mode                                                    |                 |      |      |      |      |

| f <sub>SCL</sub>    | SCL clock<br>frequency                                  |                 | 0    |      | 400  | kHz  |

| t <sub>SU_STA</sub> | Setup time for START condition                          |                 | 0.6  |      |      | μs   |

| t <sub>HD_STA</sub> | Hold time for START condition                           |                 | 0.6  |      |      | μs   |

| t <sub>HIGH</sub>   | SCL high time                                           |                 | 0.6  |      |      | μs   |

| t <sub>LOW</sub>    | SCL low time                                            |                 | 1.3  |      |      | μs   |

| t <sub>SU_DAT</sub> | DATA setup time                                         |                 | 100  |      |      | ns   |

| t <sub>HD_DAT</sub> | DATA hold time                                          |                 | 0    |      | 0.9  | μs   |

| t <sub>R</sub>      | SDA, SCL rise time                                      |                 |      |      | 300  | ns   |

| t <sub>F</sub>      | SDA, SCL fall time                                      |                 |      |      | 300  | ns   |

| t <sub>SU_STO</sub> | Setup time for STOP condition                           |                 | 0.6  |      |      | μs   |

| t <sub>BUF</sub>    | Bus free time<br>between STOP<br>and START<br>condition |                 | 1.3  |      |      | μs   |

<sup>1.</sup> Desired signal 10dB above the input sensitivity level, CW interferer power level increased until BER ±10<sup>-3</sup>

# 4 Functional description

### 4.1 General description

The STB5701 FSK/ASK receiver is a heterodyne configuration (10.7 MHz IF Frequency) and it is designed for applications in the 350MHz to 400MHz frequency range and includes ASK and FSK detectors. The synthesizer has a typical channel spacing of better than 100 kHz and uses a integrated fully VCO. With the STB5701 receiver chip, various circuit configurations can be arranged in order to meet a number of different customer requirement.

The STB5701 is housed in a VQF package 5mm x 5mm 32 leads.

The STB5701 receiver IC consists of the following building blocks:

- Phase Locked Loop Synthesizer (PLL): M-Counter, A-Counter, Prescaler, Phase-Frequency Detector (PFD), Charge Pump (CP), Voltage Controlled Oscillator (VCO).

- Programmable reference divider for crystal and channel step selection.

- Low Noise Amplifier (LNA) with AGC function for high sensitivity and dynamic range RF signal reception.

- Image Rejection Mixer for down conversion of the RF signal to the IF (without external saw image filter).

- IF amplifier to amplify and limit the IF signal and for RSSI generation.

- Phase coincidence demodulator to demodulate the IF signal.

- Operation amplifier for data slicing, filtering and ASK detection.

- Min/max peak detector to create a DC output voltage equal to the mean of the min and max peak value of the data signal.

- I2C bus to exchange data between the STB5701 and the micro.

- Start code detector (SCD) to recognize a valid data signal to prevent continuos toggling

of data in the absence of an RF Signal due to the noise.

- Bias circuitry for band gap biasing and circuit shutdown.

# 4.2 Programmable Phase Locked Loop synthesizer (PLL)

Figure 3. PLL block diagram

The synthesized programmable local oscillator is a Phase Locked Loop (PLL) using a 'parallel-resonant' quartz crystal as frequency reference. The PLL block contains a phase detector, charge pump, VCO, Programmable N and R Divider and a Crystal Oscillator. The synthesized frequency (fVCO) is set by programming the 'N' Divider through the I2C interface (PINs 12, 13).

$$f_{R} = f_{XTAL} / R$$

$$f_{VCO} = N \cdot f_{N} = N \cdot f_{R} = (N / R) \cdot f_{XTAL}$$

### 4.2.1 Divider (a-counter, m-counter and prescaler)

The main divider (N) of the PLL contains a 3-bit A-counter, a 10-bit M-counter and an 8/9 prescaler. The divider ratio of the prescaler is controlled by the program counter and the swallow counter. During one cycle, the prescaler divides by 9 until the swallow A-counter reaches its terminal count. Afterwards the prescaler divider by 8 until the program counter reaches its terminal count. Therefore the overall feedback divider ratio can be expressed as:

$$N = 9 \cdot A + 8 \cdot (M - A)$$

The A-counter configuration represents the lower bits in the feedback divider register and the upper bits the M-counter configuration respectively. According to that, the following counter ranges are implemented:

$$0 \le A \le 7$$

$$7 \le M \le 1023$$

and therefore the range of the overall feedback divider ratio results in:

$$56 \le N \le 8191$$

The user does not need to care about the A- and M-counter settings. It is only necessary to know the overall feedback divider ratio N to program the register settings.

### 4.2.2 Reference divider

The reference divider reduces the frequency of the external crystal (FXTAL) to an internal reference frequency (FR) used for the phase-locked loop.

This value, corresponding to the channel step, it is set by programming a 10-bit counter through the I2C interface (PINs 12, 13).

Therefore the range of the Reference divider ratio is:

$$0 \le R \le 1023$$

### 4.2.3 Phase Frequency Detector

The phase detector (PFD) is a device that compares two input (fN and fR) phases, generating an output that is a measure of their phase difference.

The gain of the phase detector can be expressed as:

$$K_{PD} = I_{CP} / 2\pi$$

where ICP is the charge pump current.

If fR doesn't equal fN, the phase-error signal, after being filtered and amplified, causes the VCO frequency to deviate in the direction of fR.

#### 4.2.4 Loop filter

An external PLL loop filter is connected to pin LF (PIN 8). The loop filter controls the dynamic behavior of the PLL, primarily lock time and reference spur levels. Generally, the PLL lock time is a small fraction of the overall receiver start-up time. The crystal oscillator is the largest contributor to start-up time.

#### 4.3 **Receiver section**

The integrated receiver is intended to be used as a single-conversion FSK/ASK receiver. It consists of a low noise amplifier, mixer, IF filter, limiter, FSK demodulator, a LPF amplifier, and a data slicer. The received strength signal indicator (RSSI) can be used for fast carrier sense detection or as amplitude shift keying, (ASK) demodulator.

#### 4.3.1 Low Noise Amplifier (LNA)

The LNA is based on a cascode topology for low-noise, high gain and good reverse isolation. The LNA output is directly connected to the mixer removing the external output matching.

It has 2 step gain managed by an internal AGC. This AGC circuit monitors the RSSI output. The AGC has a hysteresis of ~10dB.

### 4.3.2 Image Rejection Mixer

Figure 5. Mixer block diagram

An excellent feature of the STB5701 is the integrated image rejection mixer. This device was designed to eliminate the need for a costly front-end SAW filter for many applications. The advantage of not using a SAW filter is increased sensitivity, simplified antenna matching, less board space, and lower cost. The mixer cell is a pair of double-balanced mixers that perform an IQ down conversion of the 350-400MHz RF input to the IF (10.7MHz) with low-side injection (i.e.,  $f_{RF} = f_{LO} - f_{IF}$ ). The Image Rejection circuit combines these signals to achieve ~35dB of Image Rejection over the full temperature range. Low-side injection is required due to the on-chip Image Rejection architecture.

### 4.3.3 ASK/FSK demodulator and data filter

The received signal strength indicator (RSSI) voltage is proportional to the log of the down-converted RF signal at the IF limiting amplifier input. It also used as demodulator for amplitude-shift \ keying (ASK) modulation. The signal coming from the RSSI amplifier is converted into the raw data signal by the ASK/FSK demodulator. The ASK or FSK modulation selection is set by I2C interface.

The dynamic range of the RSSI amplifier is exceeded if the RF input signal is about 80 dB higher compared to the RF input signal at full sensitivity.

In FSK mode, the S/N ratio is not affected by the dynamic range of the RSSI amplifier but at FSK receive mode the RSSI output provides a field strength indication.

Coming from the RSSI the FSK signal is fed to the input of the FSK demodulator. After buffering the signal is fed to a phase discriminator. The phase shift is generated by an external 10.7MHz Ceramic discriminator connected to FSK\_Discr. (PIN 21).

The FSK demodulator is intended to be used for an FSK deviation of 37.5 kHz. Lower values may be used but the sensitivity of the receiver is reduced in that condition. After demodulation a 2nd order Sallen and Key filter is provided in order to suppress unwanted frequency components.

Figure 6. ASK/FSK demodulator block diagram

### 4.3.4 Min /Max peak detector

The peak detector embedded in the STB5701, in conjunction with an external RC filter (PINs 22, 23, 24), generates a DC output voltage equal to the mean of the min and max peak value of the data signal. The resistor provides a path for the capacitor to discharge, allowing the peak detector to dynamically follow peak changes of the data filter output voltage.

### 4.3.5 Data slicer

The purpose of the data slicer is to take the analog output of the data filter and convert it to a digital signal. This is achieved by using a comparator and comparing the analog input to a threshold voltage. One input is supplied by the data filter output.

The other path is fed to the min/max Peak detector to derive the average value (DC component) as an adaptive slice reference which is presented to the positive comparator input. The adaptive reference allows detecting the received data over a large range of noise floor levels.

# 4.4 Digital control and source selection

Figure 7. Digital section block diagram

The STB5701 digital section is responsible for the following functions: