#### SY54023R

# Low Voltage 1.2V/1.8V CML 2x2 Crosspoint Switch with Fail-Safe Inputs, 3.2Gbps, 2.5GHz

#### **General Description**

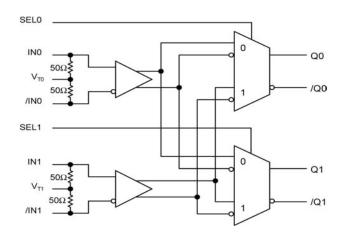

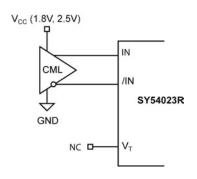

The SY54023R is a fully differential, low voltage 1.2V/1.8V CML 2x2 Crosspoint Switch with Fail Safe Inputs. The SY54023R can process clock signals as fast as 2.5GHz or data patterns up to 3.2Gbps.

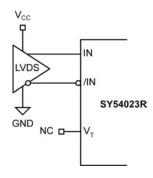

The differential input includes Micrel's unique, 3-pin input termination architecture that interfaces to LVPECL, LVDS or CML differential signals, (AC- or DC-coupled from a 2.5V driver) as small as 100mV (200mV<sub>PP</sub>) without any level-shifting or termination resistor networks in the signal path. For AC-coupled input interface applications, an internal voltage reference is provided to bias the V<sub>T</sub> pin. The outputs are CML, with extremely fast rise/fall times guaranteed to be less than 95ps.

The SY54023R operates from a 2.5V  $\pm$ 5% core supply and a 1.8V or 1.2V  $\pm$ 5% output supply and is guaranteed over the full industrial temperature range ( $-40^{\circ}$ C to  $+85^{\circ}$ C). The SY54023R is part of Micrel's high-speed, Precision Edge® product line.

Datasheets and support documentation can be found on Micrel's web site at: <a href="https://www.micrel.com">www.micrel.com</a>.

# **Functional Block Diagram**

Precision Edge®

#### **Features**

- 1.2V/1.8V CML 2x2 Crosspoint Switch with Fail Safe Inputs

- Guaranteed AC performance over temperature and voltage:

- DC-to- > 3.2Gbps throughput

- <400ps propagation delay (IN-to-Q)</li>

- <15ps Output Skew

- <95ps rise/fall times</p>

- · Ultra-low jitter design

- <1ps<sub>RMS</sub> cycle-to-cycle jitter

- <10ps<sub>PP</sub> total jitter

- <1ps<sub>RMS</sub> random jitter

- <10ps<sub>PP</sub> deterministic jitter

- High-speed CML outputs

- 2.5V ±5%, 1.8/1.2V ±5% power supply operation

- Industrial temperature range: -40°C to +85°C

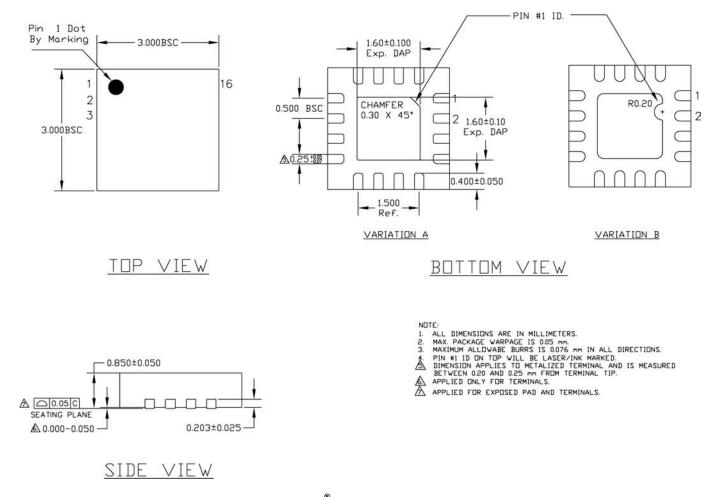

- Available in 16-pin (3mm x 3mm) MLF<sup>®</sup> package

### **Applications**

- Data Distribution: OC-48, OC-48+FEC

- SONET clock and data distribution

- · Fibre Channel clock and data distribution

- · Gigabit Ethernet clock and data distribution

#### Markets

- Storage

- ATE

- · Test and measurement

- Enterprise networking equipment

- High-end servers

- Access

- Metro area network equipment

Precision Edge is a registered trademark of Micrel, Inc. MLF and *Micro*LeadFrame are registered trademarks of Amkor Technology.

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • http://www.micrel.com

# Ordering Information<sup>(1)</sup>

| Part Number                 | Package<br>Type | Operating<br>Range | Package Marking                         | Lead<br>Finish    |

|-----------------------------|-----------------|--------------------|-----------------------------------------|-------------------|

| SY54023RMG                  | MLF-16          | Industrial         | 023R<br>with Pb-Free bar-line indicator | NiPdAu<br>Pb-Free |

| SY54023RMGTR <sup>(2)</sup> | MLF-16          | Industrial         | 023R<br>with Pb-Free bar-line indicator | NiPdAu<br>Pb-Free |

#### Notes:

- 1. Contact factory for die availability. Dice are guaranteed at T<sub>A</sub> = 25°C, DC Electricals only.

- 2. Tape and Reel.

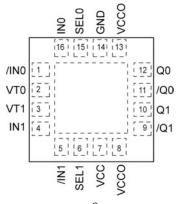

# **Pin Configuration**

16-Pin MLF® (MLF-16)

# **Pin Description**

| Pin Number  | Pin Name              | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

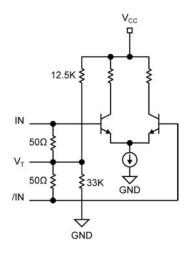

| 16,1<br>4,5 | INO, /INO<br>IN1,/IN1 | Differential Inputs: These input pairs are the differential signal inputs to the device. They accept differential signals as small as 100mV (200mV $_{PP}$ ). Each input pin internally terminates with 50 $\Omega$ to the VT pin. If the input swing falls below a certain threshold (typical 30mV), the Fail-Safe Input (FSI) feature will guarantee a stable output by latching the output to its last valid state. |

| 2           | VT0                   | Input Termination Center-Tap: Each side of the differential input pair terminates to VT pin.                                                                                                                                                                                                                                                                                                                           |

| 3           | VT1                   | This pin provides a center-tap to a termination network for maximum interface flexibility. An internal high impedance resistor divider biases VT to allow input AC-coupling. For AC-coupling, bypass VT with a 0.1µF low ESR capacitor to VCC. See "Interface Applications" subsection and Figure 2a.                                                                                                                  |

| 15          | SEL0                  | These single-ended TTL/CMOS-compatible inputs select the inputs of the crosspoint switch.                                                                                                                                                                                                                                                                                                                              |

| 6           | SEL1                  | Note that these inputs are internally connected to a $25k\Omega$ pull-up resistor and will default to a logic HIGH state if left open.                                                                                                                                                                                                                                                                                 |

| 7           | VCC                   | Positive Power Supply: Bypass with $0.1\mu F//0.01\mu F$ low ESR capacitors as close to the $V_{CC}$ pin as possible. Supplies input and core circuitry.                                                                                                                                                                                                                                                               |

| 8,13        | VCCO                  | Output Supply: Bypass with $0.1\mu F//0.01\mu F$ low ESR capacitors as close to the $V_{CCO}$ pins as possible. Supplies the output buffers.                                                                                                                                                                                                                                                                           |

| 14          | GND,<br>Exposed pad   | Ground: Exposed pad must be connected to a ground plane that is the same potential as the ground pin.                                                                                                                                                                                                                                                                                                                  |

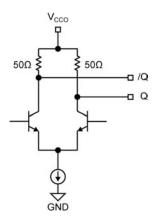

| 12,11       | Q0, /Q0               | CML Differential Output Pairs: Differential buffered copies of the input signal. The output                                                                                                                                                                                                                                                                                                                            |

| 10,9        | Q1, /Q1               | swing is typically 390mV. See "Interface Applications" subsection for termination information.                                                                                                                                                                                                                                                                                                                         |

# **Truth Table**

| SEL0 | SEL1 | Q0  | Q1  |

|------|------|-----|-----|

| L    | L    | IN0 | IN0 |

| L    | Н    | IN0 | IN1 |

| Н    | L    | IN1 | IN0 |

| Н    | Н    | IN1 | IN1 |

# Absolute Maximum Ratings<sup>(1)</sup>

| Supply Voltage (V <sub>CC</sub> )      | 0.5V to +3.0V                   |

|----------------------------------------|---------------------------------|

| Supply Voltage (V <sub>CCO</sub> )     | 0.5V to +2.7V                   |

| V <sub>CC</sub> - V <sub>CCO</sub>     | <1.8V                           |

| V <sub>CCO</sub> - V <sub>CC</sub>     | <0.5V                           |

| Input Voltage (V <sub>IN</sub> )       | –0.5V to V <sub>CC</sub>        |

| CML Output Voltage (V <sub>OUT</sub> ) | .0.6V to V <sub>CCO</sub> +0.5V |

| Current (V <sub>T</sub> )              |                                 |

| Source or sink current on VT pin.      | ±100mA                          |

| Input Current                          |                                 |

| Source or sink current on (IN, /IN)    | ±50mA                           |

| Maximum operating Junction Tempera     | ature125°C                      |

| Lead Temperature (soldering, 20sec.)   | 260°C                           |

| Storage Temperature (T <sub>s</sub> )  | 65°C to +150°C                  |

|                                        |                                 |

# Operating Ratings<sup>(2)</sup>

| Supply Voltage (V <sub>CC</sub> )         | 2.375V to 2.625V |

|-------------------------------------------|------------------|

| (V <sub>CCO</sub> )                       | 1.14V to 1.9V    |

| Ambient Temperature (T <sub>A</sub> )     | 40°C to +85°C    |

| Package Thermal Resistance <sup>(3)</sup> |                  |

| MLF <sup>®</sup>                          |                  |

| Still-air ( $\theta_{JA}$ )               | 75°C/W           |

| Junction-to-board $(\psi_{JB})$           | 33°C/W           |

## DC Electrical Characteristics<sup>(4)</sup>

$T_A = -40$ °C to +85°C, unless otherwise stated.

| Symbol               | Parameter                                                           | Condition                                   | Min   | Тур | Max                  | Units |

|----------------------|---------------------------------------------------------------------|---------------------------------------------|-------|-----|----------------------|-------|

| V <sub>CC</sub>      | Power Supply Voltage Range                                          | V <sub>cc</sub>                             | 2.375 | 2.5 | 2.625                | V     |

|                      |                                                                     | V <sub>cco</sub>                            | 1.14  | 1.2 | 1.26                 | V     |

|                      |                                                                     | V <sub>cco</sub>                            | 1.7   | 1.8 | 1.9                  | V     |

| I <sub>CC</sub>      | Power Supply Current                                                | Max. V <sub>cc</sub>                        |       | 42  | 55                   | mA    |

| I <sub>cco</sub>     | Power Supply Current                                                | No Load. Max V <sub>cco</sub>               |       | 32  | 42                   | mA    |

| R <sub>IN</sub>      | Input Resistance<br>(IN-to-V <sub>T</sub> , /IN-to-V <sub>T</sub> ) |                                             | 45    | 50  | 55                   | Ω     |

| R <sub>DIFF_IN</sub> | Differential Input Resistance (IN-to-/IN)                           |                                             | 90    | 100 | 110                  | Ω     |

| V <sub>IH</sub>      | Input HIGH Voltage (IN, /IN)                                        | IN, /IN                                     | 1.2   |     | V <sub>CC</sub>      | V     |

| $V_{IL}$             | Input LOW Voltage (IN, /IN)                                         | V <sub>IL</sub> with V <sub>IH</sub> = 1.2V | 0.2   |     | V <sub>IH</sub> -0.1 | V     |

| V <sub>IH</sub>      | Input HIGH Voltage (IN, /IN)                                        | IN, /IN                                     | 1.14  |     | V <sub>CC</sub>      | V     |

| $V_{\text{IL}}$      | Input LOW Voltage (IN, /IN)                                         | $V_{IL}$ with $V_{IH} = 1.14V$ , (1.2V-5%)  | 0.66  |     | V <sub>IH</sub> -0.1 | V     |

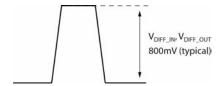

| V <sub>IN</sub>      | Input Voltage Swing (IN, /IN)                                       | see Figure 3a                               | 0.1   |     | 1.0                  | V     |

| V <sub>DIFF_IN</sub> | Differential Input Voltage Swing ( IN - /IN )                       | see Figure 3b                               | 0.2   |     | 2.0                  | V     |

| V <sub>IN_FSI</sub>  | Input Voltage Threshold that Triggers FSI                           |                                             |       | 30  | 100                  | mV    |

| V <sub>T_IN</sub>    | Voltage from Input to V <sub>T</sub>                                |                                             |       |     | 1.28                 | V     |

#### Notes:

Permanent device damage may occur if absolute maximum ratings are exceeded. This is a stress rating only and functional operation is not implied at conditions other than those detailed in the operational sections of this data sheet. Exposure to absolute maximum ratings conditions for extended periods may affect device reliability.

<sup>2.</sup> The data sheet limits are not guaranteed if the device is operated beyond the operating ratings.

<sup>3.</sup> Package thermal resistance assumes exposed pad is soldered (or equivalent) to the device's most negative potential on the PCB.  $\psi_{JB}$  and  $\theta_{JA}$  values are determined for a 4-layer board in still-air number, unless otherwise stated.

<sup>4.</sup> The circuit is designed to meet the DC specifications shown in the above table after thermal equilibrium has been established.

# CML Outputs DC Electrical Characteristics<sup>(5)</sup>

$V_{CCO}$  = 1.14V to 1.26V R<sub>L</sub> = 50 $\Omega$  to  $V_{CCO}$

$V_{CCO}$  = 1.7V to 1.9V,  $R_L$  = 50 $\Omega$  to  $V_{CCO}$  or 100 $\Omega$  across the outputs,

$V_{CC}$  = 2.375V to 2.625V.  $T_A$  = -40°C to +85°C, unless otherwise stated.

| Symbol                | Parameter                         | Condition                     | Min                 | Тур                 | Max  | Units |

|-----------------------|-----------------------------------|-------------------------------|---------------------|---------------------|------|-------|

| V <sub>OH</sub>       | Output HIGH Voltage               | $R_L = 50\Omega$ to $V_{CCO}$ | <b>V</b> cco -0.020 | <b>V</b> cco -0.010 | Vcco | V     |

| V <sub>OUT</sub>      | Output Voltage Swing              | See Figure 3a                 | 300                 | 390                 | 475  | mV    |

| V <sub>DIFF_OUT</sub> | Differential Output Voltage Swing | See Figure 3b                 | 600                 | 780                 | 950  | mV    |

| R <sub>OUT</sub>      | Output Source Impedance           |                               | 45                  | 50                  | 55   | Ω     |

# LVTTL/CMOS DC Electrical Characteristics<sup>(5)</sup>

$V_{CC}$  = 2.5V ±5%;  $V_{CCO}$  = +1.14V to +1.26V or +1.7V to +1.9V;  $T_A$  = -40°C to +85°C, unless otherwise stated.

| Symbol          | Parameter          | Condition | Min  | Тур | Max             | Units |

|-----------------|--------------------|-----------|------|-----|-----------------|-------|

| V <sub>IH</sub> | Input HIGH Voltage |           | 2.0  |     | V <sub>cc</sub> | V     |

| V <sub>IL</sub> | Input LOW Voltage  |           |      |     | 0.8             | V     |

| I <sub>IH</sub> | Input HIGH Current |           | -125 |     | 30              | μA    |

| I <sub>IL</sub> | Input LOW Current  |           | -300 |     |                 | μA    |

#### Note:

5. The circuit is designed to meet the DC specifications shown in the above table after thermal equilibrium has been established.

#### **AC Electrical Characteristics**

$V_{CCO}$  = 1.14V to 1.26V R<sub>L</sub> = 50 $\Omega$  to  $V_{CCO}$

$V_{\text{CCO}}$  = 1.7V to 1.9V,  $R_{L}$  =  $50\Omega$  to  $V_{\text{CCO}}$  or  $100\Omega$  across the outputs,

$V_{CC}$  = 2.375V to 2.625V.  $T_A$  = -40°C to +85°C, unless otherwise stated.

| Symbol                        | Parameter                           | Condition                                        | Min | Тур | Max | Units             |

|-------------------------------|-------------------------------------|--------------------------------------------------|-----|-----|-----|-------------------|

| f <sub>MAX</sub>              | Maximum Frequency                   | NRZ Data                                         | 3.2 |     |     | Gbps              |

|                               |                                     | V <sub>OUT</sub> > 200mV Clock                   | 2.5 |     |     | GHz               |

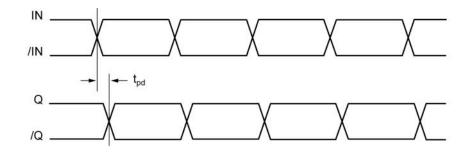

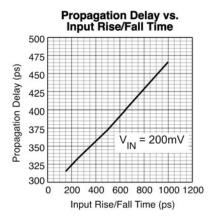

| t <sub>PD</sub>               | Propagation Delay IN-to-0           | V <sub>IN</sub> : 100mV-200mV, Note 6, Figure 1a | 250 | 350 | 500 | ps                |

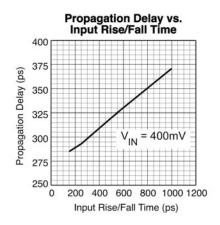

|                               |                                     | V <sub>IN</sub> : >200mV, Note 6, Figure 1a      | 200 | 300 | 400 | ps                |

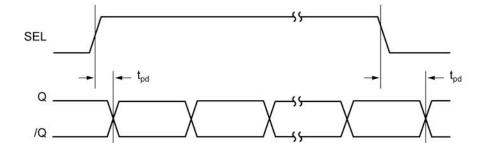

|                               | SEL-to-0                            | Figure 1a                                        | 90  |     | 350 | ps                |

| t <sub>Skew</sub>             | Input-to-Input Skew                 | Note 6                                           |     | 5   | 20  | ps                |

|                               | Output-to-Output skew               | Note 7                                           |     | 3   | 15  | ps                |

|                               | Part-to-Part Skew                   | Note 8                                           |     |     | 75  | ps                |

| t <sub>Jitter</sub>           | Data Random Jitter                  | Note 9                                           |     |     | 1   | ps <sub>RMS</sub> |

|                               | Deterministic Jitter                | Note 10                                          |     |     | 10  | ps <sub>PP</sub>  |

|                               | Clock Cycle-to-Cycle Jitte          | Note 11                                          |     |     | 1   | ps <sub>RMS</sub> |

|                               | Total Jitter                        | Note 12                                          |     |     | 10  | ps <sub>PP</sub>  |

|                               | Crosstalk Induced Jitte             | r Note 13                                        |     |     | 0.7 | ps <sub>PP</sub>  |

|                               | (Adjacent Channe                    | )                                                |     |     |     |                   |

| t <sub>R</sub> t <sub>F</sub> | Output Rise/Fall Times (20% to 80%) | At full output swing.                            | 30  | 60  | 95  | ps                |

|                               | Duty Cycle                          | Differential I/O                                 | 47  |     | 53  | %                 |

#### Notes:

- 6. Input-to-Input skew is the difference in time between both inputs, measured at the same output, for the same temperature, voltage and transition.

- Output-to-Output skew is the difference in time between both outputs, receiving data from the same input, for the same temperature, voltage and transition.

- Part-to-part skew is defined for two parts with identical power supply voltages at the same temperature and no skew at the edges at the respective inputs. V<sub>IN</sub> >200mV with input t<sub>r</sub>/t<sub>t</sub> ≤300ps (20% to 80%).

- 9. Random jitter is measured with a K28.7 pattern, measured at  $\leq$  f<sub>MAX</sub>.

- 10. Deterministic jitter is measured at 2.5Gbps with both K28.5 and 2<sup>23</sup>–1 PRBS pattern.

- 11. Cycle-to-cycle jitter definition: the variation period between adjacent cycles over a random sample of adjacent cycle pairs. t<sub>JITTER\_CC</sub> = T<sub>n</sub> -T<sub>n+1</sub>, where T is the time between rising edges of the output signal.

- 12. Total jitter definition: with an ideal clock input frequency of ≤ f<sub>MAX</sub> (device), no more than one output edge in 10<sup>12</sup> output edges will deviate by more than the specified peak-to-peak jitter value.

- 13. Crosstalk induced jitter is defined as the added jitter that results from signals applied to the adjacent channel. It is measured at the output while applying a similar, differential clock frequency to both inputs that is asynchronous with respect to each other.

#### **Functional Description**

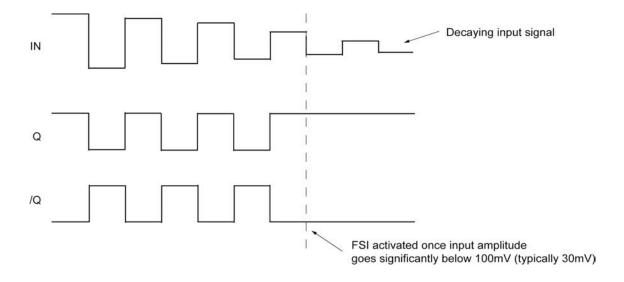

#### Fail-Safe Input (FSI)

The input includes a special failsafe circuit to sense the amplitude of the input signal and to latch the output when there is no input signal present, or when the amplitude of the input signal drops sufficiently below 100mV<sub>PK</sub> (200mV<sub>PP</sub>), typically 30mV<sub>PK</sub>. Maximum frequency of the SY54023R is limited by the FSI function.

#### Input Clock Failure Case

If the input clock fails to a floating, static, or extremely low signal swing, the FSI function will eliminate a metastable condition and guarantee a stable output. No ringing and no undetermined state will occur at the output under these conditions.

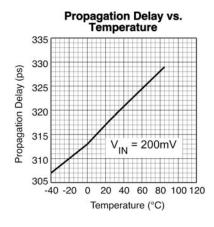

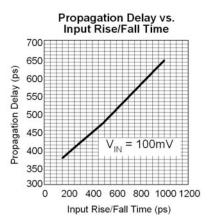

Note that the FSI function will not prevent duty cycle distortion in case of a slowly deteriorating (but still toggling) input signal close to the FSI threshold. Due to the FSI function, the propagation delay will depend on rise and fall time of the input signal and on its amplitude. Refer to "Typical Characteristics" for detailed information

#### Interface Applications

For Input Interface Applications, see Figures 4a through 4f and for CML Output Termination, see Figures 5a through 5d.

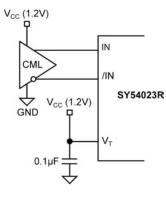

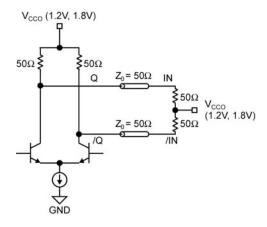

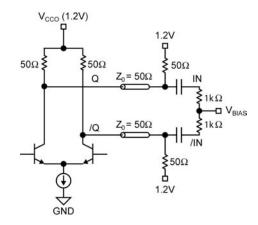

#### CML Output Termination with VCCO 1.2V

For VCCO of 1.2V, Figure 5a, terminate the output with  $50\Omega$ -to-1.2V, DC-coupled, not  $100\Omega$  differentially across the outputs.

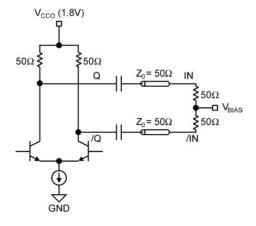

If AC-coupling is used, Figure 5d, terminate into  $50\Omega$ to-1.2V before the coupling capacitor and then connect to a high value resistor to a reference voltage.

Do not AC couple with internally terminated receiver. For example,  $50\Omega$  ANY-IN input. AC-coupling will offset the output voltage by 200mV and this offset voltage will be too low for proper driver operation.

Any unused output pair needs to be terminated when VCCO is 1.2V, do not leave floating.

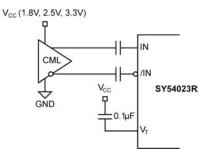

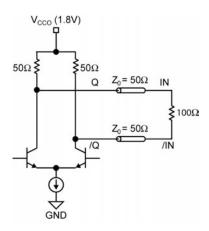

#### CML Output Termination with VCCO 1.8V

For VCCO of 1.8V, Figure 5a and Figure b, terminate with either  $50\Omega$ -to-1.8V or  $100\Omega$  differentially across the outputs. AC- or DC-coupling is fine.

#### Input AC Coupling

The SY54023R input can accept AC-coupling from any driver. Bypass VT with a 0.1µF low ESR capacitor to VCC as shown in Figures 4c and 4d. VT has an internal high impedance resistor divider as shown in Figure 2a, to provide a bias voltage for AC-coupling.

# **Timing Diagrams**

Figure 1a. Propagation Delay

Figure 1b. Fail Safe Feature

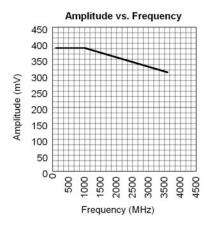

## **Typical Characteristics**

$V_{CC}$  = 2.5V,  $V_{CCO}$  =1.2V GND = 0V,  $V_{IN}$  = 100mV,  $R_L$  = 50 $\Omega$  to 1.2V,  $T_A$  = 25°C, unless otherwise stated.

## **Functional Characteristics**

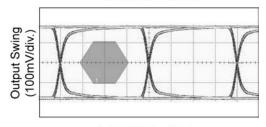

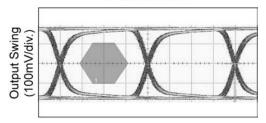

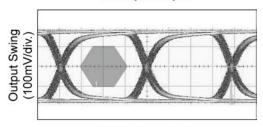

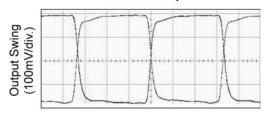

$V_{CC}$  = 2.5V,  $V_{CCO}$  =1.2V GND = 0V,  $V_{IN}$  = 400mV,  $R_L$  = 50 $\Omega$  to 1.2V, Data Pattern:  $2^{23}$ -1,  $T_A$  = 25°C, unless otherwise stated.

#### 1.25Gbps Output

TIME (200ps/div.)

#### 2.5Gbps Output

TIME (100ps/div.)

#### 3.2Gbps Output

TIME (80ps/div.)

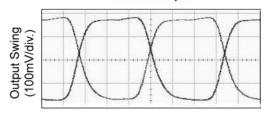

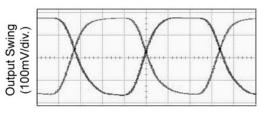

## **Functional Characteristics**

$V_{CC}$  = 2.5V,  $V_{CCO}$  =1.2V GND = 0V,  $V_{IN}$  = 400mV,  $R_L$  = 50 $\Omega$  to 1.2V,  $T_A$  = 25°C, unless otherwise stated.

#### 500MHz Output

TIME (300ps/div.)

#### 1.5GHz Output

TIME (100ps/div.)

#### 2GHz Output

TIME (75ps/div.)

# **Input and Output Stage**

Figure 2a. Simplified Differential Input Buffer

Figure 2b. Simplified CML Output Buffer

# **Single-Ended and Differential Swings**

Figure 3a. Single-Ended Swing

Figure 3b. Differential Swing

# **Input Interface Applications**

Figure 4a. CML Interface (DC-Coupled, 1.8V, 2.5V)

Figure 4b. CML Interface (DC-Coupled, 1.2V)

Figure 4c. CML Interface (AC-Coupled)

Figure 4d. LVPECL Interface (AC-Coupled)

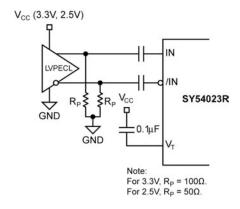

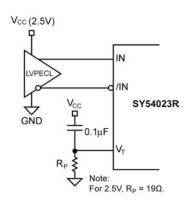

Figure 4e. LVPECL Interface (DC-Coupled)

Figure 4f. LVDS Interface

# **CML Output Termination**

Figure 5a. 1.2V or 1.8V CML DC-Coupled Termination

Figure 5b. 1.8V CML DC-Coupled Termination

Figure 5c. CML AC-Coupled Termination (V<sub>cco</sub> 1.8V only)

Figure 5d. CML AC-Coupled Termination (V<sub>cco</sub> 1.2V only)

# **Related Product and Support Documents**

| Part Number      | Function                                                           | Datasheet Link                                                            |

|------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------|

| SY54023AR        | 3.2Gbps Precision, 2x2 Crosspoint Switch with Internal Termination | http://www.micrel.com/page.do?page=/product-info/products/sy54023ar.shtml |

| HBW<br>Solutions | New Products and Termination Application Notes                     | http://www.micrel.com/page.do?page=/product-info/as/HBWsolutions.shtml    |

## **Package Information**

16-Pin MLF® (3mm x3mm) (MLF-16)

#### MICREL, INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL +1 (408) 944-0800 FAX +1 (408) 474-1000 WEB http://www.micrel.com

The information furnished by Micrel in this data sheet is believed to be accurate and reliable. However, no responsibility is assumed by Micrel for its use. Micrel reserves the right to change circuitry and specifications at any time without notification to the customer.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is a Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2008 Micrel, Incorporated.