# M62392P/FP

# 8-bit 12ch I<sup>2</sup>C BUS D/A Converter with Buffer Amplifiers

REJ03D0883-0300 Rev.3.00 Mar 25, 2008

### **Description**

The M62392P/FP is a CMOS 12 channels D/A converter with output buffer amplifiers. It can communicate with a microcontroller via few wiring thanks to the adoption of the two-line I<sup>2</sup>C BUS.

The output buffer amplifier employs AB class output with sinking and sourcing capability of more than 1.0 mA, and an output voltage range is nearly between ground and VrefU.

Maximum 8 ICs can be connected to a bus by using three chip-select pins, so that it is possible to handle up to 96 channels.

#### **Features**

- I<sup>2</sup>C BUS serial data method

- Wide output voltage range Nearly between ground and VrefU (0 to 5 V)

- High output current drive capability over  $\pm 1.0$  mA

- 2 setting voltage ranges by dual input pins for upper voltage references (VrefU1, U2)

#### **Application**

Conversion from digital data to analog control data for both consumer and industrial equipment.

Gain control and automatic adjustment of display-monitor or CTV.

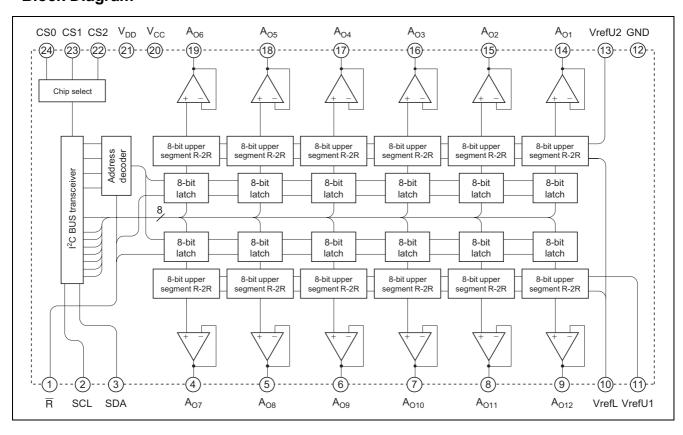

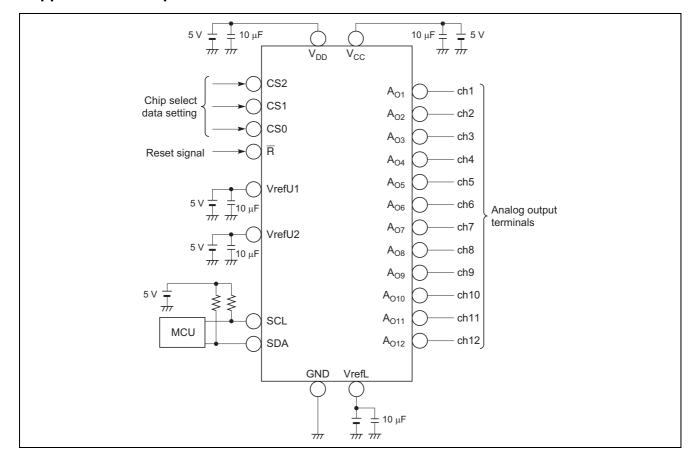

#### **Block Diagram**

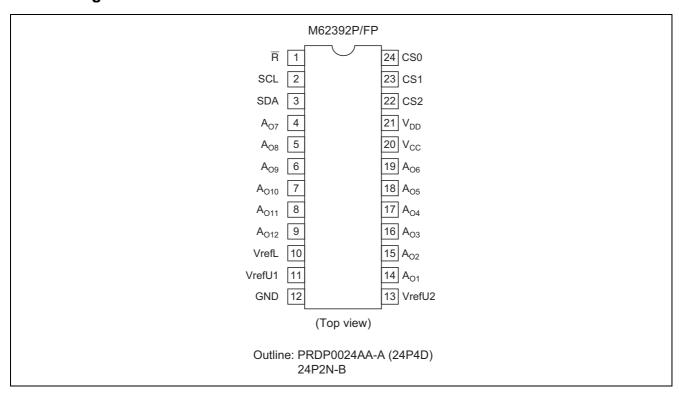

# **Pin Arrangement**

# **Pin Description**

| Pin No. | Pin Name        | Function                                                    |

|---------|-----------------|-------------------------------------------------------------|

| 3       | SDA             | Serial data input terminal                                  |

| 1       | R               | Reset signal input terminal                                 |

| 2       | SCL             | Serial clock input terminal                                 |

| 14      | Ao1             | 8-bit D/A converter output terminal                         |

| 15      | Ao2             | o-bit D/A converter output terminar                         |

| 16      | A02<br>A03      | -                                                           |

| 17      | A03             |                                                             |

|         |                 |                                                             |

| 18      | Ao5             |                                                             |

| 19      | Ao6             |                                                             |

| 4       | Ao7             |                                                             |

| 5       | Ao8             |                                                             |

| 6       | Ao9             |                                                             |

| 7       | Ao10            |                                                             |

| 8       | Ao11            |                                                             |

| 9       | Ao12            |                                                             |

| 20      | V <sub>CC</sub> | Analog power supply terminal                                |

| 21      | $V_{DD}$        | Digital power supply terminal                               |

| 12      | GND             | Analog and digital common GND                               |

| 10      | VrefL           | D/A converter low level reference voltage input terminal    |

| 11      | VrefU1          | D/A converter high level reference voltage input terminal 1 |

| 13      | VrefU2          | D/A converter high level reference voltage input terminal 2 |

| 22      | CS2             | Chip select data input terminal 2                           |

| 23      | CS1             | Chip select data input terminal 1                           |

| 24      | CS0             | Chip select data input terminal 0                           |

# **Absolute Maximum Ratings**

| Item                                       | Symbol          | Ratings                       | Unit |

|--------------------------------------------|-----------------|-------------------------------|------|

| Supply voltage                             | V <sub>CC</sub> | -0.3 to +7.0                  | V    |

| Supply voltage                             | $V_{DD}$        | -0.3 to +7.0                  | V    |

| D/A converter high level reference voltage | VrefU1, 2       | -0.3 to +7.0                  | V    |

| Input voltage                              | Vin             | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Output voltage                             | Vo              | -0.3 to V <sub>CC</sub> + 0.3 | V    |

| Power dissipation                          | Pd              | 465 (P) / 421 (FP)            | mW   |

| Operating temperature                      | Topr            | -20 to +85                    | °C   |

| Storage temperature                        | Tstg            | -40 to +125                   | °C   |

### **Electrical Characteristics**

### <Digital Part>

$(V_{CC},V_{DD},VrefU1,2=+5~V\pm10\%,V_{CC}\geq VrefU1,2,GND=VrefL=0~V,Ta=-20~to~+85^{\circ}C,unless~otherwise~noted.)$

|                          |                  |                     | Limits |                     |      |                          |

|--------------------------|------------------|---------------------|--------|---------------------|------|--------------------------|

| Item                     | Symbol           | Min                 | Тур    | Max                 | Unit | Conditions               |

| Supply voltage           | $V_{DD}$         | 4.5                 | 5.0    | 5.5                 | V    |                          |

| Supply current           | I <sub>DD</sub>  | _                   | _      | 1.0                 | mA   | CLK = 1 MHz operation,   |

|                          |                  |                     |        |                     |      | $I_{AO} = 0 \mu A$       |

| Input leak current       | I <sub>ILK</sub> | -10                 | _      | 10                  | μΑ   | $V_{IN} = 0$ to $V_{DD}$ |

| Output low voltage (SDA) | V <sub>OL</sub>  | _                   | _      | 0.4                 | V    | Isink = 3 mA             |

| Input low voltage        | V <sub>IL</sub>  | _                   | _      | 0.2 V <sub>DD</sub> | V    |                          |

| Input high voltage       | V <sub>IH</sub>  | 0.8 V <sub>DD</sub> | _      | _                   | V    |                          |

#### <Analog Part>

$(V_{CC},V_{DD},VrefU1,2=+5~V\pm10\%,V_{CC}\geq VrefU1,2,GND=VrefL=0~V,Ta=-20~to~+85^{\circ}C,unless~otherwise~noted.)$

|                           |                   |      | Limits |                |      |                                           |

|---------------------------|-------------------|------|--------|----------------|------|-------------------------------------------|

| Item                      | Symbol            | Min  | Тур    | Max            | Unit | Conditions                                |

| Supply voltage            | V <sub>CC</sub>   | 4.5  | 5.0    | 5.5            | V    |                                           |

| Supply current            | I <sub>CC</sub>   |      | 1.0    | 3.0            | mA   | CLK = 1 MHz operation, $I_{AO} = 0 \mu A$ |

| D/A converter high level  | IrefU             |      | 1.4    | 3.0            | mA   | VrefU = 5 V, VrefL = 0 V                  |

| reference voltage input   |                   |      |        |                |      | Data condition: at maximum current        |

| current                   |                   |      |        |                |      |                                           |

| D/A converter high level  | VrefU             | 3.5  | _      | $V_{CC}$       | V    | The output dose not necessarily be        |

| reference voltage range   |                   |      |        |                |      | the values within the reference           |

| D/A converter low level   | VrefL             | GND  | _      | $V_{CC} - 3.5$ | V    | voltage setting range.                    |

| reference voltage range   |                   |      |        |                |      |                                           |

| Buffer amplifier output   | $V_{AO}$          | 0.1  | _      | $V_{CC} - 0.1$ | V    | $I_{AO} = \pm 100 \mu A$                  |

| voltage range             |                   | 0.2  |        | $V_{CC} - 0.2$ | V    | $I_{AO} = \pm 500 \mu A$                  |

| Buffer amplifier output   | I <sub>AO</sub>   | -1.0 | _      | 1.0            | mA   | Upper side saturation voltage = 0.3 V     |

| drive range               |                   |      |        |                |      | Lower side saturation voltage = 0.2 V     |

| Differential nonlinearity | S <sub>DL</sub>   | -1.0 | _      | 1.0            | LSB  | VrefU = 4.79 V                            |

| Nonlinearity              | S <sub>L</sub>    | -1.5 | _      | 1.5            | LSB  | VrefL = 0.95 V                            |

| Zero code error           | S <sub>ZERO</sub> | -2.0 | _      | 2.0            | LSB  | V <sub>CC</sub> = 5.5 V (15 mV/LSB)       |

| Full scale error          | S <sub>FULL</sub> | -2.0 |        | 2.0            | LSB  | Without load $(I_{AO} = 0)$               |

| Output capacitive load    | Co                | _    |        | 0.1            | μF   |                                           |

| Buffer amplifier output   | Ro                | _    | 5.0    | _              | Ω    |                                           |

| impedance                 |                   |      |        |                |      |                                           |

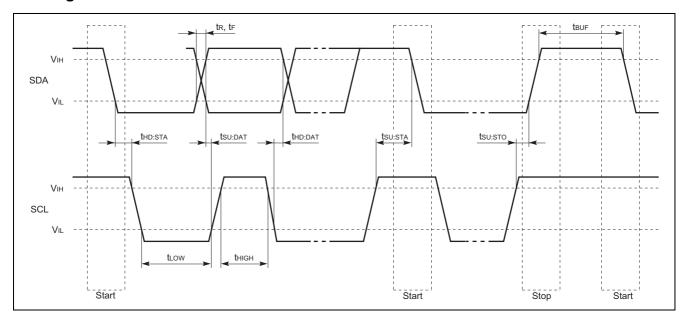

# I<sup>2</sup>C BUS Line Characteristics

|                                                               |                     | Norma |      |      |

|---------------------------------------------------------------|---------------------|-------|------|------|

| Item                                                          | Symbol              | Min   | Max  | Unit |

| SCL clock frequency                                           | f <sub>SCL</sub>    | 0     | 100  | kHz  |

| Time the bus must be free before a new transmission can start | t <sub>BUF</sub>    | 4.7   | _    | μS   |

| Hold time START condition.                                    | t <sub>HD:STA</sub> | 4.0   | _    | μS   |

| After this period, the first clock pulse is generated.        |                     |       |      |      |

| Low period of the clock                                       | t <sub>LOW</sub>    | 4.7   | _    | μS   |

| High period of the clock                                      | t <sub>HIGH</sub>   | 4.0   | _    | μS   |

| Setup time for START condition                                | t <sub>SU:STA</sub> | 4.7   | _    | μS   |

| (only relevant for a repeated START condition)                |                     |       |      |      |

| Hold time DATA                                                | t <sub>HD:DAT</sub> | 0     | _    | μS   |

| Setup time DATA                                               | t <sub>SU:DAT</sub> | 250   | _    | ns   |

| Rise time of both SDA and SCL lines                           | t <sub>R</sub>      | _     | 1000 | ns   |

| Fall time of both SDA and SCL lines                           | t <sub>F</sub>      | _     | 300  | ns   |

| Setup time for STOP condition                                 | t <sub>SU:STO</sub> | 4.0   | _    | μS   |

Note: Transmitter must internally provide at least a hold time to bridge the undefined region (300 ns Max) of the falling edge of SCL.

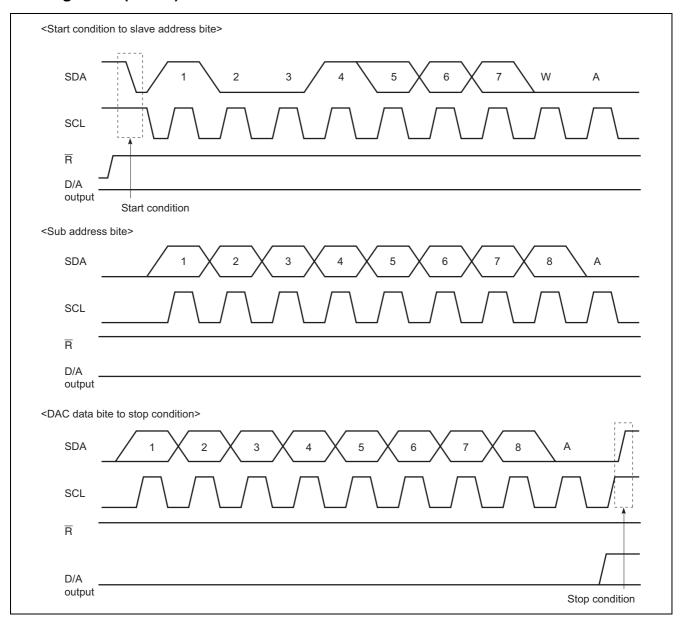

# **Timing Chart**

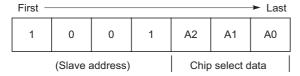

### I<sup>2</sup>C BUS Format

| I | STA | Slave address | W | Α | Sub address | Α | DAC data | Α | STP |

|---|-----|---------------|---|---|-------------|---|----------|---|-----|

## **Digital Data Format**

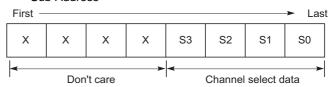

#### • Sub Address

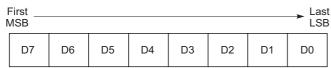

#### DAC Data

### (1) Chip Select Data

MSB LSB

| A2 | A1 | A0 | CS2 | CS1 | CS0 |

|----|----|----|-----|-----|-----|

| 0  | 0  | 0  | 0   | 0   | 0   |

| 0  | 0  | 1  | 0   | 0   | 1   |

| 0  | 1  | 0  | 0   | 1   | 0   |

| :  | :  | :  | :   | :   | :   |

| 1  | 1  | 1  | 1   | 1   | 1   |

Note: Lower 3 bits (A0, A1, A2) are a programmable address. This IC is accessed only when the lower 3 bits data of slave address coincide with the data of CS0 to CS2. (Refer to the upper table)

### (2) Channel Select Data

MSB

| LSB | SB |

|-----|----|

|-----|----|

| S3 | S2 | S1  | S0 | Channel Selection |

|----|----|-----|----|-------------------|

| 0  | 0  | 0   | 0  | Don't care        |

| 0  | 0  | 0   | 1  | ch1 selection     |

| 0  | 0  | 1   | 0  | ch2 selection     |

| :  | :  | • • | :  | :                 |

| 1  | 0  | 1   | 1  | ch11 selection    |

| 1  | 1  | 0   | 0  | ch12 selection    |

| 1  | 1  | 0   | 1  | Don't care        |

| :  | :  | :   | :  | :                 |

| 1  | 1  | 1   | 1  | Don't care        |

## (3) DAC Data

First \_\_\_\_\_\_ Last LSB

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | DAC Output                           |

|----|----|----|----|----|----|----|----|--------------------------------------|

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | (VrefU – VrefL) / 256 × 1 + VrefL    |

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | (VrefU – VrefL ) / 256 × 2 + VrefL   |

| 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | (VrefU – VrefL ) / 256 × 3 + VrefL   |

| 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | (VrefU - VrefL ) / 256 × 4 + VrefL   |

| :  | :  | :  | :  | :  | :  | :  | :  | :                                    |

| 1  | 1  | 1  | 1  | 1  | 1  | 1  | 0  | (VrefU - VrefL ) / 256 × 255 + VrefL |

| 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | VrefU                                |

# **Timing Chart (Model)**

- Start condition: With SCL at high, SDA line goes from high to low

- Stop condition: With SCL at high, SDA line goes from low to high (Under normal circumstances, SDA is changed when SCL is low)

- Acknowledge bit: The receiving IC has to pull down SDA line whenever receive slave data. (The transmitting IC releases the SDA line just then transmit 8-bit data.)

### **Precaution for Use**

M62392 have 5 terminals ( $V_{DD}$ ,  $V_{CC}$ , VrefU1, VrefU2, VrefL) for input constant voltage at use. If ripple or spike is input these terminals, accuracy of D/A conversion is down. So, when use this device, please connect capacitor among each terminal to GND for stable D/A conversion.

This IC's output amplifier has an advantage to capacitive load. So it's no problem at device action when connect capacitor (0.1  $\mu$ F Max) among output to GND for every noise eliminate.

Purchase of Renesas's  $I^2C$  components conveys a license under the Philips  $I^2C$  Patent Rights to use these components an  $I^2C$  system, provided that the system conforms to  $I^2C$  Standard Specification as defined by Philips.

### **Application Example**

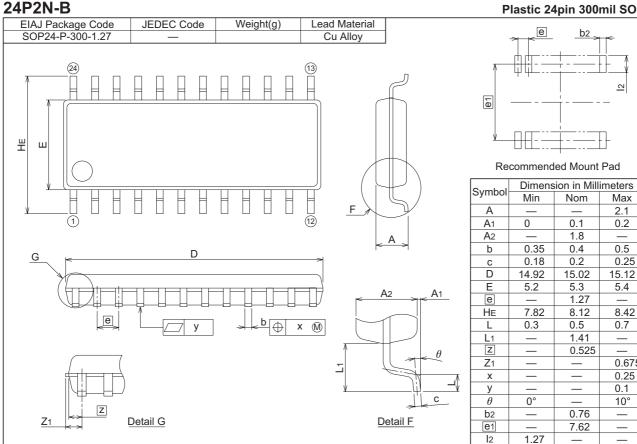

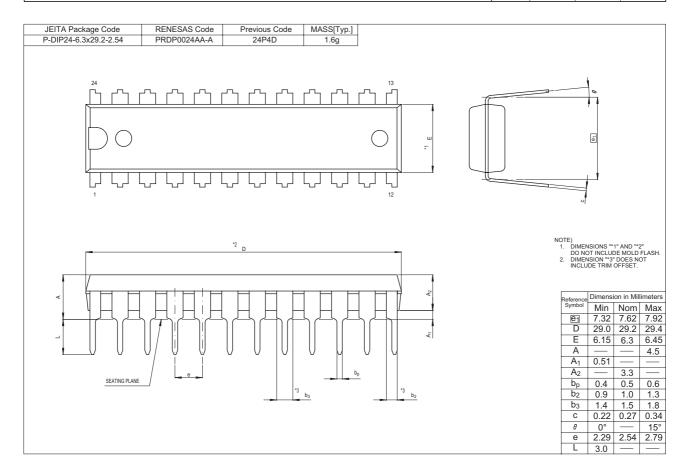

### **Package Dimensions**

Plastic 24pin 300mil SOP

Nom

0.1

1.8

0.4

0.2

15.02

5.3

1.27

8.12

0.5

1.41

0.76

7.62

0.525

2

Max 2.1

0.2

0.5

0.25

15.12

5.4

8.42

0.675 0.25 0.1

10°

0.7

#### Renesas Technology Corp. sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

- Renesas lechnology Corp. Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Notes:

1. This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warrantes or representations with respect to the accuracy or completeness of the information in this document nor grants any license to any intellectual property girbs to any other rights of representations with respect to the information in this document in this document of the purpose of the respect to the information in this document in the product data, diagrams, charts, programs, algorithms, and application circuit examples.

3. You should not use the products of the technology described in this document for the purpose of military use. When exporting the products or technology described herein, you should follow the applicable export control laws and regulations, and procedures required by such laws and regulations, and procedures required to change without any plan protein. Before purchasing or using any Renesas products listed in this document, in the development is satisfied. The procedure is such as the development of the dev

#### **RENESAS SALES OFFICES**

http://www.renesas.com

Refer to "http://www.renesas.com/en/network" for the latest and detailed information.

#### Renesas Technology America, Inc.

450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500, Fax: <1> (408) 382-7501

Renesas Technology Europe Limited

Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K.

Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900

Renesas Technology (Shanghai) Co., Ltd.

Unit 204, 205, AZIACenter, No.1233 Lujiazui Ring Rd, Pudong District, Shanghai, China 200120 Tel: <86> (21) 5877-1818, Fax: <86> (21) 6887-7858/7898

Renesas Technology Hong Kong Ltd.

7th Floor, North Tower, World Finance Centre, Harbour City, Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel: <852> 2265-6688, Fax: <852> 2377-3473

**Renesas Technology Taiwan Co., Ltd.** 10th Floor, No.99, Fushing North Road, Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 3518-3399

Renesas Technology Singapore Pte. Ltd.

1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65> 6213-0200, Fax: <65> 6278-8001

Renesas Technology Korea Co., Ltd. Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, Korea Tel: <82> (2) 796-3115, Fax: <82> (2) 796-2145

Renesas Technology Malaysia Sdn. Bhd

Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: <603> 7955-9390, Fax: <603> 7955-9510