# RENESAS

M62393P/FP

## 8-bit 8ch I<sup>2</sup>C BUS D/A Converter with Buffer Amplifiers

REJ03D0884-0300 Rev.3.00 Mar 25, 2008

#### Description

The M62393P/FP is an integrated circuit semiconductor of CMOS structure with 8 channels of built-in D/A converters with output buffer operational amplifiers. The input is 2-wires serial method is used for the transfer format of digital data to allow connection with a microcomputer with minimum wiring.

The output buffer operational amplifier employs AB class output circuit with sink and source drive capacity of 1.0 mA or more, and it operates in the whole voltage range from VrefU to ground. And because of connects maximum 8 pieces to 64 channels control.

#### Features

- Digital data transfer format: I<sup>2</sup>C BUS serial data method

- Output buffer operational amplifier It operates in the whole voltage range from VrefU (0 to 5 V) to ground.

- High output current drive capacity:  $\pm 1.0$  mA over

- Preparation two high level reference voltage terminal because there are two high level reference voltage terminal, it can set up two kinds differ voltage range.

### Application

Conversion from digital control data to analog control data for home-use and industrial equipment.

Signal gain control or automatic adjustment of display-monitor or CTV.

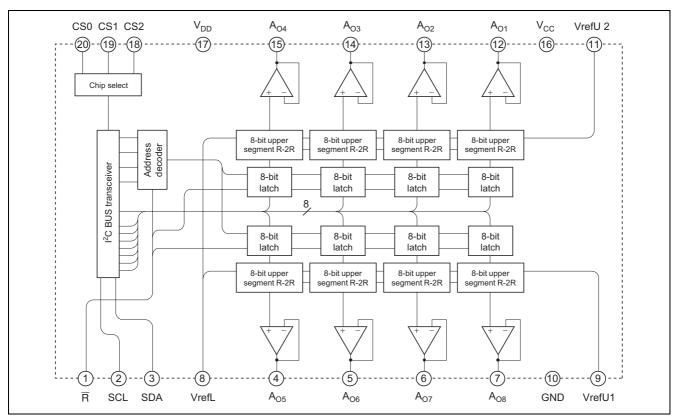

### **Block Diagram**

RENESAS

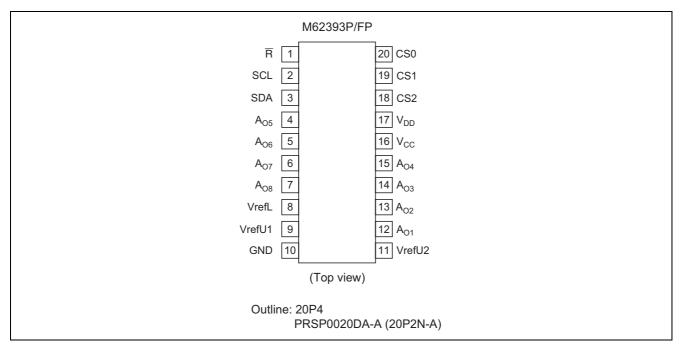

### **Pin Arrangement**

#### **Pin Description**

| Pin No. | Pin Name        | Function                                                    |

|---------|-----------------|-------------------------------------------------------------|

| 3       | SDA             | Serial data input terminal                                  |

| 1       | R               | Reset signal input terminal                                 |

| 2       | SCL             | Serial clock input terminal                                 |

| 12      | Ao1             | 8-bit D/A converter output terminal                         |

| 13      | Ao2             |                                                             |

| 14      | Ao3             |                                                             |

| 15      | Ao4             |                                                             |

| 4       | Ao5             |                                                             |

| 5       | Ao6             |                                                             |

| 6       | Ao7             |                                                             |

| 7       | Ao8             |                                                             |

| 16      | V <sub>cc</sub> | Analog power supply terminal                                |

| 17      | V <sub>DD</sub> | Digital power supply terminal                               |

| 10      | GND             | Analog and digital common GND                               |

| 8       | VrefL           | D/A converter low level reference voltage input terminal    |

| 9       | VrefU1          | D/A converter high level reference voltage input terminal 1 |

| 11      | VrefU2          | D/A converter high level reference voltage input terminal 2 |

| 18      | CS2             | Chip select data input terminal 2                           |

| 19      | CS1             | Chip select data input terminal 1                           |

| 20      | CS0             | Chip select data input terminal 0                           |

### **Absolute Maximum Ratings**

| Item                                       | Symbol          | Ratings                       | Unit |

|--------------------------------------------|-----------------|-------------------------------|------|

| Supply voltage                             | V <sub>CC</sub> | -0.3 to +7.0                  | V    |

| Supply voltage                             | V <sub>DD</sub> | -0.3 to +7.0                  | V    |

| D/A converter high level reference voltage | VrefU1, 2       | -0.3 to +7.0                  | V    |

| Input voltage                              | V <sub>IN</sub> | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Output voltage                             | Vo              | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Power dissipation                          | Pd              | 990 (P) / 590 (FP)            | mW   |

| Operating temperature                      | Topr            | -20 to +85                    | °C   |

| Storage temperature                        | Tstg            | -40 to +125                   | °C   |

#### **Electrical Characteristics**

#### <Digital Part>

```

(V_{CC}, V_{DD}, VrefU1, 2 = +5 V \pm 10\%, V_{CC} \ge VrefU1, 2, GND = VrefL = 0 V, Ta = -20 to +85^{\circ}C, unless otherwise noted.)

```

|                          |                  | Limits              |     |              |      |                          |

|--------------------------|------------------|---------------------|-----|--------------|------|--------------------------|

| ltem                     | Symbol           | Min                 | Тур | Max          | Unit | Conditions               |

| Supply voltage           | V <sub>DD</sub>  | 4.5                 | 5.0 | 5.5          | V    |                          |

| Supply current           | I <sub>DD</sub>  | —                   | —   | 1.0          | mA   | CLK = 1 MHz operation,   |

|                          |                  |                     |     |              |      | $I_{AO} = 0 \ \mu A$     |

| Output low voltage (SDA) | V <sub>OL</sub>  |                     | —   | 0.4          | V    | lsink = 3 mA             |

| Input leak current       | I <sub>ILK</sub> | -10                 | —   | 10           | μΑ   | $V_{IN} = 0$ to $V_{CC}$ |

| Input low voltage        | VIL              |                     | —   | $0.2 V_{CC}$ | V    |                          |

| Input high voltage       | VIH              | 0.8 V <sub>CC</sub> | _   |              | V    |                          |

#### <Analog Part>

$(V_{CC}, V_{DD}, VrefU1, 2 = +5 V \pm 10\%, V_{CC} \ge VrefU1, 2, GND = VrefL = 0 V, Ta = -20 to +85^{\circ}C, unless otherwise noted.)$

|                           |                   | Limits |     |                       |      |                                                 |

|---------------------------|-------------------|--------|-----|-----------------------|------|-------------------------------------------------|

| Item                      | Symbol            | Min    | Тур | Max                   | Unit | Conditions                                      |

| Supply voltage            | V <sub>CC</sub>   | 4.5    | 5.0 | 5.5                   | V    |                                                 |

| Supply current            | I <sub>CC</sub>   | -      | 1.6 | 3.2                   | mA   | CLK = 1 MHz operation, $I_{AO} = 0 \ \mu A$     |

| D/A converter high level  | IrefU             | -      | 1.0 | 2.0                   | mA   | VrefU = 5 V, VrefL = 0 V                        |

| reference voltage input   |                   |        |     |                       |      | Data condition: at maximum current              |

| current                   |                   |        |     |                       |      |                                                 |

| D/A converter high level  | VrefU             | 3.5    | —   | V <sub>cc</sub>       | V    | The output dose not necessarily be              |

| reference voltage range   |                   |        |     |                       |      | the values within the reference                 |

| D/A converter low level   | VrefL             | GND    | —   | $V_{CC} - 3.5$        | V    | voltage setting range.                          |

| reference voltage range   |                   |        |     |                       |      |                                                 |

| Buffer amplifier output   | V <sub>AO</sub>   | 0.1    | —   | V <sub>CC</sub> – 0.1 | V    | $I_{AO} = \pm 100 \ \mu A$                      |

| voltage range             |                   | 0.2    | _   | $V_{CC}-0.2$          | V    | $I_{AO} = \pm 500 \ \mu A$                      |

| Buffer amplifier output   | I <sub>AO</sub>   | -1.0   | —   | 1.0                   | mA   | Upper side saturation voltage = $0.3 \text{ V}$ |

| current range             |                   |        |     |                       |      | Lower side saturation voltage = 0.2 V           |

| Differential nonlinearity | S <sub>DL</sub>   | -1.0   | —   | 1.0                   | LSB  | VrefU = 4.79 V                                  |

| Nonlinearity              | SL                | -1.5   | _   | 1.5                   | LSB  | VrefL = 0.95 V                                  |

| Zero code error           | SZERO             | -2.0   | _   | 2.0                   | LSB  | $V_{CC} = 5.5 \text{ V} (15 \text{ mV/LSB})$    |

| Full scale error          | S <sub>FULL</sub> | -2.0   | —   | 2.0                   | LSB  | Without load $(I_{AO} = 0)$                     |

| Output capacitive load    | Co                | -      | —   | 0.1                   | μF   |                                                 |

| Buffer amplifier output   | Ro                | —      | 5.0 | —                     | Ω    |                                                 |

| impedance                 |                   |        |     |                       |      |                                                 |

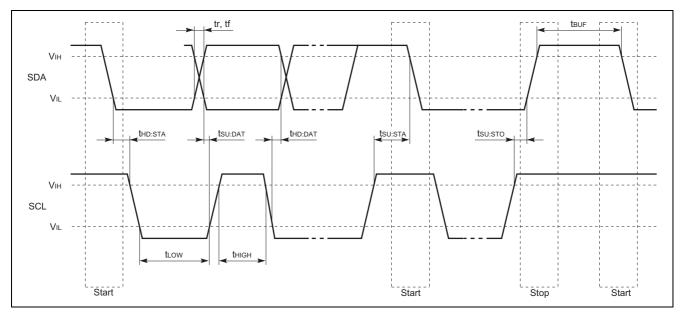

### I<sup>2</sup>C BUS Line Characteristics

|                                                                                      |                       | Norma | I Mode | High Spe | ed Mode |      |

|--------------------------------------------------------------------------------------|-----------------------|-------|--------|----------|---------|------|

| Item                                                                                 | Symbol                | Min   | Max    | Min      | Max     | Unit |

| SCL clock frequency                                                                  | f <sub>SCL</sub>      | 0     | 100    | 0        | 400     | kHz  |

| Time the bus must be free before a new transmission can start                        | t <sub>BUF</sub>      | 4.7   | —      | 1.3      | —       | μs   |

| Hold time start condition. After this period.<br>The first clock pulse is generated. | t <sub>HD : STA</sub> | 4.0   | _      | 0.6      | _       | μs   |

| Low period of the clock                                                              | t <sub>LOW</sub>      | 4.7   | _      | 1.3      | _       | μS   |

| High period of the clock                                                             | t <sub>HIGH</sub>     | 4.0   | —      | 0.6      | —       | μs   |

| Setup time for start condition (only relevant for a repeated start condition)        | t <sub>SU : STA</sub> | 4.7   | —      | 4.7      | —       | μs   |

| Hold time data                                                                       | t <sub>HD : DAT</sub> | 0     | —      | 0        | 0.9     | μs   |

| Setup time data                                                                      | t <sub>SU : DAT</sub> | 250   | —      | 100      | —       | ns   |

| Rise time of both SDA and SCL lines                                                  | t <sub>R</sub>        | _     | 1000   | 20       | 300     | ns   |

| Fall time of both SDA and SCL lines                                                  | t <sub>F</sub>        | _     | 300    | 20       | 300     | ns   |

| Setup time for stop condition                                                        | t <sub>SU:STO</sub>   | 4.0   | _      | 0.6      | _       | μS   |

Note: Transmitter must internally at reset a hold time to bridge the undefined region (300 ns Max) of the falling edge of SCL.

### **Timing Chart**

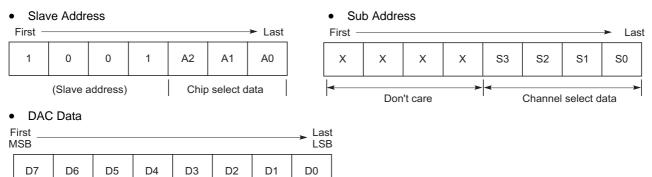

### I<sup>2</sup>C BUS Format

| STA Slave address W A | Sub address A | A DAC data | А | STP |

|-----------------------|---------------|------------|---|-----|

### **Digital Data Format**

#### (1) Chip Select Data

| MSB |    | LSB | LSB |     |     |  |  |  |

|-----|----|-----|-----|-----|-----|--|--|--|

| A2  | A1 | A0  | CS2 | CS1 | CS0 |  |  |  |

| 0   | 0  | 0   | 0   | 0   | 0   |  |  |  |

| 0   | 0  | 1   | 0   | 0   | 1   |  |  |  |

| 0   | 1  | 0   | 0   | 1   | 0   |  |  |  |

| :   | :  | :   | :   | :   | :   |  |  |  |

| 1   | 1  | 1   | 1   | 1   | 1   |  |  |  |

#### (2) Channel Select Data

| MSB |    |    | LSB |                   |

|-----|----|----|-----|-------------------|

| S3  | S2 | S1 | S0  | Channel Selection |

| 0   | 0  | 0  | 0   | Don't care        |

| 0   | 0  | 0  | 1   | ch1 selection     |

| 0   | 0  | 1  | 0   | ch2 selection     |

| :   | :  | :  | :   | :                 |

| 0   | 1  | 1  | 1   | ch7 selection     |

| 1   | 0  | 0  | 0   | ch8 selection     |

| 1   | 0  | 0  | 1   | Don't care        |

| :   | :  | :  | :   | :                 |

| 1   | 1  | 1  | 1   | Don't care        |

#### (3) DAC Data

| First<br>MSB |    |    |    |    |    |    | → Last<br>LSB |                                             |

|--------------|----|----|----|----|----|----|---------------|---------------------------------------------|

| D7           | D6 | D5 | D4 | D3 | D2 | D1 | D0            | DAC Output                                  |

| 0            | 0  | 0  | 0  | 0  | 0  | 0  | 0             | (VrefU – VrefL ) / 256 × 1 + VrefL          |

| 0            | 0  | 0  | 0  | 0  | 0  | 0  | 1             | (VrefU – VrefL ) / 256 $\times$ 2 + VrefL   |

| 0            | 0  | 0  | 0  | 0  | 0  | 1  | 0             | (VrefU – VrefL ) / 256 $\times$ 3 + VrefL   |

| 0            | 0  | 0  | 0  | 0  | 0  | 1  | 1             | (VrefU – VrefL ) / 256 $\times$ 4 + VrefL   |

| :            | :  | :  | :  | :  | :  | :  | :             | :                                           |

| 1            | 1  | 1  | 1  | 1  | 1  | 1  | 0             | (VrefU – VrefL ) / 256 $\times$ 255 + VrefL |

| 1            | 1  | 1  | 1  | 1  | 1  | 1  | 1             | VrefU                                       |

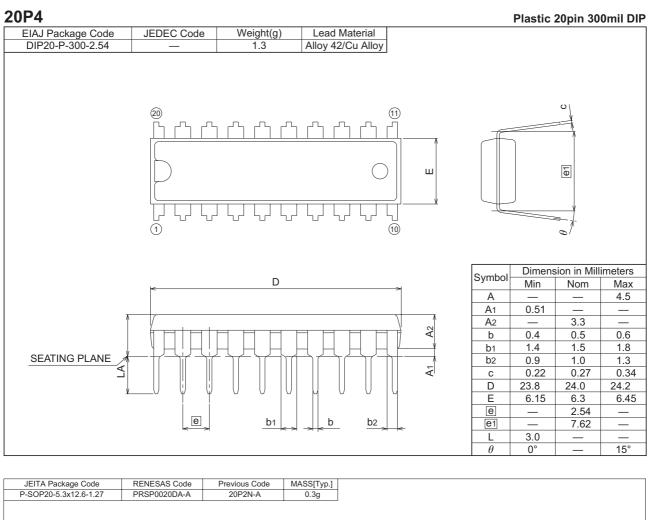

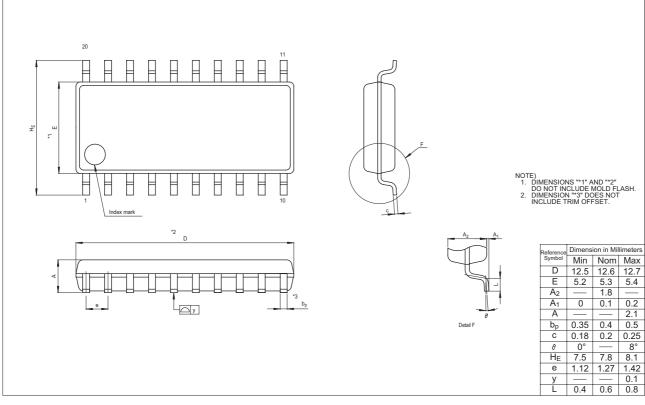

#### **Package Dimensions**

RENESAS

#### RenesasTechnology Corp. sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

- Benesas lechnology Corp. sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

Pines

This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information in this document.

But not infinited to, product data. diagrams, charts, programs, algorithms, and application scuch as the development of weapons of mass and regulations, and proceedures required by such laws and regulation.

All information in this document, included in this document for the purpose of military application scuch as the development of weapons of mass and regulations, and proceedures required by such laws and regulations.

All information included in this document such as product data, diagrams, charts, programs, algorithms, and application carcuit examples, is current as of the date this document, when exporting the products or the technology described herein, you should follow the applicable export control laws and regulations.

Renesas has used reasonable care in compiling the information in this document, but Renesas assumes no liability whatsoever for any damages incurred as a set exception of protein ting from the internation included in this document. Dut Renesas asproaces are not exception of protein ting from the protein ting from the internation included in this document.

When using or otherwise requires the failue or mating inclusion incurred and this document. Dut Renesas asproaces are area consulting what how any particular in the date this document.

When using or otherwise requires the failue or mating inclusion in the set of the state of the total system before deciding about the applicability of otherwise in systems the failue or mating inclusion in the indication. Renesas products are not designed phase to the set of any parti

#### **RENESAS SALES OFFICES**

Refer to "http://www.renesas.com/en/network" for the latest and detailed information.

#### Renesas Technology America, Inc.

450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500, Fax: <1> (408) 382-7501

Renesas Technology Europe Limited Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K. Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900

Renesas Technology (Shanghai) Co., Ltd. Unit 204, 205, AZIACenter, No.1233 Lujiazui Ring Rd, Pudong District, Shanghai, China 200120 Tel: <86> (21) 5877-1818, Fax: <86> (21) 6887-7858/7898

Renesas Technology Hong Kong Ltd. 7th Floor, North Tower, World Finance Centre, Harbour City, Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel: <852> 2265-6688, Fax: <852> 2377-3473

Renesas Technology Taiwan Co., Ltd. 10th Floor, No.99, Fushing North Road, Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 3518-3399

#### Renesas Technology Singapore Pte. Ltd.

1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65> 6213-0200, Fax: <65> 6278-8001

Renesas Technology Korea Co., Ltd. Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, Korea Tel: <82> (2) 796-3115, Fax: <82> (2) 796-2145

Renesas Technology Malaysia Sdn. Bhd Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: <603> 7955-9390, Fax: <603> 7955-9510

http://www.renesas.com