# **AK7740ET**

# 24bit 2ch ADC + 24bit 4ch DAC with Audio DSP

## 1. General Description

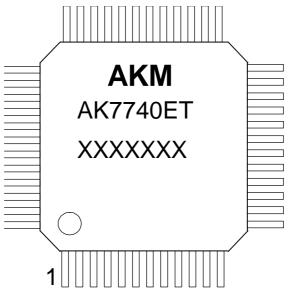

The AK7740 is a highly integrated audio processing IC, including four 24-bit output D/A channels, a stereo 24-bit input A/D, and an audio DSP. High quality analog output performance is provided by the quad DAC with 97dB dynamic range, and the stereo ADC with 98dB dynamic range. The converters support sampling frequencies from 32kHz to 48kHz. This device includes 72kbits of SRAM audio delay that is suitable for simulated sound fields. The DSP is optimized for audio signal processing. The design allows up to 512 execution lines per audio sample cycle, with multiple functions per line. The AK7740 is ideal for sound field control applications, including echo, 3D, parametric equalization, and speaker compensation. It is housed in a 48-lead LQFP package.

### 2. Features

#### DSP:

Word length: 24-bit (Data RAM)

Instruction cycle time: 40ns (512fs, fs=48kHz)

Multiplier:  $24 \times 16 \rightarrow 40$ -bit

- Divider:  $24 / 24 \rightarrow 16$ -bit or 24-bit

- ALU: 34-bit arithmetic operation (overflow margin: 4-bits)

24-bit arithmetic and logic operation

Shift+Register: 1, 2, 3, 4, 6, 8 and 15 bits shifted left

1, 2, 3, 4, 8, 14 and 15 bits shifted right

- Other numbers in parentheses are restricted. Provided with indirect shift function

Program RAM: 512 x 32-bit

Coefficient RAM: 512 x 16-bit

Data RAM: 256 x 24-bit

Offset RAM: 48 x 13-bit

- (6144 x 12-bit / 3072 x 24-bit / 4096 x 12-bit + 1024 x 24-bit )

Internal Memory: 72kbit SRAM

Sampling frequency: 32kHz to 48kHz

Serial interface port for micro-controller

Master clock: 512fsMaster/Slave operation

- Serial signal input port (2 to 4 ch): 16/20/24-bit: Output port (2 ch): 24-bit

#### **ADC: 2 channels**

- 24-bit 64x over-sampling delta sigma

- DR, S/N: 98dBA (full-differential Input)

S/(N+D): 89dB

Digital HPF (fc = 1Hz)

Single-ended or full-differential Input

#### DAC: 4 channels

- 24-bit 128x over-sampling advanced multi-bit

DR, S/N: 97dBAS/(N+D): 89dB

- Single ended or differential output

#### **Input Selector**

- 1 full-differential and 4 single-ended Input

## Other

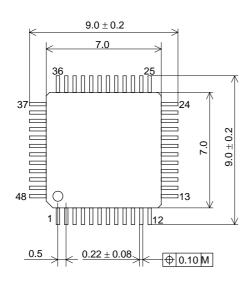

- Power supply:  $+3.3V\pm10\%$

Operating temperature range: -10°C~70°C

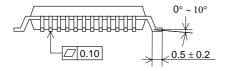

- Package: 48pin LQFP (0.5mm pitch)

<Pre-E-01> - 1 - 2006/10

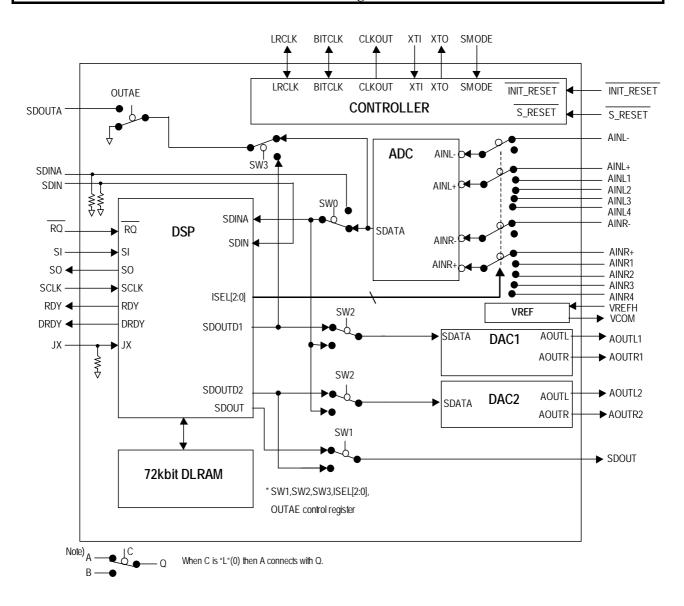

## 3. Block diagram

This block diagram is a simplified illustration of the AK7740; it is not a circuit diagram.

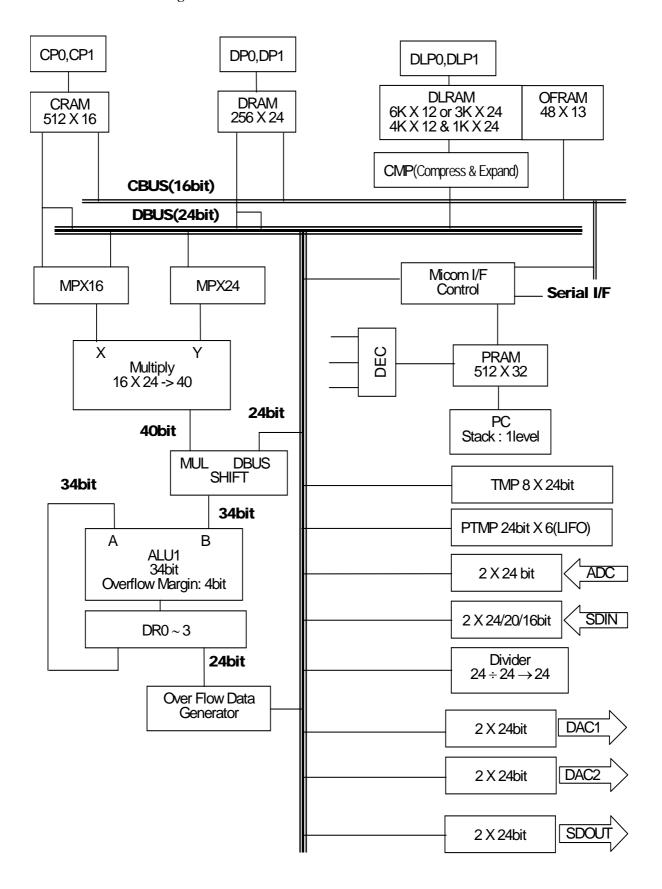

# ♦ AK7740 DSP Block diagram

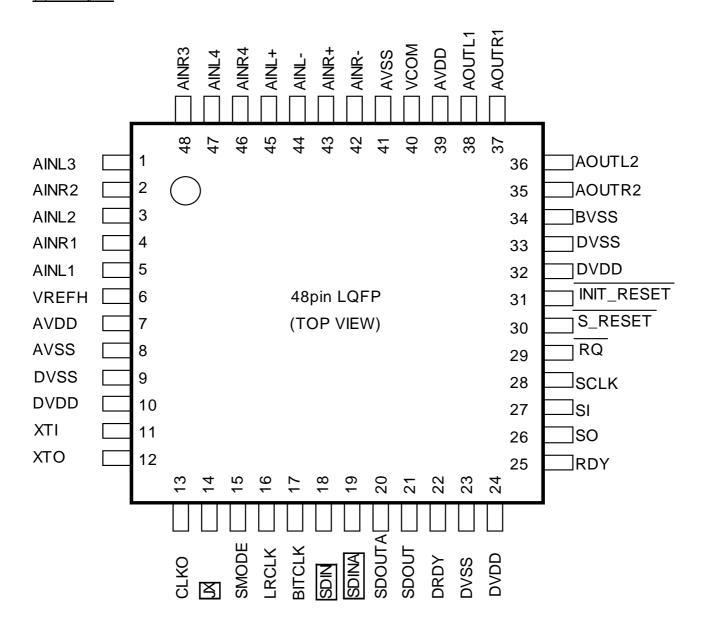

# 4. Description of Input/Output Pins

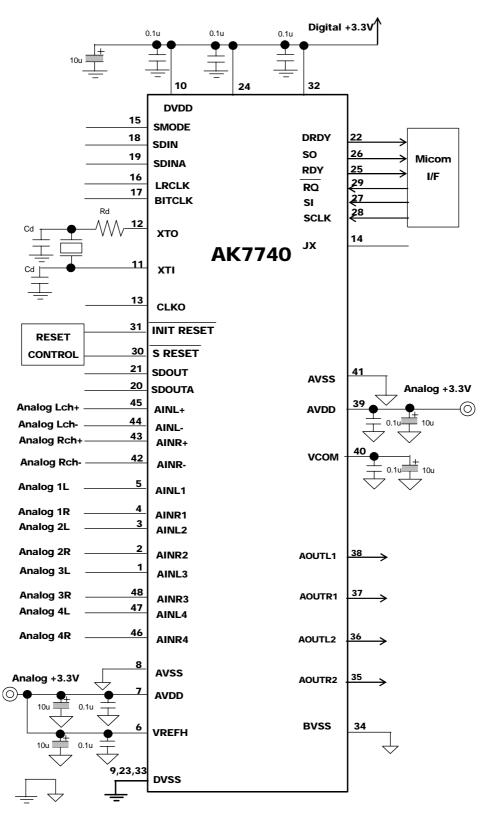

## (1) Pin layout

Note) [X], SDIN and SDINA are Pull-down pins

# (2) Pin function

| Pin No. | Pin name                                | I/O | Function                                                                                | Classification    |

|---------|-----------------------------------------|-----|-----------------------------------------------------------------------------------------|-------------------|

| 1       | AINL3                                   | I   | ADC single-ended analog Lch input pin 3                                                 | Analog section    |

| 2       | AINR2                                   | I   | ADC single-ended analog Rch input pin 2                                                 |                   |

| 3       | AINL2                                   | I   | ADC single-ended analog Lch input pin 2                                                 |                   |

| 4       | AINR1                                   | I   | ADC single-ended analog Rch input pin 1                                                 |                   |

| 5       | AINL1                                   | I   | ADC single-ended analog Lch input pin 1                                                 |                   |

| 6       | VREFH                                   | I   | Analog reference voltage input                                                          |                   |

|         |                                         |     | Connect to AVDD (pin 7), and bypass with 0.1uF and                                      |                   |

|         |                                         |     | 10uF capacitors between this pin and AVSS.                                              |                   |

| 7       | AVDD                                    |     | Analog power supply 3.3V typical                                                        | Analog            |

| 8       | AVSS                                    | -   | Analog ground                                                                           | Power Supply      |

| 9       | DVSS                                    | -   | Digital ground                                                                          | Digital           |

| 10      | DVDD                                    | _   | Digital power supply 3.3V typical                                                       | Power Supply      |

|         |                                         |     | Master clock input                                                                      | System clock      |

| 11      | XTI                                     | I   | Connect a crystal oscillator between this pin and the XTO pin,                          |                   |

|         |                                         |     | or input an external CMOS clock signal to the XTI pin.                                  |                   |

|         |                                         |     | Crystal oscillator output                                                               |                   |

| 12      | XTO                                     | О   | When a crystal oscillator is used, connect between XTI and XTO.                         |                   |

|         |                                         |     | When an external clock is used, keep this pin open                                      |                   |

|         | AT TTA                                  |     | Clock output                                                                            | System clock      |

| 13      | CLKO                                    | O   | Outputs the XTI clock.                                                                  |                   |

| 1.4     | TT7                                     |     | Allows the output to be set to "L" by control register setting.                         | G 133             |

| 14      | JX                                      |     | External condition jump (pulldown)                                                      | Condition input   |

| 1.5     | CMODE                                   |     | Slave/master mode selector                                                              | Control           |

| 15      | SMODE                                   | I   | Sets LRCLK and BITCLK to input or output mode. SMODE="L": Slave mode (clock input mode) |                   |

|         |                                         |     | SMODE= L': Slave mode (clock input mode) SMODE="H": Master mode (clock output mode)     |                   |

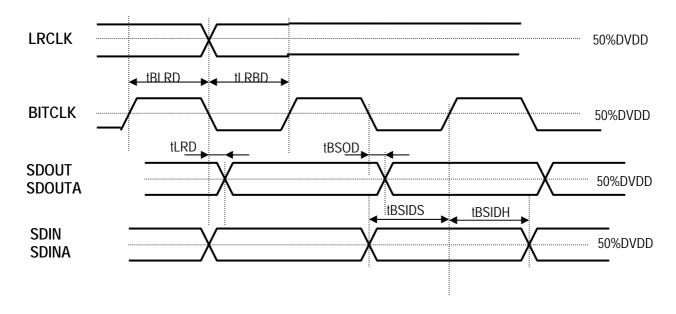

|         |                                         |     | LR channel select clock                                                                 | System clock      |

| 16      | LRCLK                                   |     | SMODE="L": Slave mode: Inputs the fs clock                                              | System clock      |

| 10      | LKCLK                                   | 1/0 | SMODE="H": Master mode: Outputs the fs clock                                            |                   |

|         |                                         |     | Serial bit clock                                                                        |                   |

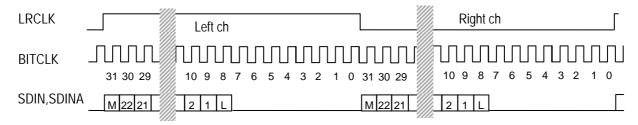

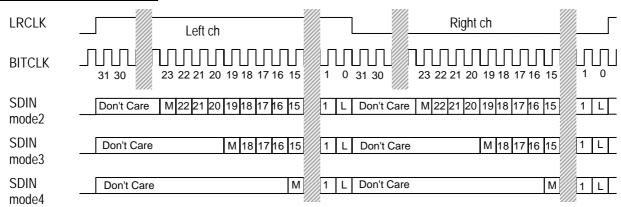

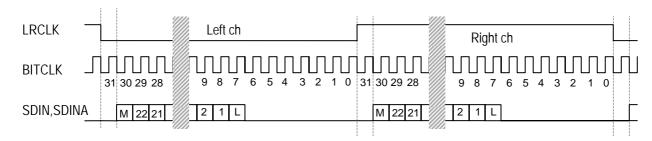

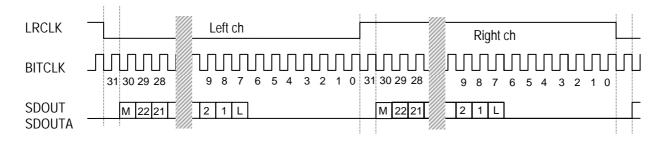

| 17      | BITCLK                                  |     | SMODE="L": Slave mode: Inputs 64 fs or 48 fs clocks                                     |                   |

| 1 /     | DITCLK                                  | 1,0 | SMODE="H": Master mode: Outputs 64 fs clocks                                            |                   |

|         |                                         |     | DSP serial data input (Pulldown)                                                        | Digital section   |

| 18      | SDIN                                    |     | Compatible with MSB/LSB justified 24, 20 and 16 bits.                                   | Serial input data |

| - 0     | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |     |                                                                                         |                   |

|         |                                         |     | DSP serial data input (Pulldown)                                                        |                   |

| 19      | SDINA                                   |     | When using the ADC, leave open or connect to DVSS.                                      |                   |

|         |                                         |     | Compatible with MSB justified 24 bits.                                                  |                   |

| Pin No. | Pin name   | I/O | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Classification     |

|---------|------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

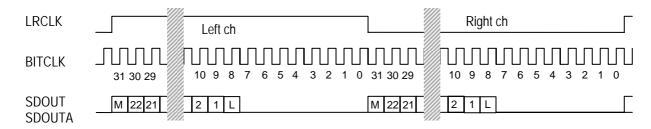

| 20      | SDOUTA     | Ο   | DSP serial data output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Digital section    |

|         |            |     | Outputs MSB justified 24-bit data selected from ADC or SDOUTD1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Serial output data |

|         |            |     | by control register setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                    |

| 21      | SDOUT      | Ο   | DSP serial data output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                    |

|         |            |     | Outputs MSB justified 24-bit data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                    |

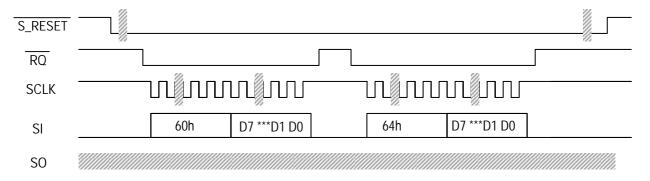

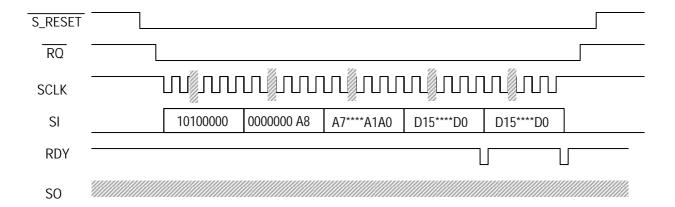

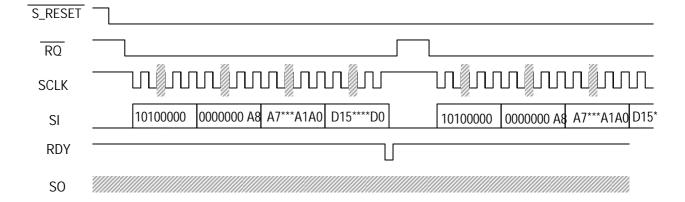

| 22      | DRDY       | Ο   | Output data ready pin for microcontroller interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Microcontroller    |

|         |            |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | interface          |

| 23      | DVSS       |     | Digital ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Power supply       |

| 24      | DVDD       |     | Digital power supply 3.3V typical                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                    |

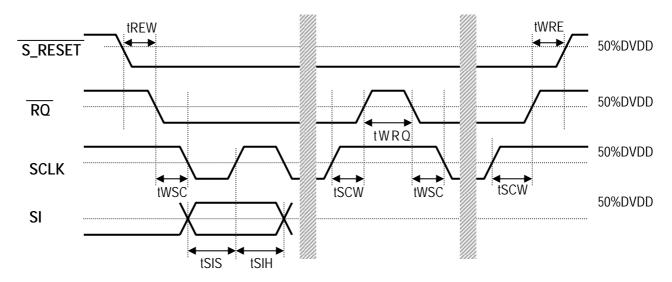

| 25      | RDY        |     | Data write ready output for microcontroller interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Microcontroller    |

| 26      | SO         | О   | Serial data output for microcontroller interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | interface          |

|         |            |     | Microcontroller interface serial data input and serial data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                    |

| 27      | SI         | I   | output control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                    |

|         |            |     | When SI does not use, leave SI="L"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4                  |

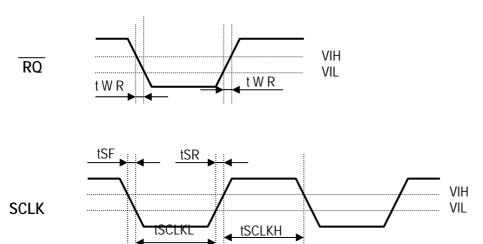

| 20      | 0.01.17    |     | Microcontroller interface serial data clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                    |

| 28      | SCLK       | I   | When SCLK is not used, leave SCLK="H"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                    |

|         |            |     | Marian Andrews | -                  |

| 20      | RQ         | т   | Microcontroller interface writes request pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    |

| 29      |            | Ι   | RQ ="L": Microcontroller interface enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                    |

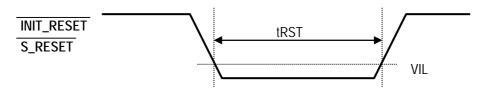

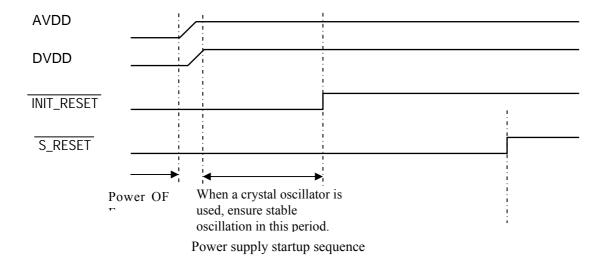

| 30      | S_RESET    | I   | System Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Reset              |

|         | S_KESE I   |     | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4                  |

| 31      | INIT_RESET | I   | Reset (for initialization)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                    |

|         |            |     | Input "L" to initialize the AK7740 at power-on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | D .                |

| 32      | DVDD       |     | Digital power supply 3.3V typical                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Power supply       |

| 33      | DVSS       |     | Digital ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | D .                |

| 34      | BVSS       |     | Substrate ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Power supply       |

| 35      | AOUTR2     |     | DAC2 Rch analog output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Analog section     |

| 36      | AOUTL2     |     | DAC2 Lch analog output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4                  |

| 37      | AOUTR1     |     | DAC1 Rch analog output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | _                  |

| 38      | AOUTL1     |     | DAC1 Lch analog output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                    |

| 39      | AVDD       |     | Analog power supply 3.3V typical                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Power supply       |

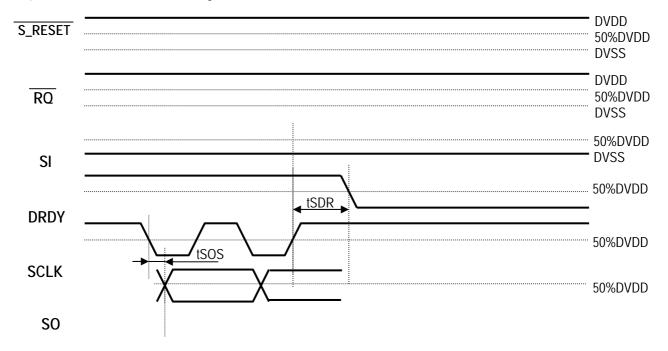

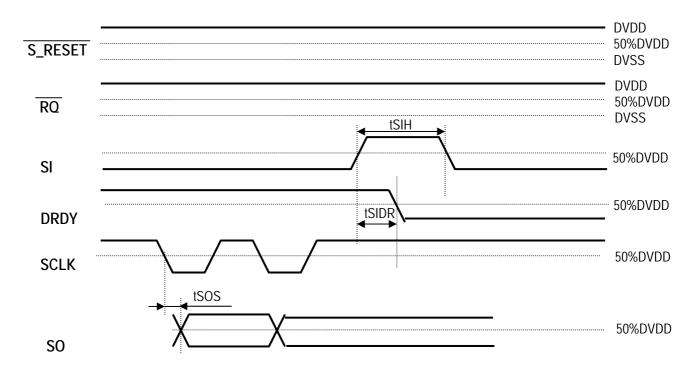

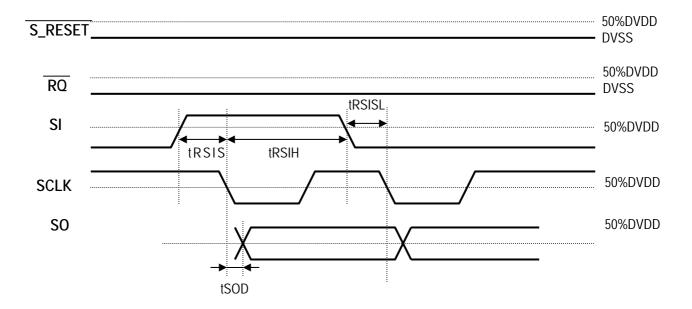

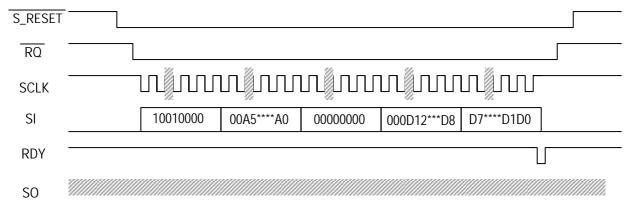

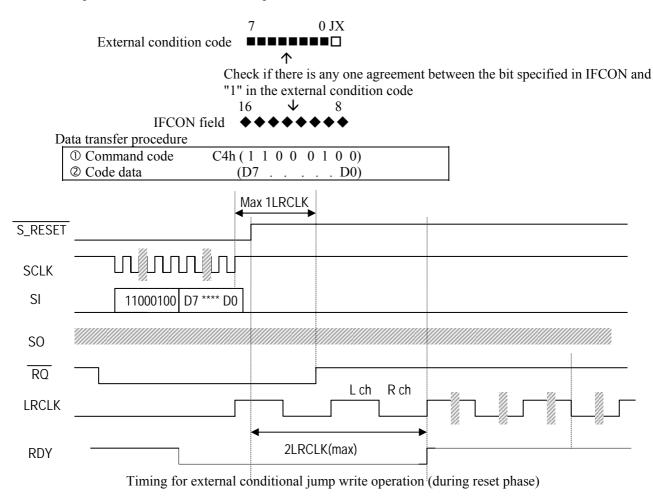

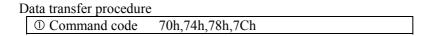

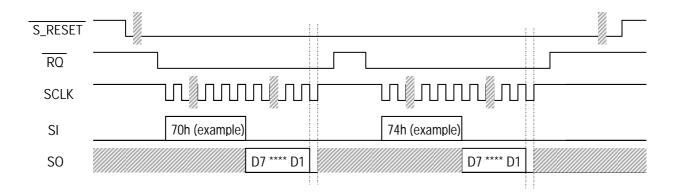

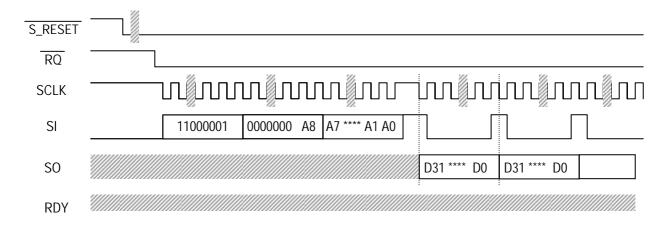

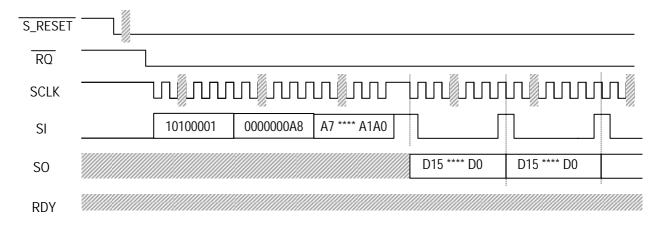

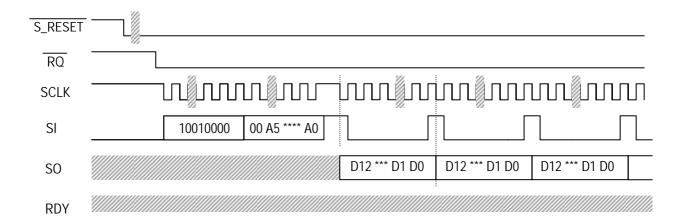

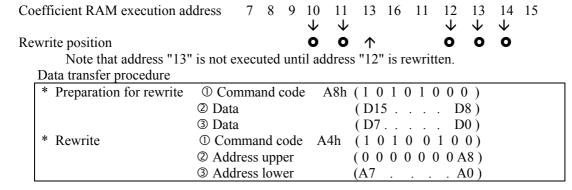

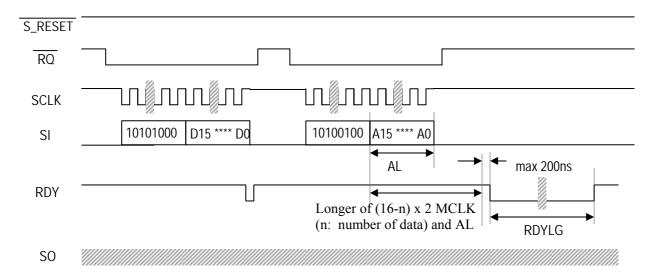

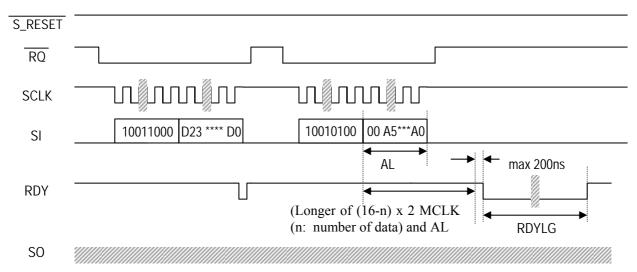

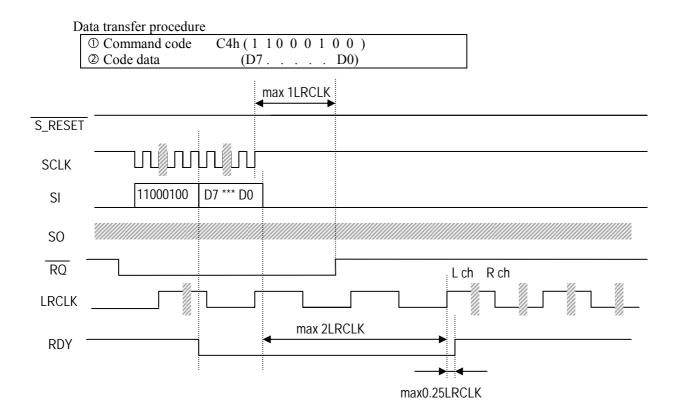

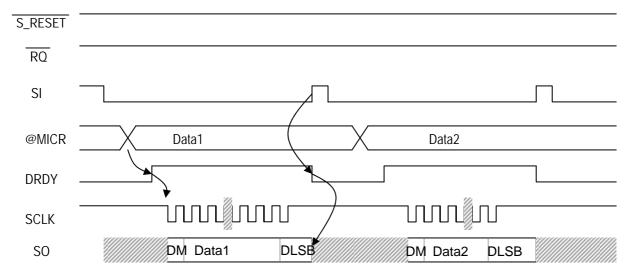

| 40      | VCOM       | О   | Common voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Analog section     |