M65667SP

Picture-in-Picture Signal Processing

REJ03F0186-0201 Rev.2.01 Mar 31, 2008

### Description

The M65667SP is a NTSC PIP (Picture in Picture) signal processing LSI, whose sub and main-picture inputs are composite and Y/C separated signals, respectively. The built-in field memory (96 Kbit RAM), V-chip data slicer and analog circuitries lead the PIP system low cost and small size.

### Features

- Built-in 96 Kbit field memory (sub-picture data storage)

- Internal V-chip data slicer (for sub-picture)

- Pin compatible with M65617SP

- Vertical filter for sub-picture (Y signal)

- Single sub-picture (selectable picture size: 1/9, 1/16)

- Sub-picture processing specification (1/9 size / 1/16 size) Quantization bits Y, B-Y, R-Y: 6 bits Horizontal sampling 171 pixels (Y), 28.5 pixels (B-Y, R-Y Vertical lines 69/52 lines

- Frame (sub-picture) on/off

- Built-in analog circuits

- Two 8-bit A/D converters (main and sub-picture signals) Two 8-bit D/A converters (Y and C sub-picture signals) Sync-tip-clamp, VCXO, Analog switch, etc.

- I<sup>2</sup>C BUS control (parallel/serial control)

PIP on/off, Sub-picture size (1/9 or 1/16), Frame on/off (programmable luma level), PIP position (4 corners fixed position), Picture freeze, Y delay adjustment, Chroma level, Tint, Black level, Contrast, etc.

# Application

NTSC color TV

### **Recommended Operating Condition**

| Supply voltage range 3.1 to 3                | 8.5 V                 |

|----------------------------------------------|-----------------------|

| Operating frequency 14.32 M                  | ИHz                   |

| Operating temperature20 to 7                 | 75°C                  |

| Input voltage (CMOS interface) "H" Vdd $\pm$ | 0.7 to Vdd V          |

| "L" 0 to Vd                                  | $d \pm 0.3 V$         |

| Output current (output buffer) 4 mA (        | Max)                  |

| Output load capacitance 20 pF (              | Max) <sup>Note2</sup> |

| Circuit current                              | ł                     |

- Notes: 1. Connect a 0.1  $\mu$ F or larger capacitor between Vdd and Vss pins.

- 2. Include pin capacitance (7 pF)

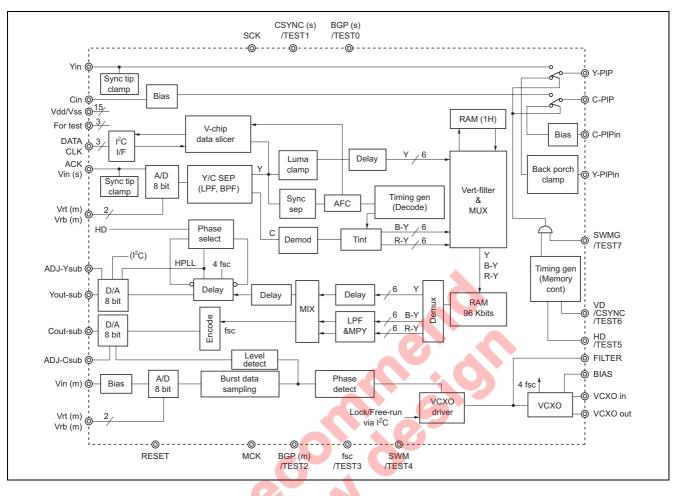

## **Block Diagram**

Notr

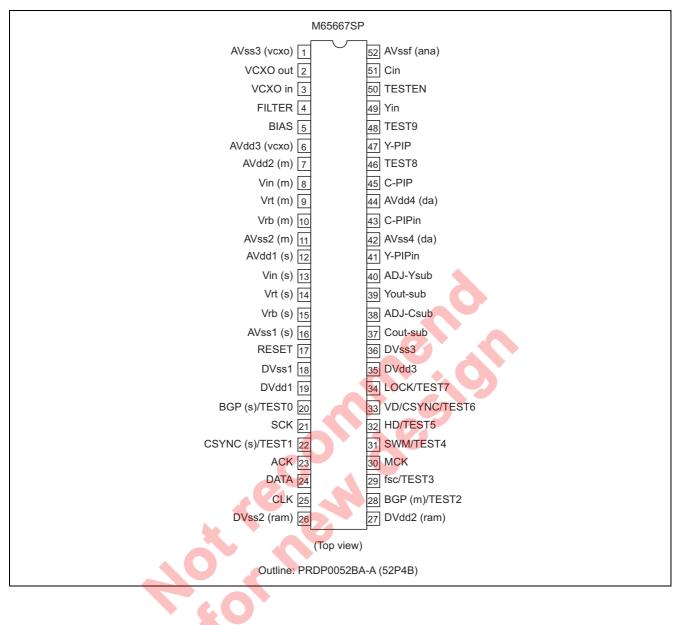

### **Pin Arrangement**

# **Pin Description**

| Pin<br>No. | Name             | I/O    | Function                                                       | Remarks                        |  |

|------------|------------------|--------|----------------------------------------------------------------|--------------------------------|--|

| 1          | AVss3 (vcxo)     | GND    | Connects to analog GND                                         |                                |  |

| 2          | VCXO out         | 0      | VCXO output signal                                             |                                |  |

| 3          | VCXO in          | -      | VCXO input signal                                              |                                |  |

| 4          | FILTER           | I      | Filter                                                         |                                |  |

| 5          | BIAS             | 0      | Bias                                                           |                                |  |

| 6          | AVdd3 (vcxo)     | Vdd    | Connect to analog power supply                                 |                                |  |

| 7          | AVdd2 (m)        | Vdd    | Connect to analog power supply                                 |                                |  |

| 8          | Vin (m)          | I      | Chroma signal input (main-picture)                             |                                |  |

| 9          | Vrt (m)          | 0      | A/D Vref+ (main-picture)                                       |                                |  |

| 10         | Vrb (m)          | 0      | A/D Vref- (main-picture)                                       |                                |  |

| 11         | AVss2 (m)        | GND    | Connect to analog GND                                          |                                |  |

| 12         | AVdd1 (s)        | Vdd    | Connect to analog power supply                                 |                                |  |

| 13         | Vin (s)          | I      | Composite video signal input (sub-picture)                     |                                |  |

| 14         | Vrt (s)          | 0      | A/D Vref+ (sub-picture)                                        |                                |  |

| 15         | Vrb (s)          | 0      | A/D Vref- (sub-picture)                                        |                                |  |

| 16         | AVss1 (s)        | GND    | Connect to analog GND                                          |                                |  |

| 17         | RESET            | I      | Power on reset input signal ("L" reset)                        | 100 kΩ to Vdd,<br>10 μF to GND |  |

| 18         | DVss1            | GND    | Connect to digital GND                                         |                                |  |

| 19         | DVdd1            | Vdd    | Connect to digital power supply                                |                                |  |

| 20         | BGP (s) /TEST0   | (I/) O | For test                                                       | Non connect                    |  |

| 21         | SCK              | I      | For test (connect to digital GND)                              | Connect to GND                 |  |

| 22         | CSYNC (s) /TEST1 | I (/O) | For test (connect to digital GND)                              | Pull down 15 k $\Omega$        |  |

| 23         | ACK              | 0      | I <sup>2</sup> C bus-data/Acknowledge output signal            |                                |  |

| 24         | DATA             | I      | I <sup>2</sup> C b <mark>us-data i</mark> nput signal          |                                |  |

| 25         | CLK              | I      | I <sup>2</sup> C bus-clock input signal                        |                                |  |

| 26         | DVss2 (ram)      | GND    | Connect to digital GND                                         |                                |  |

| 27         | DVdd2 (ram)      | Vdd    | Connect to digital power supply                                |                                |  |

| 28         | BGP (m) /TEST2   | (I/) O | For test                                                       | Non connect                    |  |

| 29         | fsc/TEST3        | I (/O) | For test (pull down to digital GND by resistor 15 k $\Omega$ ) | Pull down 15 k $\Omega$        |  |

| 30         | МСК              | I      | For test (connect to digital GND)                              | Connect to GND                 |  |

| 31         | SWM/TEST4        | (I/) O | For test                                                       | Non connect                    |  |

| 32         | HD/TEST5         | I (/O) | Horizontal sync input signal (Positive going edge is used)     |                                |  |

| 33         | VD/CSYNC/TEST6   | I (/O) | Vertical sync input signal (active "H")                        |                                |  |

| 34         | SWMG/TEST7       | I (/O) | Enable input signal to display sub picture ("H" enable)        | Pull up 15 kΩ                  |  |

| 35         | DVdd3            | Vdd    | Connect to digital power supply                                |                                |  |

| 36         | DVss3            | GND    | Connect to digital GND                                         |                                |  |

| 37         | Cout-sub         | 0      | D/A output signal (Chroma signal of sub-picture)               |                                |  |

| 38         | ADJ-Csub         | I      | D/A adjust for chroma signal (sub-picture)                     |                                |  |

| 39         | Yout-sub         | 0      | D/A output signal (Luma signal of sub-picture)                 |                                |  |

| 40         | ADJ-Ysub         | I      | D/A adjust for luma signal (sub-picture)                       |                                |  |

| 41         | Y-PIPin          | I      | PIP luma signal re-input                                       |                                |  |

| 42         | AVss4 (da)       | GND    | Connects to analog GND                                         |                                |  |

| 43         | C-PIPin          | I      | PIP chroma signal re-input                                     |                                |  |

| 44         | AVdd4 (da)       | Vdd    | Connect to analog power supply                                 |                                |  |

| 45         | C-PIP            | 0      | PIP chroma signal output                                       |                                |  |

# **Pin Description (cont.)**

| Pin<br>No. | Name        | I/O | Function                           | Remarks        |

|------------|-------------|-----|------------------------------------|----------------|

| 46         | TEST8       | I   | For test (connect to analog GND)   | Pull up 15 kΩ  |

| 47         | Y-PIP       | 0   | PIP luma signal output             |                |

| 48         | TEST9       | I   | For test (connect to analog GND)   | Connect to GND |

| 49         | Yin         | I   | Luma input signal (main-picture)   |                |

| 50         | TESTEN      | I   | For test (connect to analog GND)   | Connect to GND |

| 51         | Cin         | I   | Chroma input signal (main-picture) |                |

| 52         | AVssf (ana) | Vss | Connect to analog GND              |                |

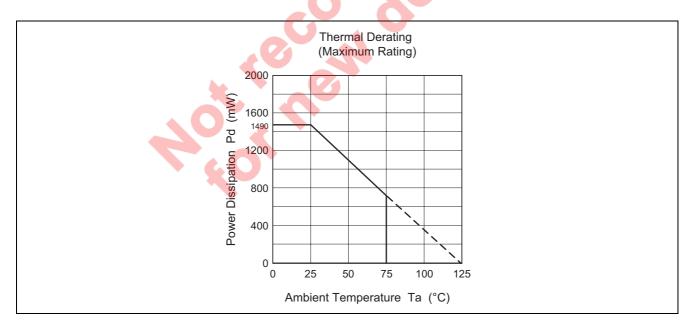

# **Absolute Maximum Ratings**

(Vss = 0 V)

|                        |                  | Lin  |                        |      |  |

|------------------------|------------------|------|------------------------|------|--|

| Item                   | Symbol           | Min  | Max                    | Unit |  |

| Supply voltage (3.3 V) | V <sub>DD3</sub> | -0.3 | 4.6                    | V    |  |

| Input voltage          | VI               | -0.3 | V <sub>DD3</sub> + 0.3 | V    |  |

| Output voltage         | Vo               | -0.3 | V <sub>DD3</sub> + 0.3 | V    |  |

| Output current Note1   | lo               | - 7  | I <sub>OL</sub> = 20   | mA   |  |

|                        |                  |      | I <sub>OH</sub> = -26  |      |  |

| Power dissipation      | Pd               |      | 1400                   | mW   |  |

| Operating temperature  | Topr             | -20  | 75                     | °C   |  |

| Storage temperature    | Tstg             | -50  | 125                    | °C   |  |

Note: 1. Output current per output terminal. But Pd limits all current.

# **DC Characteristics**

|                                |            |                  |      | Limits |      |      |                                                         |

|--------------------------------|------------|------------------|------|--------|------|------|---------------------------------------------------------|

| Item                           |            | Symbol           | Min  | Тур    | Max  | Unit | Test Conditions                                         |

| Input voltage                  | L          | V <sub>IL</sub>  | 0    | —      | 0.81 | V    | V <sub>DD</sub> = 2.7 V                                 |

| (CMOS interface)               | Н          | VIH              | 2.52 | —      | 3.6  | V    | V <sub>DD</sub> = 3.6 V                                 |

| Input voltage schmitt          | -          | V <sub>T-</sub>  | 0.5  | —      | 1.65 | V    | $V_{DD} = 3.3V$                                         |

| trigger                        | +          | V <sub>T+</sub>  | 1.4  | —      | 2.4  | V    |                                                         |

| (CMOS interface)               | Hysteresis | V <sub>H</sub>   | 0.3  | —      | 1.2  | V    |                                                         |

| Output voltage                 | L          | V <sub>OL</sub>  | _    | —      | 0.05 | V    | $V_{DD} = 3.3 \text{ V},  I_0  < 1 \ \mu\text{A}$       |

|                                | Н          | V <sub>OH</sub>  | 3.25 | _      | _    | V    |                                                         |

| Output current                 | L          | I <sub>OL</sub>  | 4    | _      |      | mA   | $V_{DD} = 3.0 \text{ V}, V_{OL} = 0.4 \text{ V}$        |

|                                | Н          | I <sub>OH</sub>  | _    | —      | -4   | mA   | $V_{DD}$ = 3.0 V, $V_{OH}$ = 2.6 V                      |

| Input current                  | L          | l <sub>IL</sub>  | -1   | _      | 1    | μΑ   | $V_{DD} = 3.6 \text{ V}, \text{ V}_{I} = 0 \text{ V}$   |

|                                | Н          | IIH              | -1   | _      | 1    | μΑ   | $V_{DD} = 3.6 \text{ V}, \text{ V}_{I} = 3.6 \text{ V}$ |

| Output leakage current         | L          | I <sub>OZL</sub> | -1   | _      | 1    | μA   | $V_{DD} = 3.6 \text{ V}, \text{ V}_{O} = 0 \text{ V}$   |

|                                | Н          | I <sub>OZH</sub> | -1   | _      | 1    | μA   | $V_{DD} = 3.6 \text{ V}, V_{O} = 3.6 \text{ V}$         |

| Input pin capacitance          |            | Cı               |      | 7      | 15   | pF   | f = 1 MHz, V <sub>DD</sub> = 0 V                        |

| Output pin capacitance         |            | Co               | —    | 7      | 15   | pF   |                                                         |

| Bidirectional pin capacitance  |            | CIO              |      | 7      | 15   | pF   |                                                         |

| Operating current 3.3 V supply |            | I <sub>DD</sub>  |      |        | 140  | mA   |                                                         |

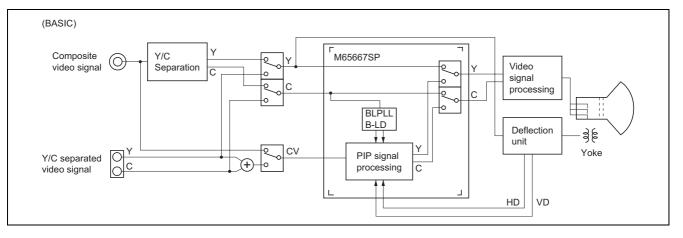

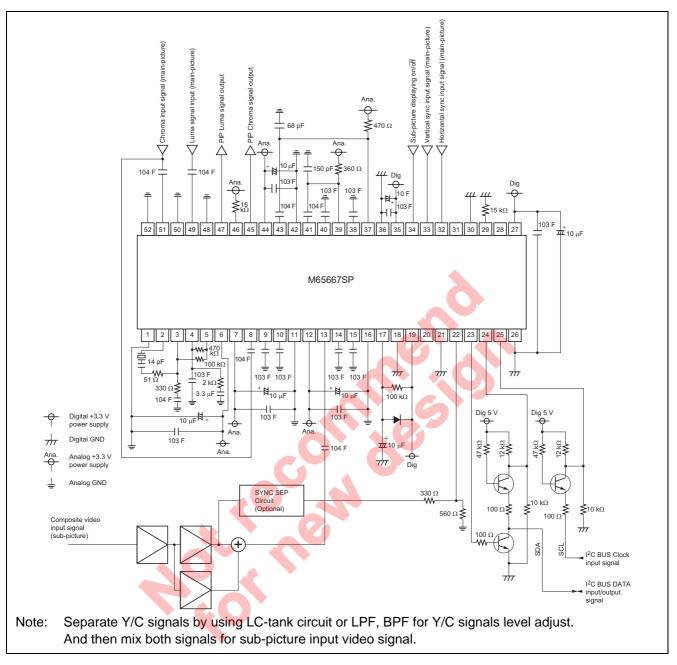

# PIP TV System Block Diagram

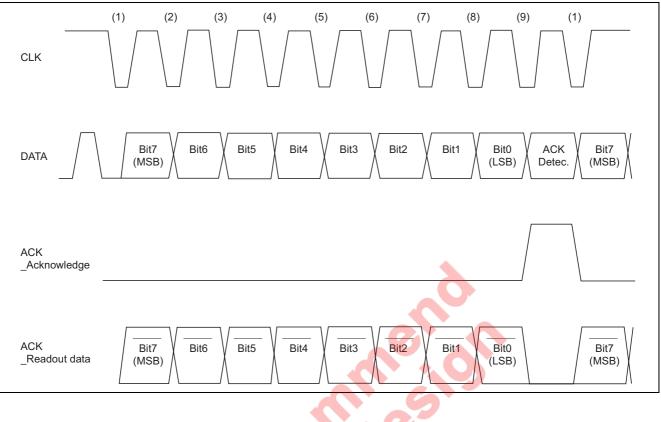

#### Driving Method and Operating Specification for Serial Interface Data

(1) Serial data transmission completion and start

A low-to-high transition of the DATA (serial data) line while the CLK (serial clock) is high, that completes the serial transmission and makes the bus free.

A high-to-low transition of the DATA line while the CLK is high, that starts the serial transmission and waits for the following CLK and DATA inputs.

(2) Serial data transmission

The data are transmitted in the most significant bit (MSB) first by one-byte unit on the DATA line successively. One-byte data transmission is completed by 9 clock cycles, the former 8 cycles are for address/data and the latter one is for acknowledge detection. (In reading state, ACK is "H" under these two conditions;

- 1. The coincidence of two address data for the address data transmission.

- The completion of 8-bit setting data transfer. In writing state, ACK is "H" with the address coincidence and ACK is "L" for detecting acknowledge input from the master (micro processor) after sending 8-bit setting data).

For address/data transmission, DATA must change while CLK is "L". (The data change while CLK is "H" or the simultaneous change of CLK and DATA, that will be a false operation because of undistinguished condition from the completion/start of serial data transfer.)

After the beginning of serial data transmission, the total number of data bytes that can be transferred are not limited.

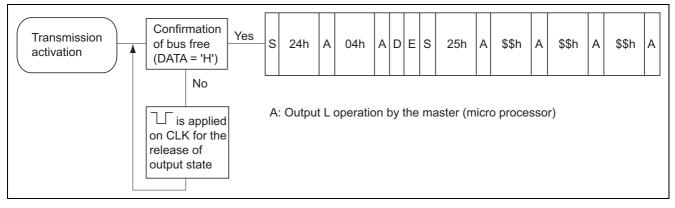

- (3) The byte format of data transmission (The sequence of data transmission)

- 1. The byte format during data setting to M65667SP are shown as follows.

In right after the forming of serial data transmitting state, the slave address 24h (00100100b) is transferred. Afterwards, the internal register address (1 byte) and setting data (by 1 byte unit) are transferred successively. Several bytes of setting data can be handled in the one transmission. In this operation, the setting data are written into the address resister whose address is increased one in initially transferred internal register address. (The next address of 7Fh, it returns to 00h.)

2. The byte format during data reading from M65667SP are shown as follows. Before data reading from M65667SP, whose internal address need to be set by the data reading/transmitting. After the data reading/transmitting, the operation of "serial data transmission completion and start" (described in (1)) is necessary. Continuously, the slave address 25h (00100101b) is sent, and then the inverted read out data are available on ACK. Several bytes of writing data can be handled in the one transmission, too. In this operation, the setting data also are written into the address register whose address is increased one in initially transferred internal register address. (The next address of 7Fh, it returns to 00h.)

#### The Examples of Serial Byte Transmission Format

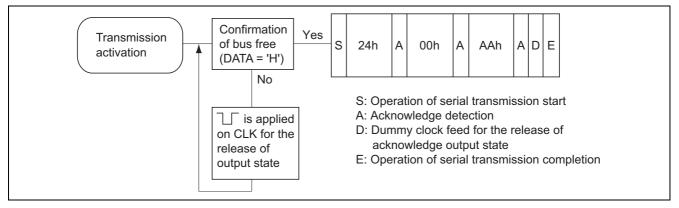

(1) The writing operation of the setting data (AAh) into M65667SP internal address of 00h

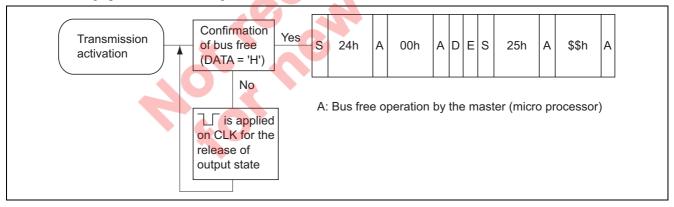

(3) The reading operation of the setting data from M65667SP internal address of 00h

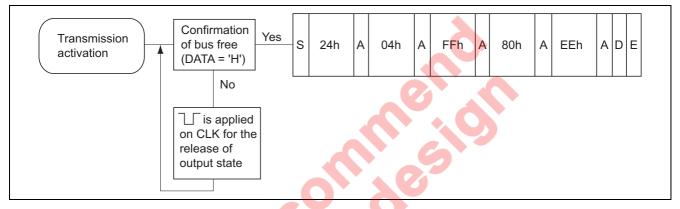

(4) The reading operation of the setting data from M65667SP internal address of 04h to 06h

RENESAS

# **Timing Diagram**

Bit3 Bit2

# **Application Example**

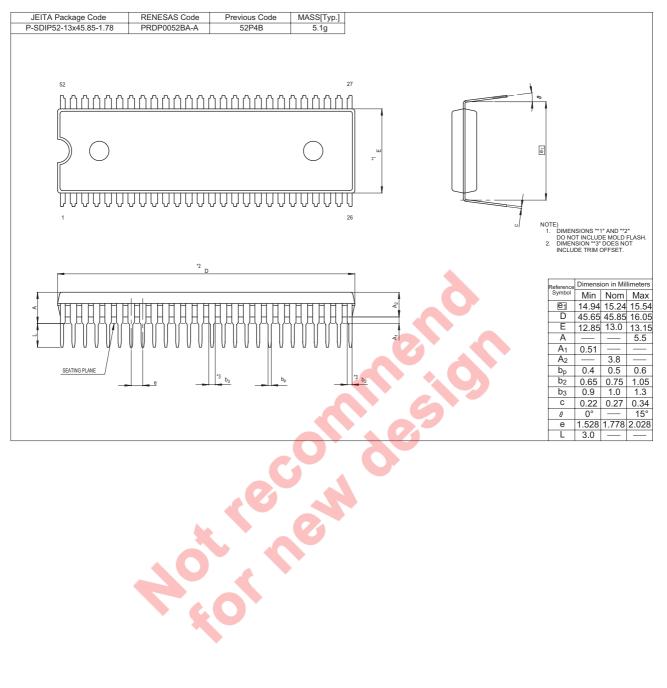

### **Package Dimensions**

## RenesasTechnology Corp. sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

- Benesas lechnology Corp. sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

Pines

This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information in this document.

This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for the intersect on the information in this document.

The product date. diagrams, charts, programs, algorithms, and application circuit examples.

An information included in this document is used. When exporting the products or the technology described herein, you should follow the applicable export control laws and regulations, and proceedures required by such laws and regulations.

An information included in this document, included in this document, but Renesas as more the applicable export control laws and regulations, and proceedures required by such laws and regulations.

Renesas has used reasonable care in compiling the information in this document, but Renesas assumes no liability whatteever for any damages incurred as a set estil of errors or omissions in the information included in this document. Dut Renesas as products for the technology described herein you should follow the applicability of such assay and the substability of the substability of the substability of the substability of the such assay included in this document.

When using or otherwise relying on the information included in this document. Nou should evaluate the information includes and regulations.

When using or otherwise relying on the information included in this document.

When using or otherwise relying on the information included in this document.

When using or otherwise and the applicability of the substability

#### RENESAS SALES OFFICES

http://www.renesas.com

#### Refer to "http://www.renesas.com/en/network" for the latest and detailed information.

Renesas Technology America, Inc. 450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500, Fax: <1> (408) 382-7501

Renesas Technology Europe Limited Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K. Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900

Renesas Technology (Shanghai) Co., Ltd. Unit 204, 205, AZIACenter, No.1233 Lujiazui Ring Rd, Pudong District, Shanghai, China 200120 Tel: <86> (21) 5877-1818, Fax: <86> (21) 6887-7858/7898

Renesas Technology Hong Kong Ltd. 7th Floor, North Tower, World Finance Centre, Harbour City, Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel: <852> 2265-6688, Fax: <852> 2377-3473

Renesas Technology Taiwan Co., Ltd. 10th Floor, No.99, Fushing North Road, Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 3518-3399

#### Renesas Technology Singapore Pte. Ltd.

1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65> 6213-0200, Fax: <65> 6278-8001

Renesas Technology Korea Co., Ltd. Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, Korea Tel: <82> (2) 796-3115, Fax: <82> (2) 796-2145

Renesas Technology Malaysia Sdn. Bhd Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: <603> 7955-9390, Fax: <603> 7955-9510