# 1.35 Watt Audio Power Amplifier with Selectable Fast Turn On Time

The NCP2991 is an audio power amplifier designed for portable communication device applications such as mobile phone applications. The NCP2991 is capable of delivering 1.35 W of continuous average power to an  $8.0~\Omega$  BTL load from a 5.0~V power supply, and 1.1~W to a  $4.0~\Omega$  BTL load from a 3.6~V power supply.

The NCP2991 provides high quality audio while requiring few external components and minimal power consumption. It features a low–power consumption shutdown mode, which is achieved by driving the SHUTDOWN pin with logic low.

The NCP2991 contains circuitry to prevent from "pop and click" noise that would otherwise occur during turn-on and turn-off transitions. It is a zero pop noise device when a single ended or a differential audio input is used.

For maximum flexibility, the NCP2991 provides an externally controlled gain (with resistors). In addition, it integrates 2 different Turn On times (15 ms or 30 ms) adjustable with the TON pin.

Due to its superior PSRR, it can be directly connected to the battery, saving the use of an LDO.

This device is available in a 9-Pin Flip-Chip CSP (Lead-Free).

#### **Features**

- 1.35 W to an 8.0 Ω BTL Load from a 5.0 V Power Supply

- Best-in-Class PSRR: up to -100 dB, Direct Connection to the Battery

- Zero Pop Noise Signature with a Single Ended Audio Input

- Ultra Low Current Shutdown Mode: 10 nA

- 2.5 V-5.5 V Operation

- External Gain Configuration Capability

- External Turn-on Time Configuration Capability: 15 ms or 30 ms

- Thermal Overload Protection Circuitry

- This is a Pb-Free Device\*

# **Typical Applications**

- Portable Electronic Devices

- PDAs

- Wireless Phones

# ON Semiconductor®

http://onsemi.com

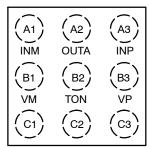

#### MARKING DIAGRAMS

P-Pin Flip-Chip CSP FC SUFFIX CASE 499E

MRH = Specific Device Code A = Assembly Location

Y = Year

WW = Work Week

= Pb-Free Package

#### PIN CONNECTIONS

BYPASS OUTB SHUTDOWN (Top View)

#### ORDERING INFORMATION

See detailed ordering and shipping information in the package dimensions section on page 13 of this data sheet.

<sup>\*</sup>For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

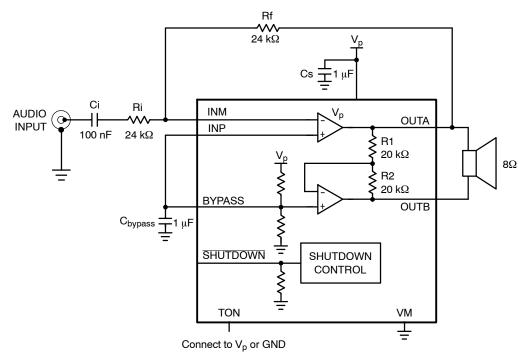

Figure 1. Typical Audio Amplifier Application Circuit with Single Ended Input

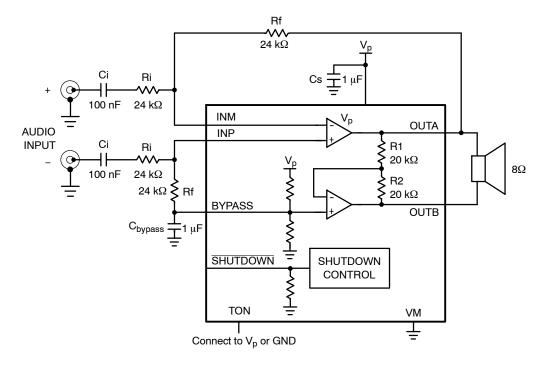

Figure 2. Typical Audio Amplifier Application Circuit with a Differential Input

#### **PIN DESCRIPTION**

| Pin | Name     | Туре | Description                                                                                                                                                     |  |

|-----|----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| A1  | INM      | I    | Negative input of the first amplifier, receives the audio input signal. Connected to the feedback resistor $R_{\rm f}$ and to the input resistor $R_{\rm in}$ . |  |

| A2  | OUTA     | 0    | Negative output of the NCP2991. Connected to the load and to the feedback resistor Rf.                                                                          |  |

| А3  | INP      | I    | Positive input of the first amplifier, receives the common mode voltage.                                                                                        |  |

| B1  | VM       | I    | Analog Ground.                                                                                                                                                  |  |

| B2  | TON      | I    | TON pin selects 2 different Turn On times:  TON = GND -> 30 ms  TON = VP -> 15 ms                                                                               |  |

| В3  | VP       | I    | Positive analog supply of the cell. Range: 2.5 V-5.5 V.                                                                                                         |  |

| C1  | BYPASS   | I    | Bypass capacitor pin which provides the common mode voltage (Vp/2).                                                                                             |  |

| C2  | OUTB     | 0    | Positive output of the NCP2991. Connected to the load.                                                                                                          |  |

| C3  | SHUTDOWN | I    | The device enters in shutdown mode when a low level is applied on this pin.                                                                                     |  |

#### MAXIMUM RATINGS (Note 1)

| Rating                                                                     | Symbol           | Value                        | Unit |

|----------------------------------------------------------------------------|------------------|------------------------------|------|

| Supply Voltage                                                             | V <sub>p</sub>   | 6.0                          | V    |

| Operating Supply Voltage                                                   | Op Vp            | 2.5 to 5.5 V                 | -    |

| Input Voltage                                                              | V <sub>in</sub>  | -0.3 to V <sub>CC</sub> +0.3 | V    |

| Max Output Current                                                         | l <sub>out</sub> | 500                          | mA   |

| Power Dissipation (Note 2)                                                 | Pd               | Internally Limited           | -    |

| Operating Ambient Temperature                                              | T <sub>A</sub>   | -40 to +85                   | °C   |

| Max Junction Temperature                                                   | TJ               | 150                          | °C   |

| Storage Temperature Range                                                  | T <sub>stg</sub> | -65 to +150                  | °C   |

| Thermal Resistance Junction-to-Air                                         | $R_{	heta JA}$   | (Note 3)                     | °C/W |

| ESD Protection Human Body Model (HBM) (Note 4) Machine Model (MM) (Note 5) | -                | 2000<br>200                  | V    |

| Latchup Current @ T <sub>A</sub> = 85°C (Note 6)                           | -                | ±100                         | mA   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect

- 1. Maximum electrical ratings are defined as those values beyond which damage to the device may occur at T<sub>A</sub> = +25°C.

- The thermal shutdown set to 160°C (typical) avoids irreversible damage on the device due to power dissipation.

The R<sub>θJA</sub> is highly dependent of the PCB Heatsink area. For example, R<sub>θJA</sub> can equal 195°C/W with 50 mm² total area and also 135°C/W with 500 mm<sup>2</sup>. The bumps have the same thermal resistance and all need to be connected to optimize the power dissipation.

- Human Body Model, 100 pF discharge through a 1.5 kΩ resistor following specification JESD22/A114.

Machine Model, 200 pF discharged through all pins following specification JESD22/A115.

# **ELECTRICAL CHARACTERISTICS** Limits apply for T<sub>A</sub> between -40°C to +85°C (Unless otherwise noted).

|                                    | 11.7                  |                                                                                                                      | Min         |                      | Max         |      |

|------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------|-------------|----------------------|-------------|------|

| Characteristic                     | Symbol                | Conditions                                                                                                           | (Note 6)    | Тур                  | (Note 6)    | Unit |

| Supply Quiescent Current           | I <sub>dd</sub>       | $V_p = 2.5 \text{ V}$ , No Load $V_p = 5.0 \text{ V}$ , No Load                                                      | -           | 1.8<br>1.95          | 3.5         | mA   |

|                                    |                       | $V_p = 2.5 \text{ V}, 8 \Omega$<br>$V_p = 5.0 \text{ V}, 8 \Omega$                                                   |             | 1.8<br>1.95          | 3.5         |      |

| Common Mode Voltage                | V <sub>cm</sub>       | -                                                                                                                    | -           | V <sub>p</sub> /2    | -           | V    |

| Shutdown Current                   | I <sub>SD</sub>       |                                                                                                                      | -           | 0.02                 | 0.5         | μΑ   |

| Shutdown Pull-Down                 | R <sub>SD</sub>       |                                                                                                                      | -           | 300                  | -           | kΩ   |

| Shutdown Voltage High              | V <sub>SDIH</sub>     | -                                                                                                                    | 1.2         | -                    | -           | V    |

| Shutdown Voltage Low               | V <sub>SDIL</sub>     | _                                                                                                                    | -           | -                    | 0.4         | V    |

| Turn On Time (Note 8)              | T <sub>WU</sub>       | TON = GND<br>TON = VP                                                                                                | -           | 30<br>15             | -           | ms   |

| Turn Off Time                      | T <sub>OFF</sub>      | -                                                                                                                    | -           | 1.0                  | -           | μs   |

| Output Impedance in Shutdown Mode  | Z <sub>SD</sub>       | -                                                                                                                    | -           | 8.5                  | -           | kΩ   |

| Output Swing                       | V <sub>loadpeak</sub> | $V_p = 2.5 \text{ V}, \ R_L = 8.0 \ \Omega$<br>$V_p = 5.0 \text{ V}, \ R_L = 8.0 \ \Omega \text{ (Note 7)}$          | 1.9         | 2.4                  | -<br>-      | V    |

|                                    |                       | T <sub>A</sub> = +25°C                                                                                               | 3.8         | 4.7                  |             |      |

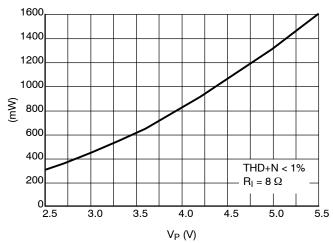

| RMS Output Power                   | Po                    | $V_p = 2.5 \text{ V}, R_L = 4.0 \Omega$<br>THD + N < 1%                                                              | _           | 0.5                  | _           | W    |

|                                    |                       | $V_p = 2.5 \text{ V}, \ R_L = 8.0 \ \Omega$<br>THD + N < 1%<br>$V_p = 5.0 \ V, \ R_L = 8.0 \ \Omega$<br>THD + N < 1% | -           | 0.3<br>1.35          | -           |      |

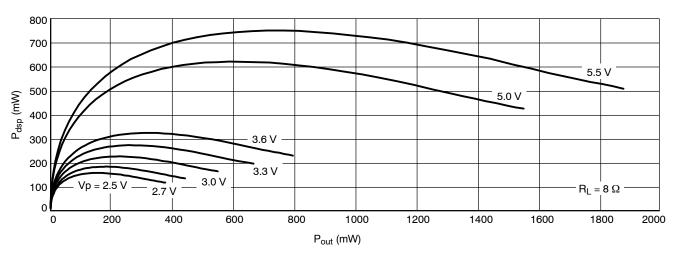

| Maximum Power Dissipation (Note 8) | P <sub>Dmax</sub>     | $V_p = 5.0 \text{ V}, R_L = 8.0 \Omega$                                                                              | -           | _                    | 0.65        | W    |

| Output Offset Voltage              | V <sub>OS</sub>       | $V_p = 2.5 \text{ V}$<br>$V_p = 5.0 \text{ V}$                                                                       | -           | 1.0                  | -           | mV   |

| Signal-to-Noise Ratio              | SNR                   | V <sub>p</sub> = 2.5 V, G = 2.0<br>20 Hz < F < 20 kHz                                                                | -           | 86                   | -           | dB   |

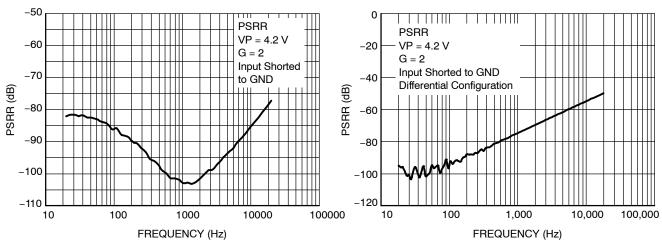

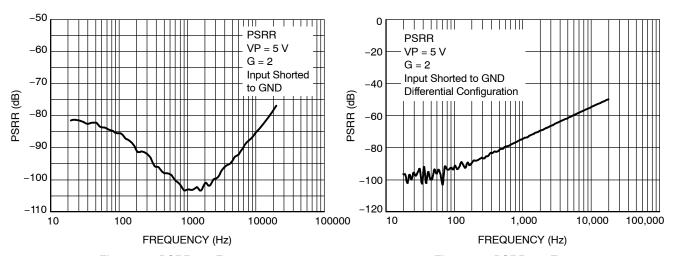

| Positive Supply Rejection Ratio    | PSRR V+               | $G=2.0,\ R_L=8.0\ \Omega$ $C_{by}=1.0\ \mu F$ Input Grounded $F=217\ Hz$ $V_p=5.0\ V$ $V_p=4.2\ V$ $V_p=3.0\ V$      | -<br>-<br>- | -91<br>-91<br>-91    | -<br>-<br>- | dB   |

|                                    |                       | $F = 1.0 \text{ kHz} V_p = 5.0 \text{ V} V_p = 4.2 \text{ V} V_p = 3.0 \text{ V}$                                    | -<br>-<br>- | -103<br>-103<br>-103 | -<br>-<br>- |      |

| Efficiency                         | η                     | $V_p = 2.5 \text{ V}, \ P_{orms} = 320 \text{ mW}$<br>$V_p = 5.0 \text{ V}, \ P_{orms} = 1.0 \text{ W}$              | -<br>-      | 71<br>64             | -           | %    |

| Thermal Shutdown Temperature       | T <sub>sd</sub>       |                                                                                                                      | -           | 160                  | -           | °C   |

| Total Harmonic Distortion          | THD                   | $V_p = 2.5 \text{ V}, F = 1.0 \text{ kHz}$ $R_L = 4.0 \Omega, A_V = 2.0$ $P_O = 0.32 \text{ W}$                      | -<br>-<br>- | -<br>0.03<br>-       | -<br>-<br>- | %    |

|                                    |                       | $V_p = 5.0 \text{ V}, F = 1.0 \text{ kHz}$ $R_L = 8.0 \Omega, A_V = 2.0$ $P_O = 1.0 \text{ W}$                       | -<br>-<br>- | –<br>0.015<br>–      | -<br>-<br>- |      |

<sup>6.</sup> Min/Max limits are guaranteed by design, test or statistical analysis.

7. This parameter is guaranteed but not tested in production in case of a 5.0 V power supply.

8. See page 12 for a theoretical approach of this parameter.

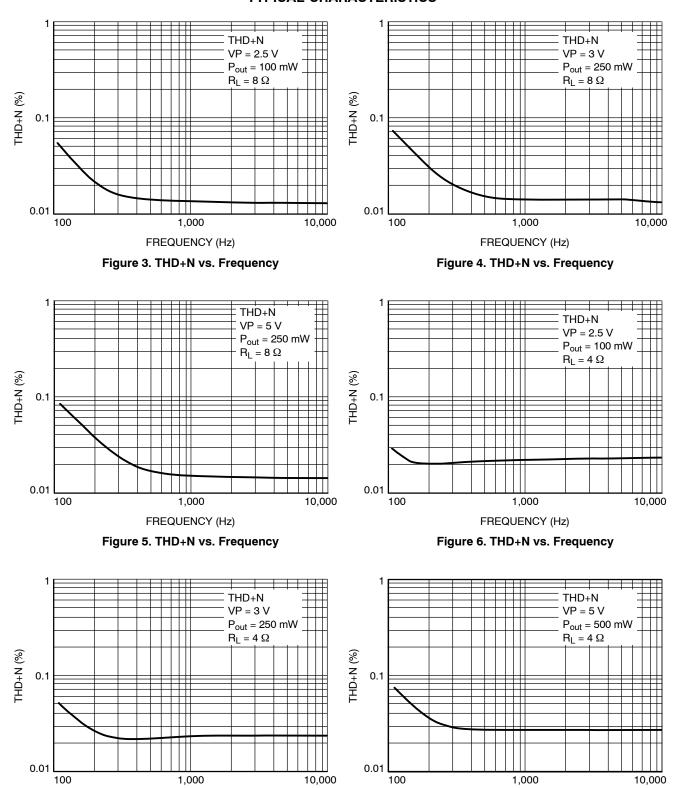

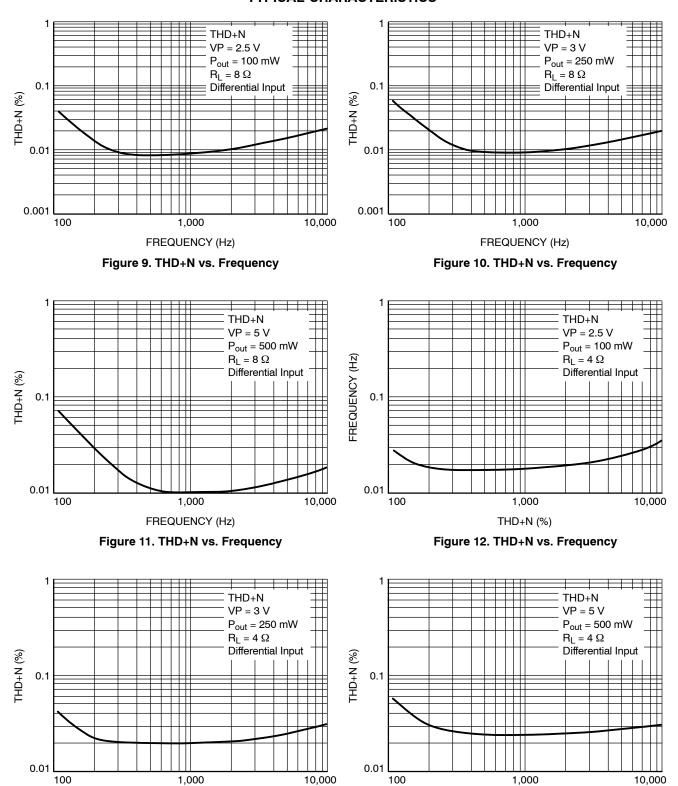

FREQUENCY (Hz)

Figure 7. THD+N vs. Frequency

FREQUENCY (Hz)

Figure 8. THD+N vs. Frequency

FREQUENCY (Hz)

Figure 13. THD+N vs. Frequency

FREQUENCY (Hz)

Figure 14. THD+N vs. Frequency

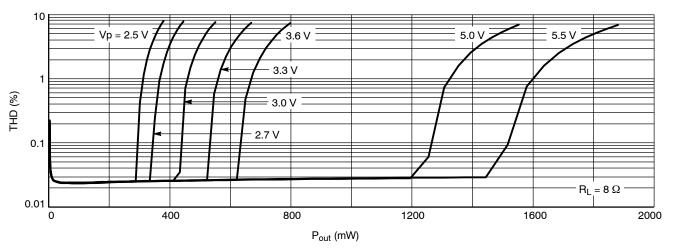

Figure 15. THD+N vs. Pout

Figure 16. THD+N vs. Pout

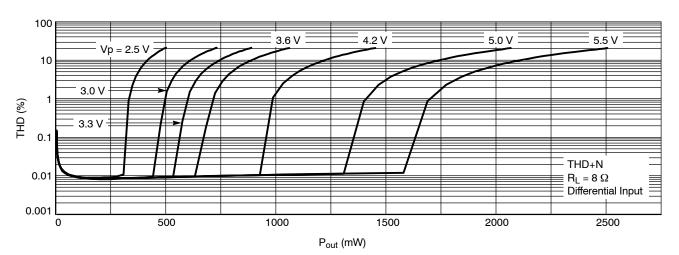

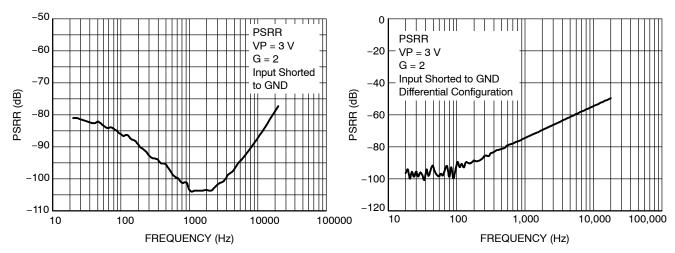

Figure 17. PSRR vs. Frequency

Figure 18. PSRR vs. Frequency

Figure 19. PSRR vs. Frequency

Figure 20. PSRR vs. Frequency

Figure 21. PSRR vs. Frequency

Figure 22. PSRR vs. Frequency

Figure 23. Power Dissipation vs. Pout

Figure 24. Maximum Output Power vs. V<sub>P</sub>

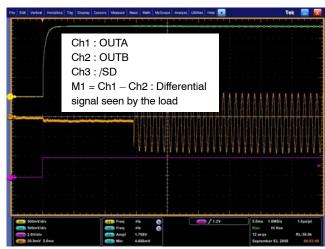

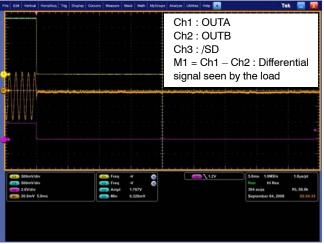

Figure 25. Zero pop noise turn on sequence with single-ended input to ground (Ci = 100 nF, Ri = 24 k $\Omega$ , Rf = 24 k $\Omega$ , Cbyp = 1  $\mu$ F, RI = 8  $\Omega$ , Ton = GND)

Figure 26. Zero pop noise turn on sequence with single-ended input audio source (Ci = 100 nF, Ri = 24 k $\Omega$ , Rf = 24 k $\Omega$ , Cbyp = 1  $\mu$ F, Rl = 8  $\Omega$ , Ton = GND)

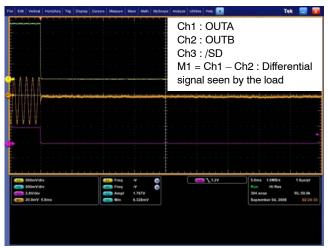

Figure 27. Zero pop noise turn off sequence with single-ended input to ground (Ci = 100 nF, Ri = 24 k $\Omega$ , Rf = 24 k $\Omega$ , Cbyp = 1  $\mu$ F, RI = 8  $\Omega$ , Ton = GND)

Figure 28. Zero pop noise turn off sequence with single-ended input audio source (Ci = 100 nF, Ri = 24 k $\Omega$ , Rf = 24 k $\Omega$ , Cbyp = 1  $\mu$ F, RI = 8  $\Omega$ , Ton = GND)

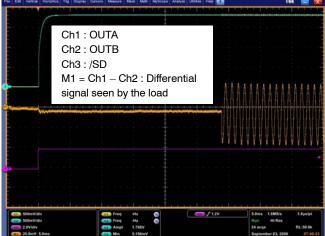

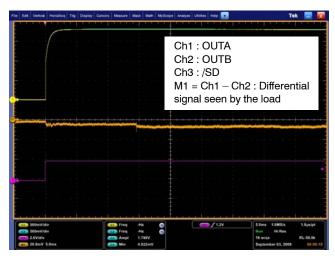

Figure 29. Zero pop noise turn on sequence with differential input to ground (Ci = 100 nF, Ri = 24 k $\Omega$ , Rf = 24 k $\Omega$ , Cbyp = 1  $\mu$ F, RI = 8  $\Omega$ , Ton = GND)

Figure 30. Zero pop noise turn on sequence with differential input audio source (Ci = 100 nF, Ri = 24 k $\Omega$ , Rf = 24 k $\Omega$ , Cbyp = 1  $\mu$ F, RI = 8  $\Omega$ , Ton = GND)

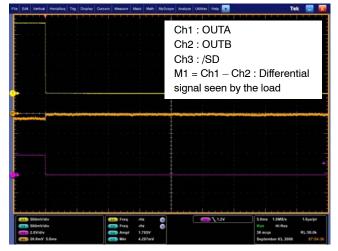

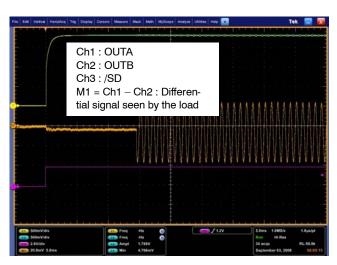

Figure 31. Zero pop noise turn off sequence with differential input to ground (Ci = 100 nF, Ri = 24 k $\Omega$ , Rf = 24 k $\Omega$ , Cbyp = 1  $\mu$ F, RI = 8  $\Omega$ , Ton = GND)

Figure 32. Zero pop noise turn off sequence with differential input audio source (Ci = 100 nF, Ri = 24 k $\Omega$ , Rf = 24 k $\Omega$ , Cbyp = 1  $\mu$ F, RI = 8  $\Omega$ , Ton = GND)

Figure 33. Zero pop noise turn on sequence with single-ended input to ground (Ci = 47 nF, Ri = 24 k $\Omega$ , Rf = 24 k $\Omega$ , Cbyp = 1  $\mu$ F, RI = 8  $\Omega$ , Ton = Vp)

Figure 34. Zero pop noise turn on sequence with single-ended input audio source (Ci = 47 nF, Ri =  $24 \text{ k}\Omega$ , Rf =  $24 \text{ k}\Omega$ , Cbyp = 1  $\mu$ F, RI =  $8 \Omega$ , Ton = Vp)

Figure 35. Zero pop noise turn off sequence with single-ended input to ground (Ci = 47 nF, Ri = 24 k $\Omega$ , Rf = 24 k $\Omega$ , Cbyp = 1  $\mu$ F, RI = 8  $\Omega$ , Ton = Vp)

Figure 36. Zero pop noise turn off sequence with single-ended input audio source (Ci = 47 nF, Ri =  $24 \text{ k}\Omega$ , Rf =  $24 \text{ k}\Omega$ , Cbyp = 1  $\mu$ F, RI =  $8 \Omega$ , Ton = Vp)

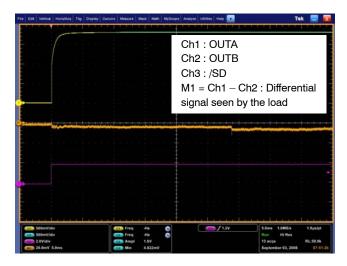

Figure 37. Zero pop noise turn on sequence with differential input to ground (Ci = 47 nF, Ri = 24 k $\Omega$ , Rf = 24 k $\Omega$ , Cbyp = 1  $\mu$ F, RI = 8  $\Omega$ , Ton = Vp)

Figure 38. Zero pop noise turn on sequence with differential input audio source (Ci = 47 nF, Ri = 24 k $\Omega$ , Rf = 24 k $\Omega$ , Cbyp = 1  $\mu$ F, RI = 8  $\Omega$ , Ton = Vp)

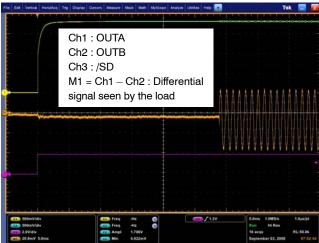

Figure 39. Zero pop noise turn off sequence with differential input to ground (Ci = 47 nF, Ri = 24 k $\Omega$ , Rf = 24 k $\Omega$ , Cbyp = 1  $\mu$ F, RI = 8  $\Omega$ , Ton = Vp)

Figure 40. Zero pop noise turn off sequence with differential input audio source (Ci = 47 nF, Ri = 24 k $\Omega$ , Rf = 24 k $\Omega$ , Cbyp = 1  $\mu$ F, RI = 8  $\Omega$ , Ton = Vp)

#### APPLICATION INFORMATION

#### **Detailed Description**

The NCP2991 audio amplifier can operate under 2.5 V until 5.5 V power supply. With less than 1% THD + N, it can deliver up to 1.35 W RMS output power to an 8.0  $\Omega$  load (Vp = 5.0 V). If application allows to reach 10% THD + N, then 1.65 W can be provided using a 5.0 V power supply.

The structure of the NCP2991 is basically composed of two identical internal power amplifiers; the first one is externally configurable with gain–setting resistors  $R_{in}$  and  $R_f$  (the closed–loop gain is fixed by the ratios of these resistors) and the second is internally fixed in an inverting unity–gain configuration by two resistors of 20 k $\Omega$ . So the load is driven differentially through OUTA and OUTB

outputs. This configuration eliminates the need for an output coupling capacitor.

#### **Internal Power Amplifier**

The output PMOS and NMOS transistors of the amplifier were designed to deliver the output power of the specifications without clipping. The channel resistance ( $R_{on}$ ) of the NMOS and PMOS transistors does not exceed 0.6  $\Omega$  when they drive current.

The structure of the internal power amplifier is composed of three symmetrical gain stages, first and medium gain stages are transconductance gain stages to obtain maximum bandwidth and DC gain.

#### Turn-On and Turn-Off Transitions

When a shutdown low level is applied, the output level is tied to Ground on each output after 10  $\mu$ s.

With  $T_{ON}$  = GND, turn on time is set to 30 ms. With  $T_{ON}$  =  $V_{P}$  turn on time is set to 15 ms. To avoid any pop and click noises,  $R_{in}$  \*  $C_{in}$  < 2.4 ms with  $T_{ON}$  = GND and  $R_{in}$  \*  $C_{in}$  < 1.2 ms with  $T_{ON}$  =  $V_{P}$ . The electrical characteristics are identical with the 2 configurations. This fast turn on time added to a very low shutdown current saves battery life and brings flexibility when designing the audio section of the final application.

NCP2991 is a zero pop noise device when using a single-ended or differential audio input configuration.

#### **Shutdown Function**

The device enters shutdown mode when shutdown signal is low. During the shutdown mode, the DC quiescent current of the circuit does not exceed 100 nA. In this configuration, the output impedance is 8.5 k $\Omega$  on each output.

#### **Current Limit Circuit**

The maximum output power of the circuit ( $P_{orms}$  = 1.0 W,  $V_P$  = 5.0 V,  $R_L$  = 8.0  $\Omega$ ) requires a peak current in the load of 500 mA.

In order to limit the excessive power dissipation in the load when a short-circuit occurs, the current limit in the load is fixed to 1.1 A. The current in the four output MOS transistors are real-time controlled, and when one current exceeds 1.1 A, the gate voltage of the MOS transistor is clipped and no more current can be delivered.

#### **Thermal Overload Protection**

Internal amplifiers are switched off when the temperature exceeds 160°C, and will be switched on again only when the temperature decreases fewer than 140°C.

The NCP2991 is unity-gain stable and requires no external components besides gain-setting resistors, an input coupling capacitor and a proper bypassing capacitor in the typical application.

The first amplifier is externally configurable ( $R_f$  and  $R_{in}$ ), while the second is fixed in an inverting unity gain configuration.

The differential-ended amplifier presents two major advantages:

- The possible output power is four times larger (the output swing is doubled) as compared to a single-ended amplifier under the same conditions.

- Output pins (OUTA and OUTB) are biased at the same potential V<sub>P</sub>/2, this eliminates the need for an output coupling capacitor required with a single-ended amplifier configuration.

The differential closed loop-gain of the amplifier is

given by

$$A_{Vd}$$

= 2 \*  $\frac{R_f}{R_{in}} = \frac{V_{orms}}{V_{inrms}}$  .

Output power delivered to the load is given by  $P_{orms} = \frac{(Vopeak)^2}{2*R_L} (V_{opeak} \text{ is the peak differential output voltage}).$

When choosing gain configuration to obtain the desired output power, check that the amplifier is not current limited or clipped.

The maximum current which can be delivered to the load

is 500 mA

$$I_{opeak} = \frac{V_{opeak}}{R_L}$$

.

# Gain-Setting Resistor Selection (Rin and Rf)

$R_{\text{in}}$  and  $R_{\text{f}}\,\text{set}$  the closed–loop gain of the amplifier.

In order to optimize device and system performance, the NCP2991 should be used in low gain configurations.

The low gain configuration minimizes THD + noise values and maximizes the signal to noise ratio, and the amplifier can still be used without running into the bandwidth limitations.

A closed loop gain in the range from 2 to 5 is recommended to optimize overall system performance.

An input resistor ( $R_{in}$ ) value of 24 k $\Omega$  is realistic in most of applications, and doesn't require the use of a too large capacitor  $C_{in}$ .

#### Input Capacitor Selection (Cin)

The input coupling capacitor blocks the DC voltage at the amplifier input terminal. This capacitor creates a high-pass filter with  $R_{\rm in}$ , the cut-off frequency is given by

$$fc = \frac{1}{2 * \Pi * R_{in} * C_{in}}$$

.

The size of the capacitor must be large enough to couple in low frequencies without severe attenuation.

#### **ORDERING INFORMATION**

| Device       | Package                      | Shipping <sup>†</sup> |

|--------------|------------------------------|-----------------------|

| NCP2991FCT2G | 9-Pin Flip-Chip<br>(Pb-Free) | 3000 / Tape & Reel    |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

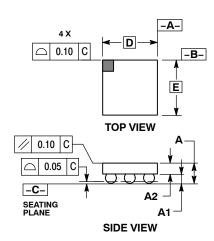

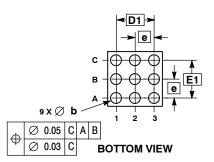

#### PACKAGE DIMENSIONS

#### 9 PIN FLIP-CHIP CASE 499E-01 **ISSUE A**

#### NOTES

- DIMENSIONING AND TOLERANCING PER

- DIMENSIONING AND TOLERANGING PER ANSI Y14.5M, 1982. CONTROLLING DIMENSION: MILLIMETERS. COPLANARITY APPLIES TO SPHERICAL CROWNS OF SOLDER BALLS.

|     | MILLIMETERS |       |  |

|-----|-------------|-------|--|

| DIM | MIN         | MAX   |  |

| Α   | 0.540       | 0.660 |  |

| A1  | 0.210       | 0.270 |  |

| A2  | 0.330       | 0.390 |  |

| D   | 1.450 BSC   |       |  |

| E   | 1.450 BSC   |       |  |

| b   | 0.290       | 0.340 |  |

| е   | 0.500 BSC   |       |  |

| D1  | 1.000 BSC   |       |  |

| E1  | 1.000 BSC   |       |  |

ON Semiconductor and una are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5773-3850

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your loca Sales Representative