16/32

# M32C/83 Group (M32C/83, M32C/83T) Hardware Manual

RENESAS 16/32-BIT SINGLE-CHIP MICROCOMPUTER

M16C FAMILY / M32C/80 SERIES

Before using this material, please visit our website to verify that this is the most current document available.

Rev. 1.31

Revision Date: Jan. 31, 2006

#### Keep safety first in your circuit designs!

1. Renesas Technology Corp. puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of non-flammable material or (iii) prevention against any malfunction or mishap.

#### Notes regarding these materials

- 1. These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corp. product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corp. or a third party.

- 2. Renesas Technology Corp. assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corp. without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor for the latest product information before purchasing a product listed herein.

- The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corp. assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

- Please also pay attention to information published by Renesas Technology Corp. by various means, including the Renesas Technology Corp. Semiconductor home page (http://www.renesas.com).

- 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corp. assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corp. semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- 6. The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduce in whole or in part these materials.

- 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

- Any diversion or reexport contrary to the export control laws and regulations of Japan and/ or the country of destination is prohibited.

- 8. Please contact Renesas Technology Corp. for further details on these materials or the products contained therein.

## **How to Use This Manual**

#### 1. Introduction

This hardware manual provides detailed information on the M32C/83 Group (M32C/83, M32C/83T) microcomputers. Users are expected to have basic knowledge of electric circuits, logical circuits and microcomputers.

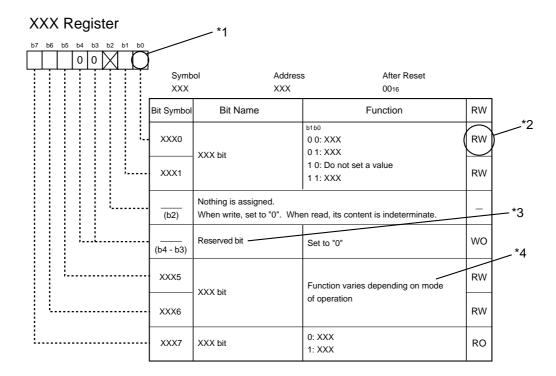

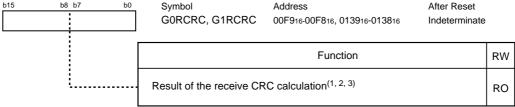

#### 2. Register Diagram

The symbols, and descriptions, used for bit function in each register are shown below.

\*1

Blank: Set to "0" or "1" according to the application

0: Set to "0"

1: Set to "1"

X: Nothing is assigned

\*2

RW: Read and write

RO: Read only

WO: Write only

Nothing is assigned

\*3

Reserved bit

Reserved bit. Set to specified value.

\*4

· Nothing is assigned

Nothing is assigned to the bit concerned. As the bit may be use for future functions, set to "0" when writing to this bit.

• Do not set a value

The operation is not guaranteed when a value is set.

• Function varies depending on mode of operation

Bit function varies depending on peripheral function mode.

Refer to respective register for each mode.

## 3. M16C Family Documents

The following documents were prepared for the M16C family. (1)

| Document                 | Contents                                                                  |  |

|--------------------------|---------------------------------------------------------------------------|--|

| Short Sheet              | Hardware overview                                                         |  |

| Data Sheet               | Hardware overview and electrical characteristics                          |  |

| Hardware Manual          | Hardware specifications (pin assignments, memory maps, peripheral         |  |

|                          | specifications, electrical characteristics, timing charts)                |  |

| Software Manual          | Detailed description of assembly instructions and microcomputer perfor-   |  |

|                          | mance of each instruction                                                 |  |

| Application Note         | Application examples of peripheral functions                              |  |

|                          | Sample programs                                                           |  |

|                          | Introduction to the basic functions in the M16C family                    |  |

|                          | Programming method with Assembly and C languages                          |  |

| RENESAS TECHNICAL UPDATE | Preliminary report about the specification of a product, a document, etc. |  |

## NOTES:

1. Before using this material, please visit the our website to confirm that this is the most current document available.

## **Table of Contents**

| Quick Reference by Address                                    | B-1 |

|---------------------------------------------------------------|-----|

| 1. Overview                                                   | 1   |

| 1.1 Applications                                              |     |

| 1.2 Performance Overview                                      | 2   |

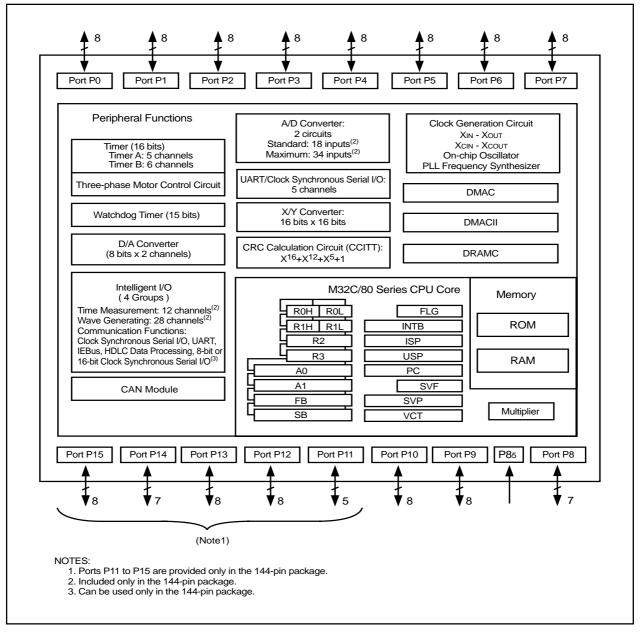

| 1.3 Block Diagram                                             | 4   |

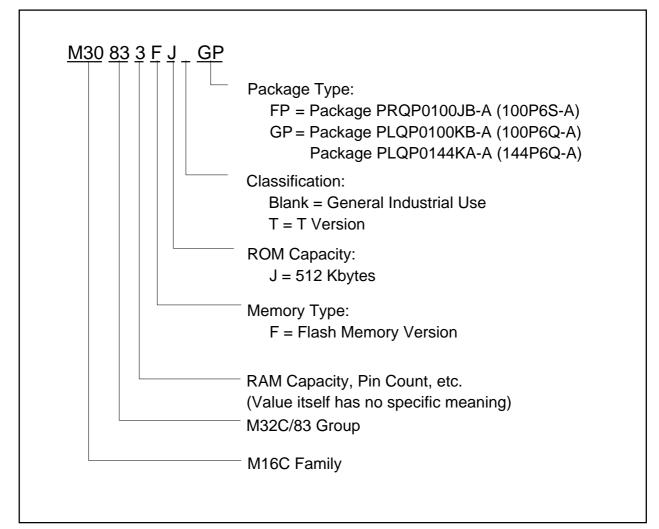

| 1.4 Product Information                                       | 5   |

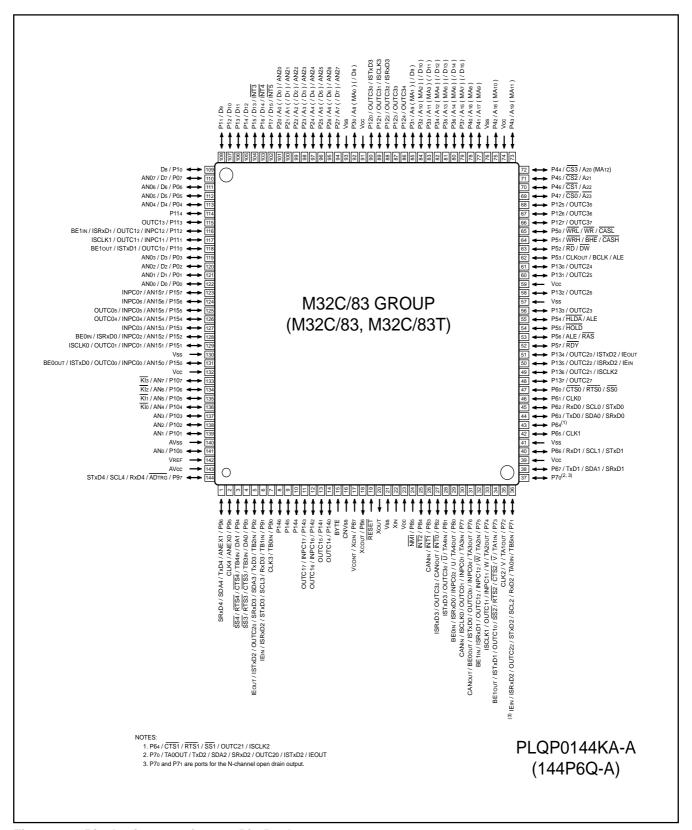

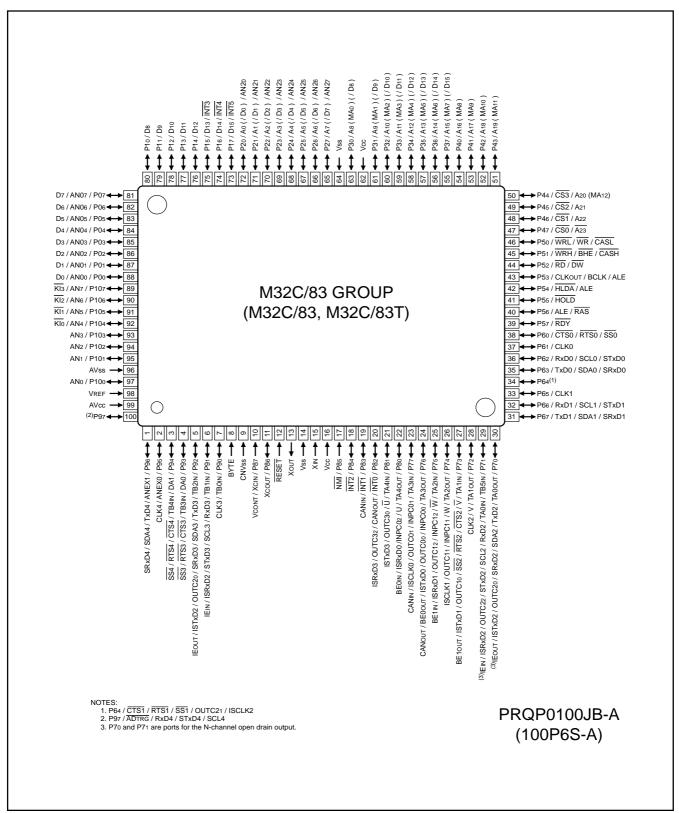

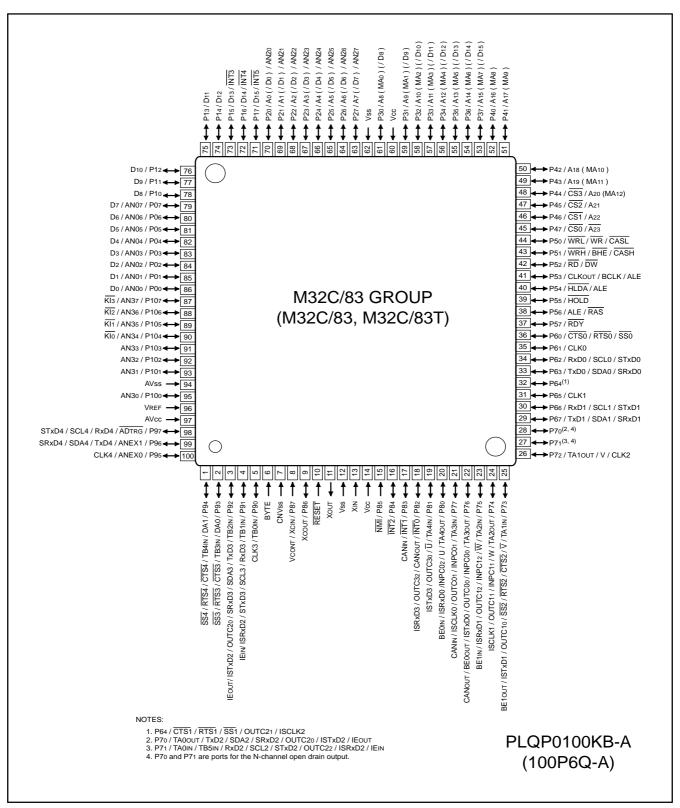

| 1.5 Pin Assignment                                            |     |

| 1.6 Pin Description                                           | 14  |

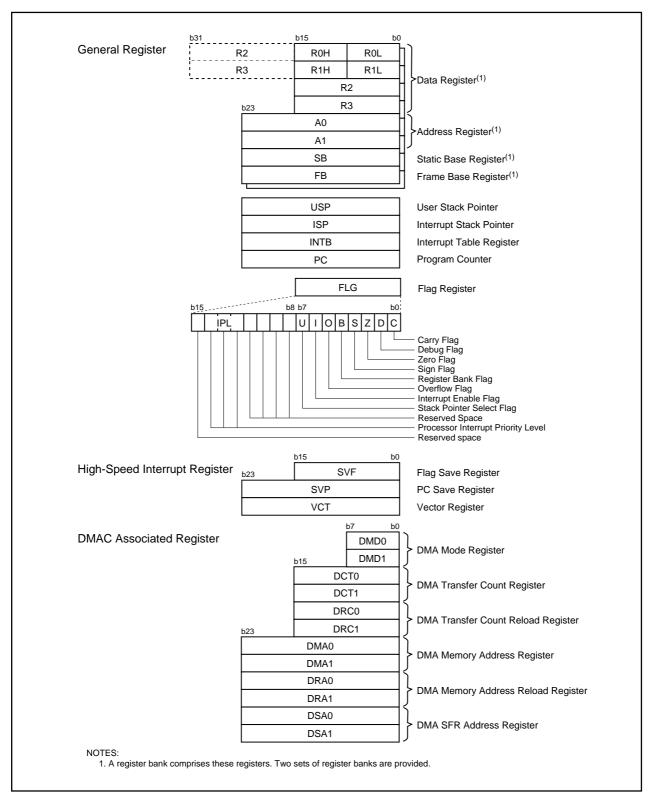

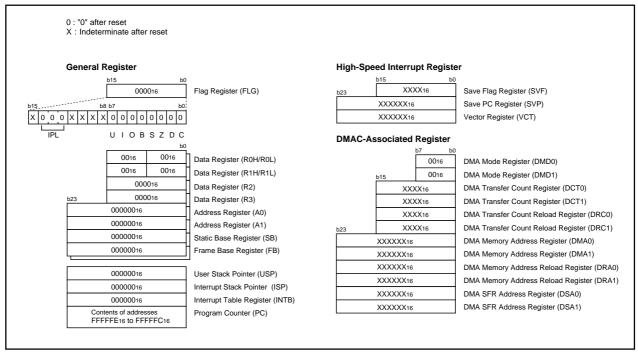

| 2. Central Processing Unit (CPU)                              | 18  |

| 2.1 General Registers                                         |     |

| 2.1.1 Data Registers (R0, R1, R2 and R3)                      |     |

| 2.1.2 Address Registers (A0 and A1)                           |     |

| 2.1.3 Static Base Register (SB)                               |     |

| 2.1.4 Frame Base Register (FB)                                |     |

| 2.1.5 Program Counter (PC)                                    |     |

| 2.1.6 Interrupt Table Register (INTB)                         |     |

| 2.1.7 User Stack Pointer (USP), Interrupt Stack Pointer (ISP) |     |

| 2.1.8 Flag Register (FLG)2.2 High-Speed Interrupt Registers   |     |

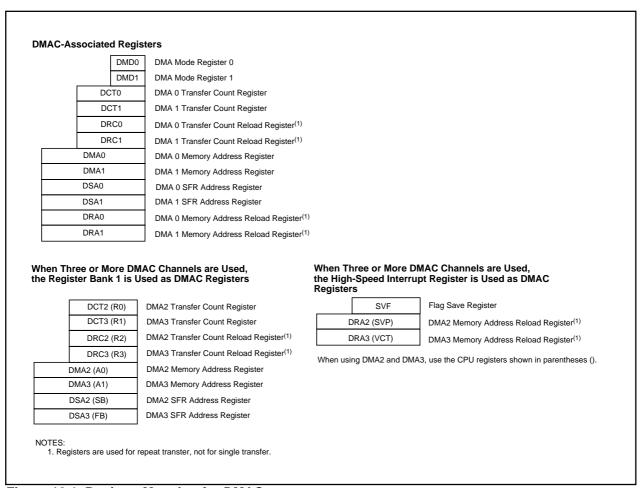

| 2.3 DMAC-Associated Registers                                 |     |

| _                                                             |     |

| 3. Memory                                                     |     |

| 4. Special Function Registers (SFR)                           | 22  |

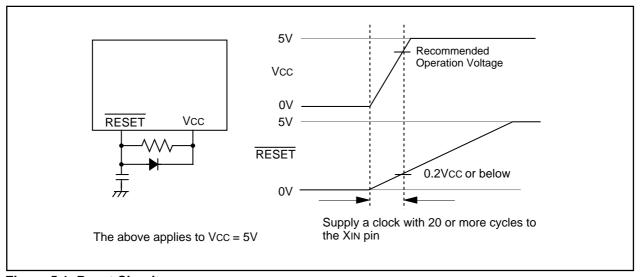

| 5. Reset                                                      | 44  |

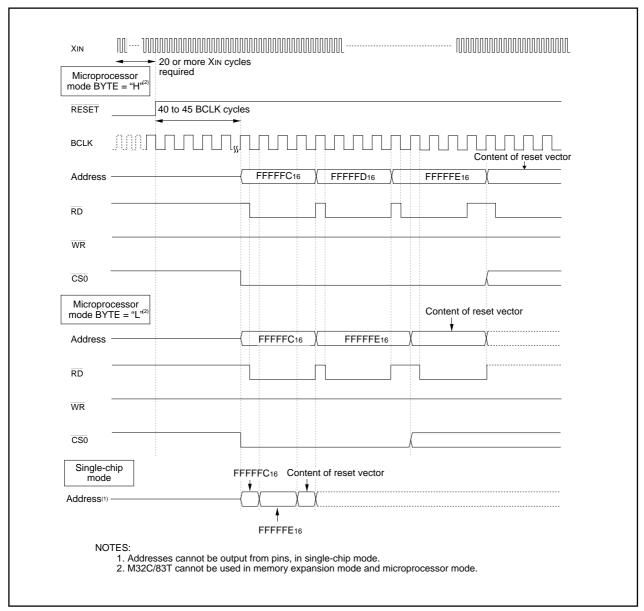

| 5.1 Hardware Reset                                            | 44  |

| 5.1.1 Reset on a Stable Supply Voltage                        | 44  |

| 5.1.2 Power-on Reset                                          |     |

| 5.2 Software Reset                                            |     |

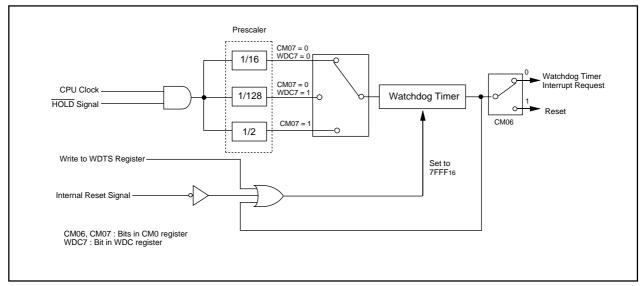

| 5.3 Watchdog Timer Reset                                      |     |

| 5.4 Internal Space                                            |     |

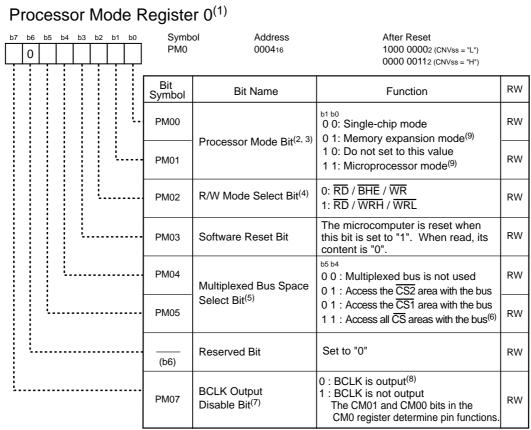

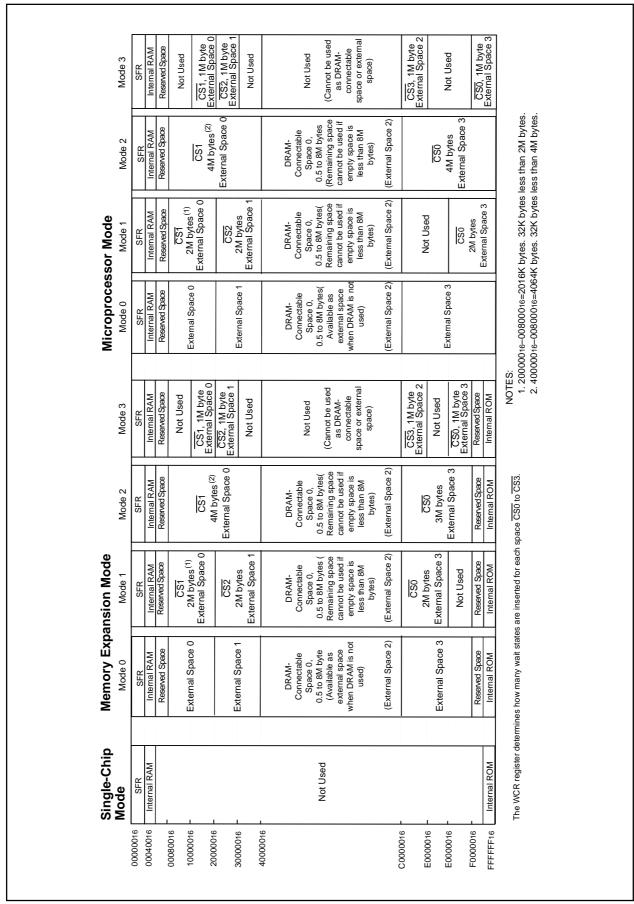

| 6. Processor Mode                                             | 48  |

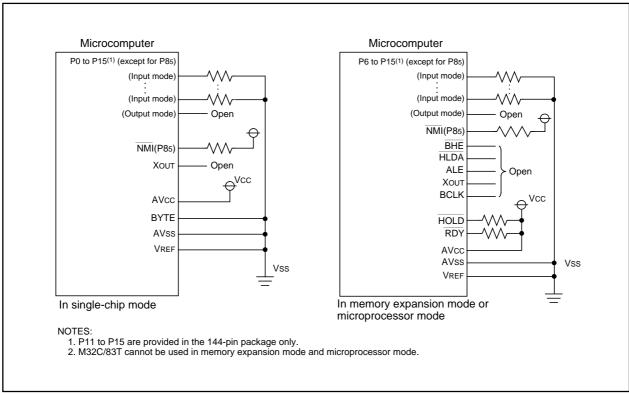

| 6.1 Types of Processor Mode                                   |     |

| 6.1.1 Single-chip Mode                                        |     |

| 6.1.2 Memory Expansion Mode                                   |     |

| 6.1.3 Microprocessor Mode                                     | 48  |

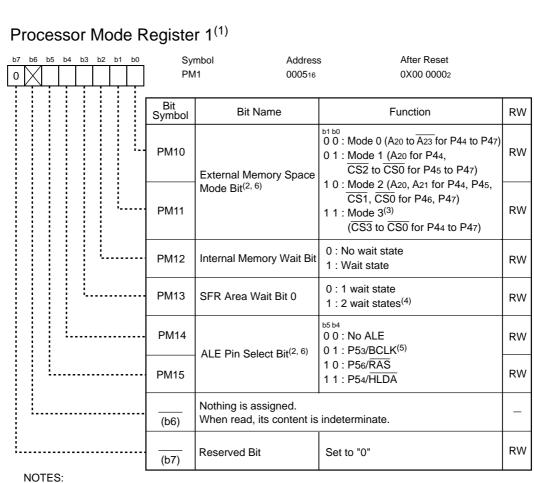

|    | 6.2 Setting Processor Mode                             | 48 |

|----|--------------------------------------------------------|----|

|    | 6.2.1 Applying VSS to CNVSS Pin                        | 48 |

|    | 6.2.2 Applying VCC to CNVSS Pin                        | 48 |

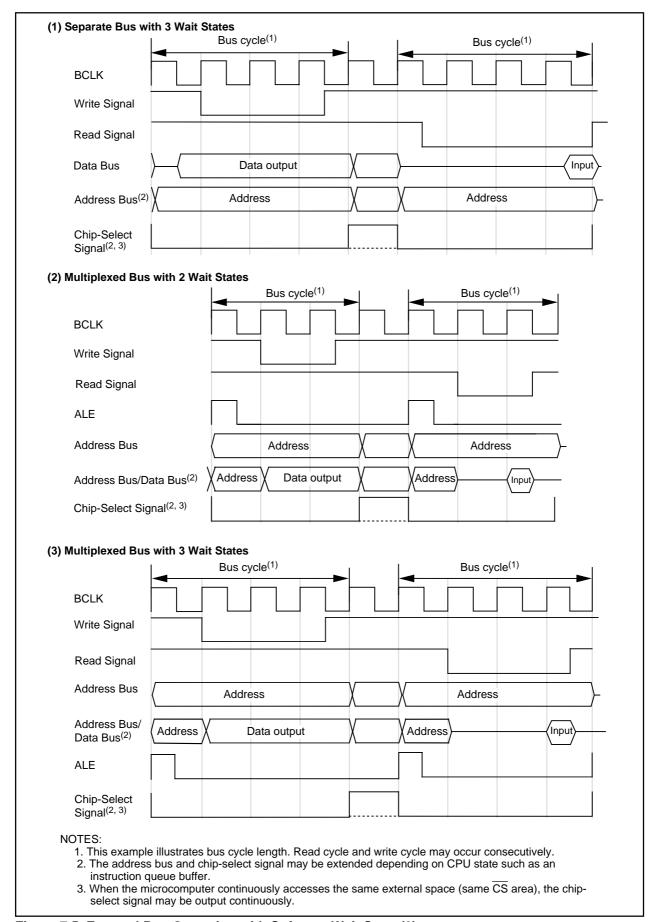

| 7. | Bus                                                    | 52 |

|    | 7.1 Bus Settings                                       | 52 |

|    | 7.1.1 Selecting External Address Bus                   | 53 |

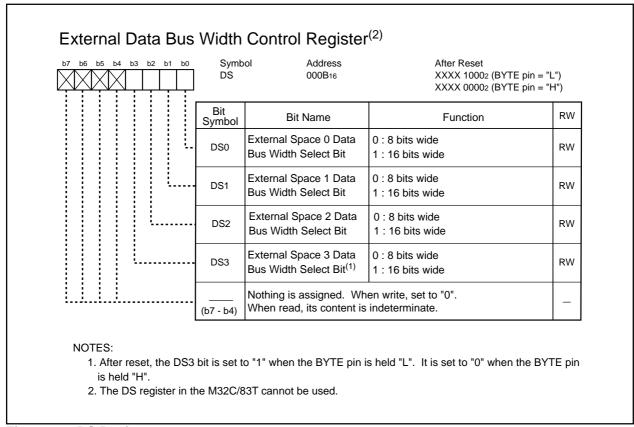

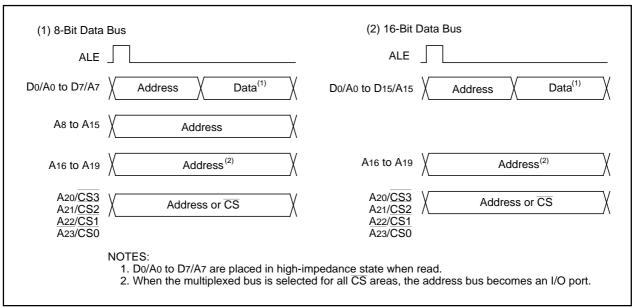

|    | 7.1.2 Selecting External Data Bus                      |    |

|    | 7.1.3 Selecting Separate/Multiplexed Bus               | 53 |

|    | 7.2 Bus Control                                        | 55 |

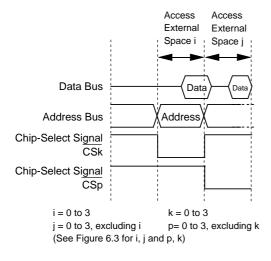

|    | 7.2.1 Address Bus and Data Bus                         | 55 |

|    | 7.2.2 Chip-Select Signal                               | 55 |

|    | 7.2.3 Read and Write Signals                           | 57 |

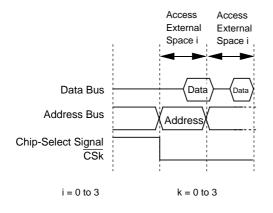

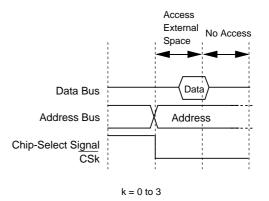

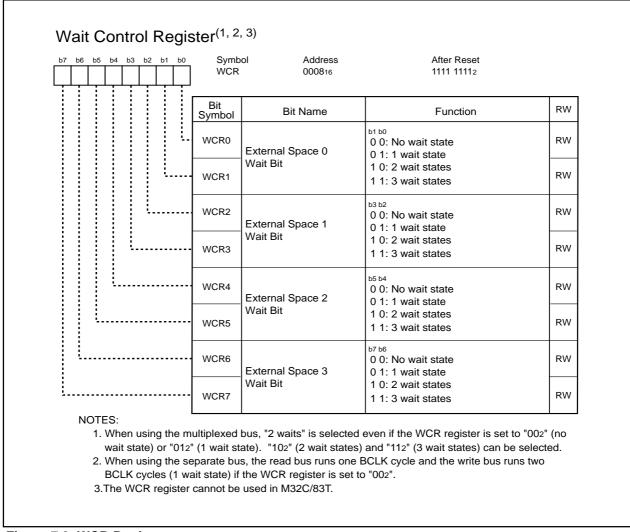

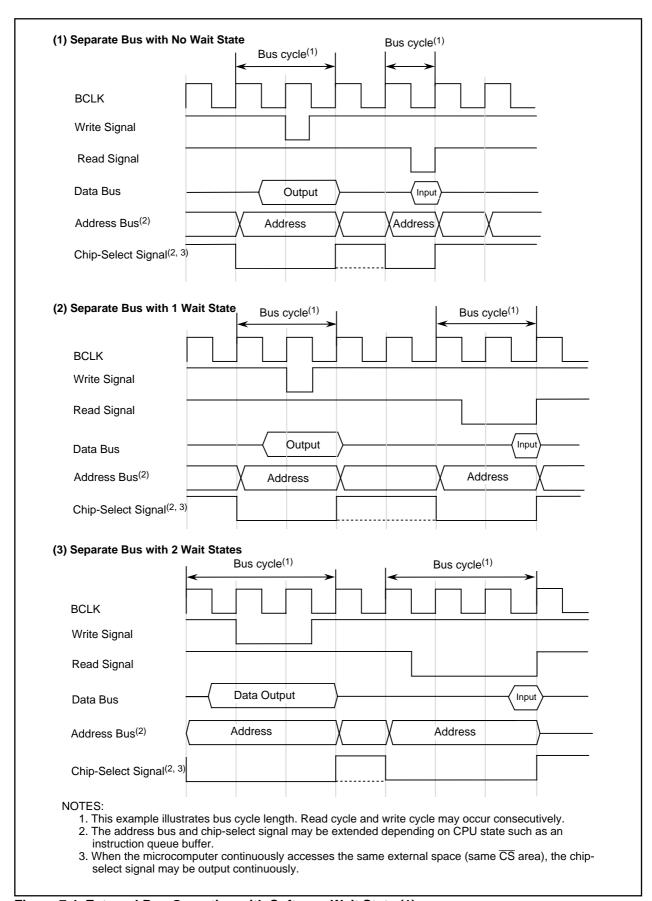

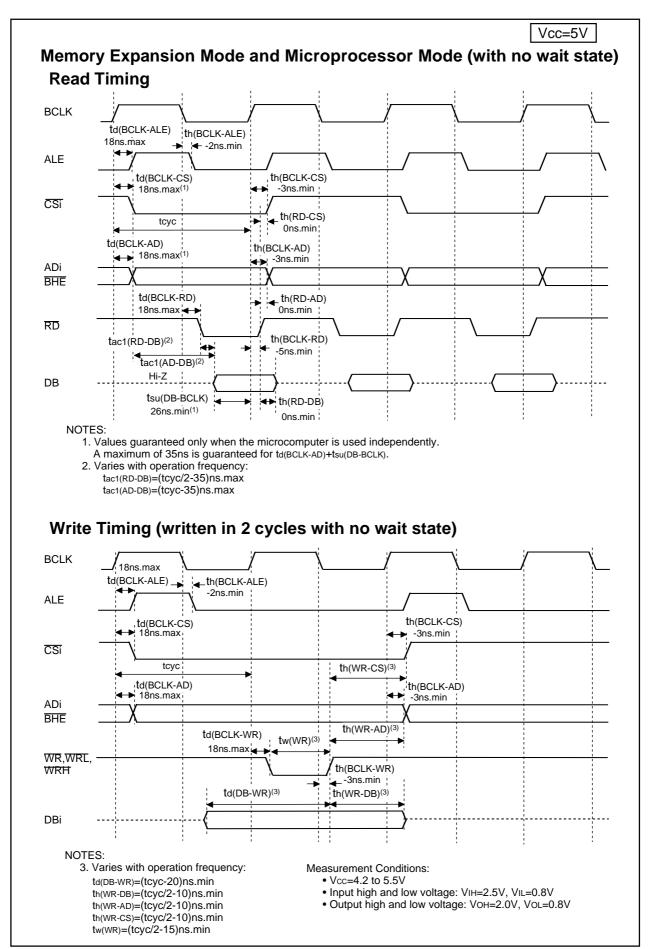

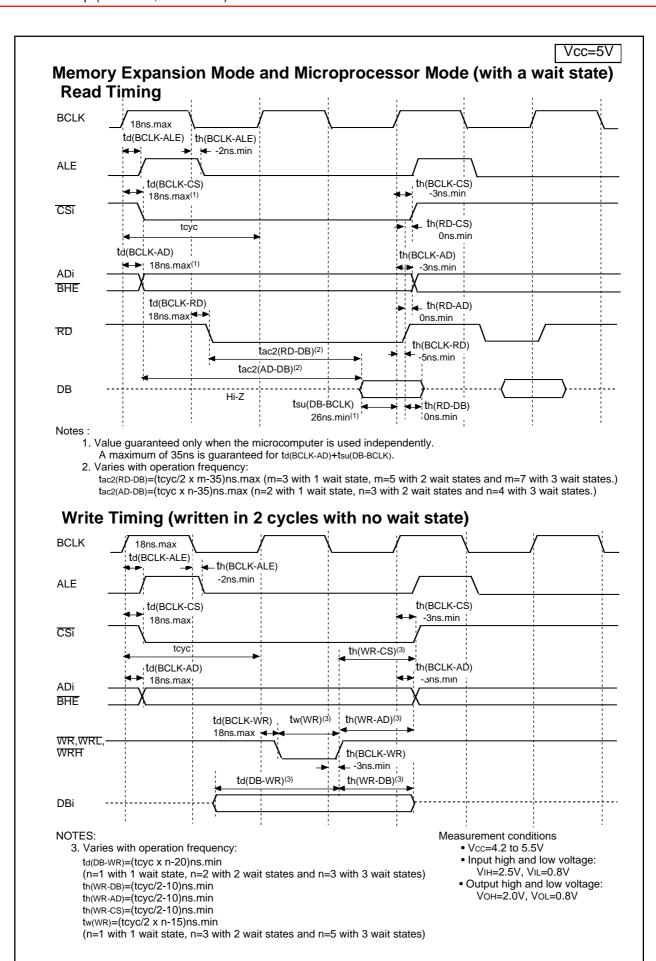

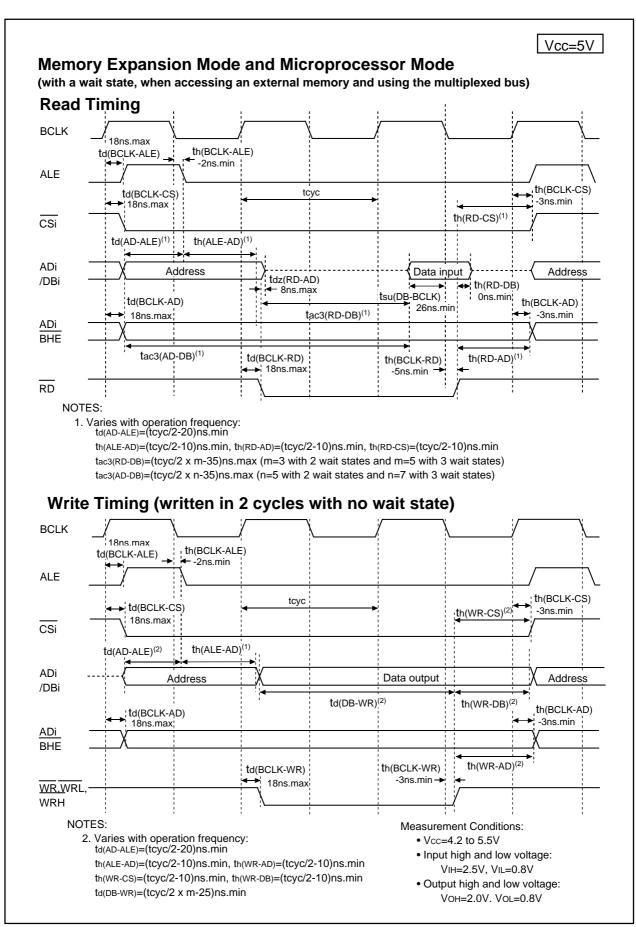

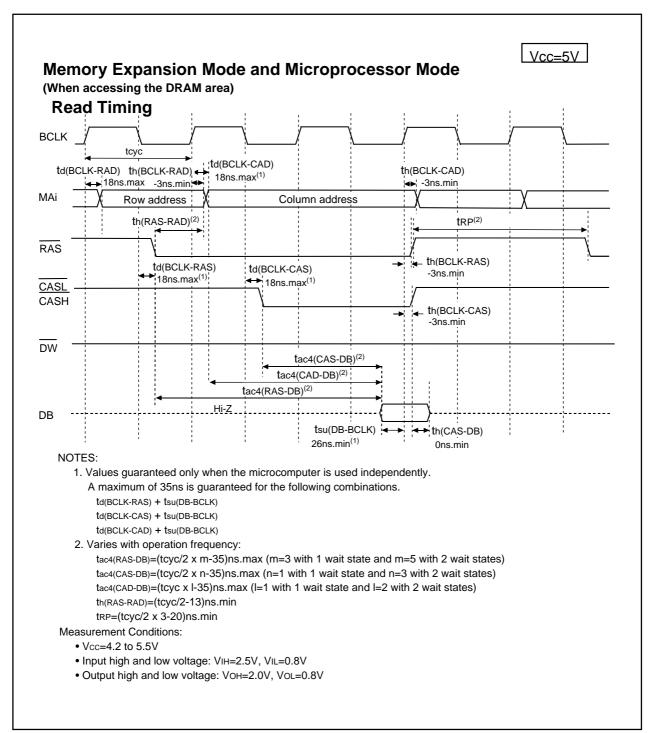

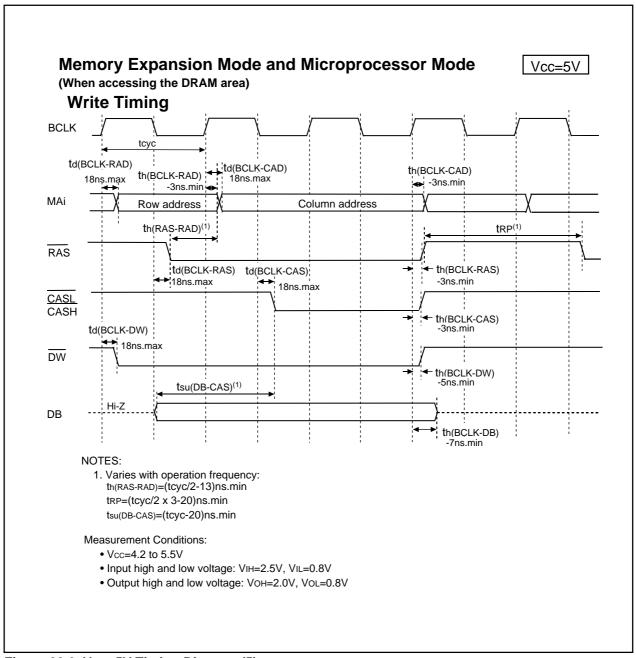

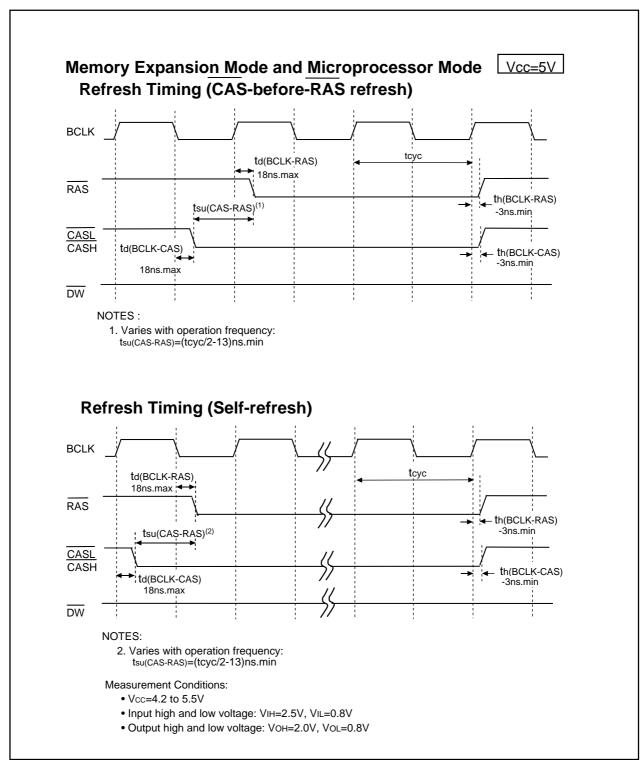

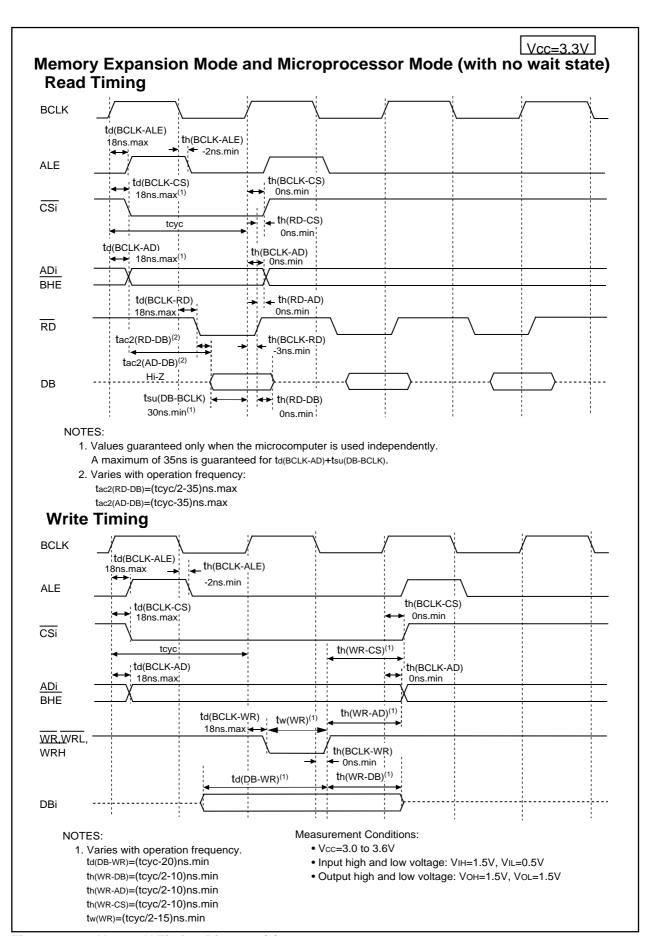

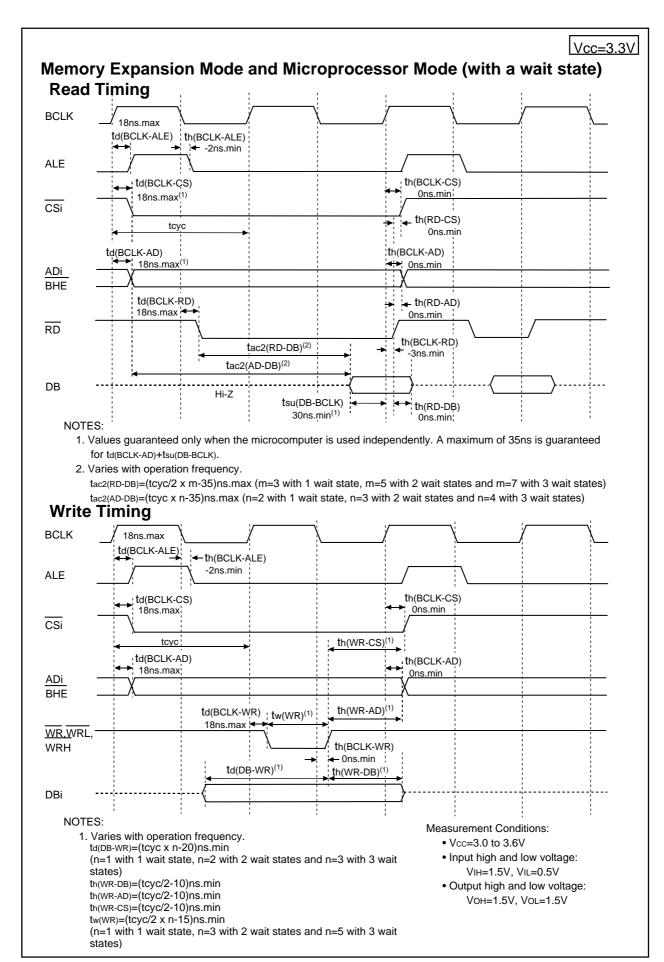

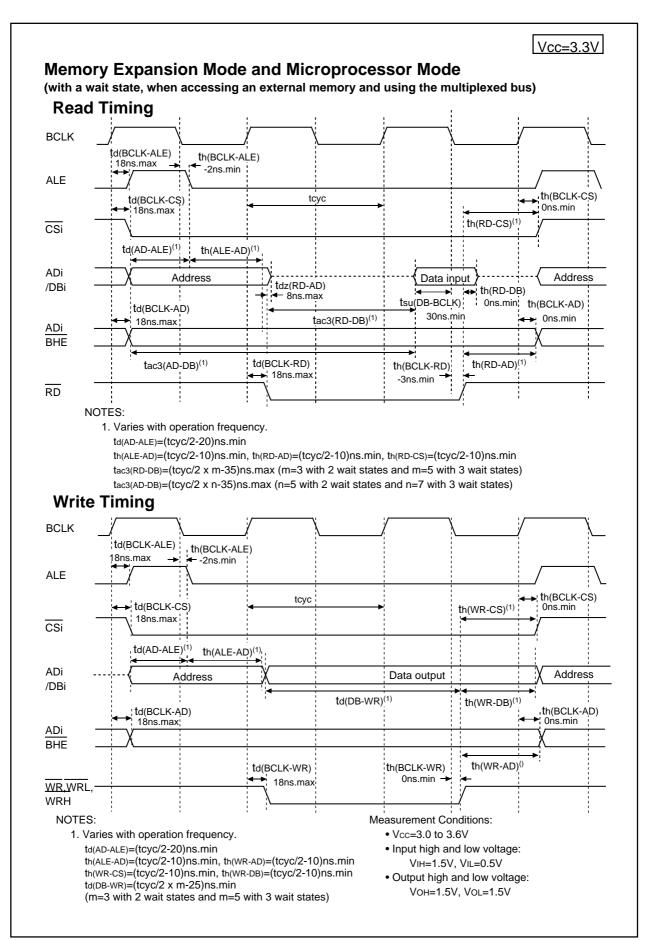

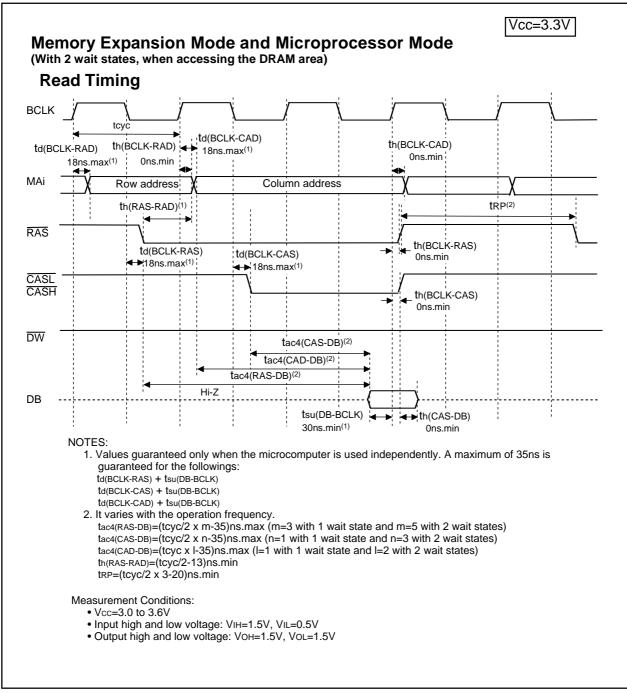

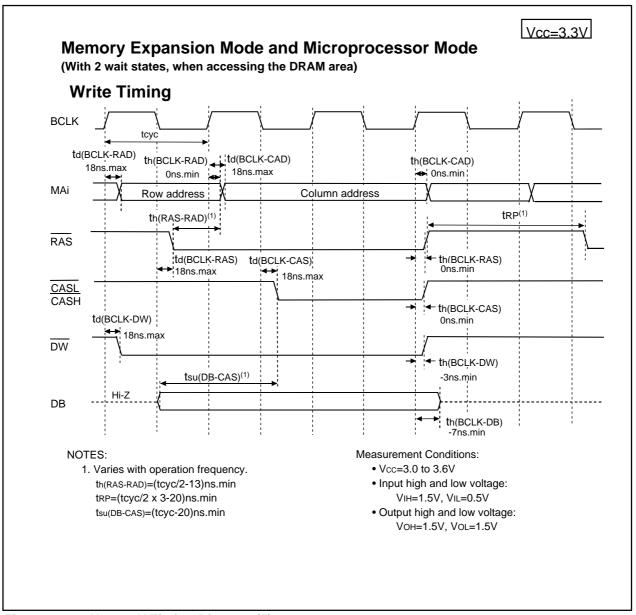

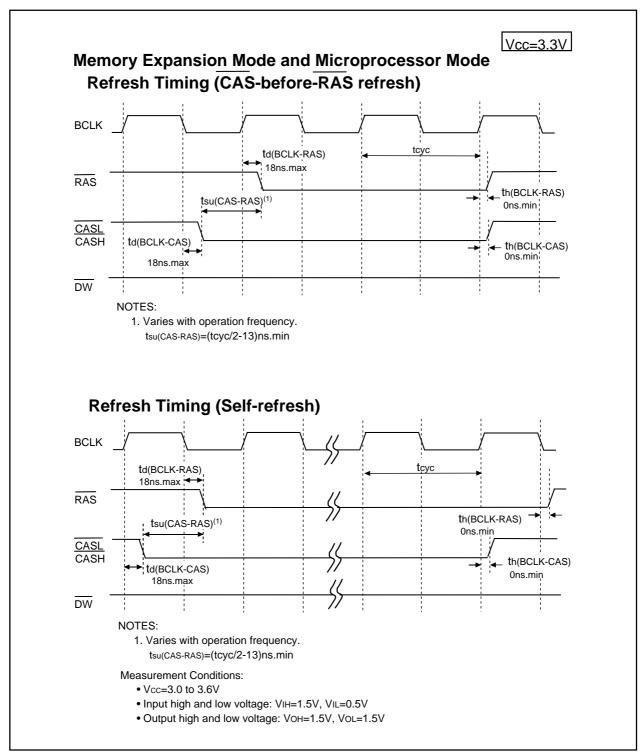

|    | 7.2.4 Bus Timing                                       | 58 |

|    | 7.2.5 ALE Signal                                       | 62 |

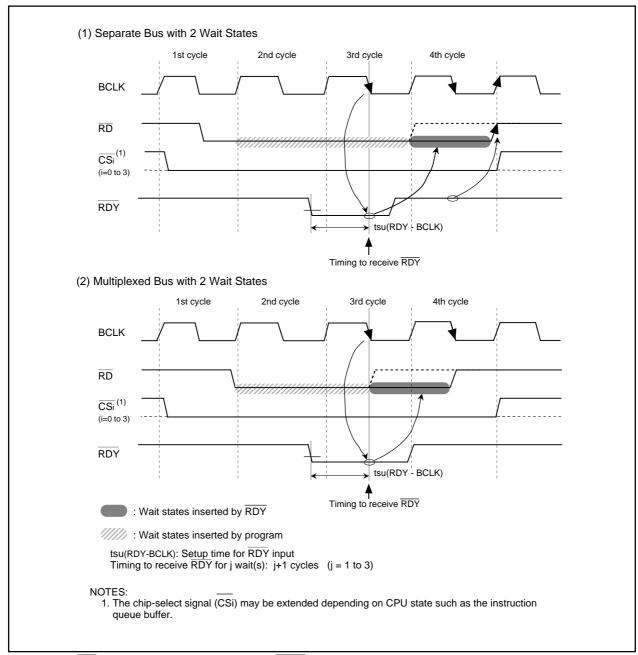

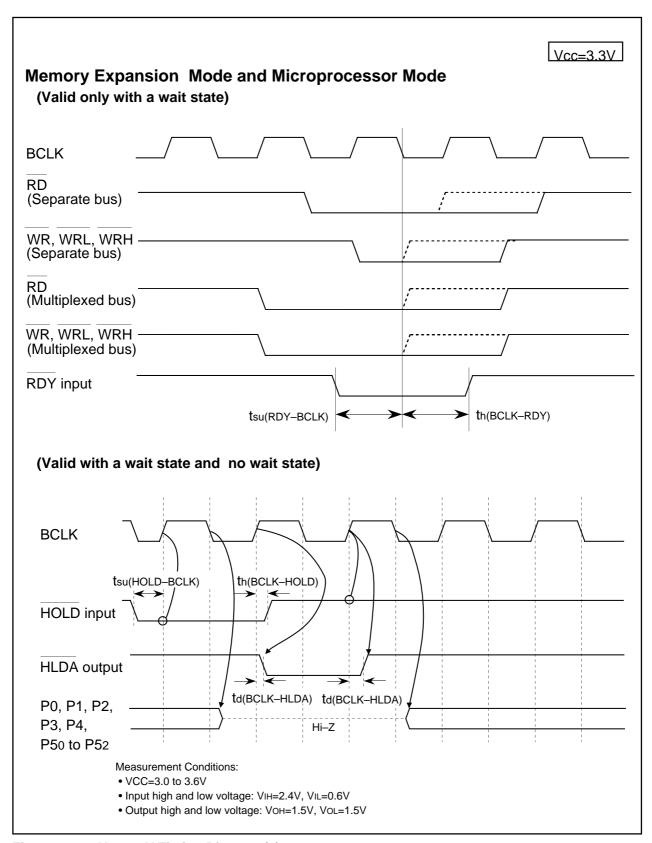

|    | 7.2.6 RDY Signal                                       | 62 |

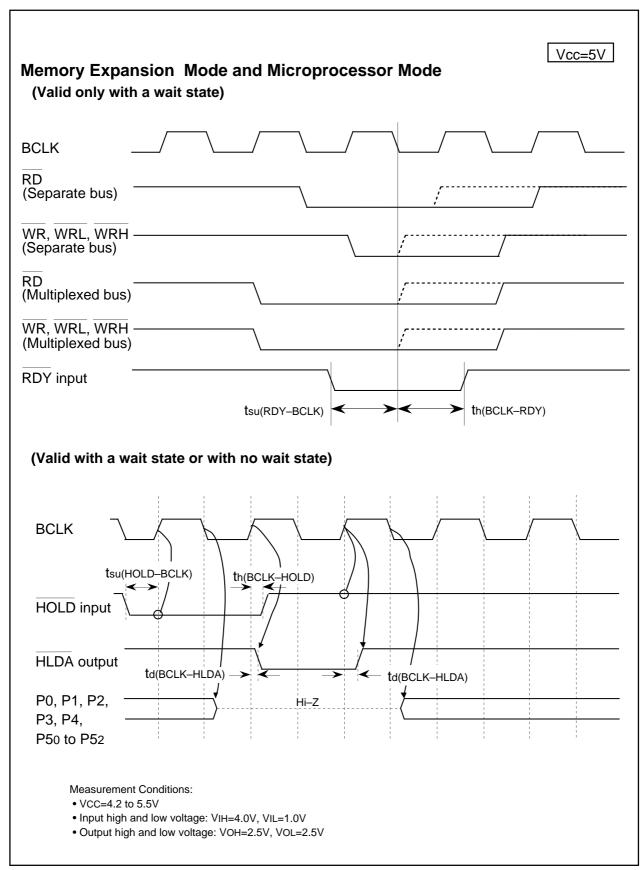

|    | 7.2.7 HOLD Signal                                      | 63 |

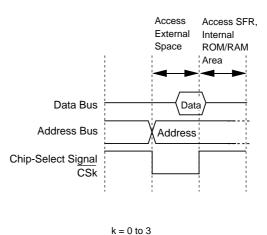

|    | 7.2.8 External Bus State when Accessing Internal Space | 64 |

|    | 7.2.9 BCLK Output                                      | 64 |

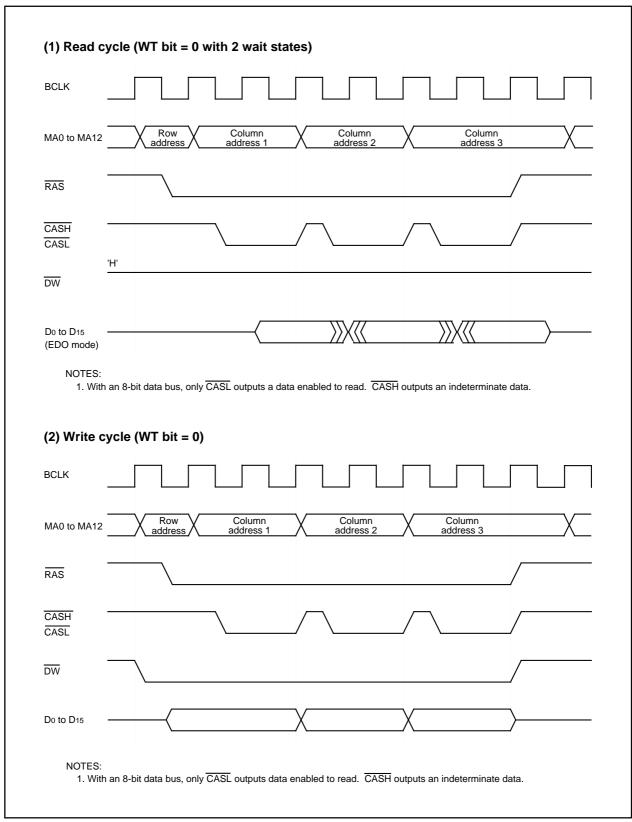

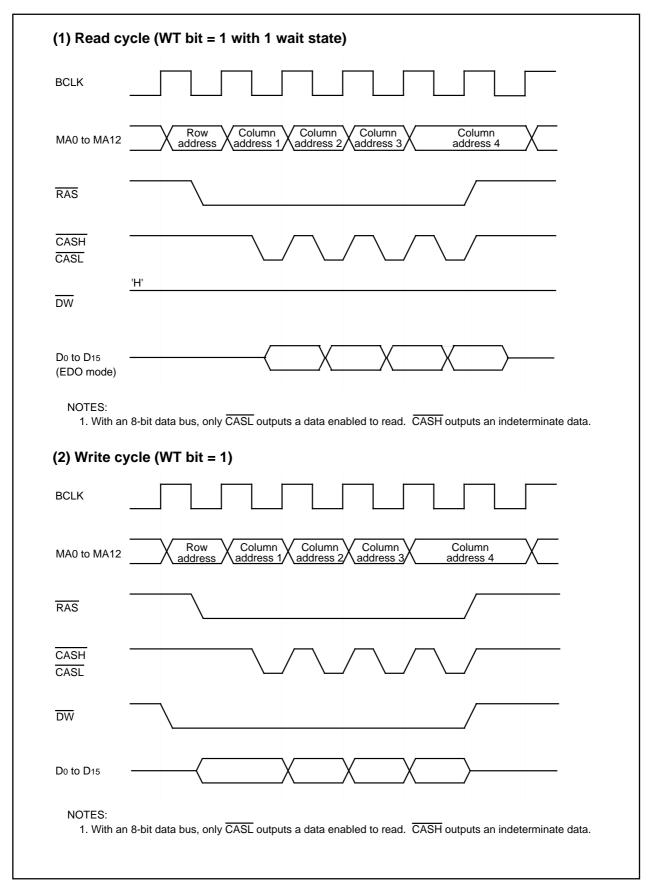

|    | 7.2.10 DRAM Control Signals (RAS, CASL, CASH and DW)   | 64 |

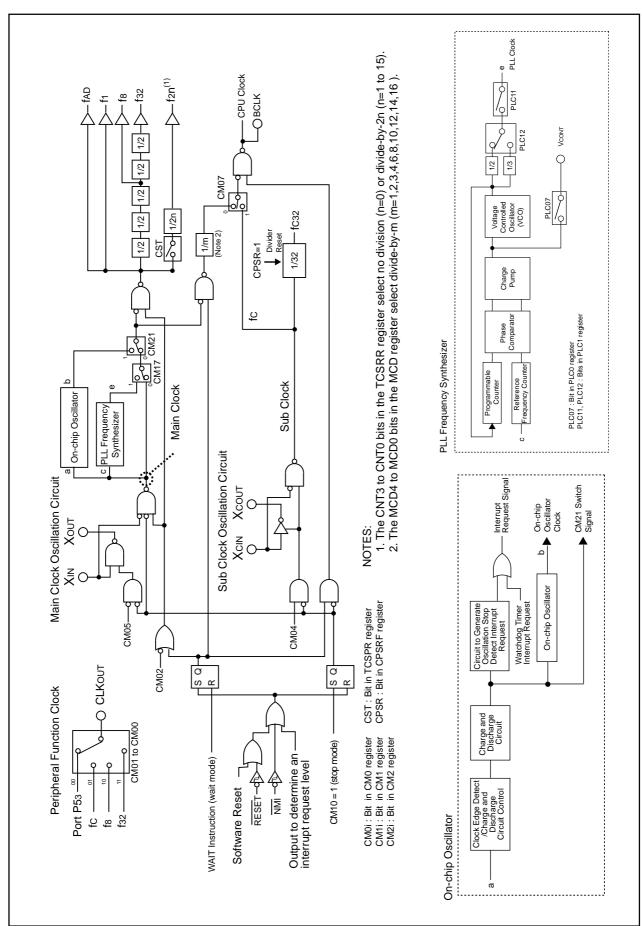

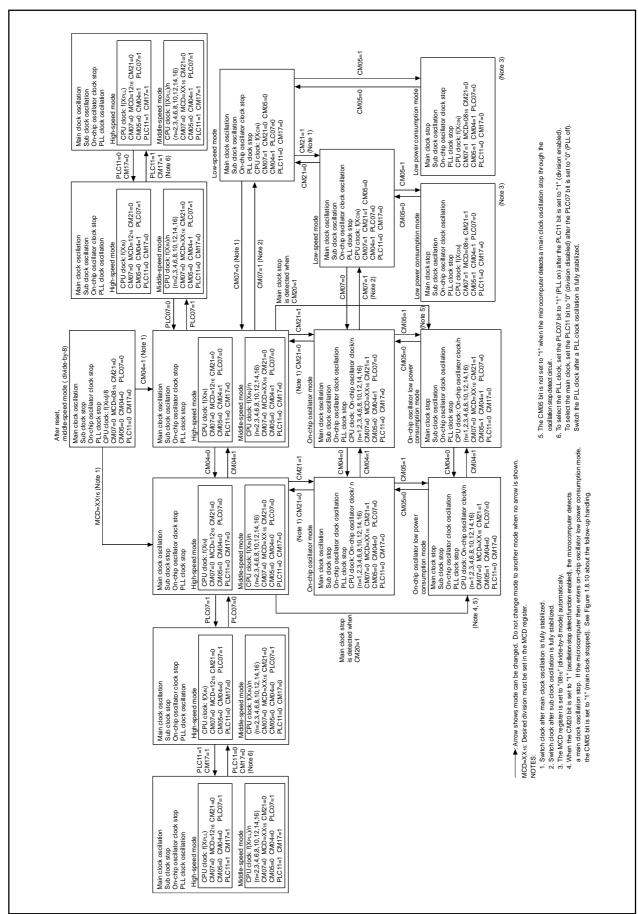

| 8. | Clock Generation Circuit                               | 65 |

|    | 8.1 Types of Clock Generation Circuits                 | 65 |

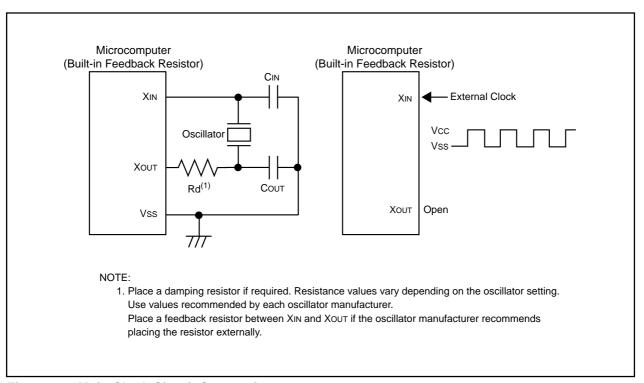

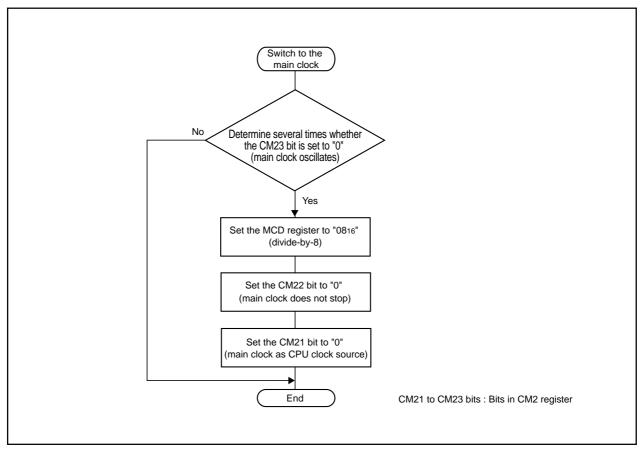

|    | 8.1.1 Main Clock                                       | 74 |

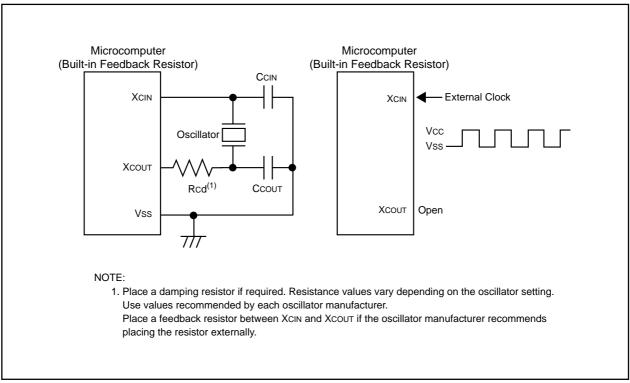

|    | 8.1.2 Sub Clock                                        | 75 |

|    | 8.1.3 On-chip Oscillator Clock                         | 76 |

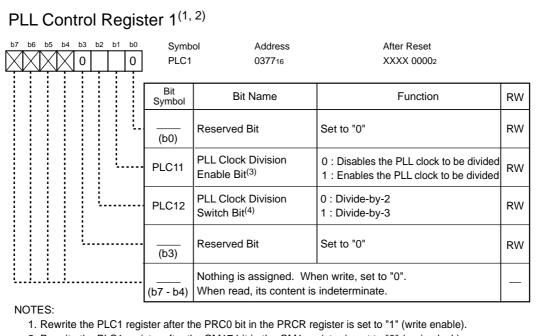

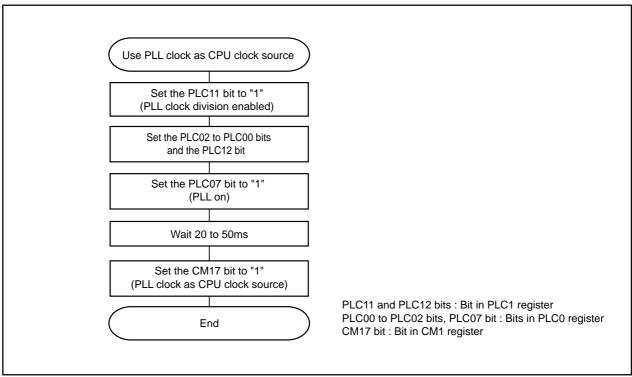

|    | 8.1.4 PLL Clock                                        | 77 |

|    | 8.2 CPU Clock and BCLK                                 | 79 |

|    | 8.3 Peripheral Function Clock                          | 79 |

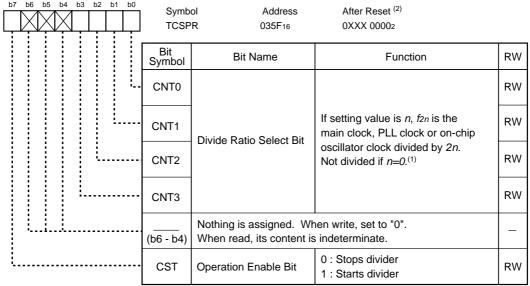

|    | 8.3.1 f1, f8, f32 and f2n                              | 79 |

|    | 8.3.2 fAD                                              | 79 |

|    | 8.3.3 fC <sub>32</sub>                                 | 80 |

|    | 8.4 Clock Output Function                              | 80 |

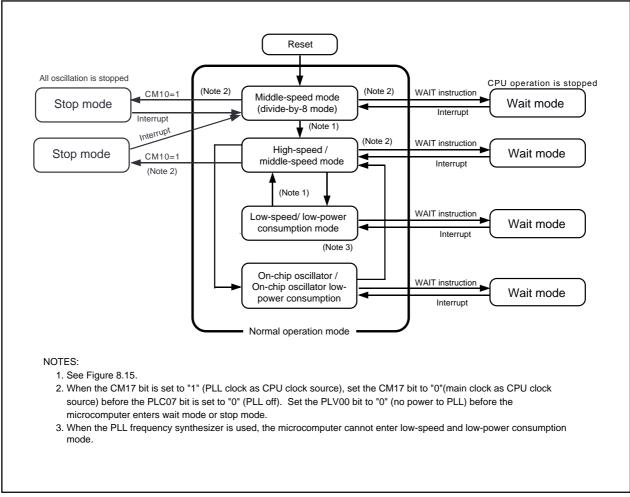

|    | 8.5 Power Consumption Control                          | 80 |

|    | 8.5.1 Normal Operation Mode                            | 81 |

|    | 8.5.2 Wait Mode                                        |    |

|    | 8.5.3 Stop Mode                                        | 84 |

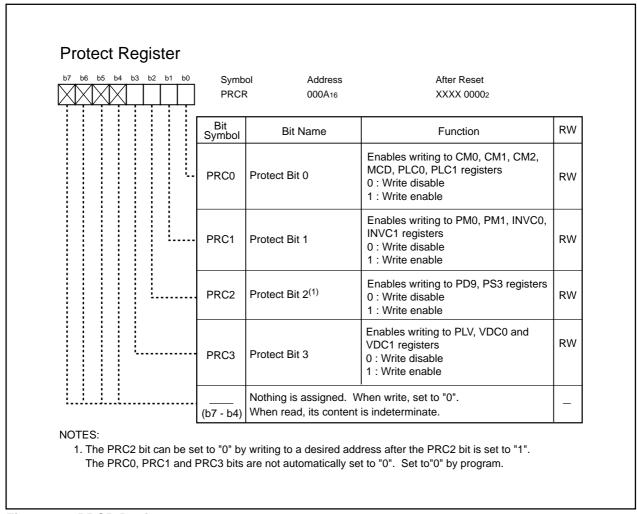

| 9  | Protection                                             | 88 |

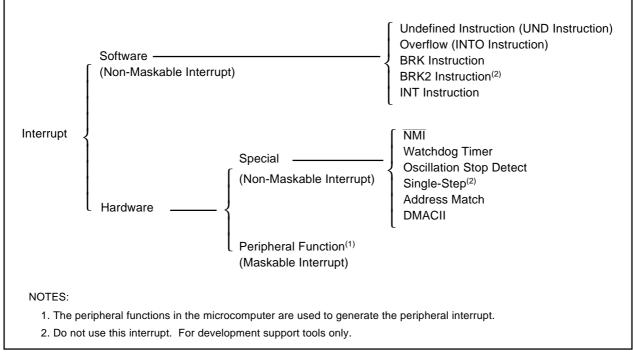

| 10. Interrupts                                    | 89            |

|---------------------------------------------------|---------------|

| 10.1 Types of Interrupts                          | 89            |

| 10.2 Software Interrupts                          |               |

| 10.2.1 Undefined Instruction Interrupt            | 89            |

| 10.2.2 Overflow Interrupt                         | 89            |

| 10.2.3 BRK Interrupt                              | 89            |

| 10.2.4 BRK2 Interrupt                             | 90            |

| 10.2.5 INT Instruction Interrupt                  | 90            |

| 10.3 Hardware Interrupts                          | 90            |

| 10.3.1 Special Interrupts                         | 90            |

| 10.3.2 Peripheral Function Interrupt              | 91            |

| 10.4 High-Speed Interrupt                         | 91            |

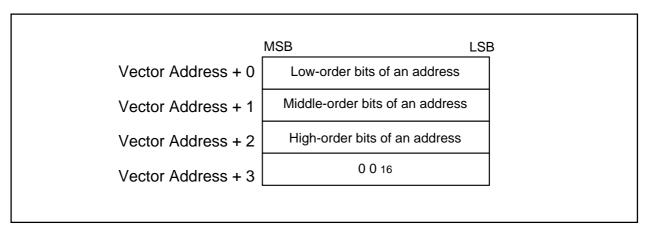

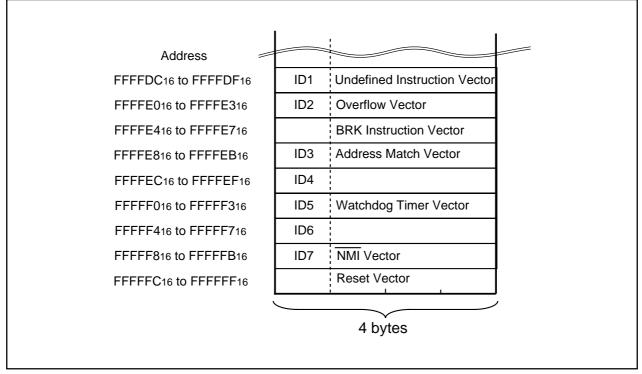

| 10.5 Interrupts and Interrupt Vectors             | 91            |

| 10.5.1 Fixed Vector Tables                        | 92            |

| 10.5.2 Relocatable Vector Tables                  | 92            |

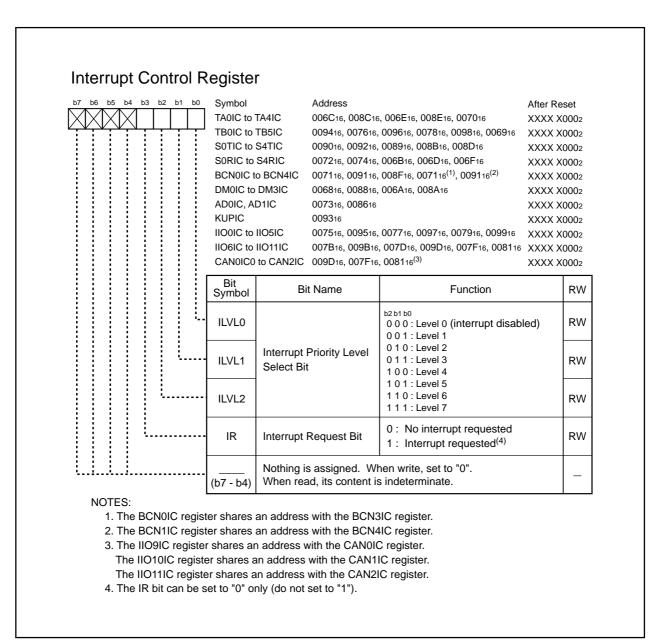

| 10.6 Interrupt Request Reception                  | 95            |

| 10.6.1 I Flag and IPL                             | 95            |

| 10.6.2 Interrupt Control Register and RLVL Regi   | ster95        |

| 10.6.3 Interrupt Sequence                         | 99            |

| 10.6.4 Interrupt Response Time                    | 100           |

| 10.6.5 IPL Change when Interrupt Request is Ac    | knowledged101 |

| 10.6.6 Saving a Register                          | 102           |

| 10.6.7 Restoration from Interrupt Routine         | 102           |

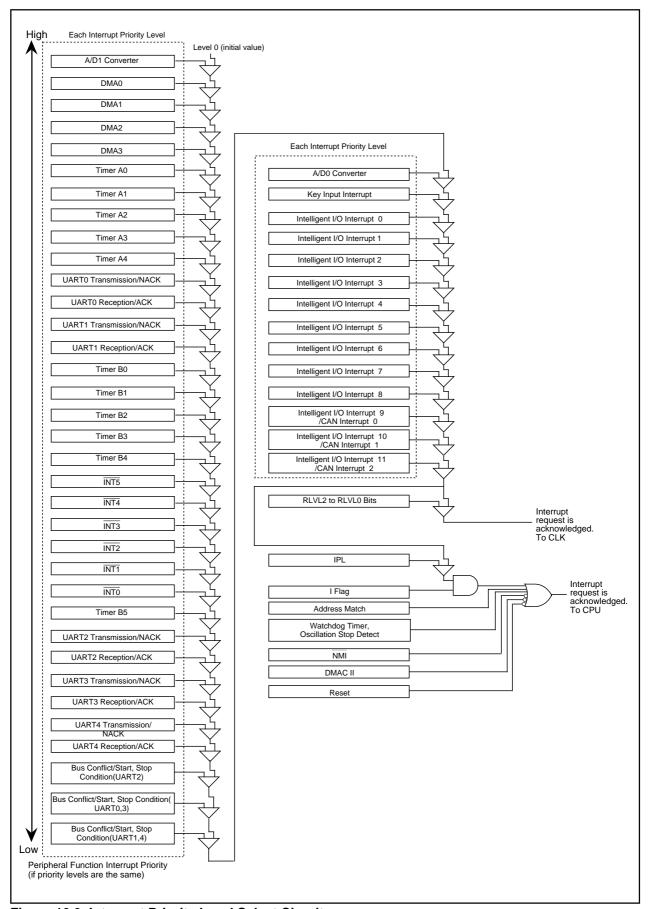

| 10.6.8 Interrupt Priority                         | 103           |

| 10.6.9 Interrupt Priority Level Select Circuit    |               |

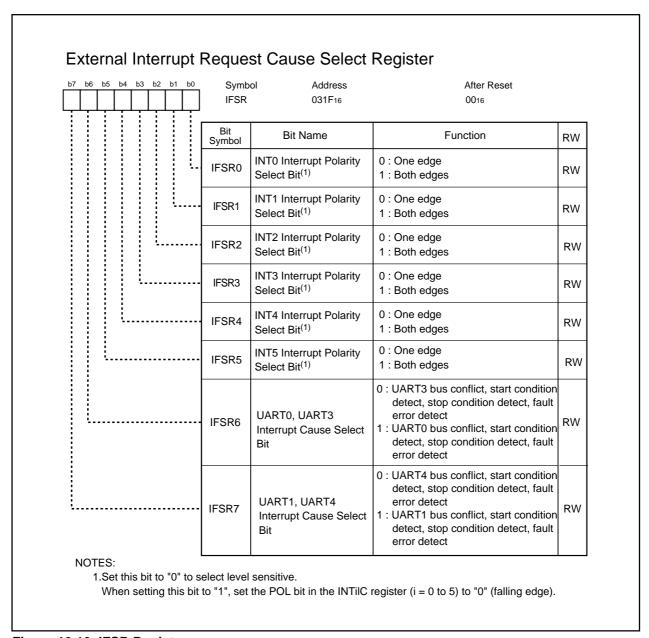

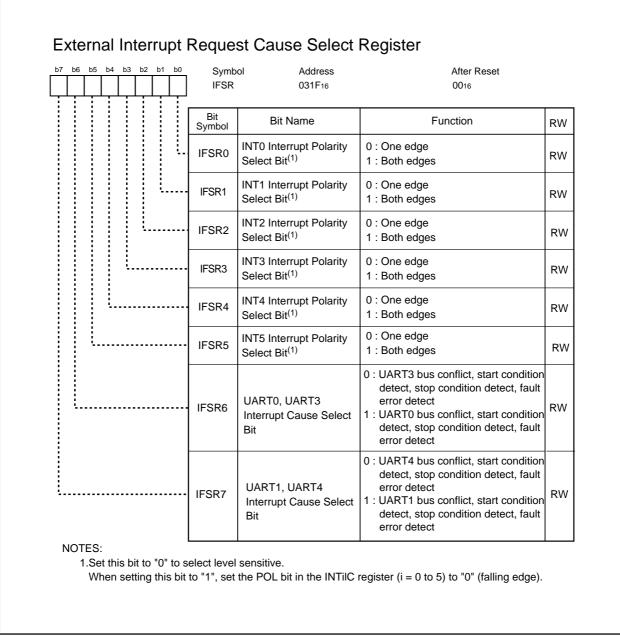

| 10.7 INT Interrupt                                | 105           |

| 10.8 NMI Interrupt                                | 106           |

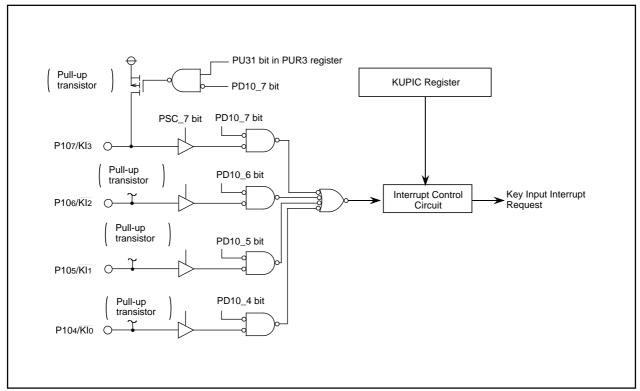

| 10.9 Key Input Interrupt                          | 106           |

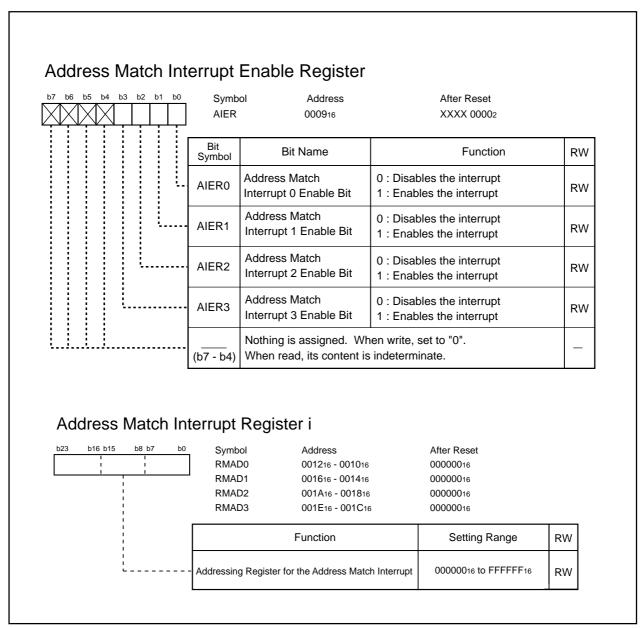

| 10.10 Address Match Interrupt                     |               |

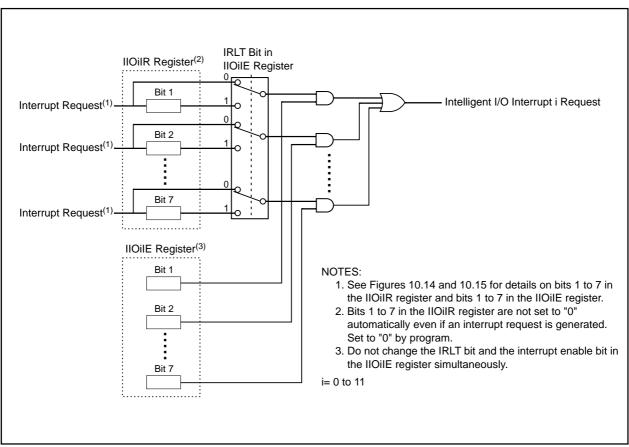

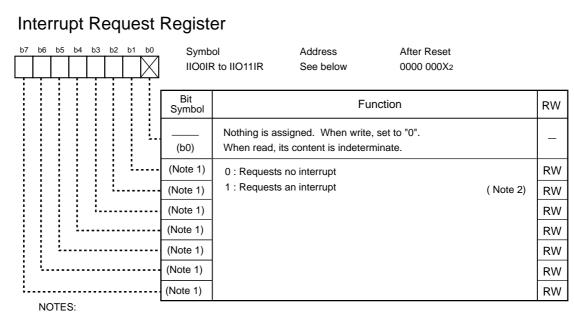

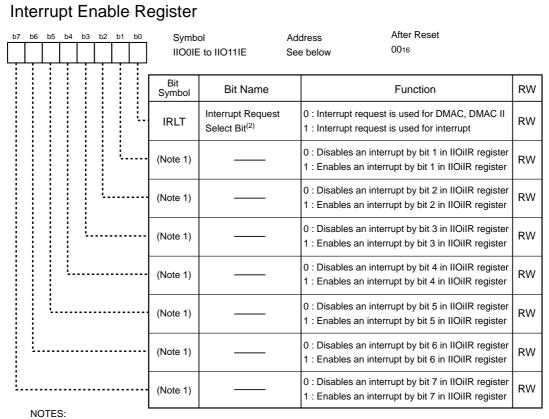

| 10.11 Intelligent I/O Interrupt and CAN Interrupt | 108           |

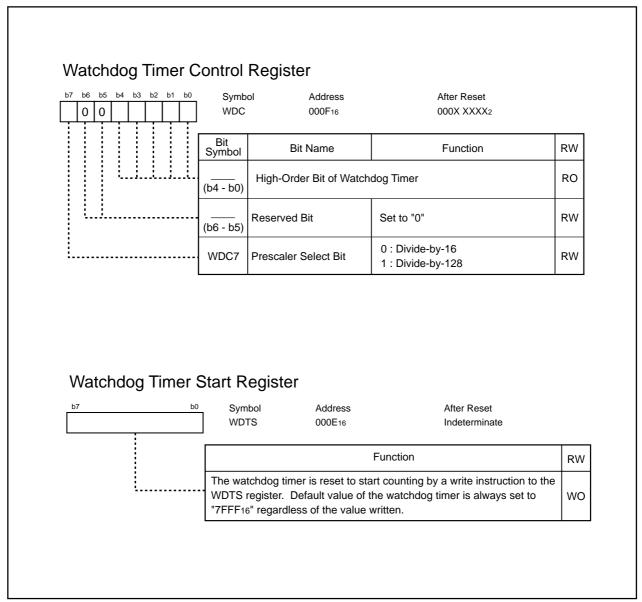

| 11. Watchdog Timer                                | 111           |

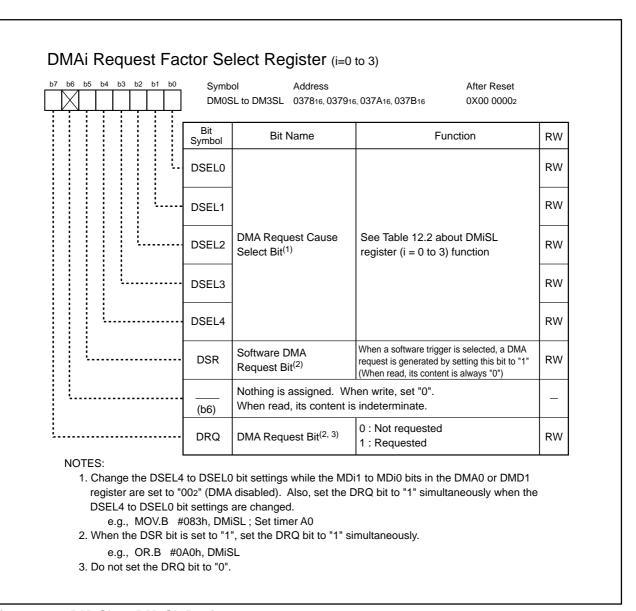

| 12. DMAC                                          | 4.4.4         |

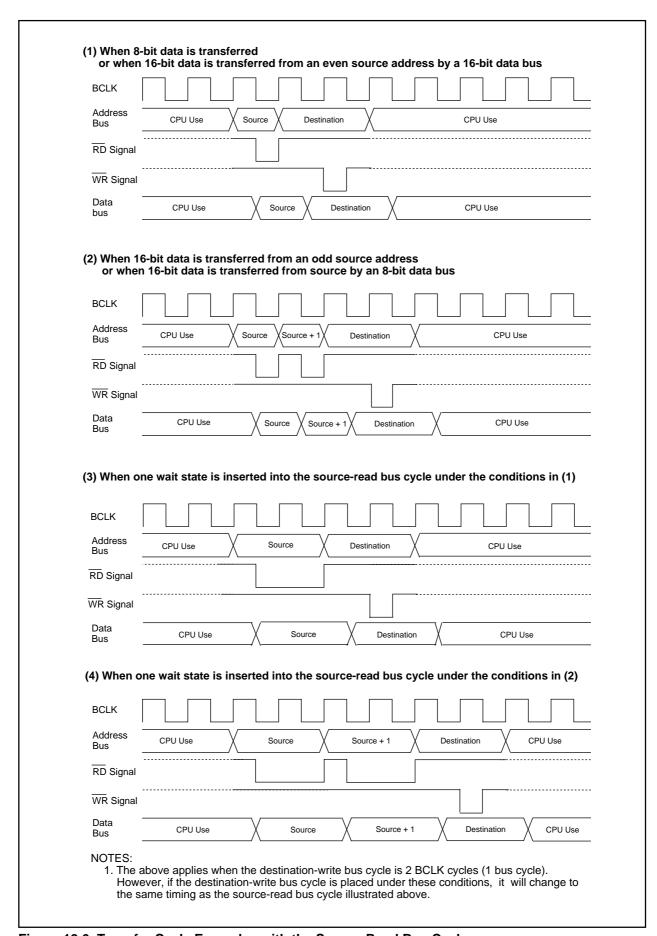

| 12.1 Transfer Cycles                              |               |

| 12.1.1 Effect of Source and Destination Address   |               |

| 12.1.2 Effect of the DS Register                  |               |

| 12.1.3 Effect of Software Wait State              |               |

| 12.1.4 Effect of RDY Signal                       |               |

| 12.2 DMAC Transfer Cycles                                     | 123 |

|---------------------------------------------------------------|-----|

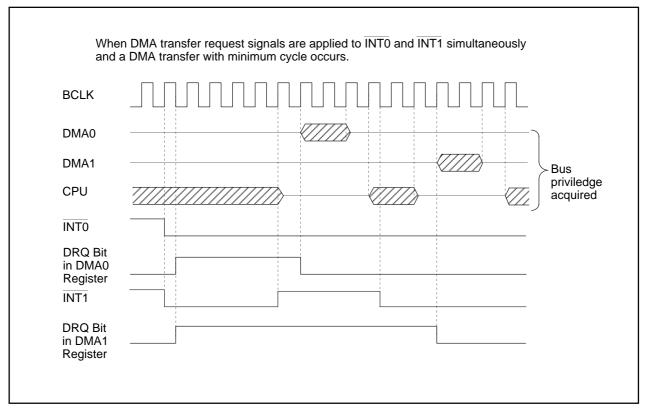

| 12.3 Channel Priority and DMA Transfer Timing                 | 123 |

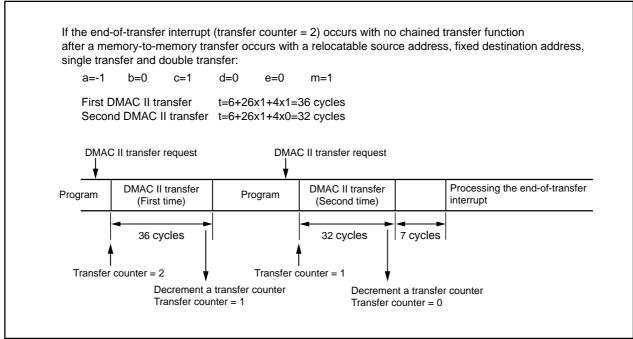

| 13. DMAC II                                                   | 125 |

| 13.1 DMAC II Settings                                         |     |

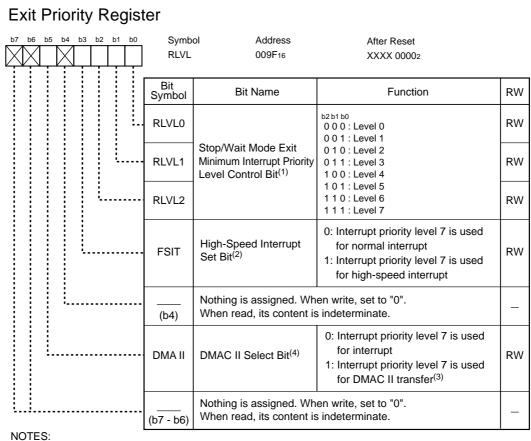

| 13.1.1 RLVL Register                                          |     |

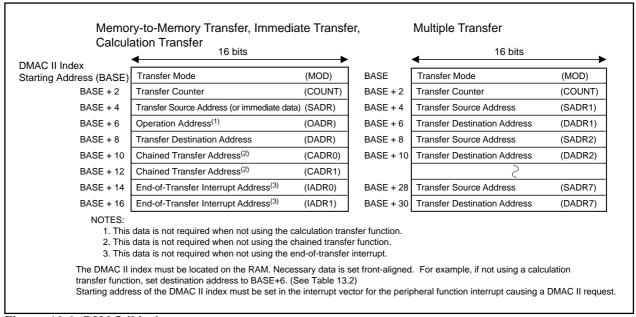

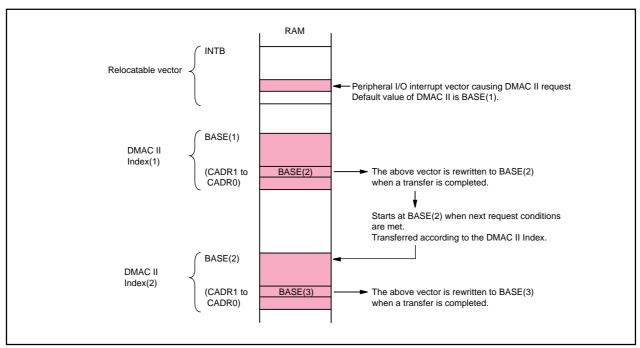

| 13.1.2 DMAC II Index                                          |     |

| 13.1.3 Interrupt Control Register for the Peripheral Function | 129 |

| 13.1.4 Relocatable Vector Table for the Peripheral Function   |     |

| 13.1.5 IRLT Bit in the IIOiIE Register (i=0 to 11)            |     |

| 13.2 DMAC II Performance                                      |     |

| 13.3 Transfer Data                                            | 129 |

| 13.3.1 Memory-to-Memory Transfer                              | 129 |

| 13.3.2 Immediate Data Transfer                                | 130 |

| 13.3.3 Calculation Transfer                                   | 130 |

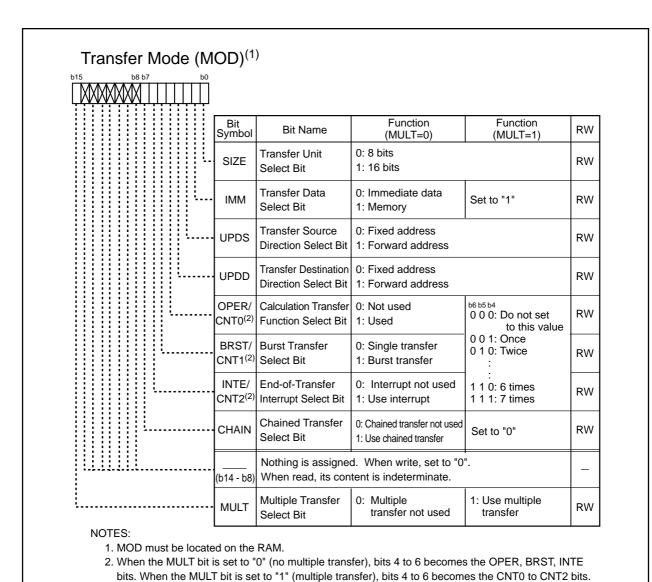

| 13.4 Transfer Modes                                           | 130 |

| 13.4.1 Single Transfer                                        | 130 |

| 13.4.2 Burst Transfer                                         | 130 |

| 13.4.3 Multiple Transfer                                      | 130 |

| 13.4.4 Chained Transfer                                       | 131 |

| 13.4.5 End-of-Transfer Interrupt                              | 131 |

| 13.5 Execution Time                                           | 132 |

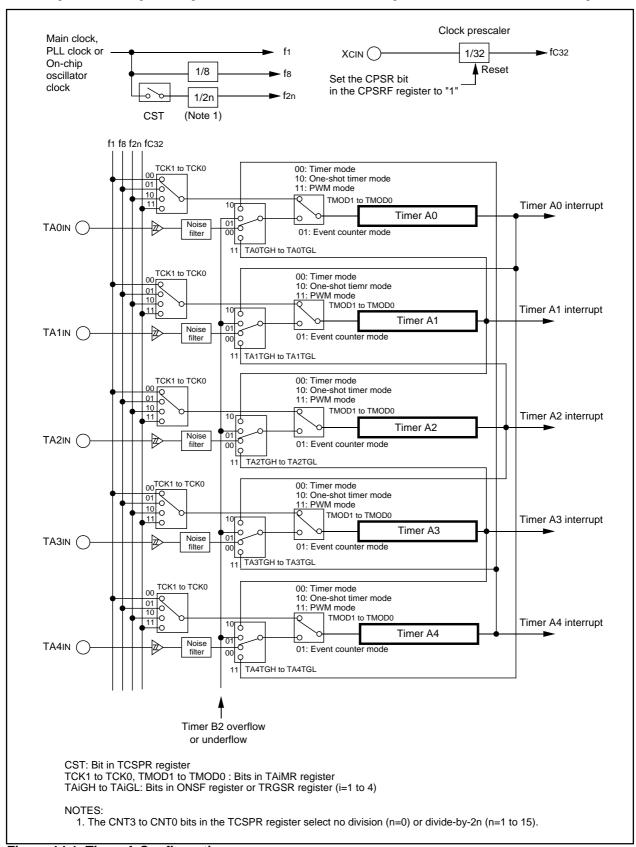

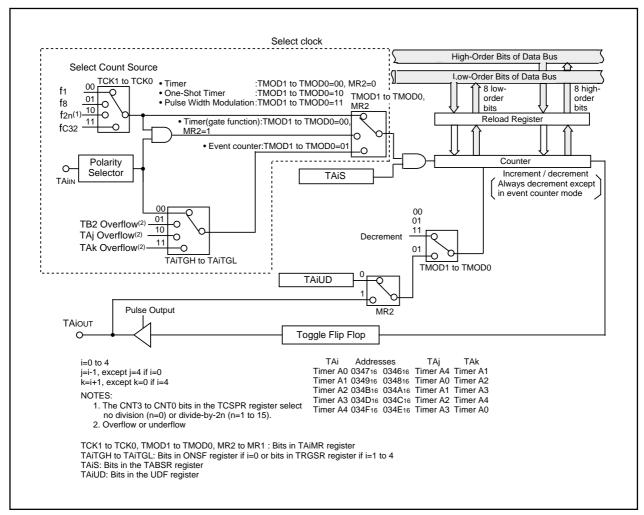

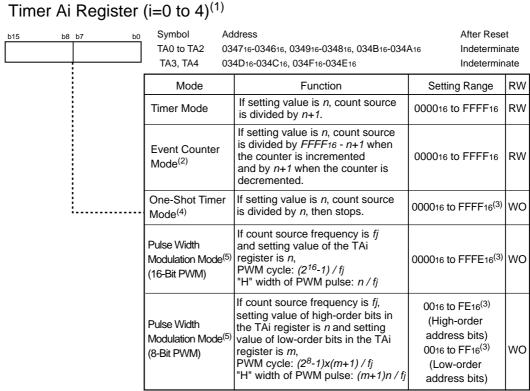

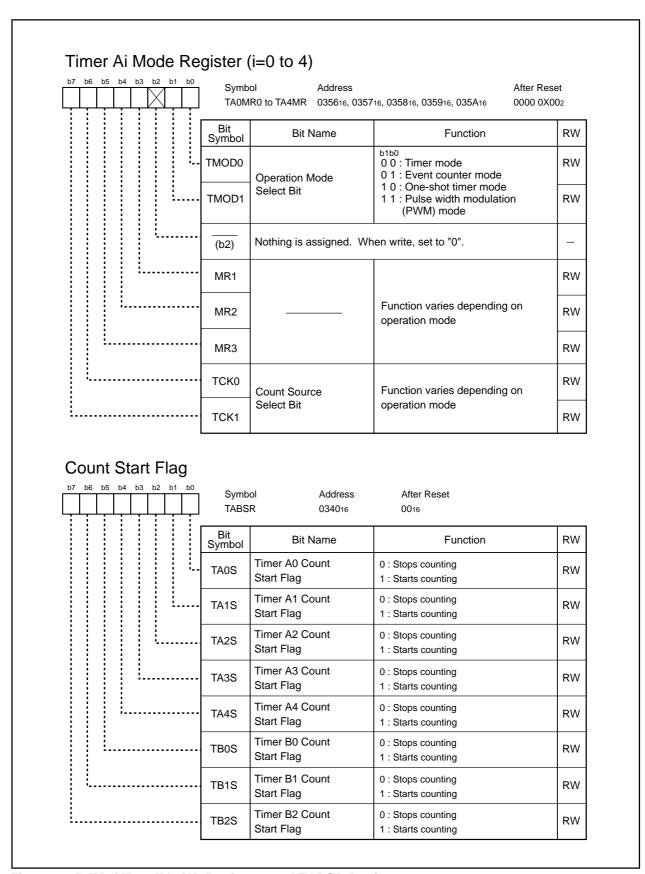

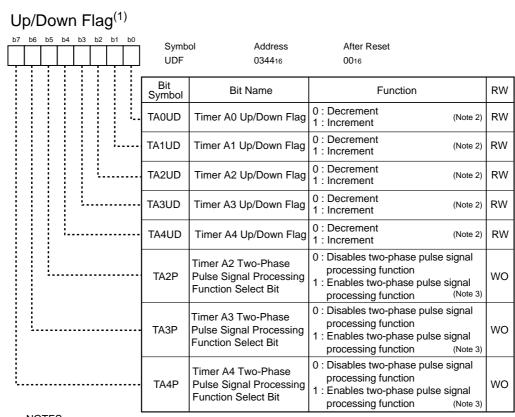

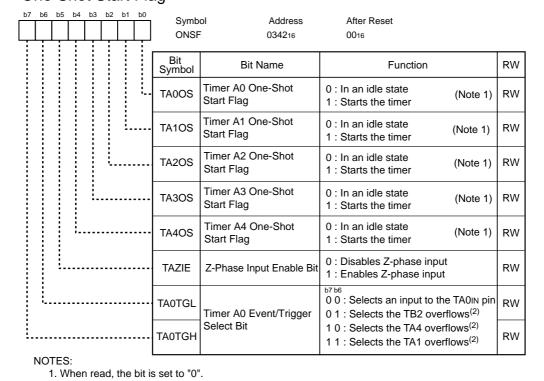

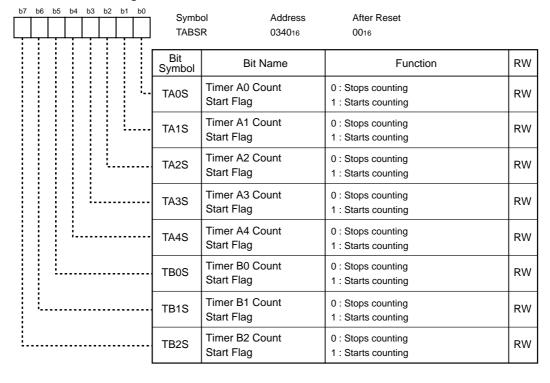

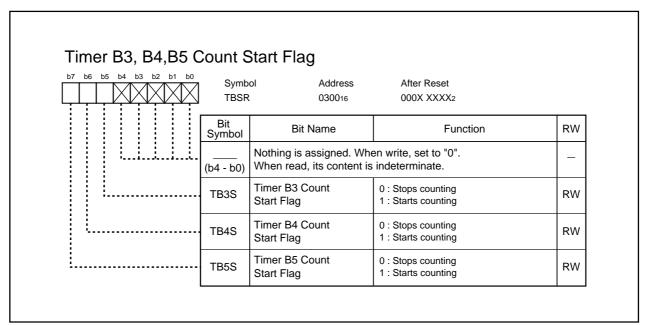

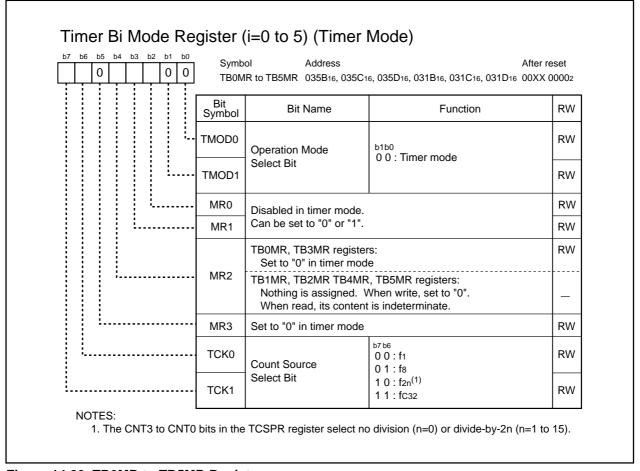

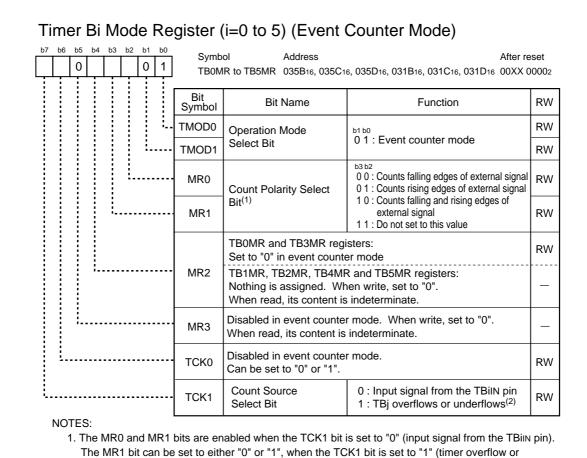

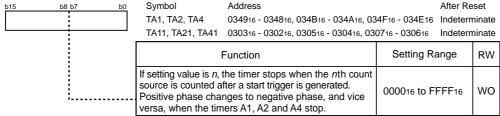

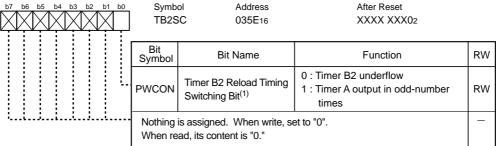

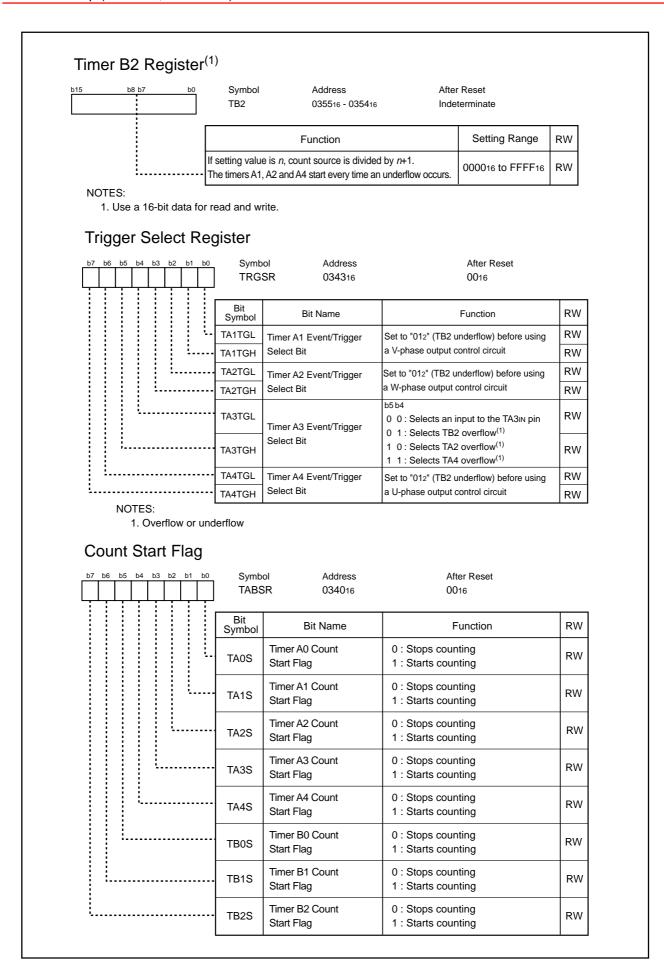

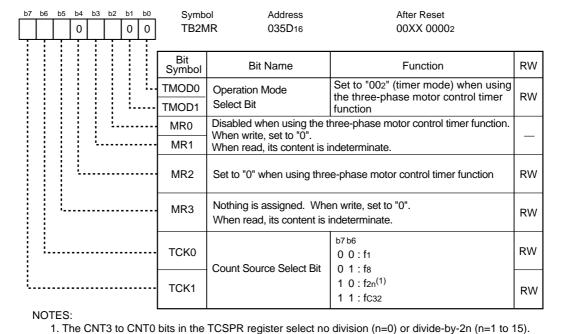

| 14. Timer                                                     | 133 |

| 14.1 Timer A                                                  |     |

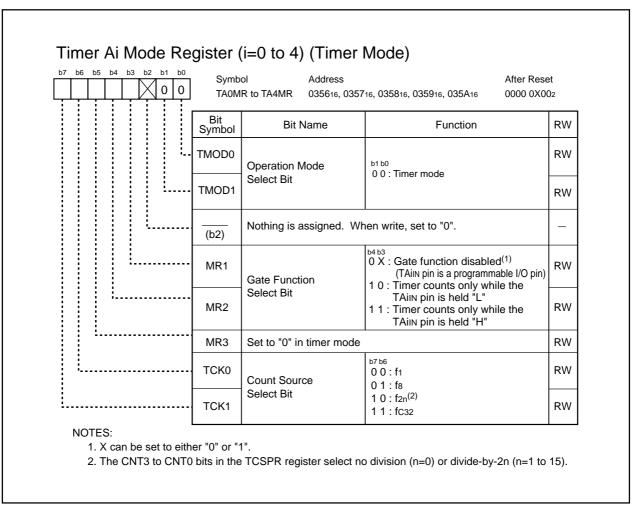

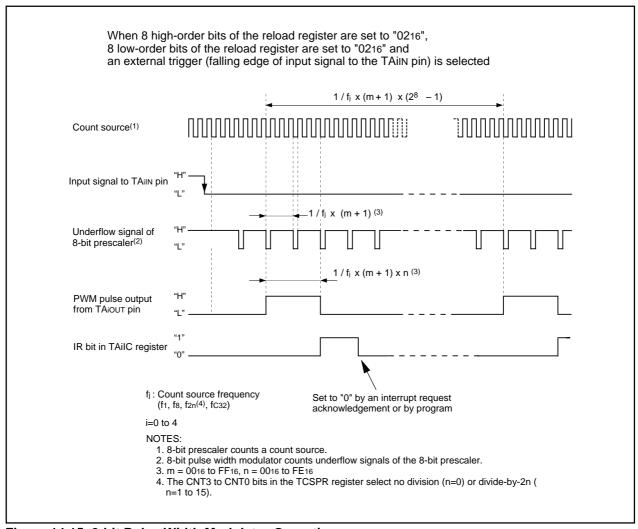

| 14.1.1 Timer Mode                                             | 141 |

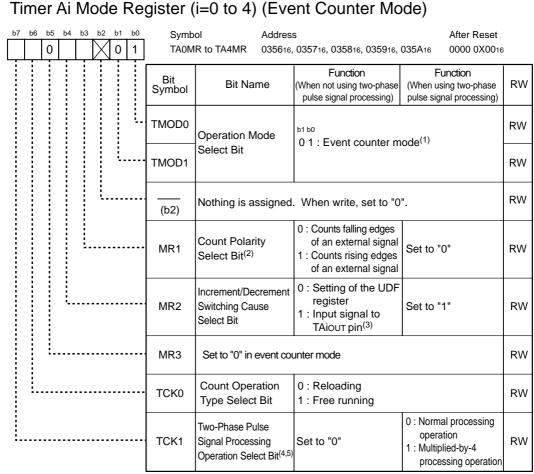

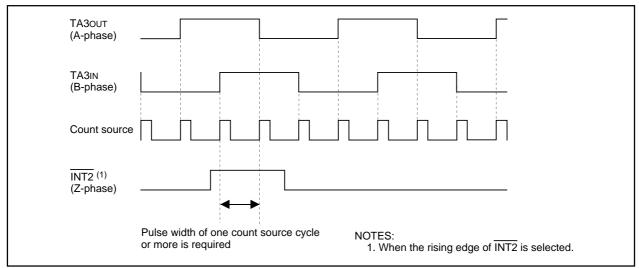

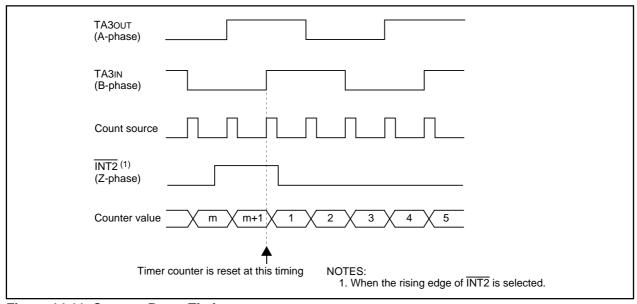

| 14.1.2 Event Counter Mode                                     | 143 |

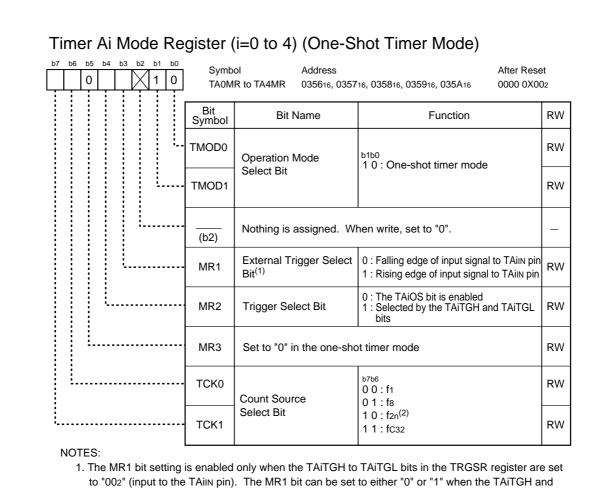

| 14.1.3 One-shot Timer Mode                                    | 147 |

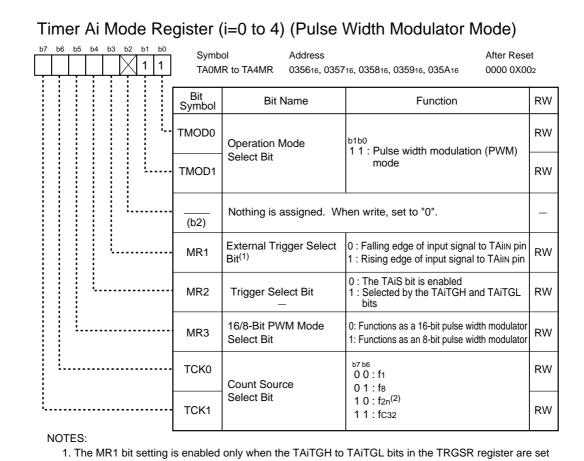

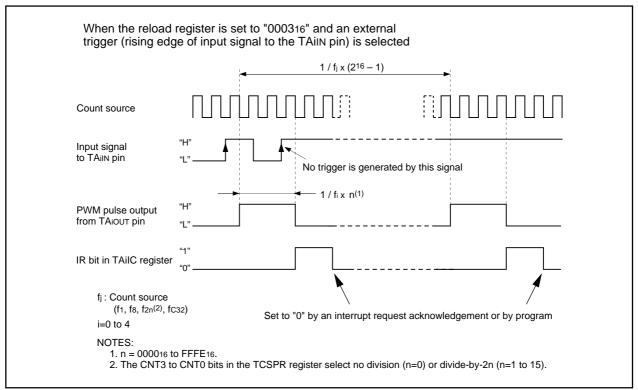

| 14.1.4 Pulse Width Modulation Mode                            | 149 |

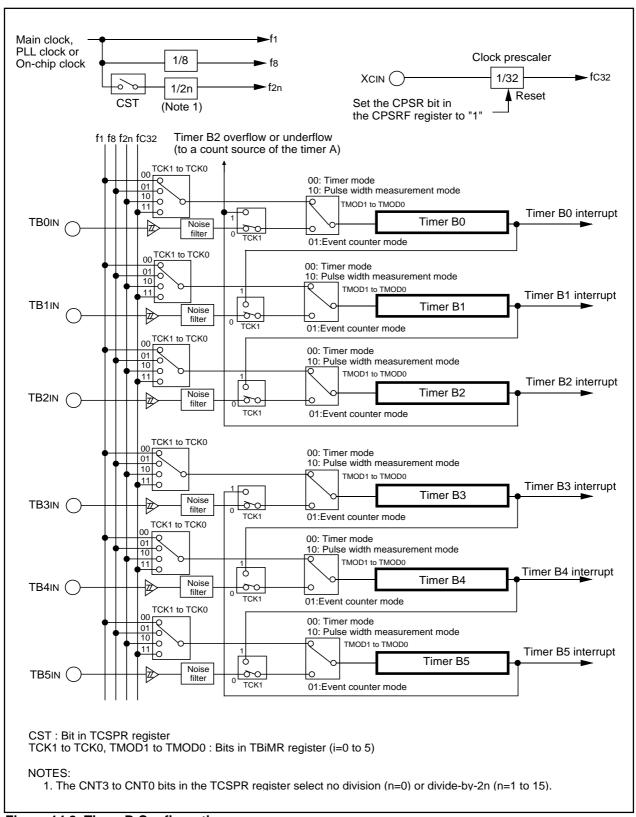

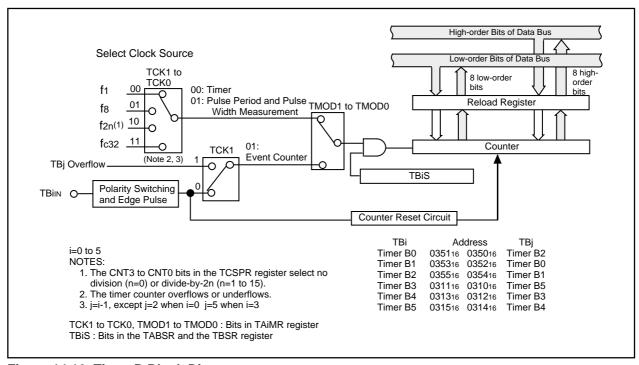

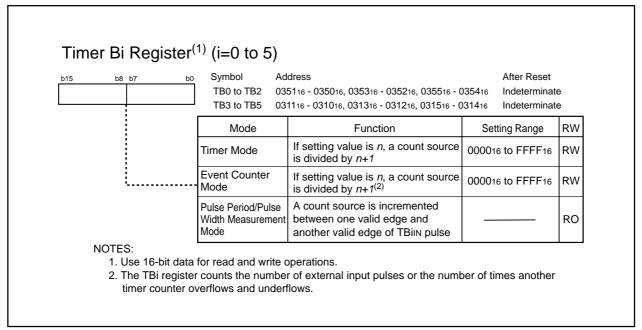

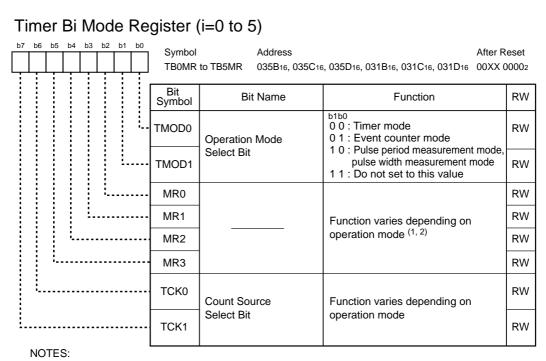

| 14.2 Timer B                                                  | 152 |

| 14.2.1 Timer Mode                                             | 155 |

| 14.2.2 Event Counter Mode                                     | 156 |

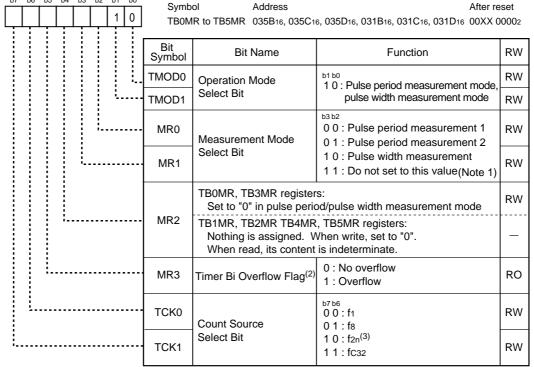

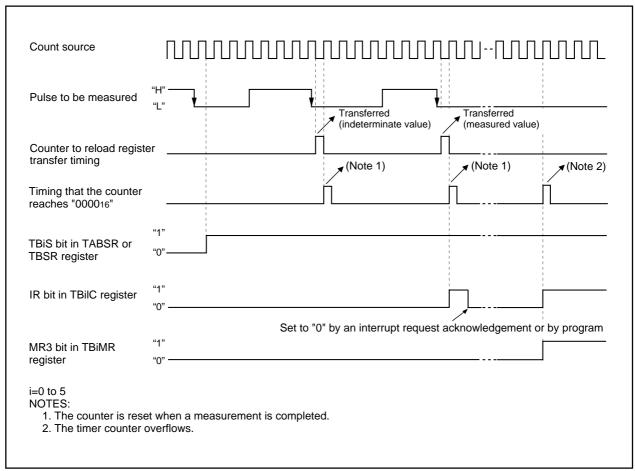

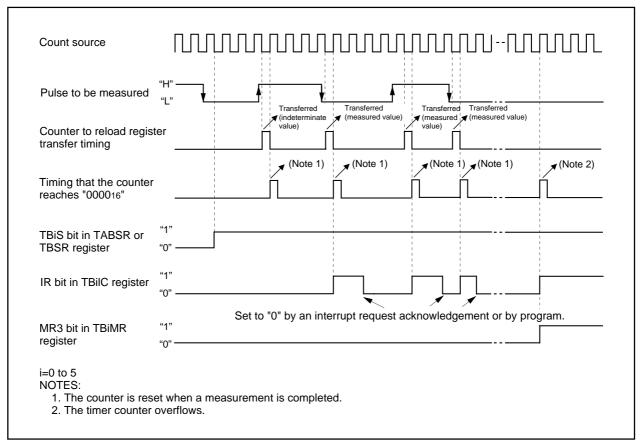

| 14.2.3 Pulse Period/Pulse Width Measurement Mode              | 158 |

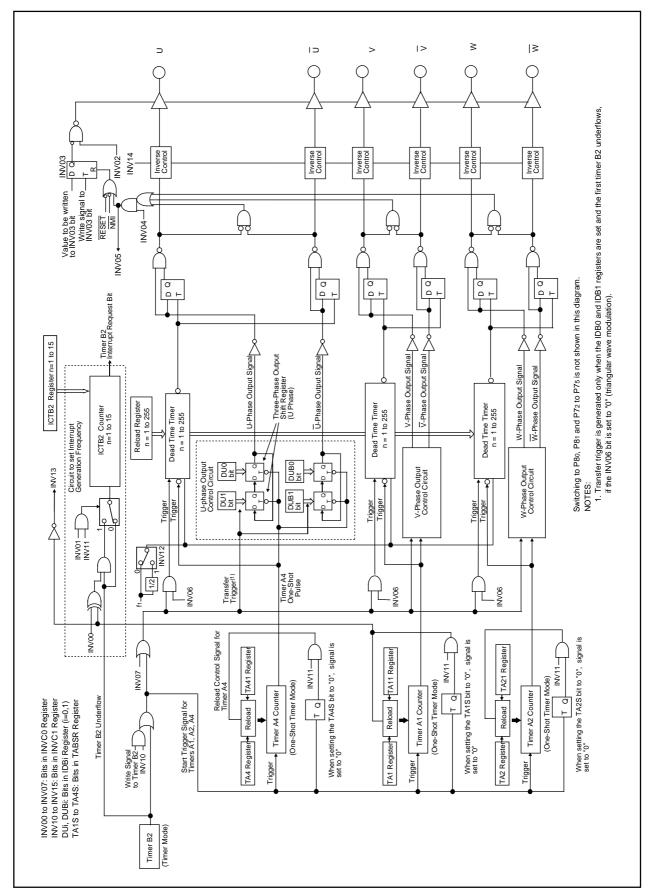

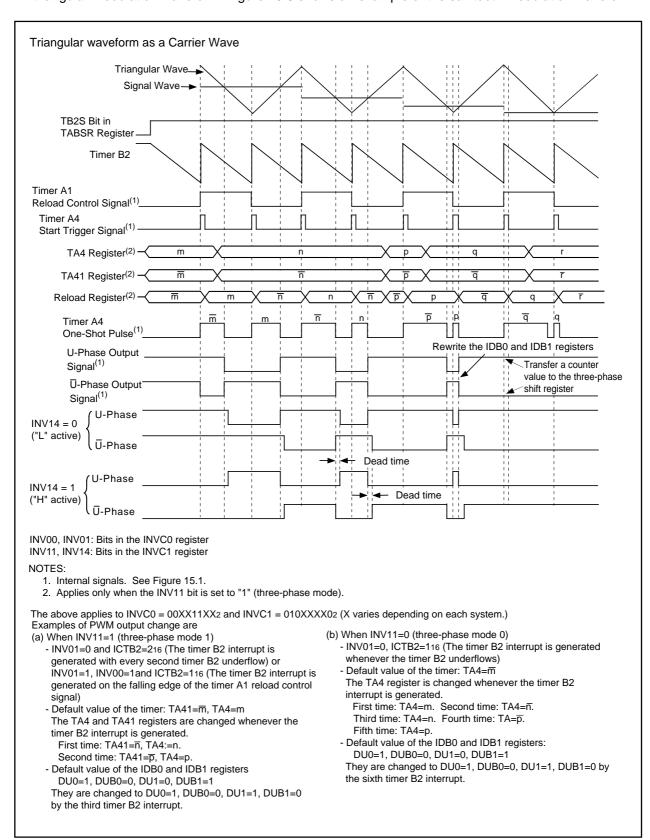

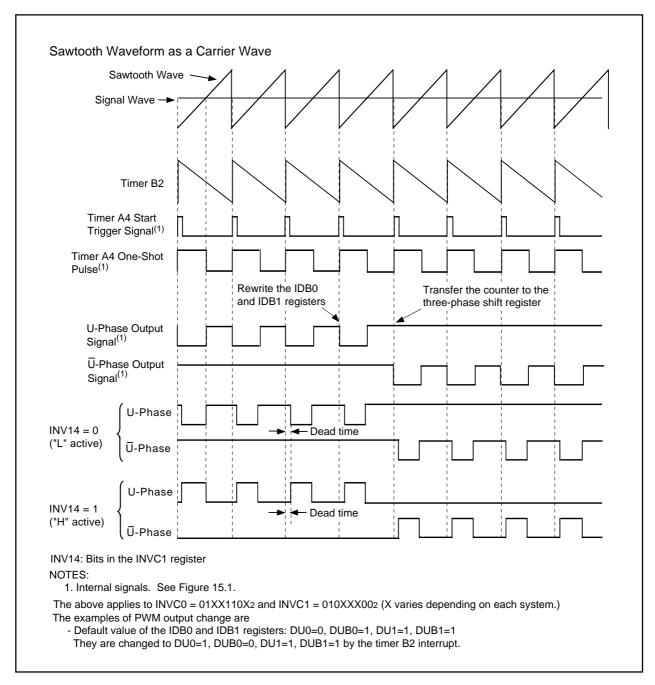

| 15. Three-Phase Motor Control Timer Functions                 | 161 |

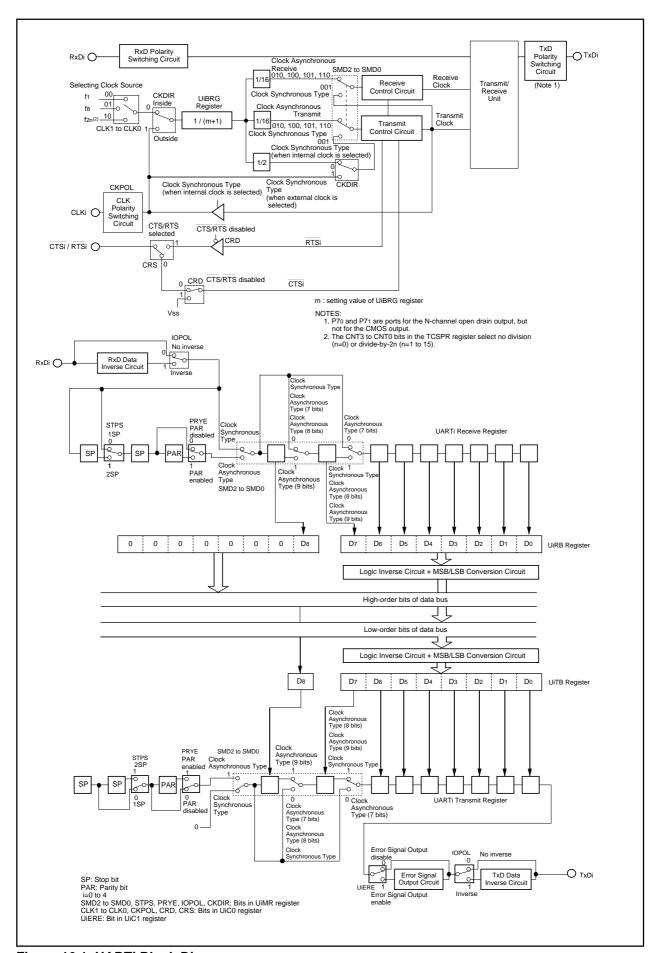

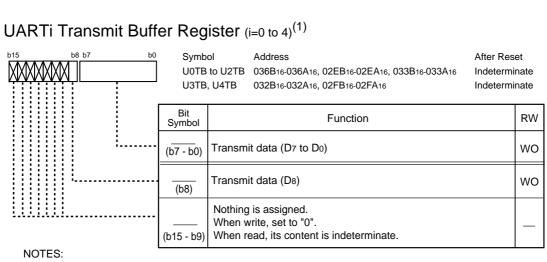

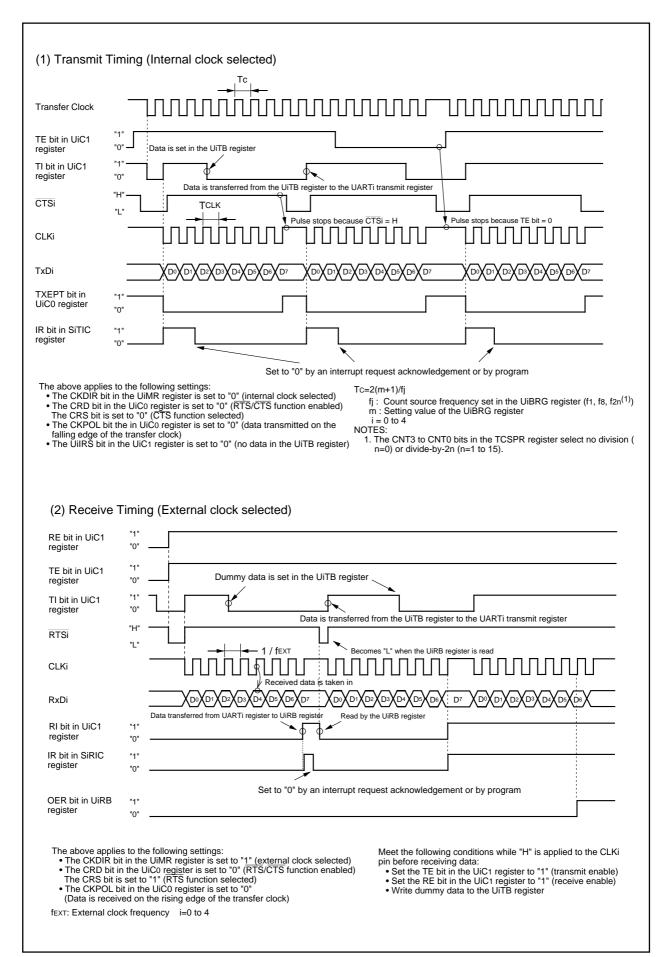

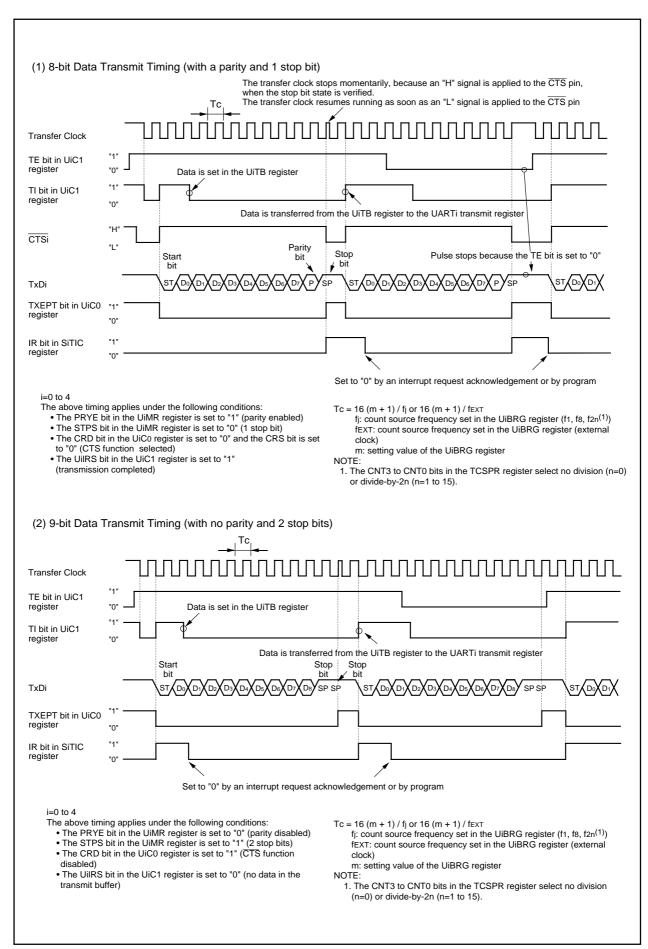

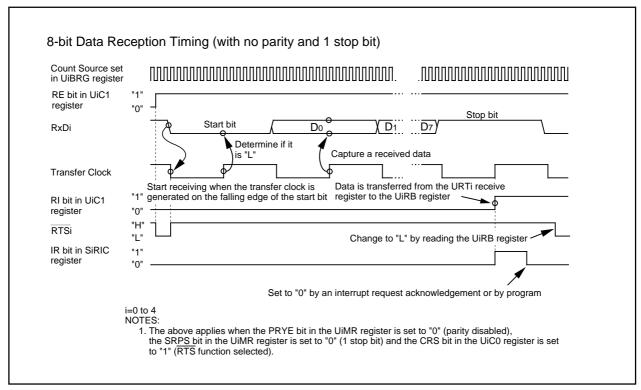

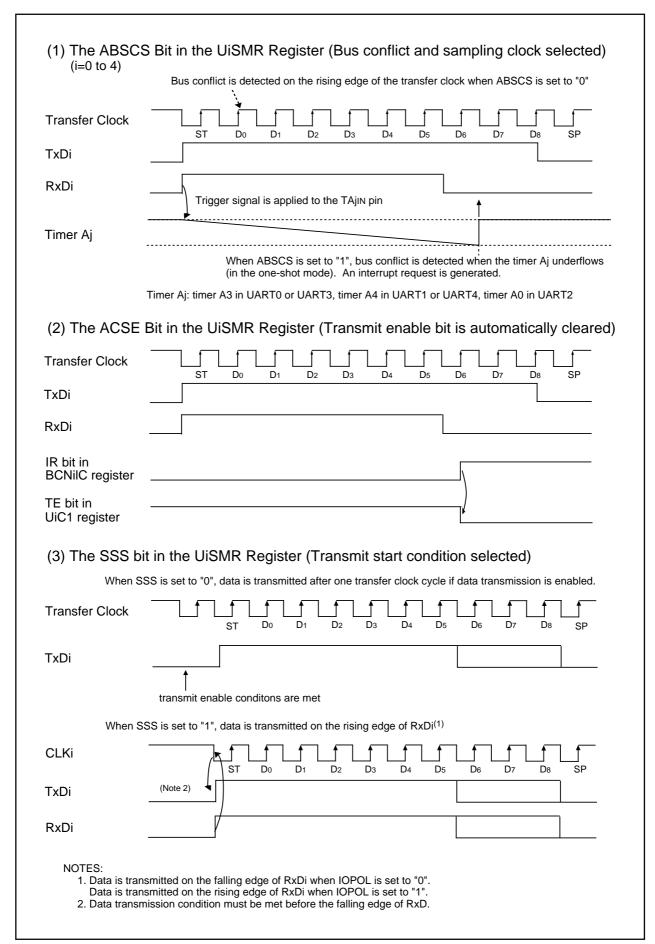

| 16. Serial I/O                                                |     |

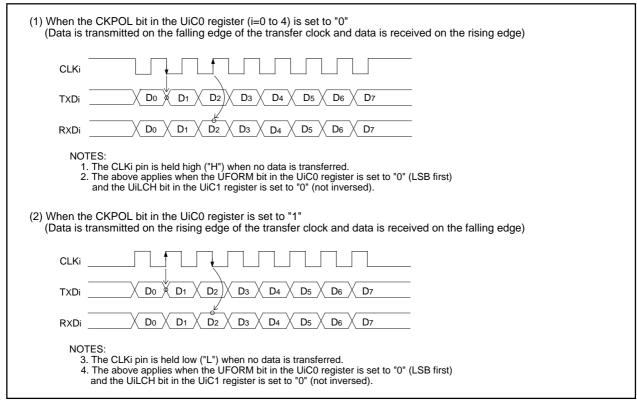

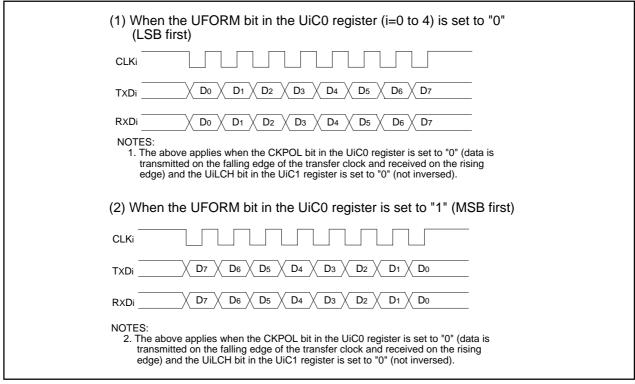

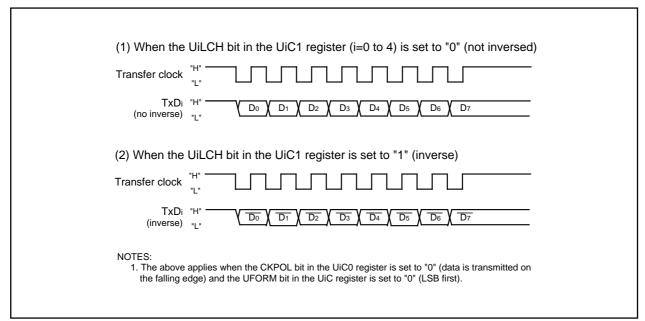

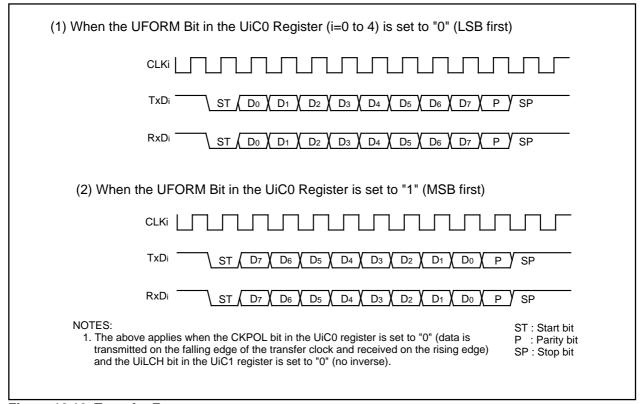

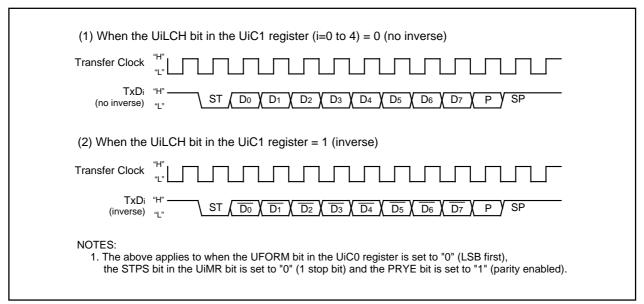

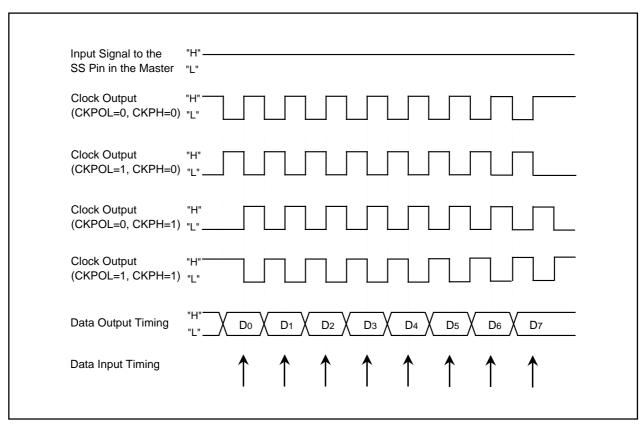

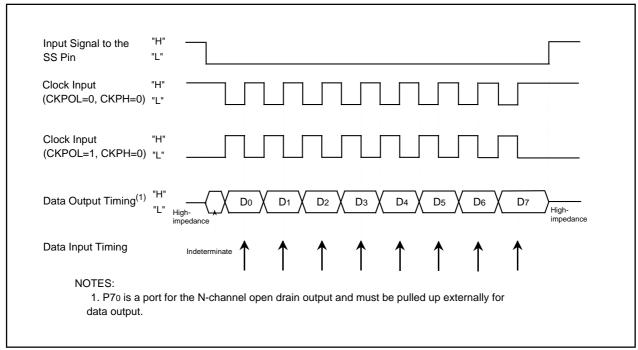

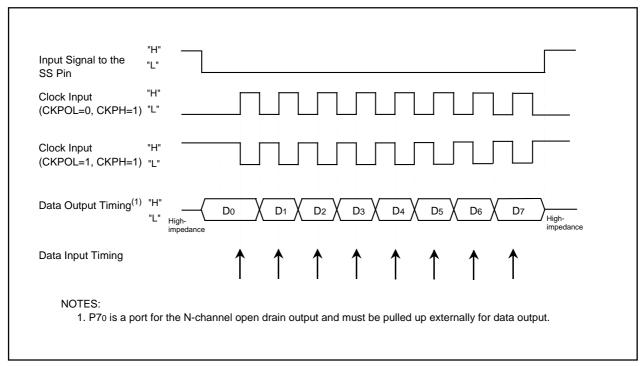

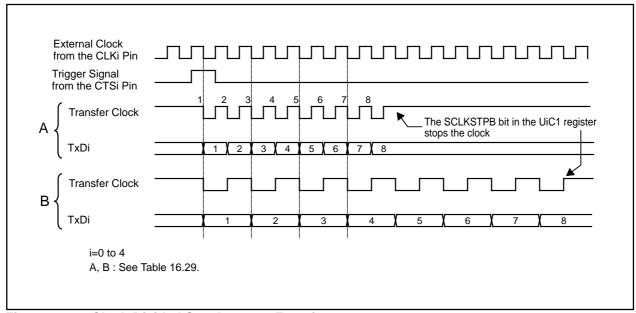

| 16.1 Clock Synchronous Serial I/O Mode                        |     |

| 16.1.1 Selecting CLK Polarity                                 |     |

| 16.1.1 Selecting CLK Polarity                                 |     |

| 16.1.2 Selecting LSB First of MSB First                       |     |

| 16.1.4 Serial Data Logic Inverse                              |     |

| 10.1.7 Deliai Dala Edyic IIIVel 36                            |     |

|                                                     | 188                      |

|-----------------------------------------------------|--------------------------|

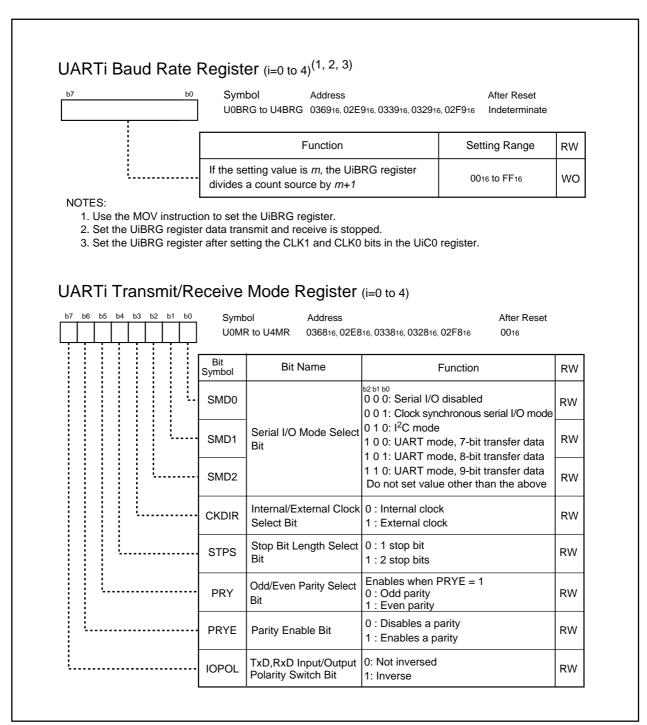

| 16.2.1 Bit Rate                                     | 192                      |

| 16.2.2 Selecting LSB First or MSB First             | 193                      |

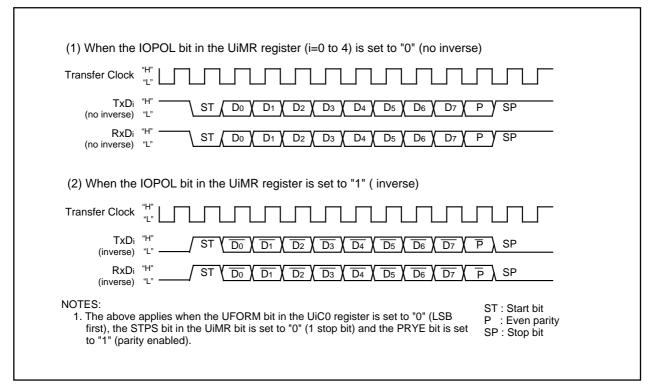

| 16.2.3 Serial Data Logic Inverse                    | 193                      |

| 16.2.4 TxD and RxD I/O Polarity Inverse             | 194                      |

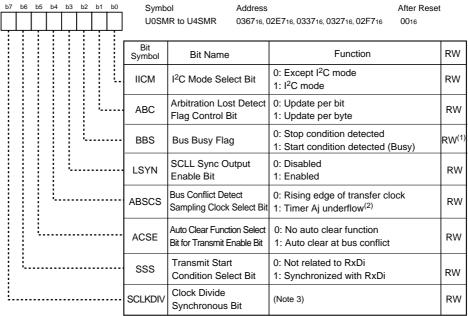

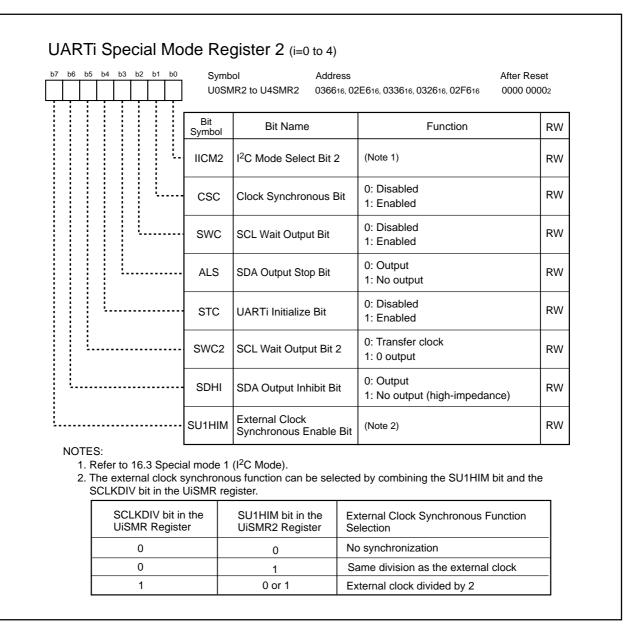

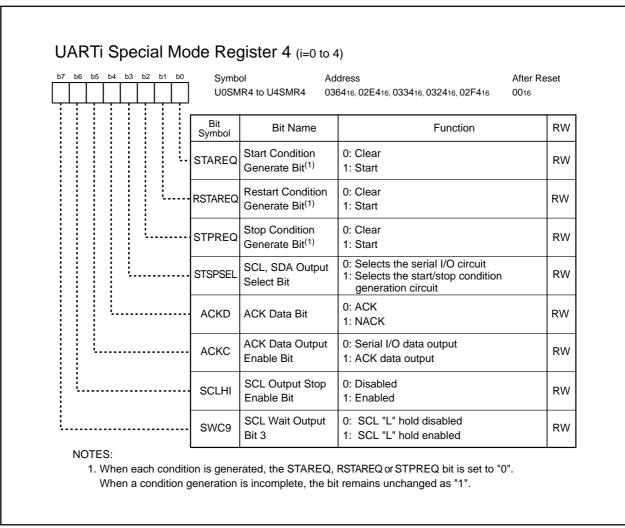

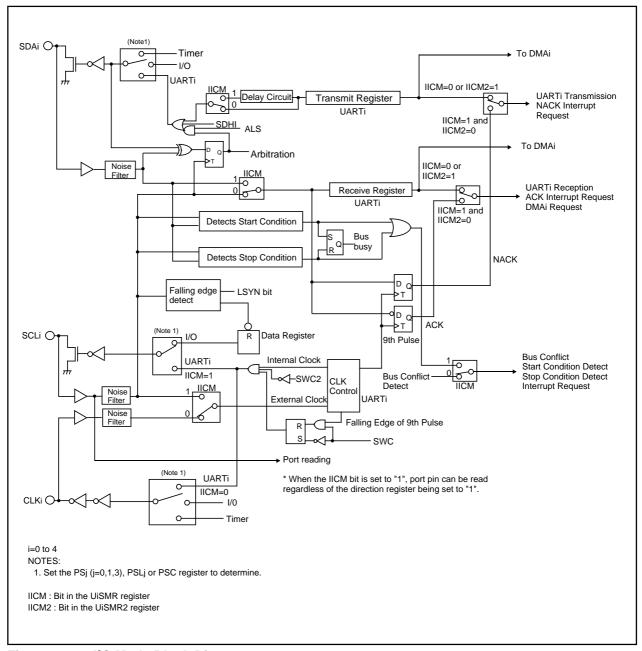

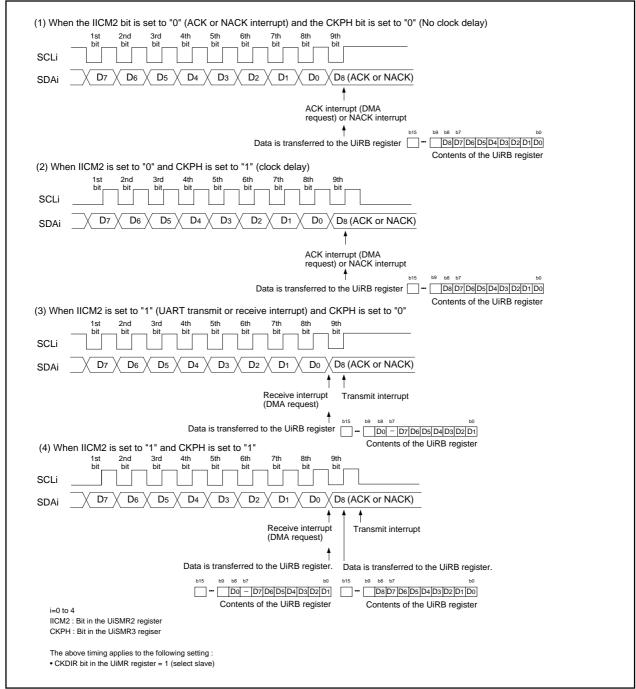

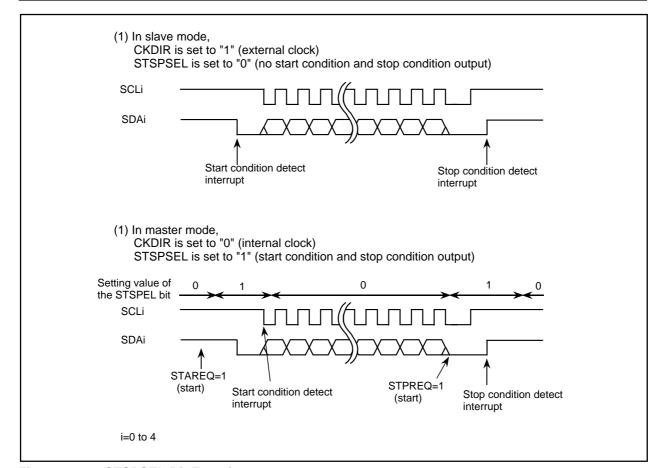

| 16.3 Special Mode 1 (I <sup>2</sup> C Mode)         | 195                      |

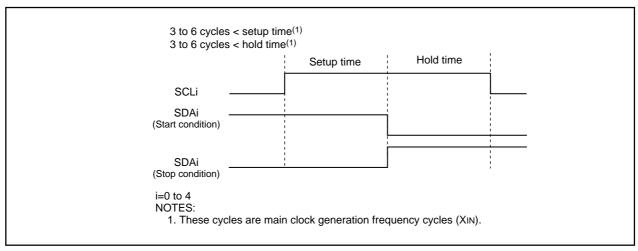

| 16.3.1 Detecting Start Condition and Stop Condition | 200                      |

| 16.3.2 Start Condition or Stop Condition Output     | 201                      |

| 16.3.3 Arbitration                                  | 202                      |

| 16.3.4 Transfer Clock                               | 202                      |

| 16.3.5 SDA Output                                   | 202                      |

| 16.3.6 SDA Input                                    | 203                      |

| 16.3.7 ACK, NACK                                    | 203                      |

| 16.3.8 Transmit and Receive Reset                   | 203                      |

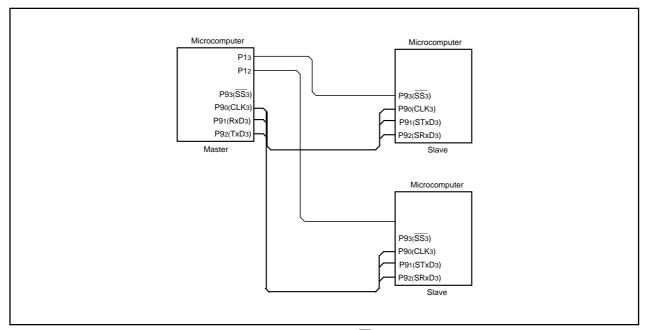

| 16.4 Special Mode 2                                 | 204                      |

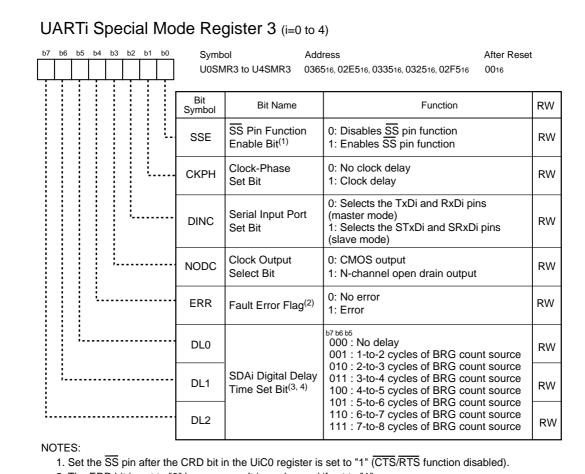

| 16.4.1 SSi Input Pin Function (i=0 to 4)            | 207                      |

| 16.4.2 Clock Phase Setting Function                 | 208                      |

| 16.5 Special Mode 3 (GCI Mode)                      | 210                      |

| 16.6 Special Mode 4 (IE Mode)                       | 214                      |

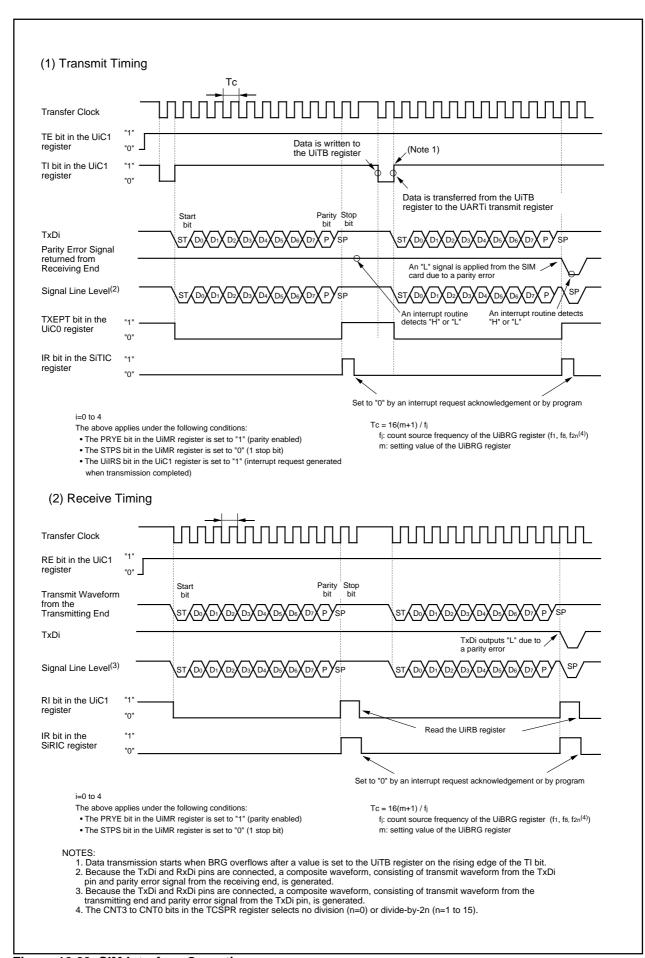

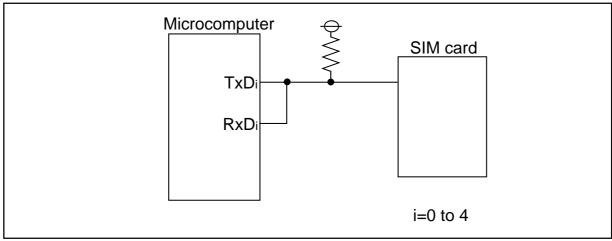

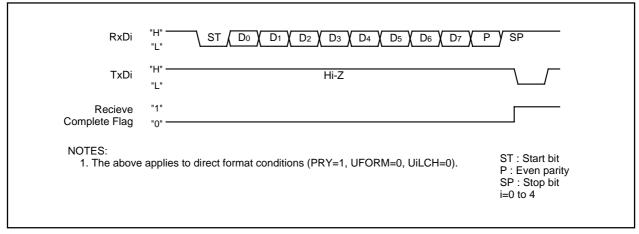

| 16.7 Special Mode 5 (SIM Mode)                      | 218                      |

| 16.7.1 Parity Error Signal                          | 222                      |

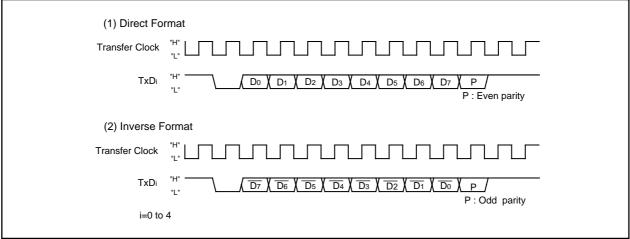

| 16.7.2 Format                                       | 223                      |

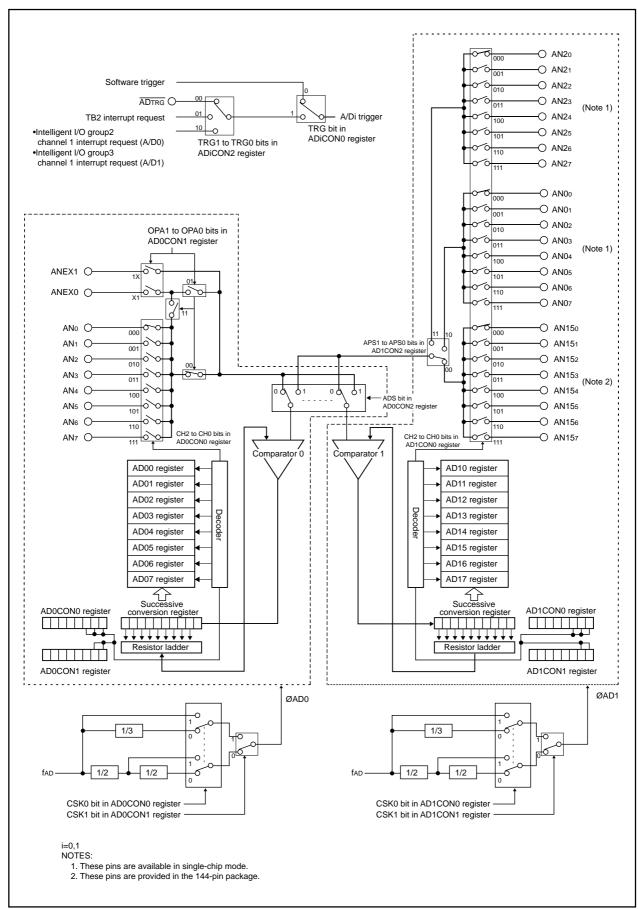

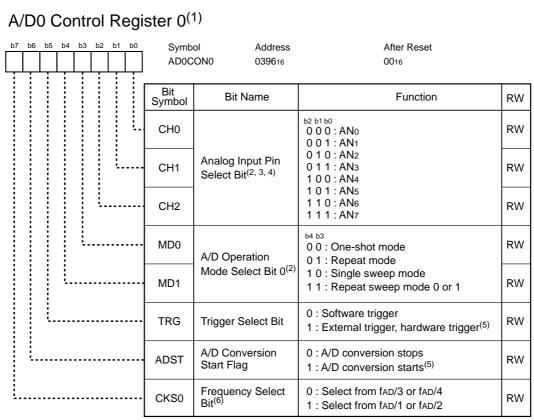

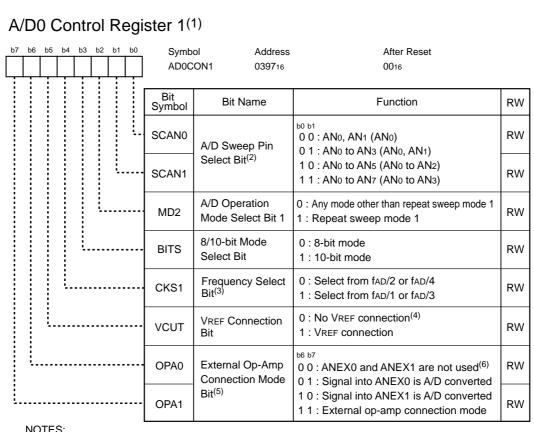

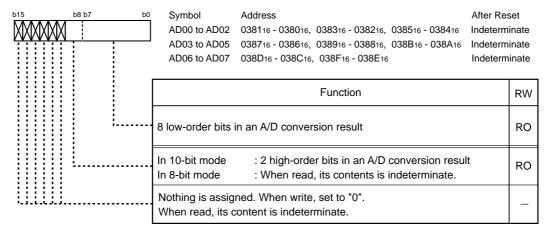

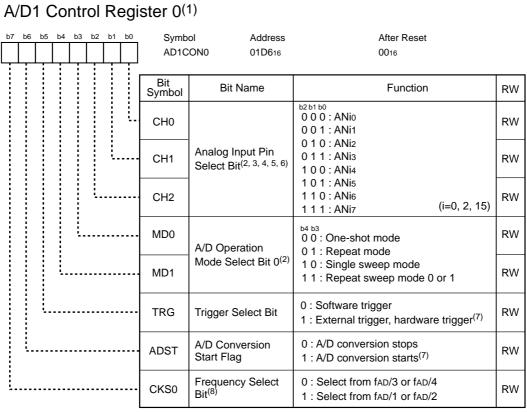

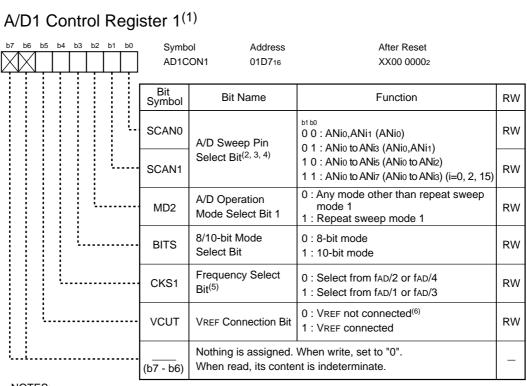

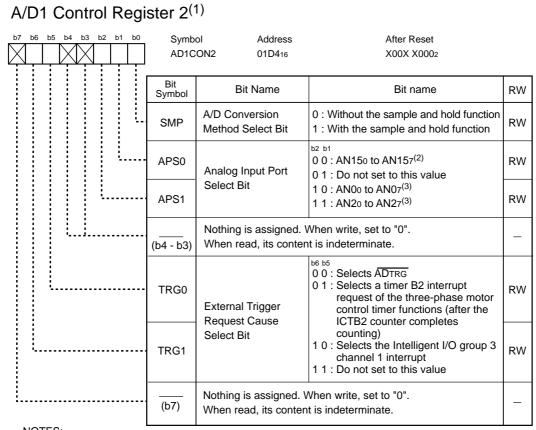

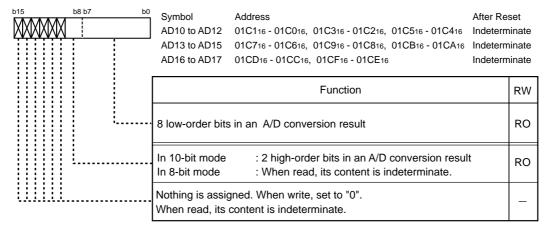

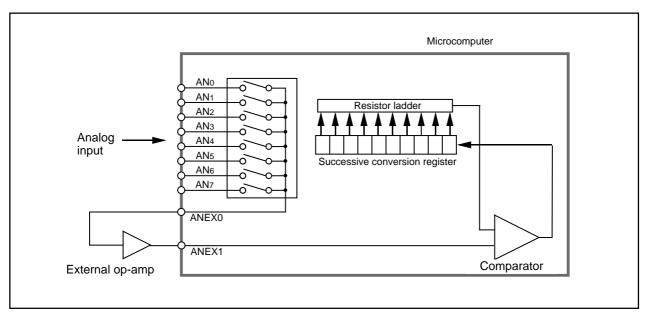

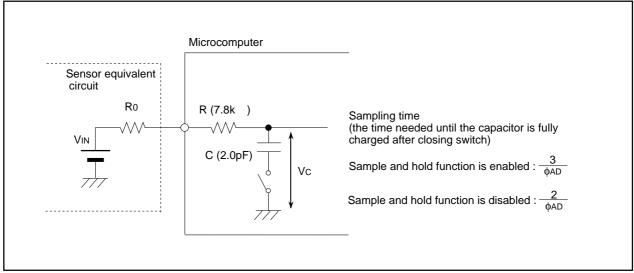

| 17. A/D Converter                                   | 224                      |

|                                                     | 23/                      |

| 17.1 Mode Description                               |                          |

| 17.1 Mode Description                               |                          |

| •                                                   | 234                      |

| 17.1.1 One-shot Mode                                | 234<br>234               |

| 17.1.1 One-shot Mode17.1.2 Repeat Mode              | 234<br>234<br>235        |

| 17.1.1 One-shot Mode                                | 234<br>234<br>235        |

| 17.1.1 One-shot Mode                                | 234<br>235<br>235<br>236 |

| 17.1.1 One-shot Mode                                |                          |

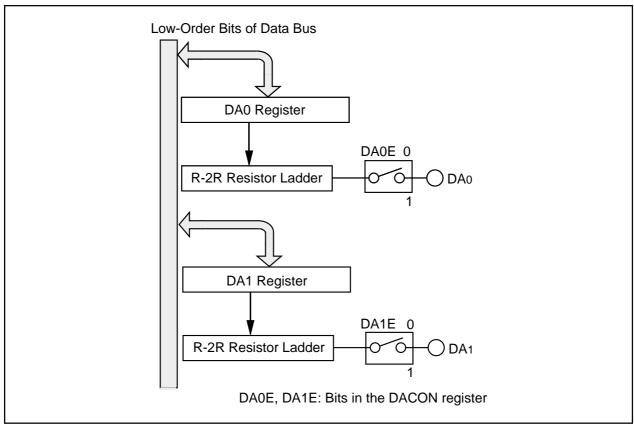

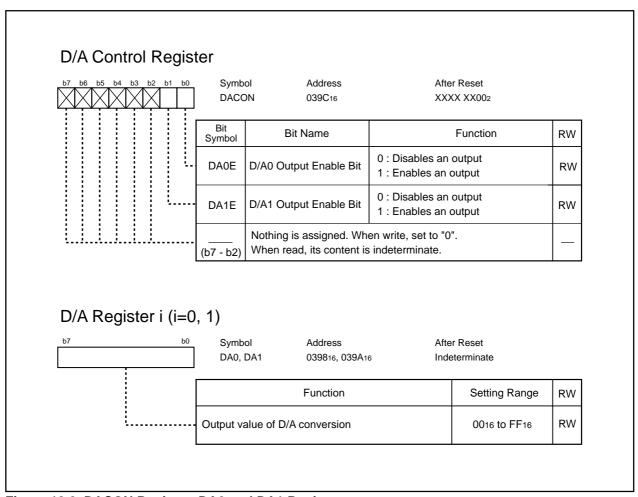

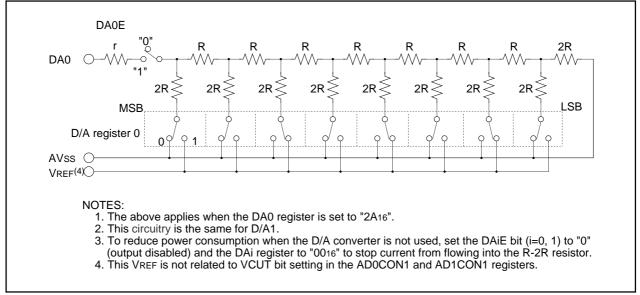

| 18. D/A Converter                                                   | 240         |

|---------------------------------------------------------------------|-------------|

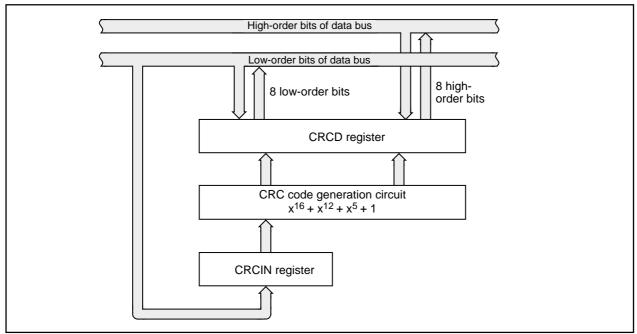

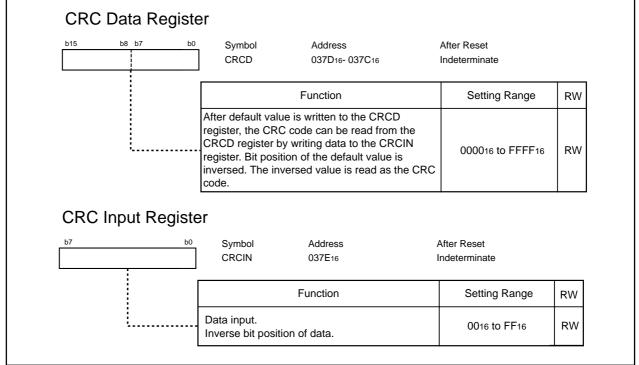

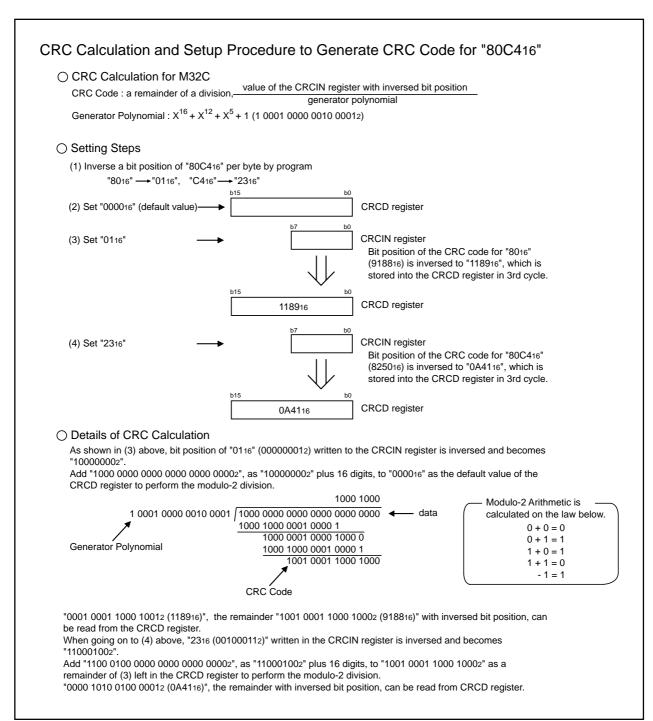

| 19. CRC Calculation                                                 | 243         |

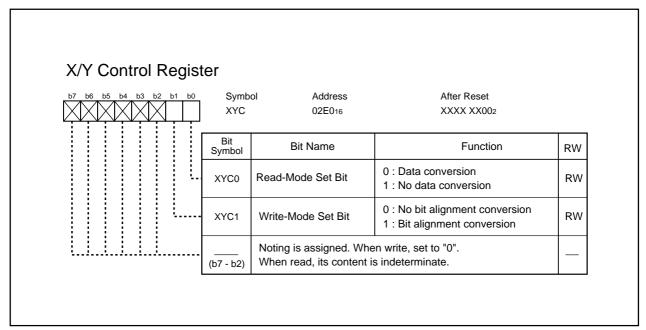

| 20. X/Y Conversion                                                  | 245         |

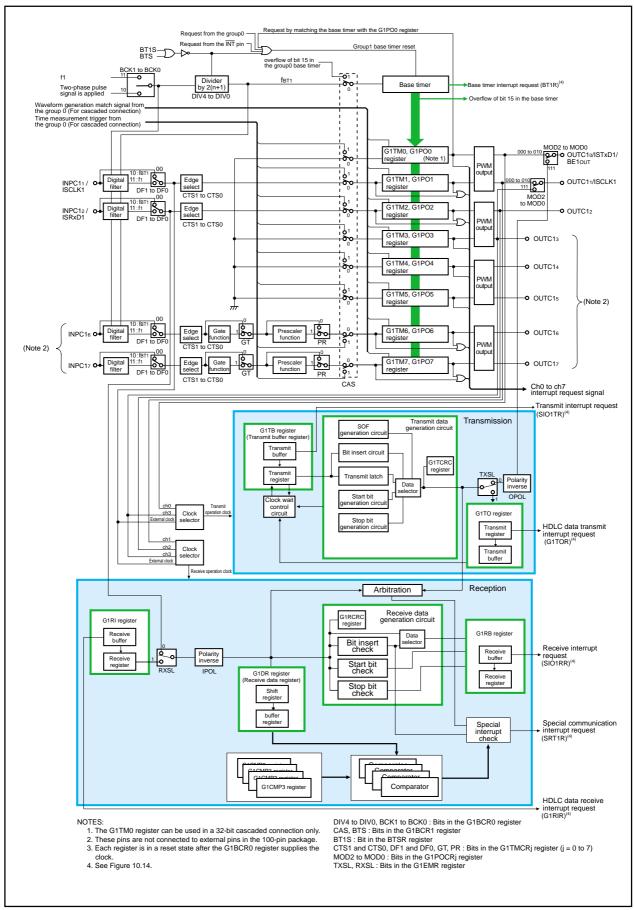

| 21. Intelligent I/O                                                 |             |

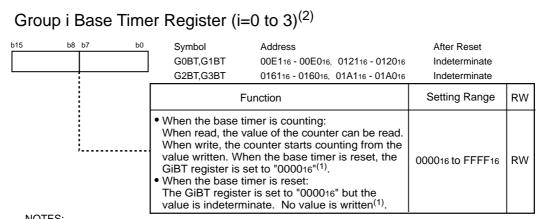

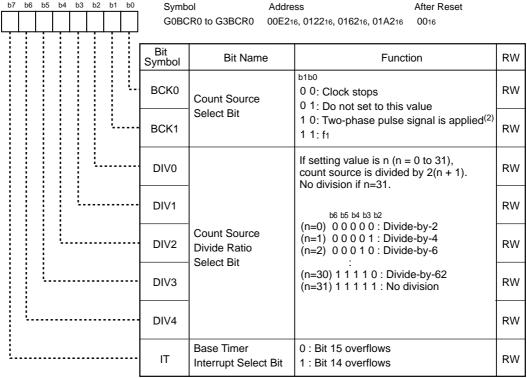

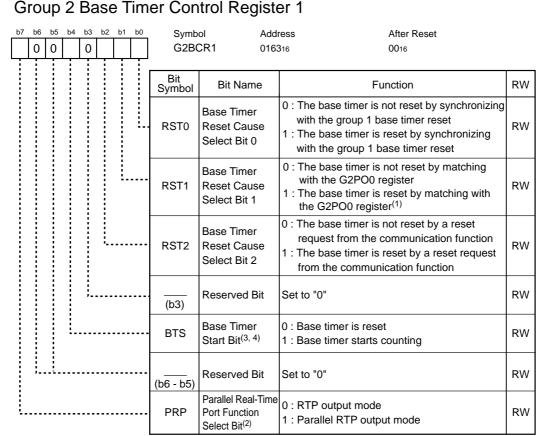

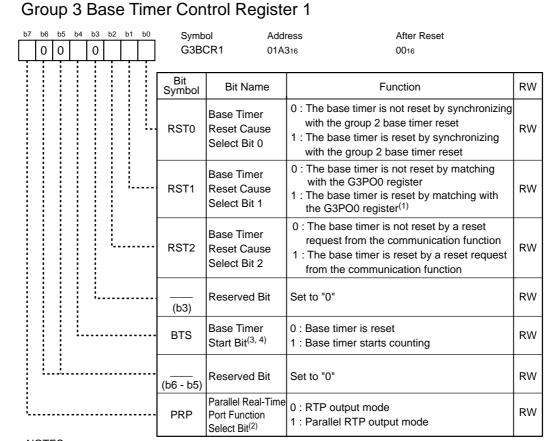

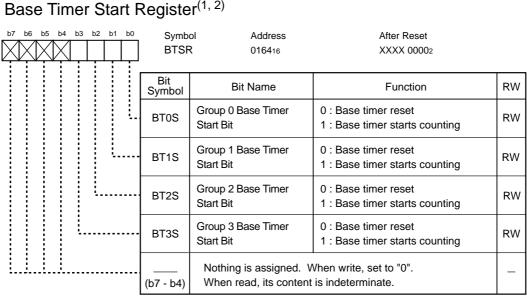

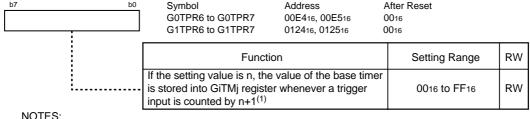

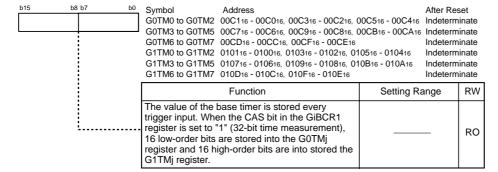

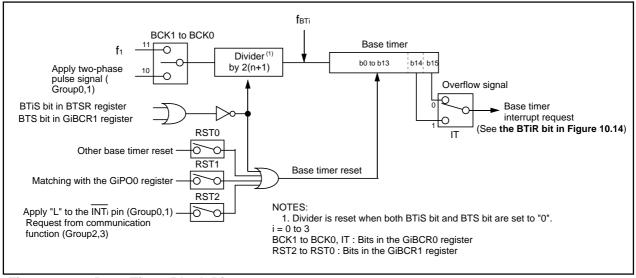

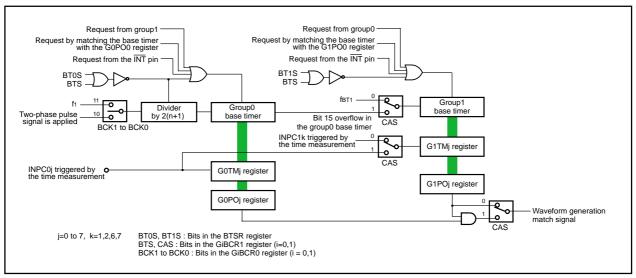

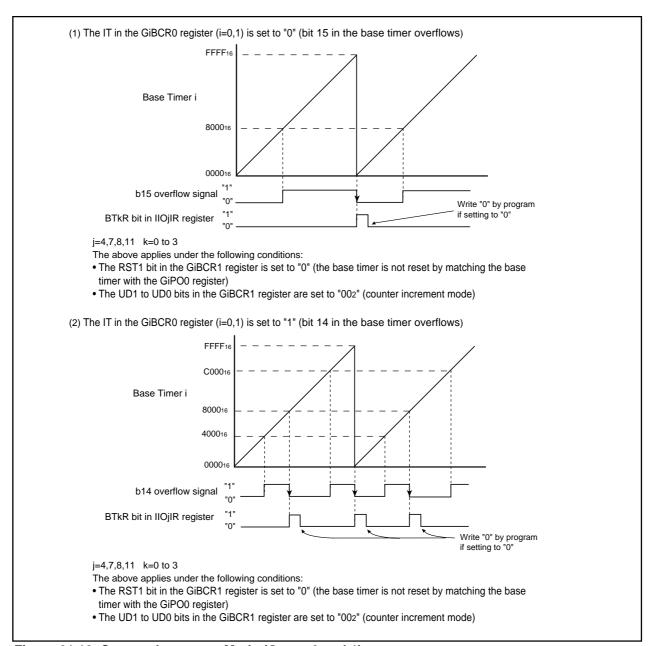

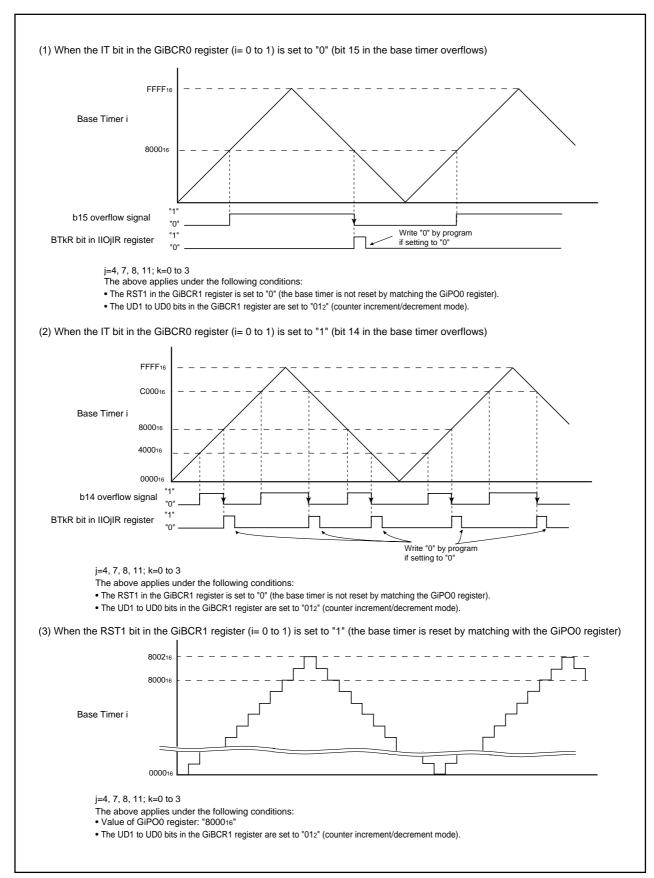

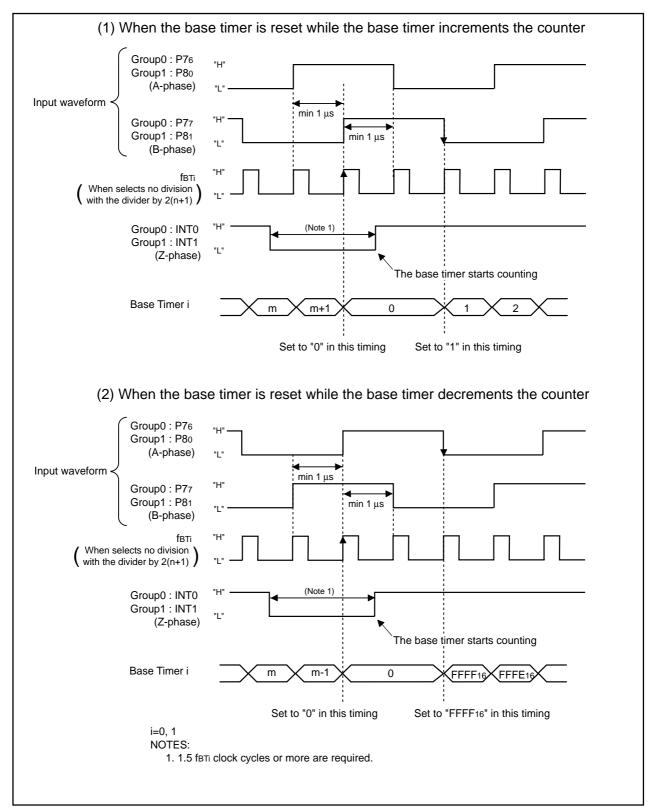

| 21.1 Base Timer                                                     |             |

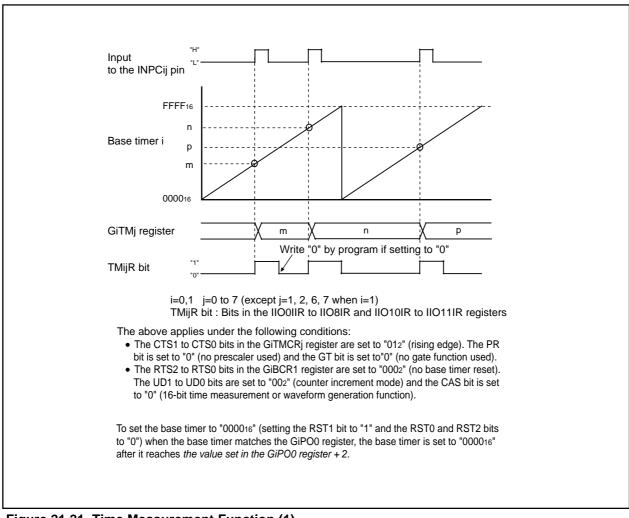

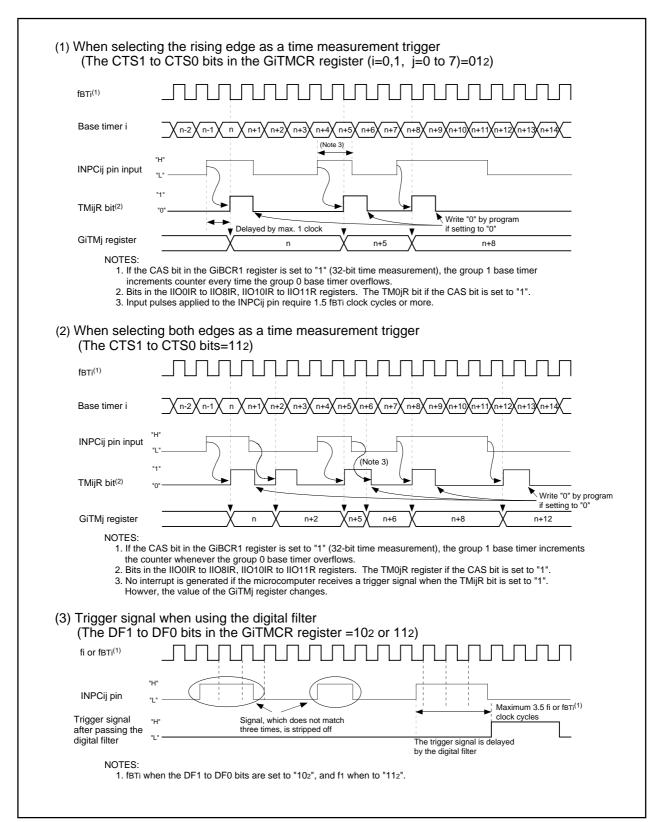

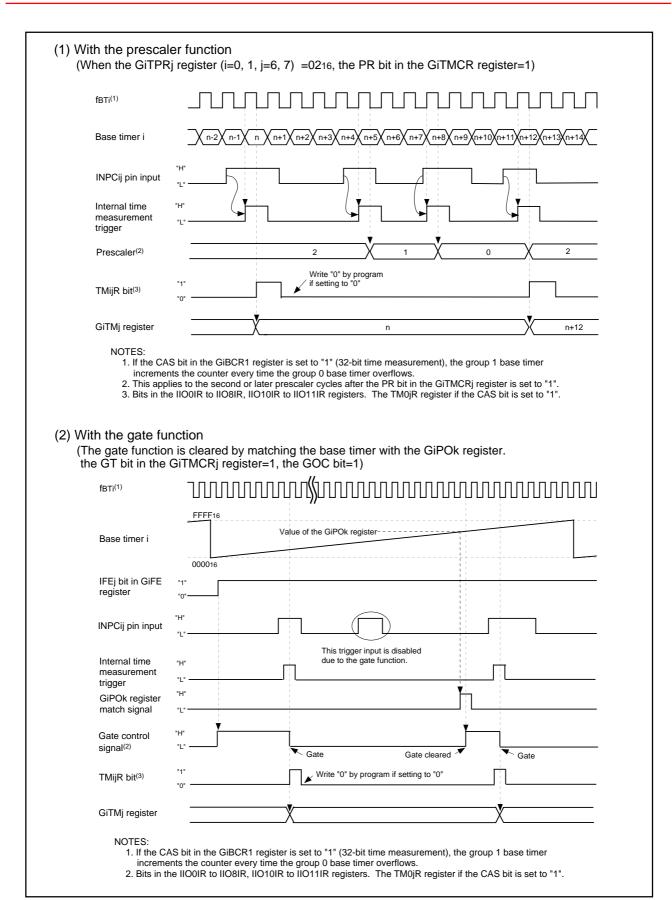

| 21.2 Time Measurement Function (Group 0 and 1)                      |             |

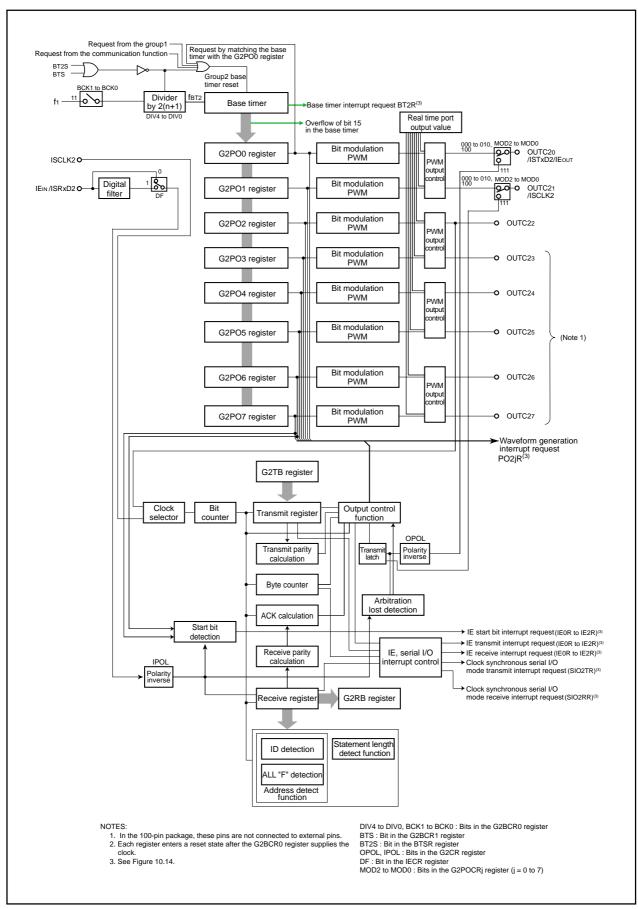

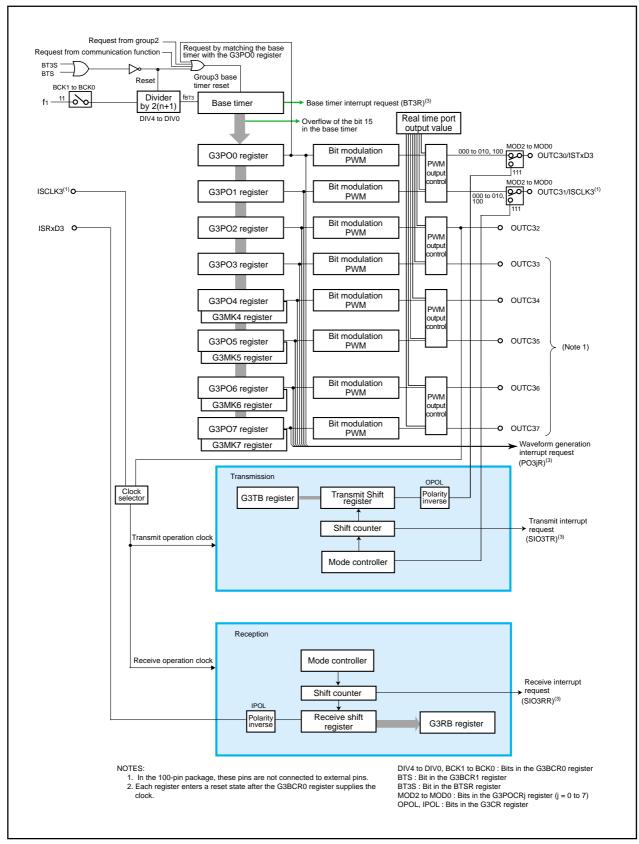

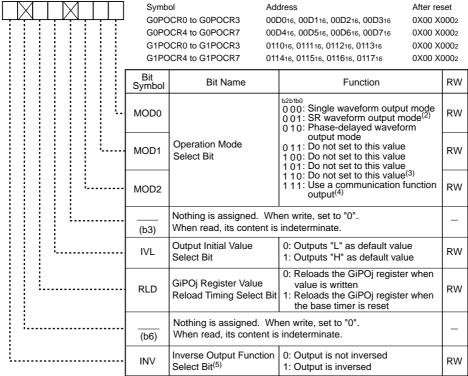

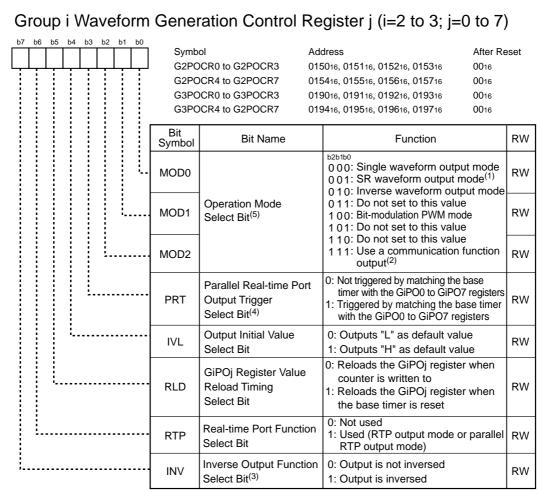

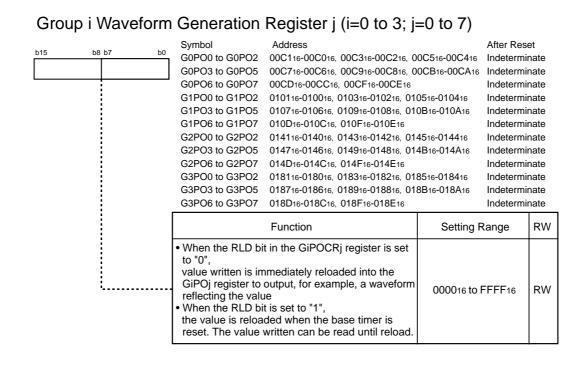

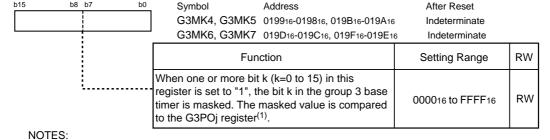

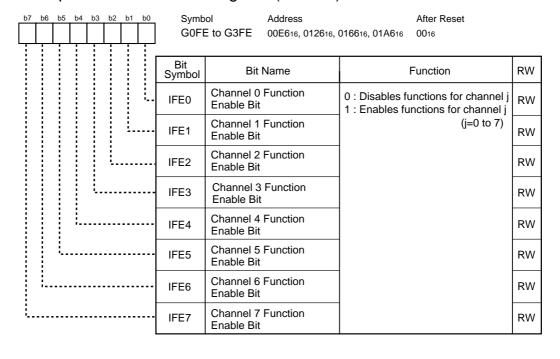

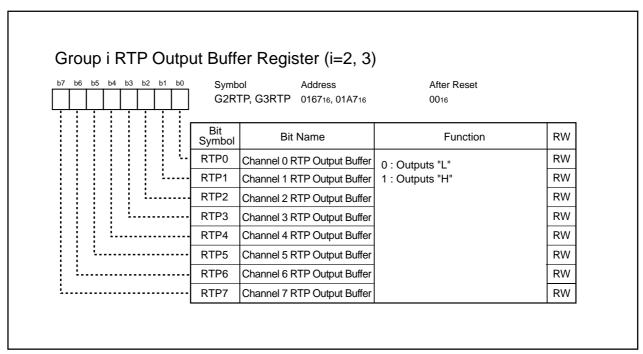

| 21.3 Waveform Generation Function                                   |             |

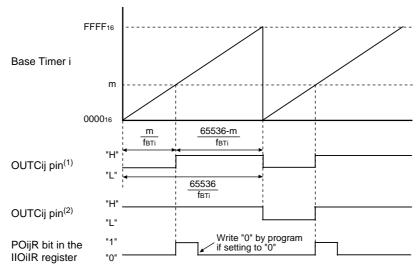

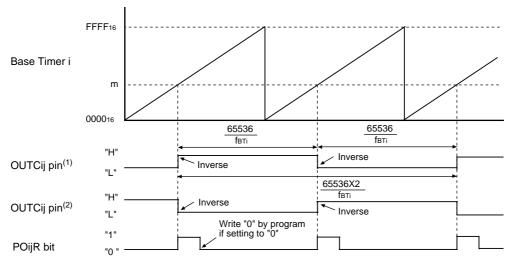

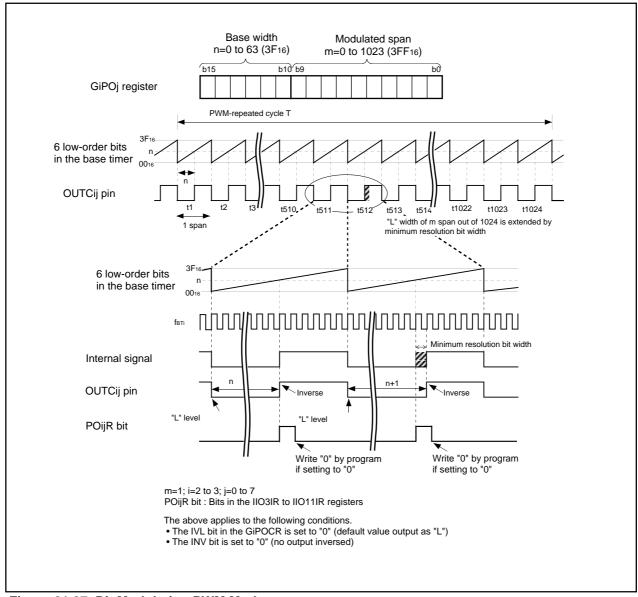

| 21.3.1 Single-Phase Waveform Output Mode (Group 0 to 3)             | 27          |

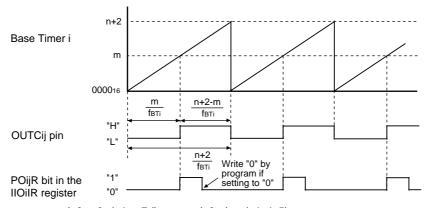

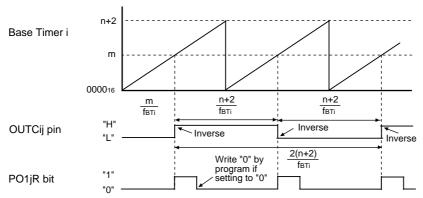

| 21.3.2 Phase-Delayed Waveform Output Mode (Group 0 to 3)            | 27          |

| 21.3.3 Set/Reset Waveform Output (SR Waveform Output) Mode (Group   | 0 to 3) 28  |

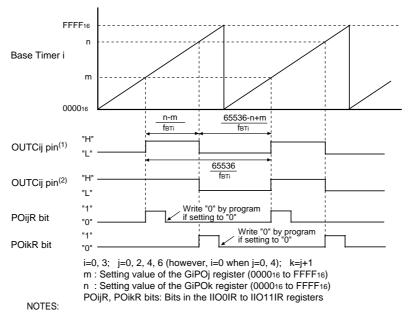

| 21.3.4 Bit Modulation PWM Output Mode (Group 2 and 3)               | 28          |

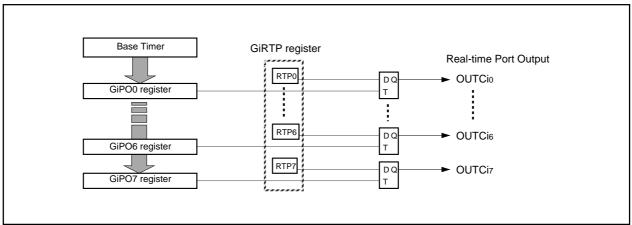

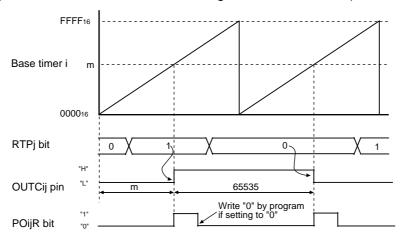

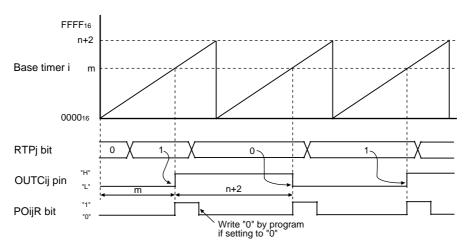

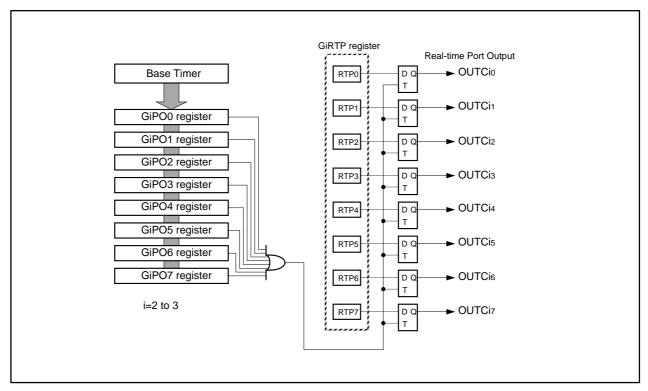

| 21.3.5 Real-Time Port (RTP) Output Mode (Group 2 and 3)             | 28          |

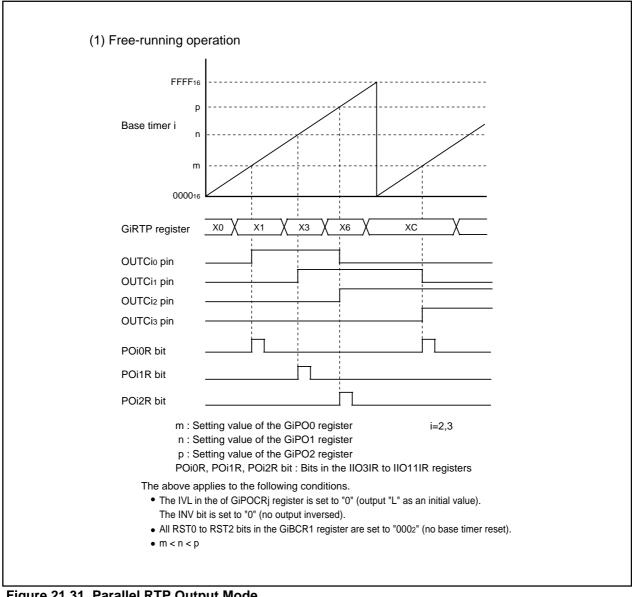

| 21.3.6 Parallel Real-Time Port Output Mode (Group 2 and 3)          | 28          |

| 21.4 Communication Unit 0 and 1 Communication Function              | 28          |

| 21.4.1 Clock Synchronous Serial I/O Mode (Groups 0 and 1)           | 29          |

| 21.4.2 Clock Asynchronous Serial I/O Mode (UART) (Groups 0 and 1    | ) <b>29</b> |

| 21.4.3 HDLC Data Processing Mode (Group 0 and 1)                    | 30          |

| 21.5 Group 2 Communication Function                                 | 30          |

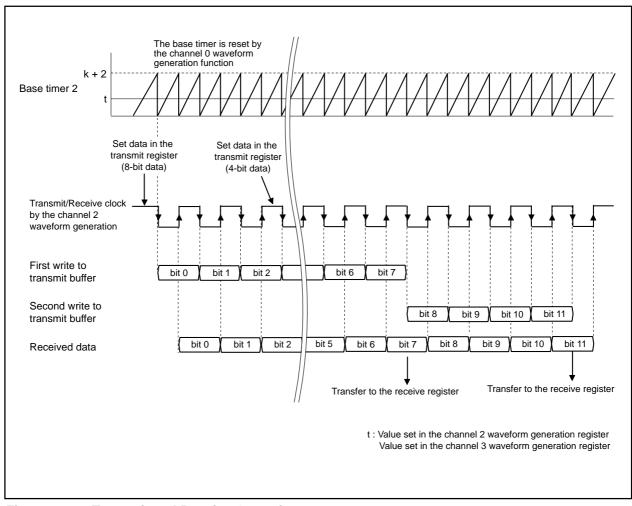

| 21.5.1 Variable Clock Synchronous Serial I/O Mode (Group 2)         | 31          |

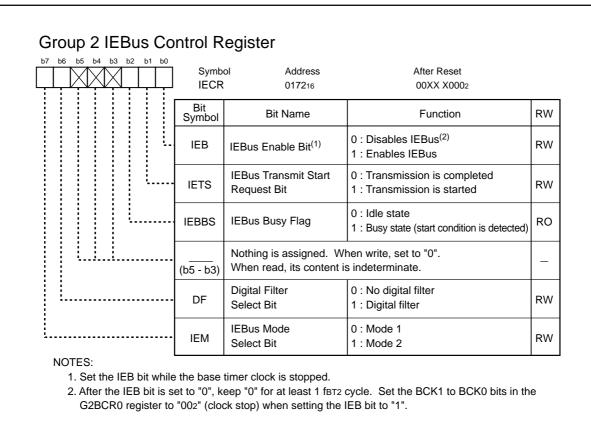

| 21.5.2 IEBus Mode (Group 2)                                         | 31          |

| 21.6 Group 3 Communication Function                                 | 31          |

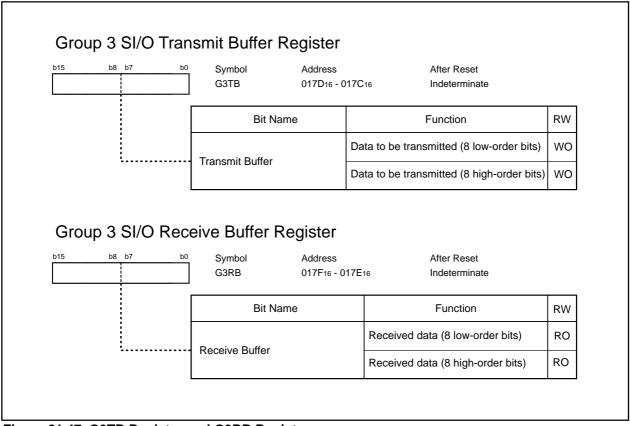

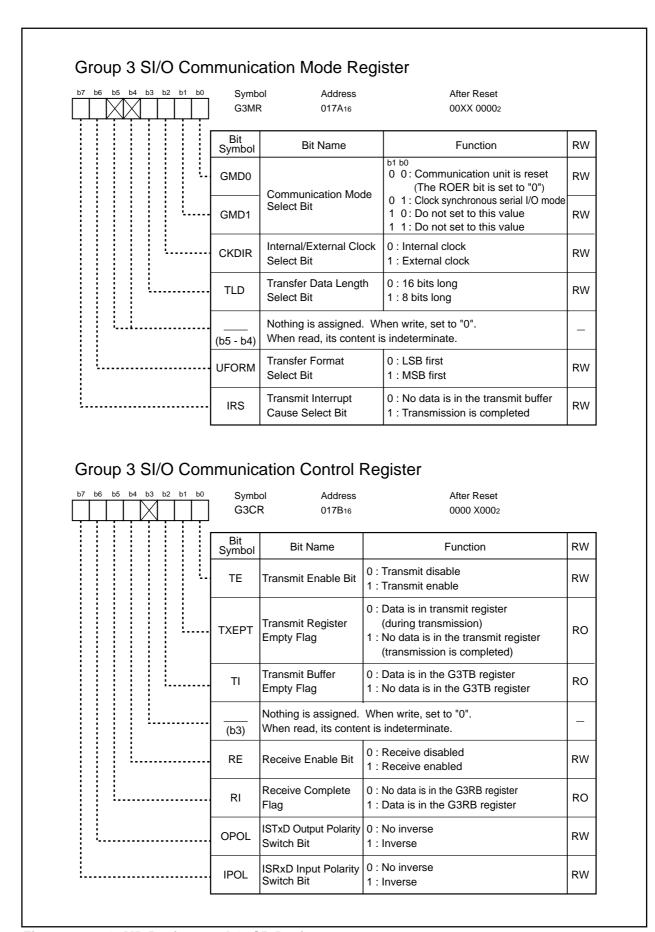

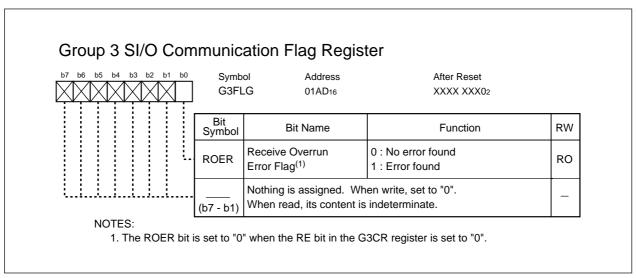

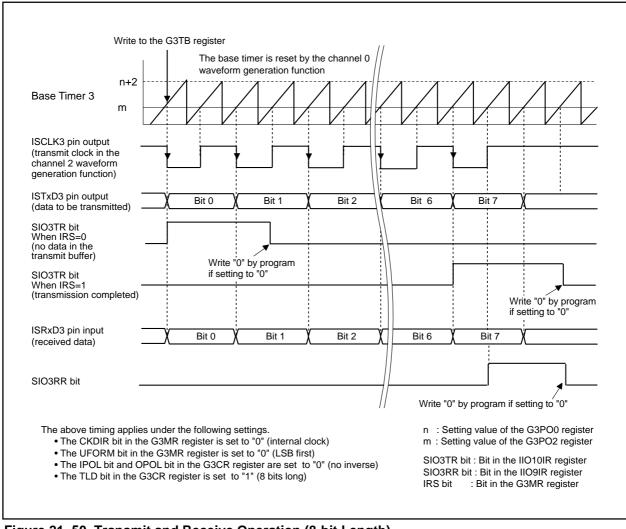

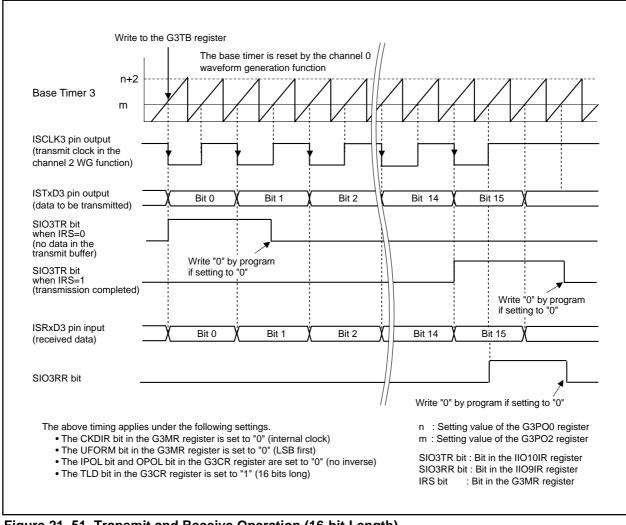

| 21.6.1 8-bit or 16-bit Clock Synchronous Serial I/O Mode (Group 3). | 32          |

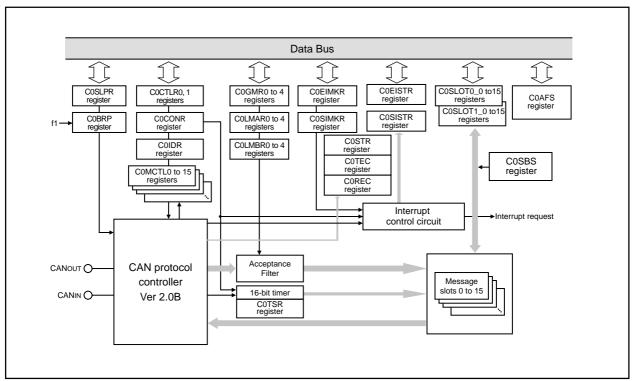

| 22. CAN Module                                                      | 324         |

| 22.1 CAN-Associated Registers                                       | 32          |

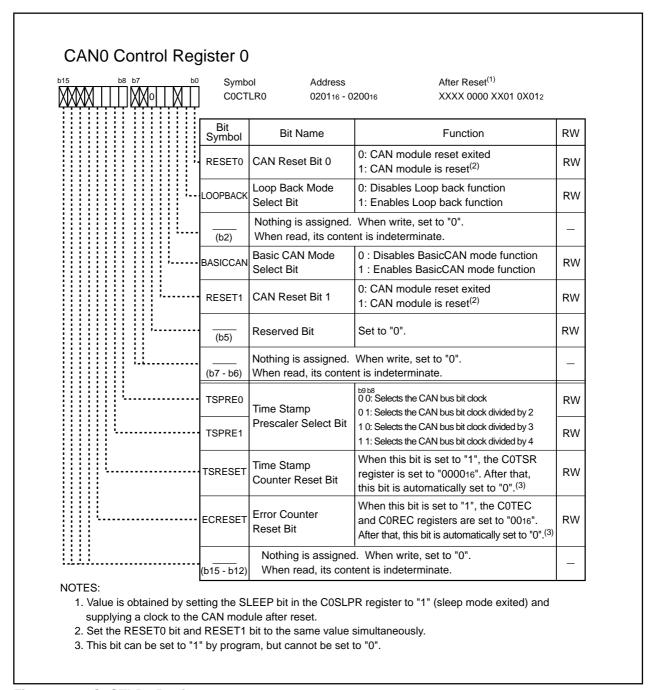

| 22.1.1 CAN0 Control Register 0 (C0CTLR0 Register)                   | 32          |

| 22.1.2 CAN0 Control Register 1 (C0CTLR1 Register)                   | 32          |

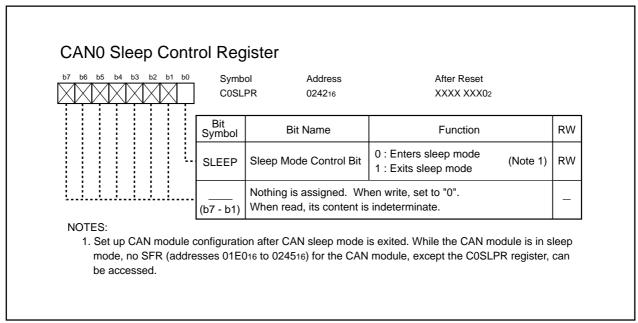

| 22.1.3 CAN0 Sleep Control Register (C0SLPR Register)                | 33          |

| 22.1.4 CAN0 Status Register (C0STR Register)                        | 33          |

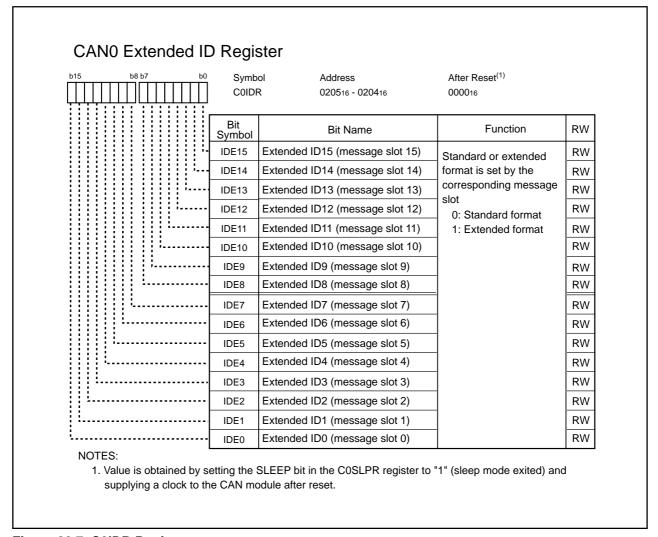

| 22.1.5 CAN0 Extended ID Register (C0IDR Register)                   | 33          |

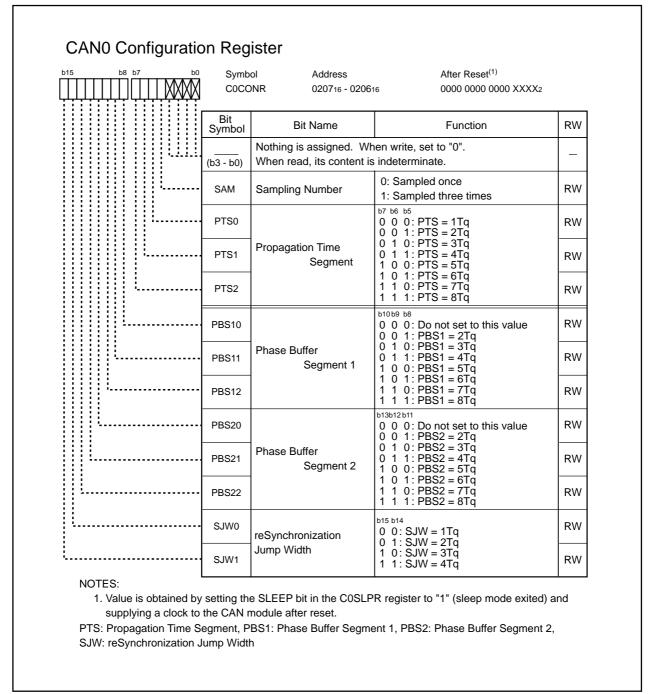

| 22.1.6 CAN0 Configuration Register (C0CONR Register)                | 33          |

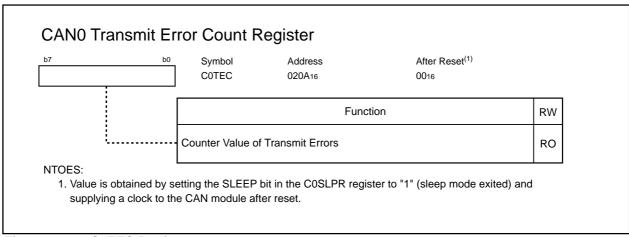

| 22.1.8 CAN0 Transmit Error Count Register (C0TEC Register)          | 33          |

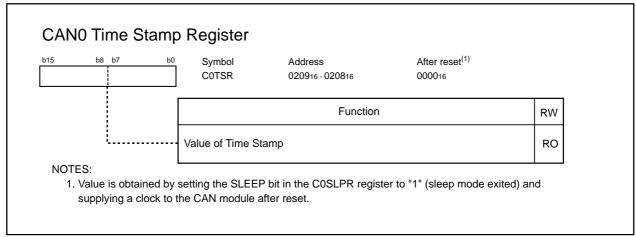

| 22.1.7 CAN0 Time Stamp Register (C0TSR Register)                    | 33          |

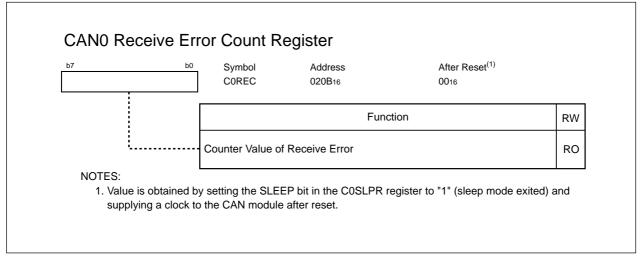

| 22.1.9 CAN0 Receive Error Count Register (C0REC Register)           | 33          |

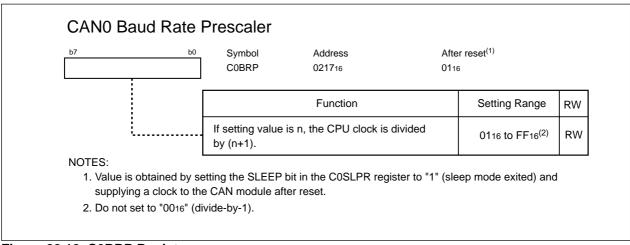

| 22.1.10 CAN0 Baud Rate Prescaler (C0BRP Register)                   | 33          |

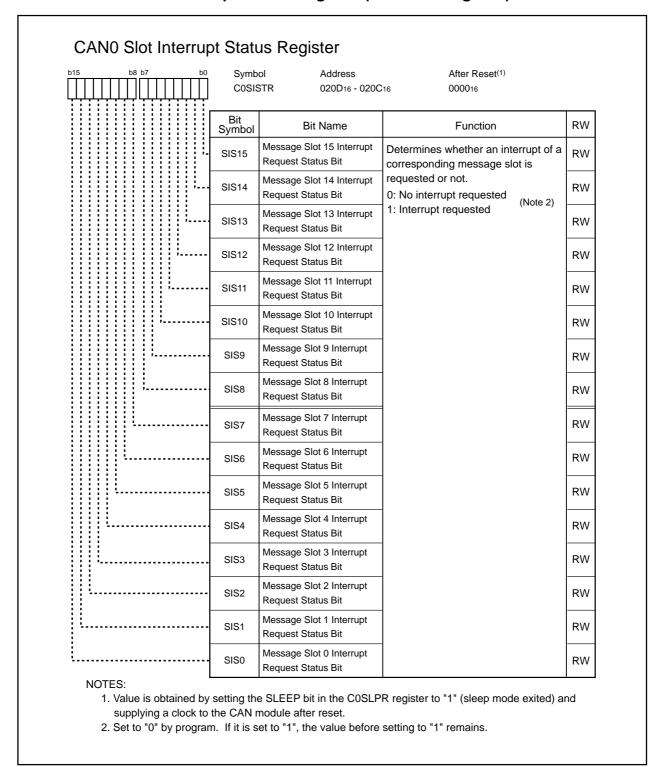

| 22.1.11 CAN0 Slot Interrupt Status Register (C0SISTR Register)      | 33          |

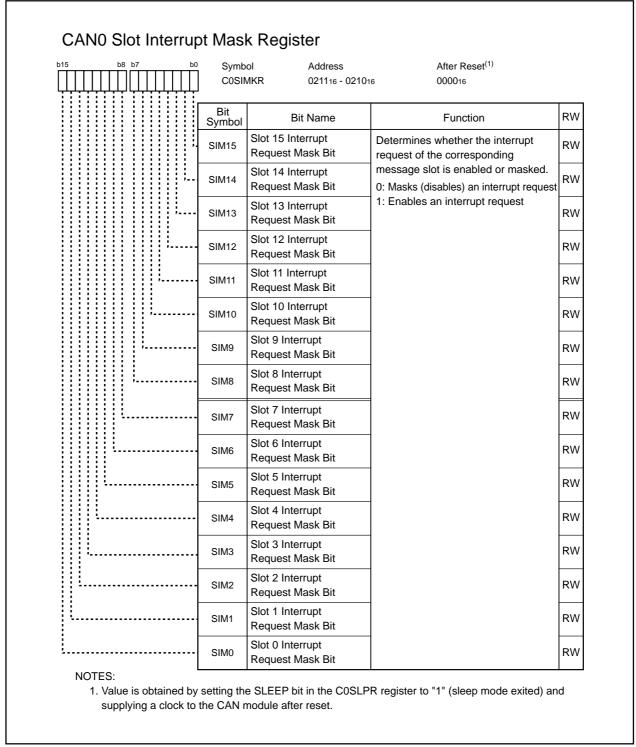

| 22.1.12 CAN0 Slot Interrupt Mask Register (C0SIMKR Register)        | 34          |

|    | 22.1.13 CAN0 Error Interrupt Mask Register (C0EIMKR Register)                | 341   |

|----|------------------------------------------------------------------------------|-------|

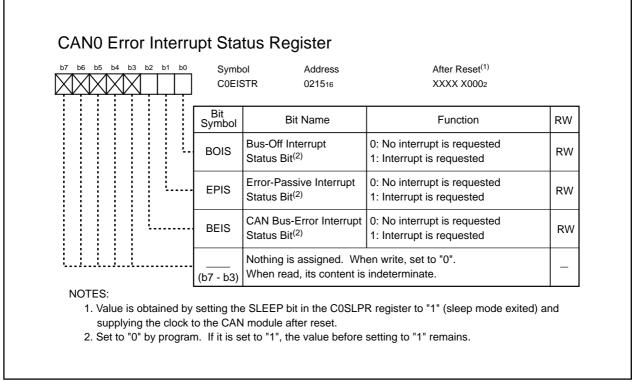

|    | 22.1.14 CAN0 Error Interrupt Status Register (C0EISTR Register)              | 342   |

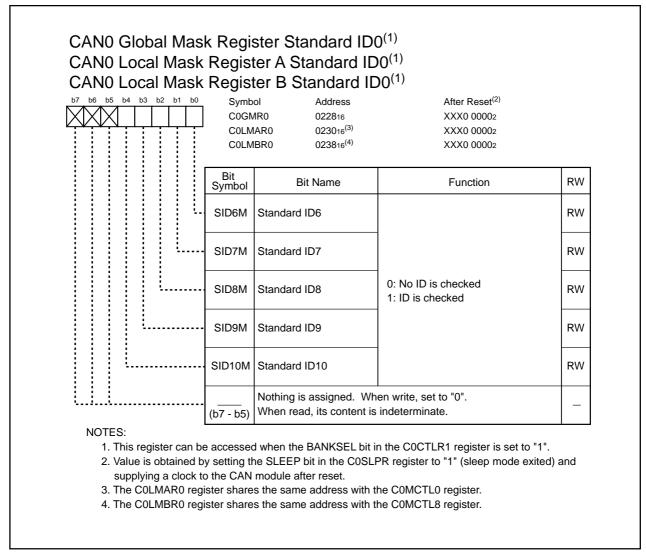

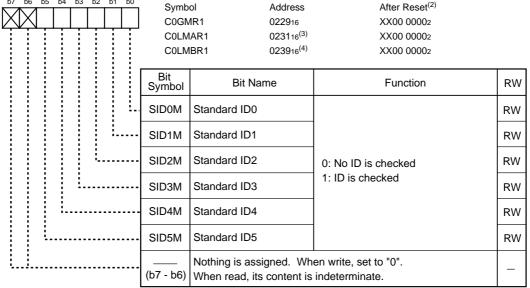

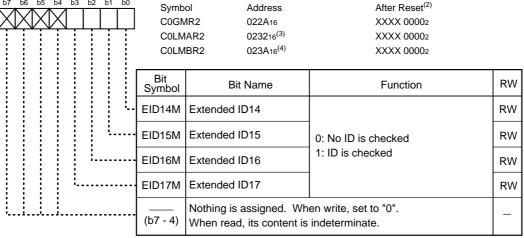

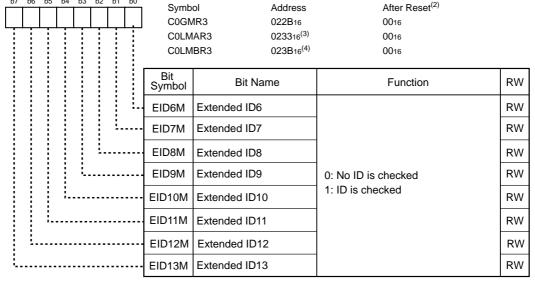

|    | 22.1.15 CAN0 Global Mask Register, CAN0 Local Mask Register A and CAN0 Local |       |

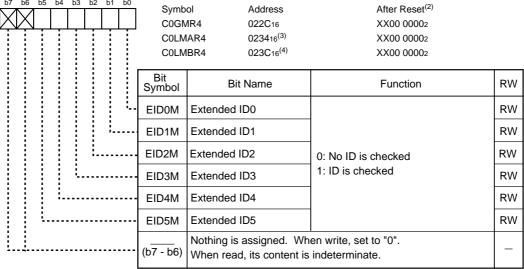

|    | Register B (C0GMRj (j=0 to4), C0LMARj and C0LMBRj Registers)                 | 343   |

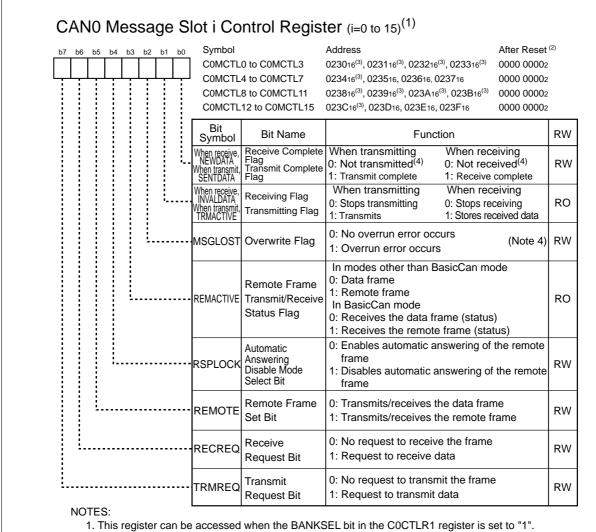

|    | 22.1.16 CAN0 Message Slot i Control Register (C0MCTLi Register) (i=0 to 15   | ) 346 |

|    | 22.1.17 CAN0 Slot Buffer Select Register (C0SBS Register)                    | 349   |

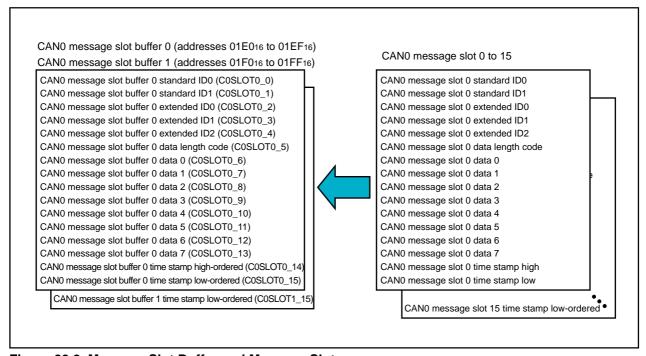

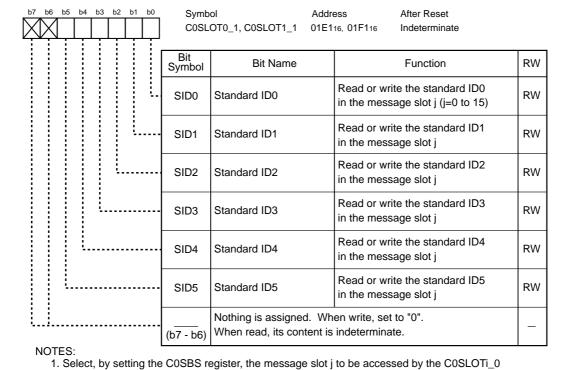

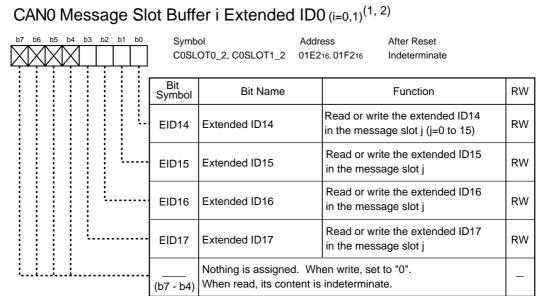

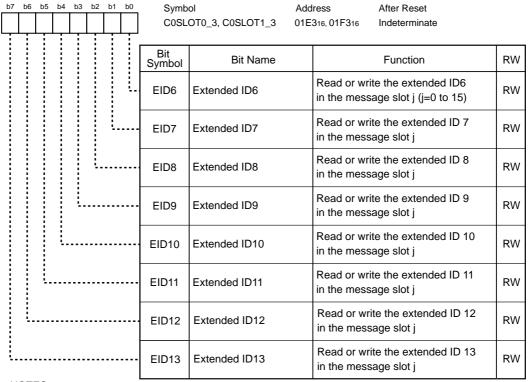

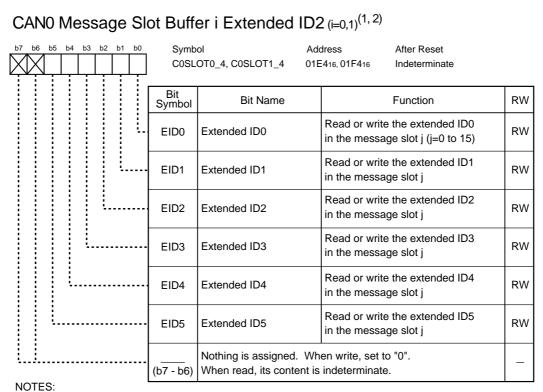

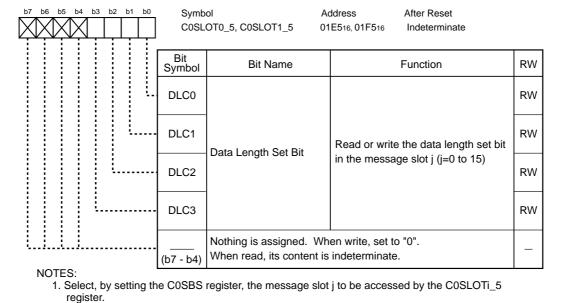

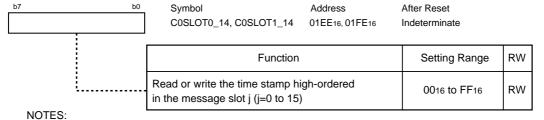

|    | 22.1.18 Message Slot Buffer                                                  | 349   |

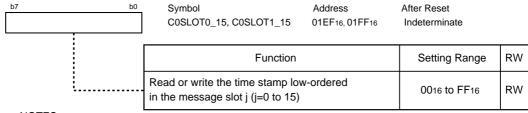

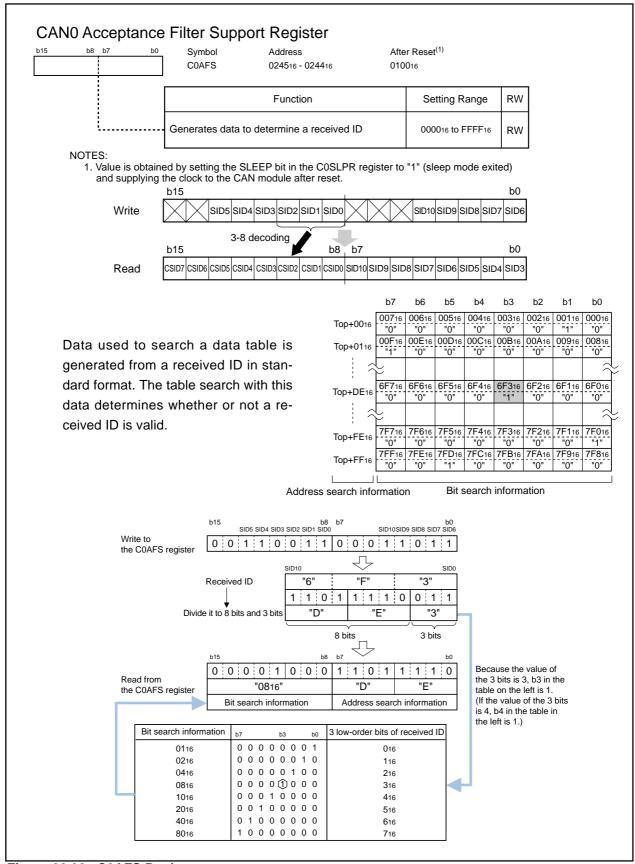

|    | 22.1.19 CAN0 Acceptance Filter Support Register (C0AFS Register)             | 354   |

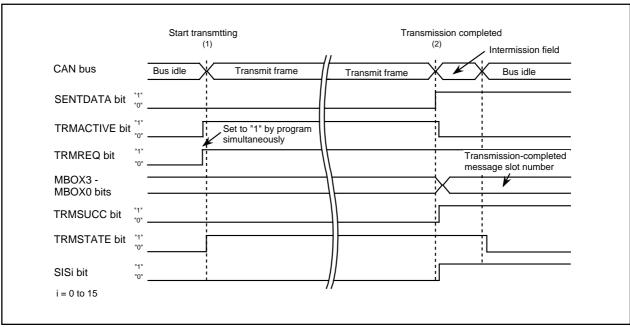

|    | 22.2.2 CAN Transmit Timing                                                   | 355   |

|    | 22.2 Timing with CAN-Associated Registers                                    | 355   |

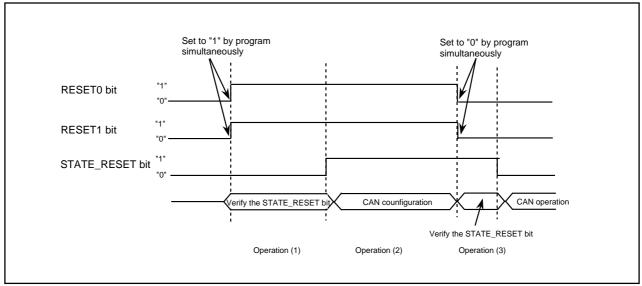

|    | 22.2.1 CAN Module Reset Timing                                               | 355   |

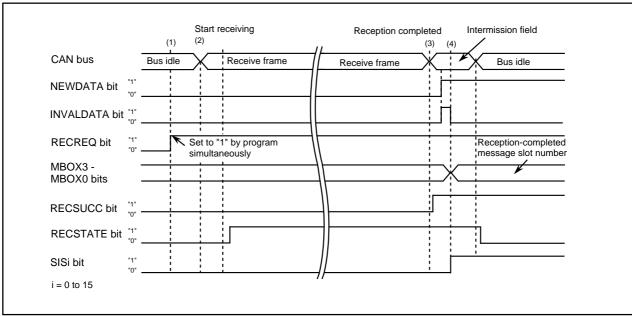

|    | 22.2.3 CAN Receive Timing                                                    | 356   |

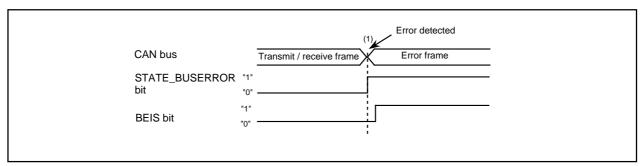

|    | 22.2.4 CAN Bus Error Timing                                                  | 357   |

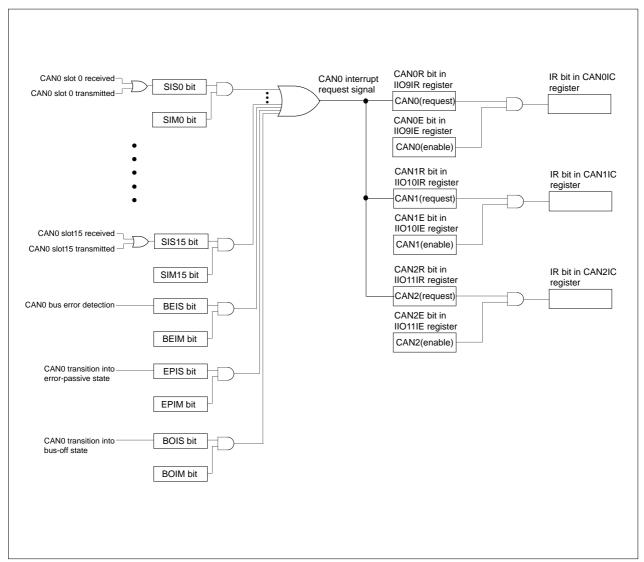

|    | 22.3 CAN Interrupts                                                          | 357   |

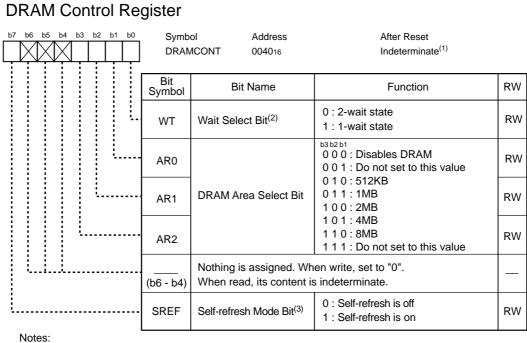

| 23 | B. DRAMC                                                                     | 359   |

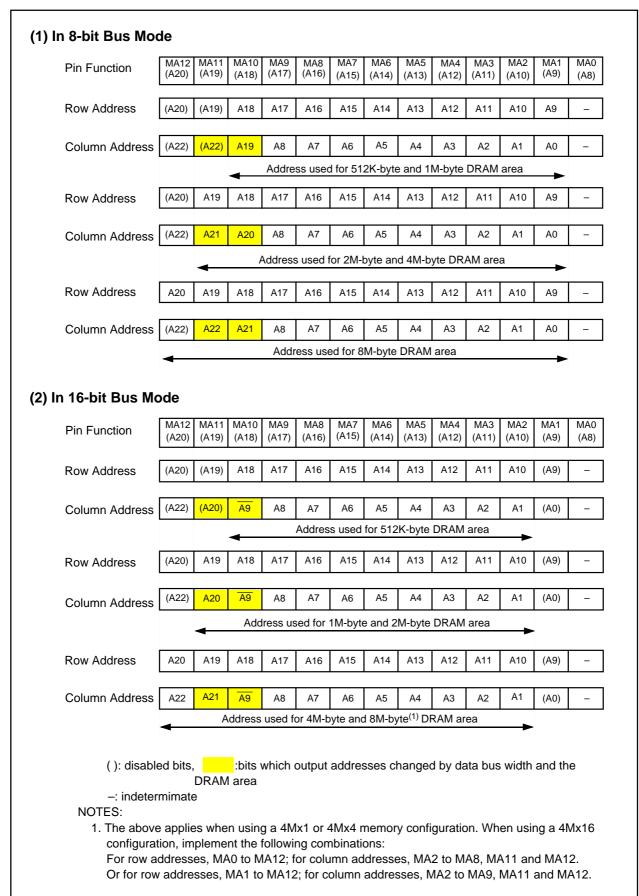

|    | 23.1 DRAMC Multiplexed Address Output                                        |       |

|    | 23.2 Refresh                                                                 |       |

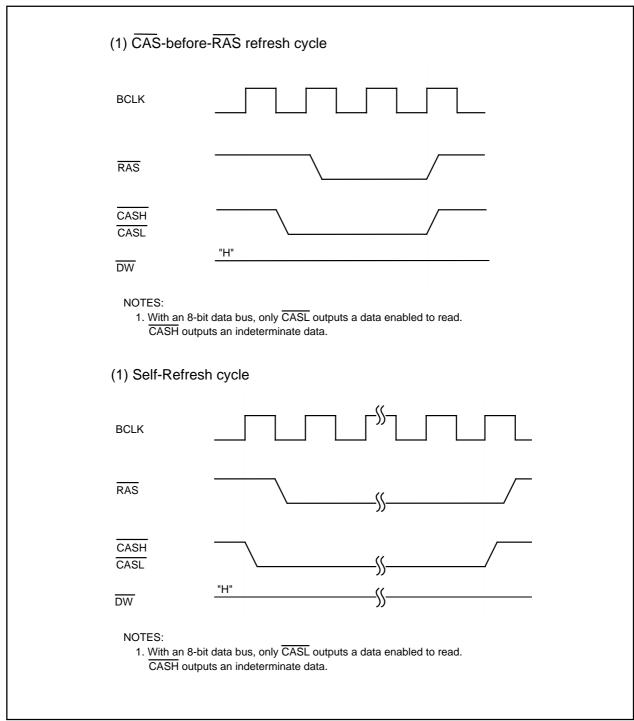

|    | 23.2.1 Refresh                                                               | 361   |

|    | 23.2.2 Self-Refresh                                                          | 361   |

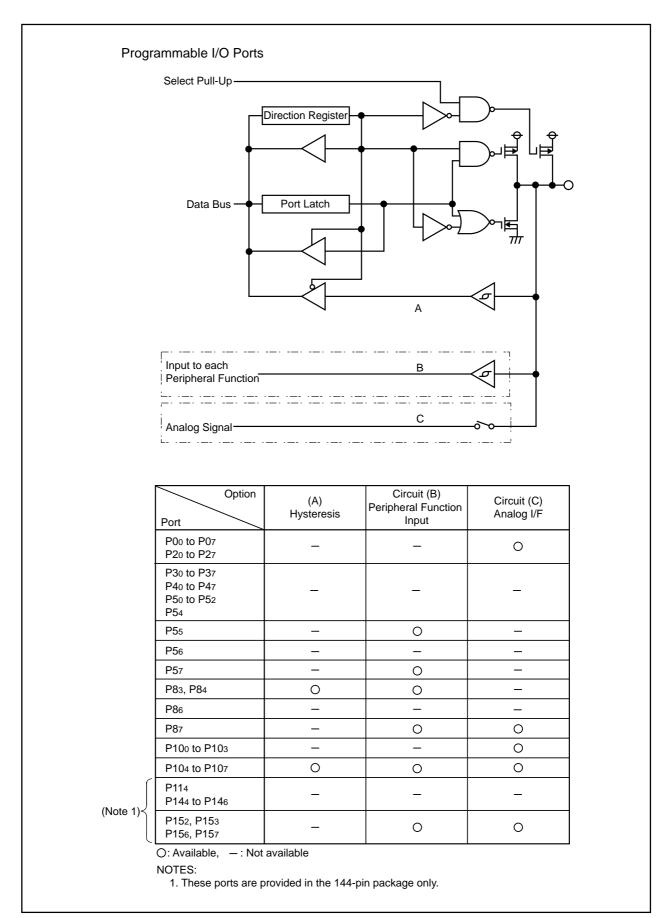

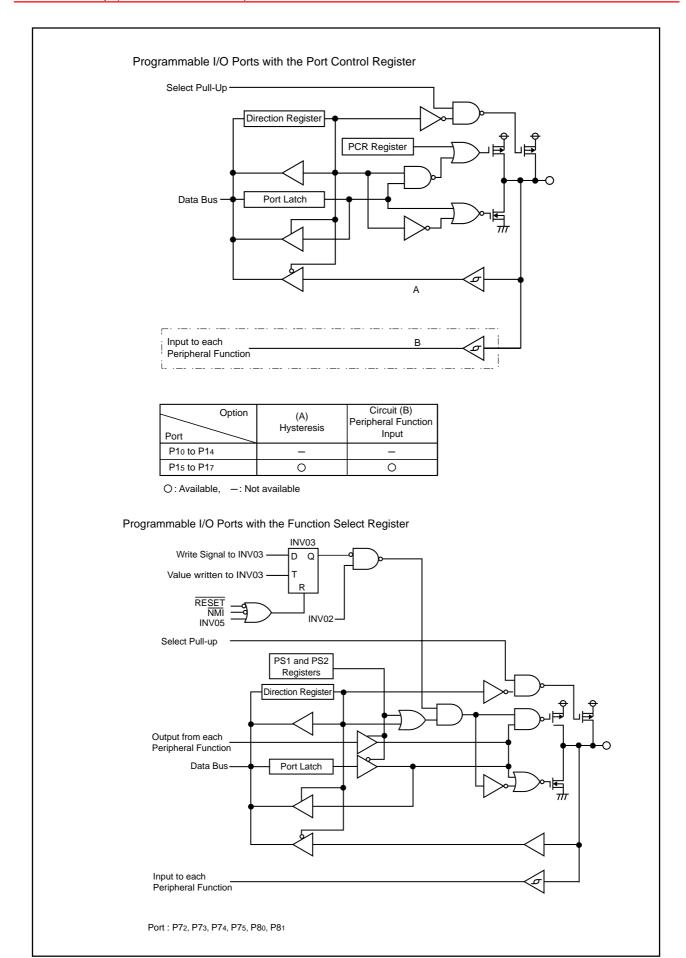

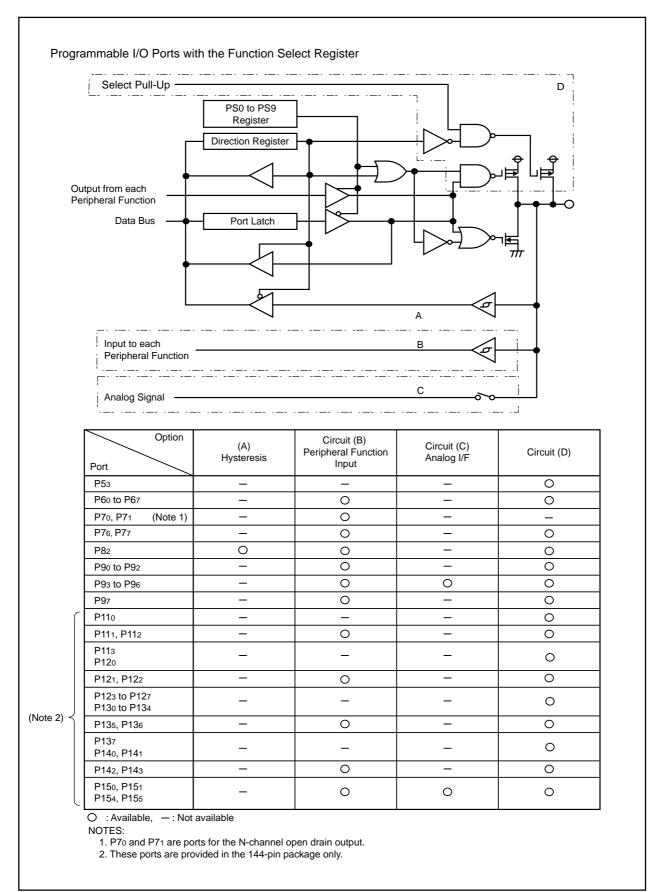

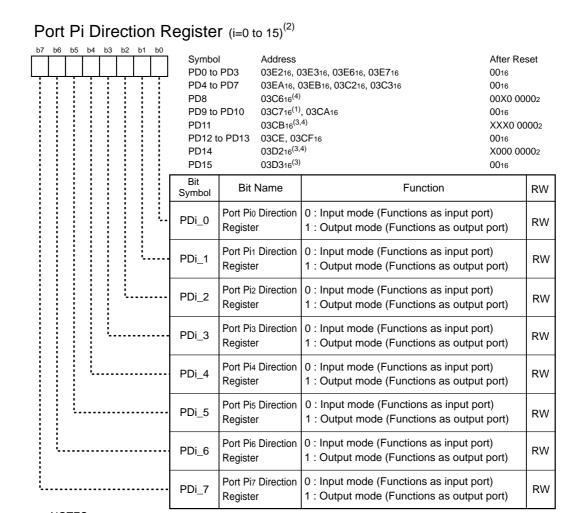

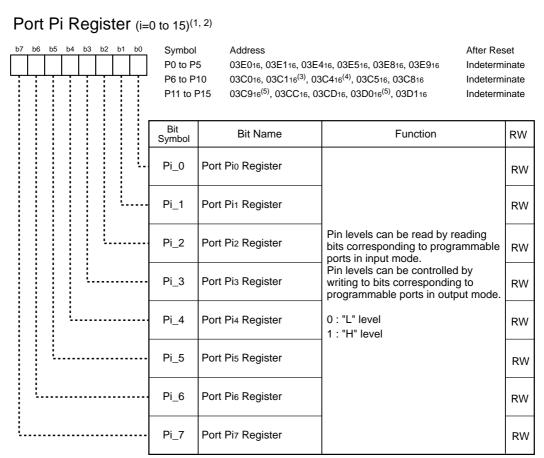

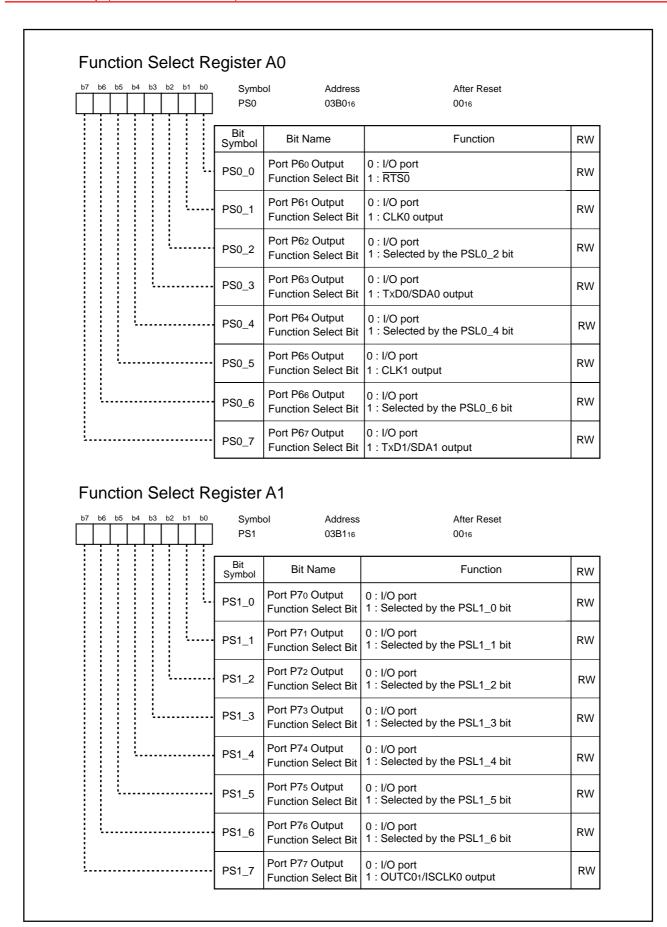

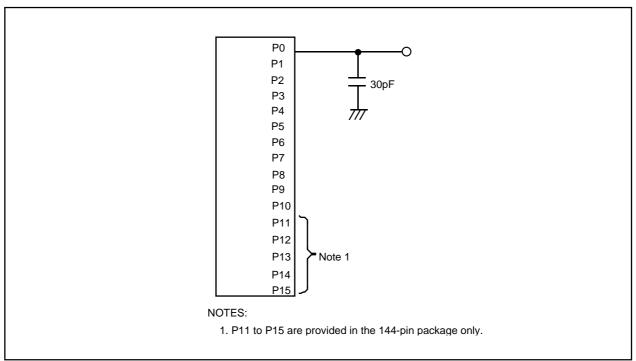

| 24 | 4. Programmable I/O Ports                                                    | 366   |

|    | 24.1 Port Pi Direction Register (PDi Register, i=0 to 15)                    |       |

|    | 24.2 Port Pi Register (Pi Register, i=0 to 15)                               |       |

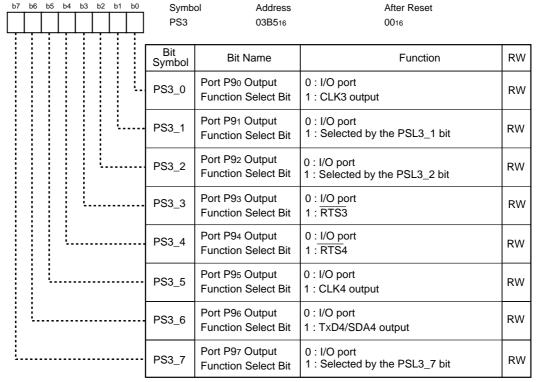

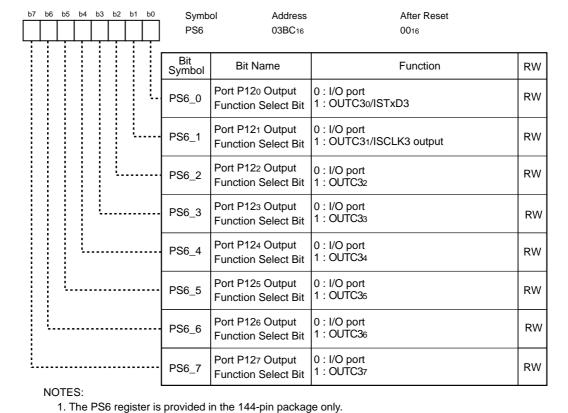

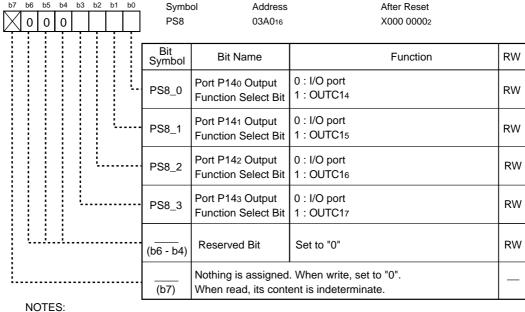

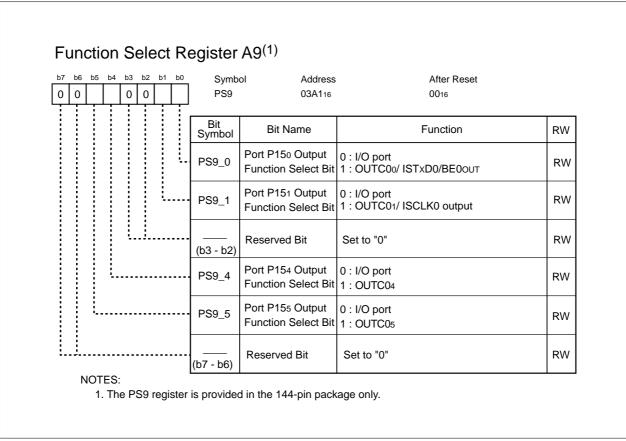

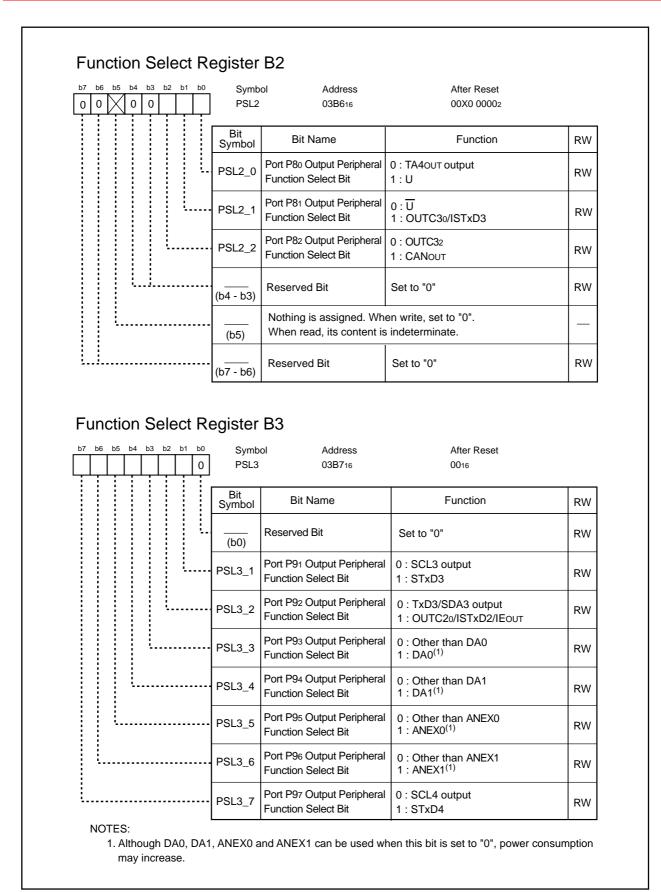

|    | 24.3 Function Select Register Aj (PSj Register) (j=0 to 3, 5 to 9)           |       |

|    | 24.4 Function Select Register Bk (PSLk Register) (k=0 to 3)                  |       |

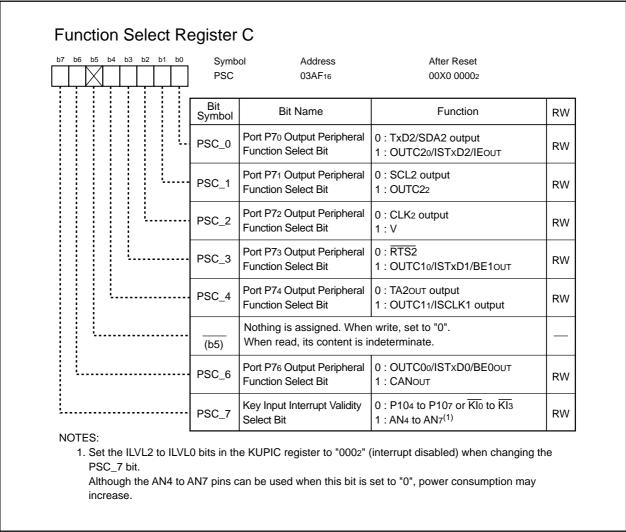

|    | 24.5 Function Select Register C (PSC Register)                               |       |

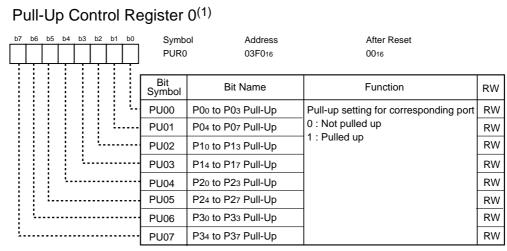

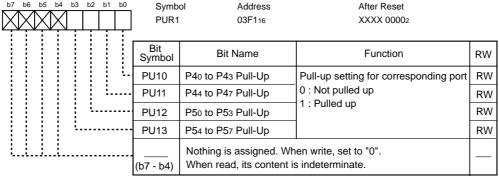

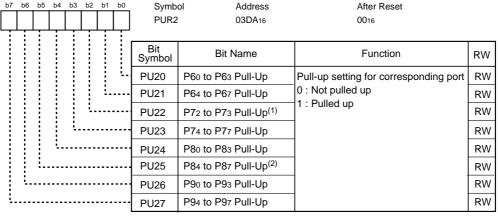

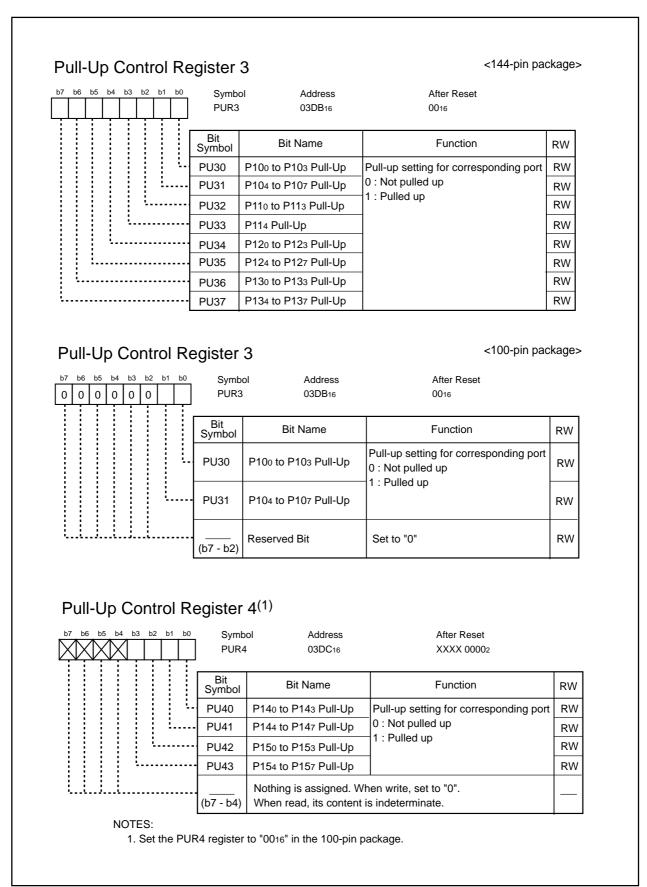

|    | 24.6 Pull-up Control Register 0 to 4 (PUR0 to PUR4 Registers)                |       |

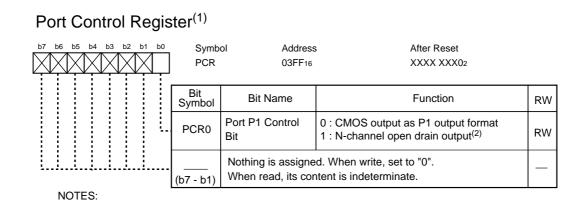

|    | 24.7 Port Control Register (PCR Register)                                    |       |

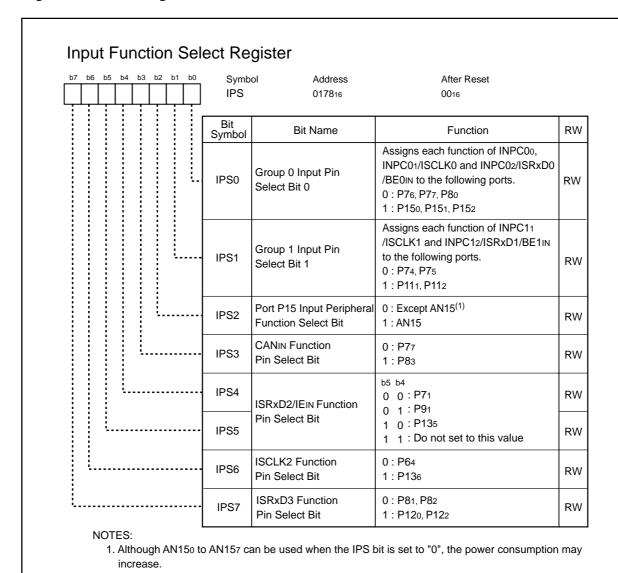

|    | 24.8 Input Function Select Register (IPS Register)                           |       |

|    | 24.9 Analog Input and Other Peripheral Function Input                        |       |

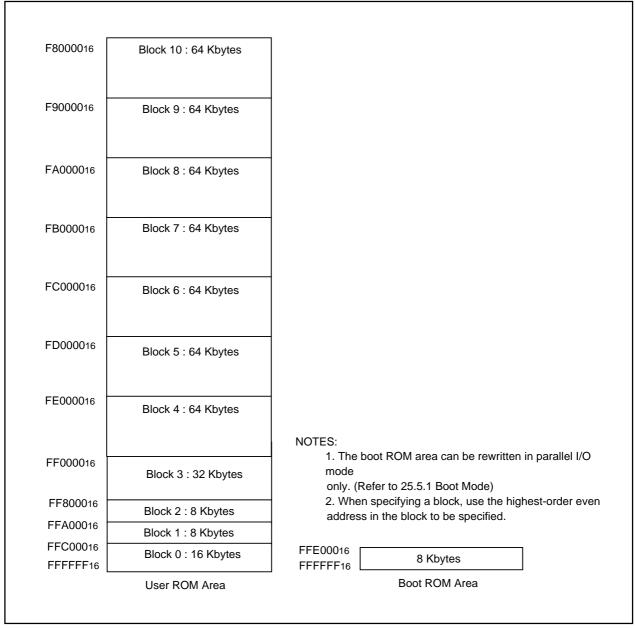

| 25 | 5. Flash Memory Version                                                      | 390   |

|    | 25.1 Memory Map                                                              |       |

|    | 25.1.1 Boot Mode                                                             |       |

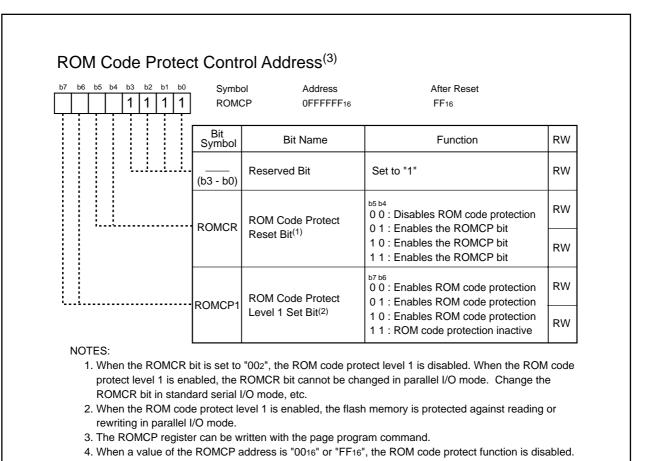

|    | 25.2 Functions to Prevent the Flash Memory from Rewriting                    |       |

|    | 25.2.1 ROM Code Protect Function                                             |       |

|    | 25.2.2 ID Code Verify Function                                               |       |

|    |                                                                              |       |

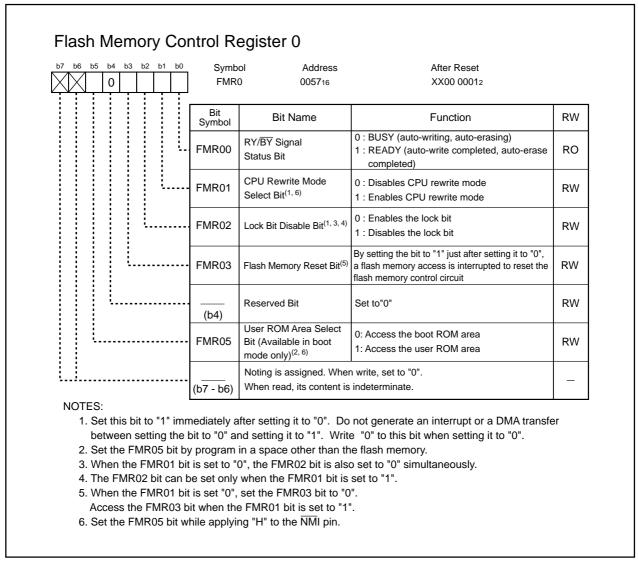

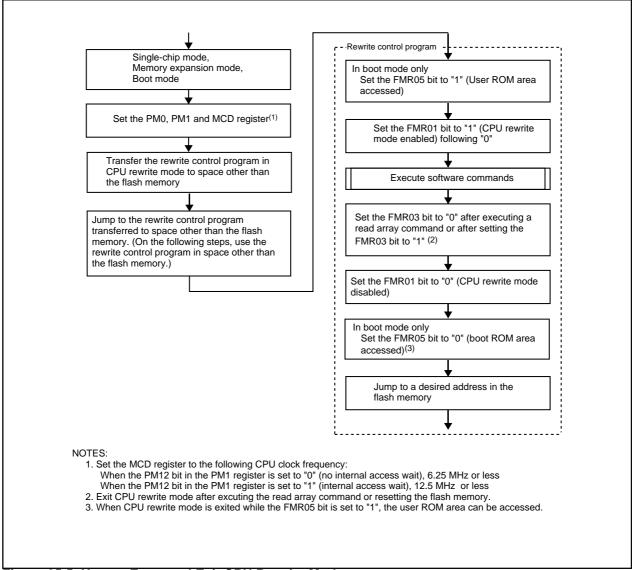

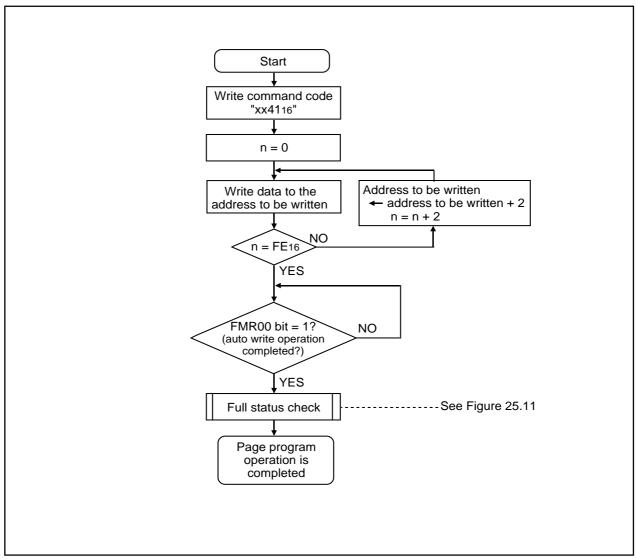

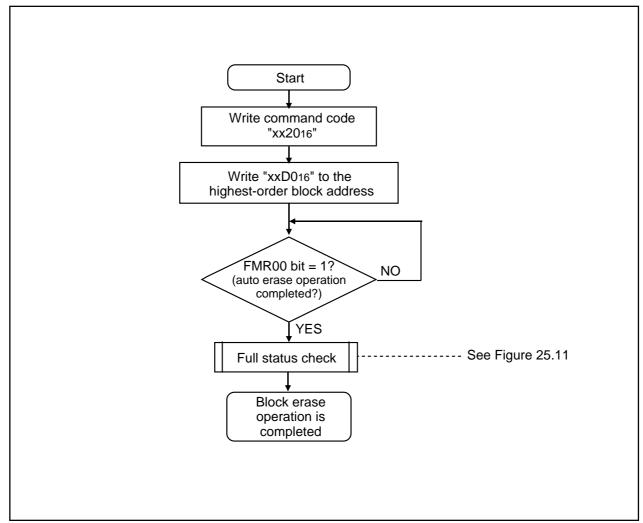

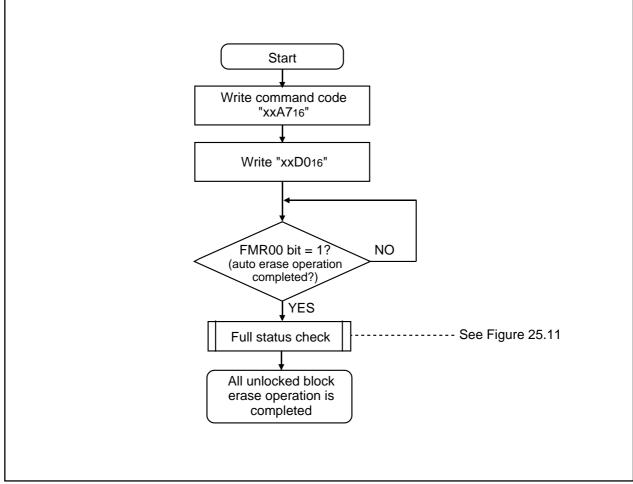

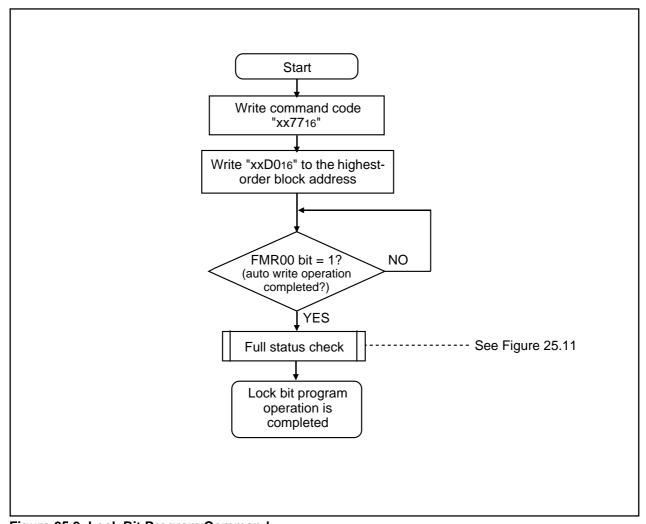

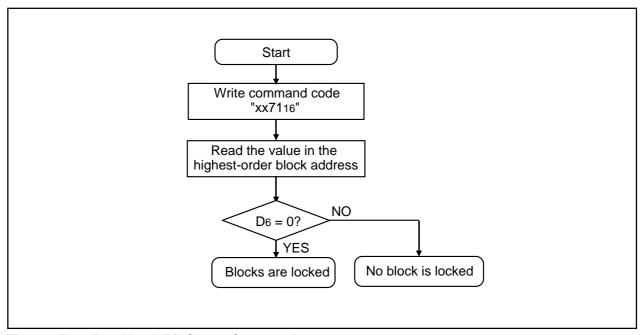

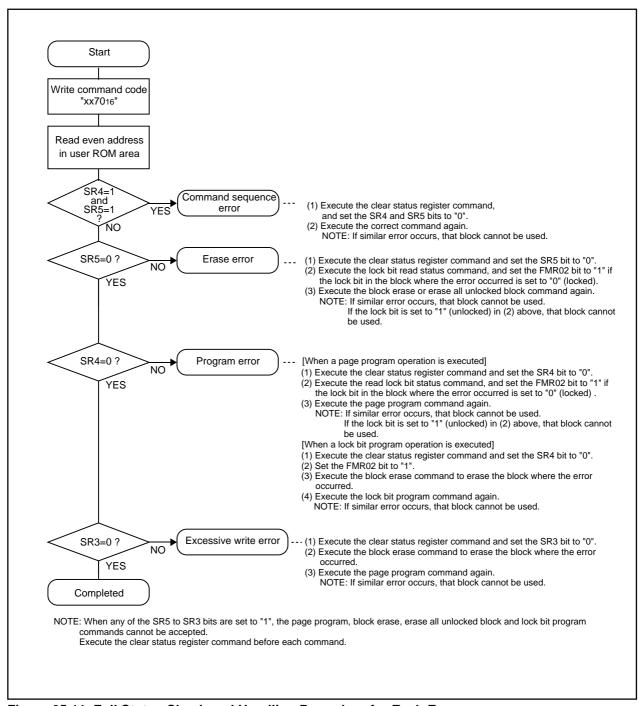

| 25.3 CPU Rewrite Mode                                  | 394 |

|--------------------------------------------------------|-----|

| 25.3.1 Flash Memory Control Register 0 (FMR0 Register) | 395 |

| 25.3.2 Status Register                                 | 397 |

| 25.3.3 Data Protect Function                           | 398 |

| 25.3.4 How to Enter and Exit CPU Rewrite Mode          | 399 |

| 25.3.5 Software Commands                               | 400 |

| 25.3.6 Full Status Check                               | 406 |

| 25.3.7 Precautions in CPU Rewrite Mode                 | 408 |

| 25.4 Standard Serial I/O Mode                          | 409 |

| 25.4.1 Pin Function                                    | 409 |

| 25.4.2 ID Code Verify Function                         | 409 |

| 25.4.3 Precautions in Standard Serial I/O Mode         | 414 |

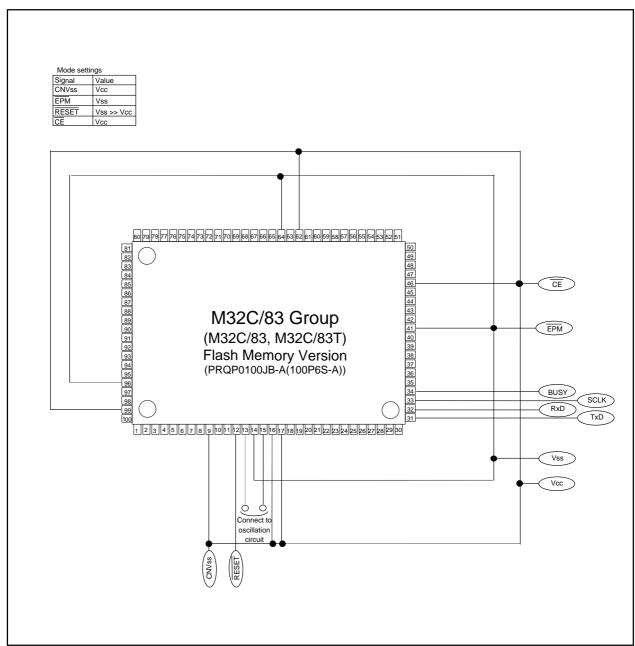

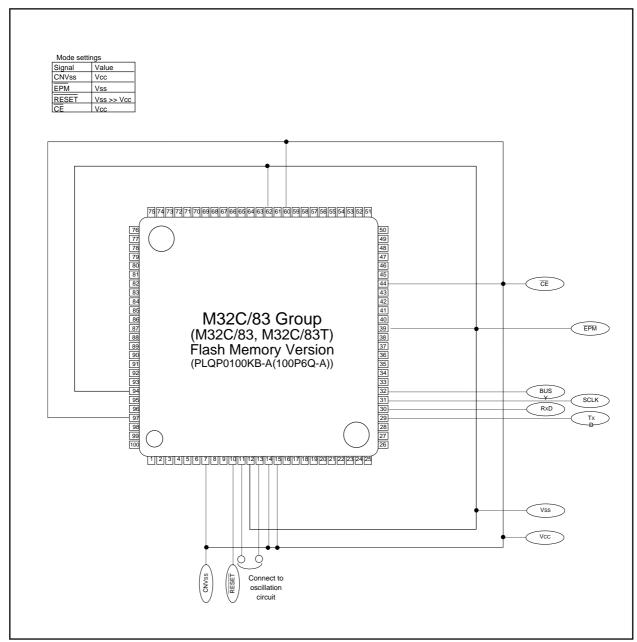

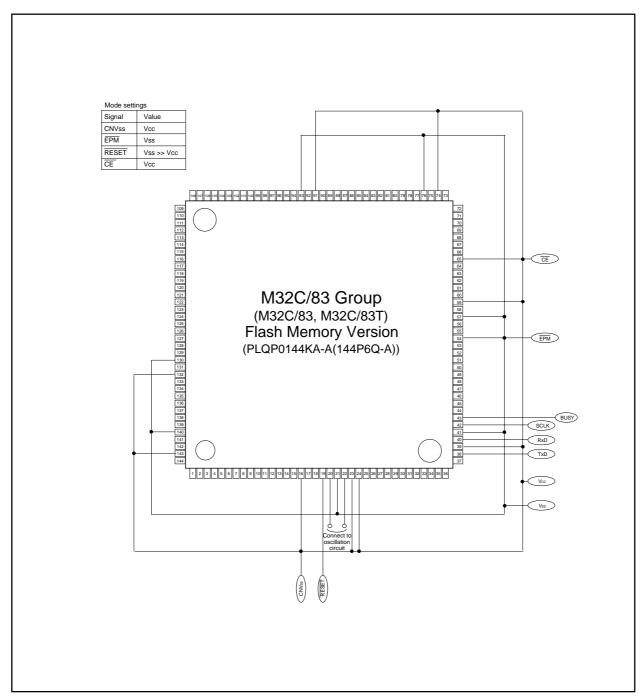

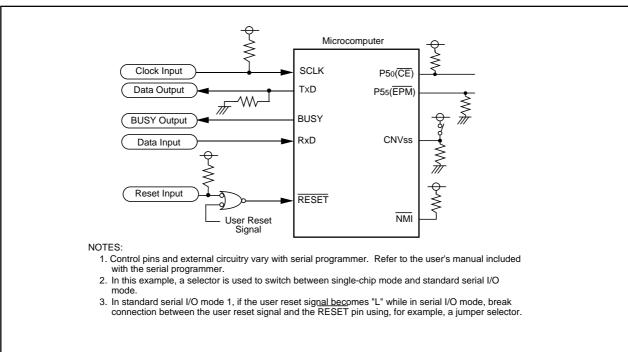

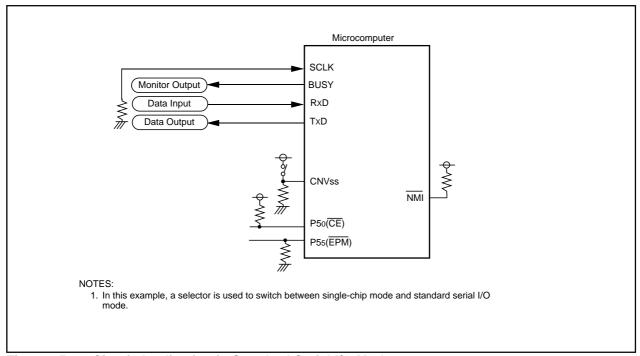

| 25.4.4 Circuit Application in Standard Serial I/O Mode | 414 |

| 25.5 Parallel I/O Mode                                 | 415 |

| 25.5.1 Boot ROM Area                                   | 415 |

| 25.5.2 ROM Code Protect Function                       | 415 |

| 25.5.3 Precautions on Parallel I/O Mode                | 415 |

| 26. Electrical Characteristics                         | 416 |

| 26.1 Electrical Characteristics (M32C/83)              | 416 |

| 26.2 Electrical Characteristics (M32C/83T)             |     |

| 27. Precautions                                        | 462 |

| 27.1 Processor Mode                                    |     |

| 27.1.1 Microprocessor Mode                             | 462 |

| 27.2 Bus                                               |     |

| 27.2.1 HOLD Signal                                     | 463 |

| 27.2.2 External Bus                                    | 463 |

| 27.3 SFR                                               | 464 |

| 27.3.1 100-Pin Package                                 | 464 |

| 27.3.2 Register Settings                               | 464 |

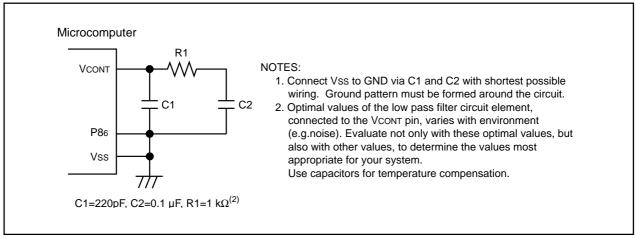

| 27.4 Clock Generation Circuit                          | 465 |

| 27.4.1 PLL Frequency Synthesizer                       | 465 |

| 27.4.2 Power Consumption Control                       | 465 |

| 27.4.3 Wait Mode                                       | 466 |

| 27.4.4 Stop Mode                                       | 466 |

| 27.5 Protection                                        | 467 |

| 27.6 Interrupts                                        | 468 |

| 27.6.1 ISP Setting                                     | 468 |

| 27.6.2 NMI Interrupt                                   | 468 |

| 27.6.3 INT Interrupt                                                    | 468   |

|-------------------------------------------------------------------------|-------|

| 27.6.4 Watchdog Timer Interrupt                                         | 469   |

| 27.6.5 Changing Interrupt Control Register                              | 469   |

| 27.6.6 Changing IIOiIR Register (i = 0 to 11)                           | 469   |

| 27.6.7 Changing RLVL Register                                           | 469   |

| 27.7 DMAC                                                               | 470   |

| 27.8 Timer                                                              | 471   |

| 27.8.1 Timers A and B                                                   | 471   |

| 27.8.2 Timer A                                                          | 471   |

| 27.8.3 Timer B                                                          | 473   |

| 27.9 Three-Phase Motor Control Timer Functions                          | 474   |

| 27.9.1 Changing TAi and TAi1 (i=1, 2, 4) Registers                      | 474   |

| 27.10 Serial I/O                                                        | 475   |

| 27.10.1 Clock Synchronous Serial I/O Mode                               | 475   |

| 27.10.2 UART Mode                                                       | 476   |

| 27.10.3 Special Mode 2                                                  | 476   |

| 27.11 A/D Converter                                                     | 477   |

| 27.12 Intelligent I/O                                                   | 479   |

| 27.12.1 Register Setting                                                | 479   |

| 27.12.2 BTSR Register Setting                                           | 479   |

| 27.13 Programmable I/O Port                                             | 480   |

| 27.14 Flash Memory Version                                              | 481   |

| 27.14.1 Differences Between Flash Memory Version and Masked ROM Version | n 481 |

| 27.15 Noise                                                             | 482   |

| 27.16 Low Voltage Operations                                            | 483   |

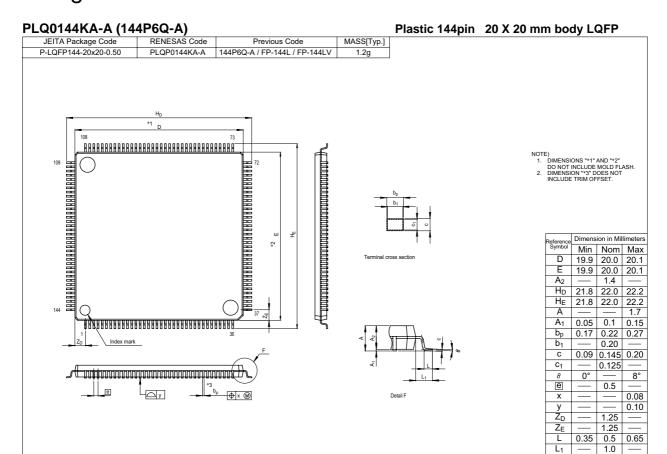

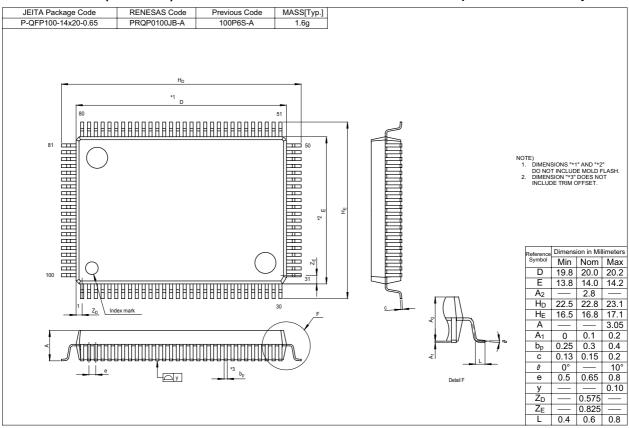

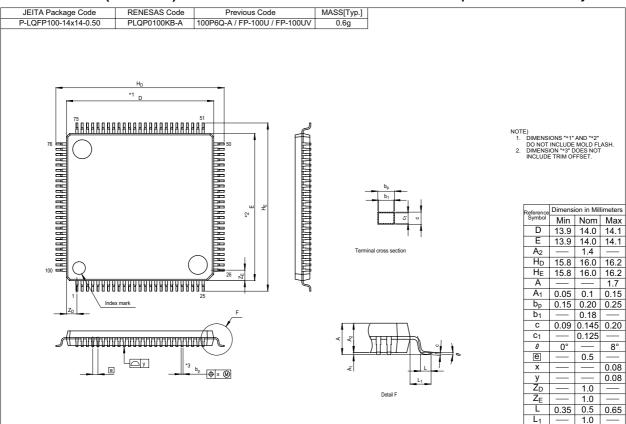

| Package Dimensions                                                      | _ 484 |

| Register Index                                                          | _ 486 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Address | Register                                       | Page | Address | Register                                    | Page |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------------------------------------------|------|---------|---------------------------------------------|------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 000016  |                                                |      |         | •                                           |      |

| 000316   000416   000416   Processor Mode Register 1 (PM1)         49         000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   000316   0                                                                                                                                                                                                                      | 000116  |                                                | 1    | 003116  |                                             |      |

| 000468 Processor Mode Register 0 (PM0)         49 Processor Mode Register 0 (PM1)         500           000568 Processor Mode Register 1 (PM1)         50           000768 System Clock Control Register 1 (CM0)         67           000768 Quarter Clock Control Register 1 (CM1)         68           000868 Wait Control Register 1 (CMC)         58           000869 Address Match Interrupt Enable Register (MEN)         107           000616 Wait Cock Control Register (MCD)         69           000616 Wait Cock Comptol Register (MCD)         70           000616 Waith Cock Division Register (MCD)         70           000161 Waith Color Division Register (MCD)         70           00161 Waith Color Division Register (MCD)         70           00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 000216  |                                                |      | 003216  |                                             |      |

| 000516         Processor Mode Register 1 (PMT)         50           000516         System Clock Control Register 0 (CM0)         68           000918         Wait Control Register 1 (WCR)         58           000918         Address Match Interrupt Enable Register (AIER)         107           000416         Protect Register (PRCR)         88           000510         Control Clock Division Register (CM2)         70           000616         Matchdog Timer Start Register (WDC)         112           00116         Address Match Interrupt Register (MDC)         117           00121e         Address Match Interrupt Register (RMAD)         107           00131e         Address Match Interrupt Register 1 (RMAD)         107           00131e         Address Match Interrupt Register 1 (RMAD)         107           00131e         Address Match Interrupt Register 2 (RMAD2)         107           00131e         VDC Control Register 10 (VDC)         107           00131e         Address Match Interrupt Register 3 (RMAD3)         107           00151e         Address Match Interrupt Register 3 (RMAD3)         107           00151e         OUCcontrol Register 0 (VDC)         104           00151e         OUCcontrol Register 0 (VDC)         104           00151e         0UCco                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 000316  |                                                |      | 003316  |                                             |      |

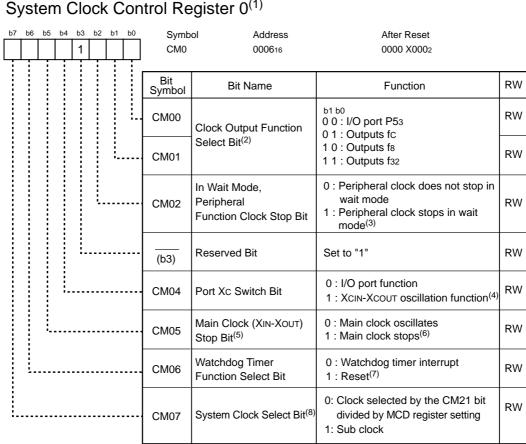

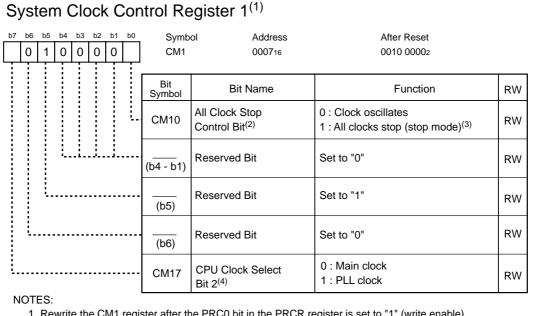

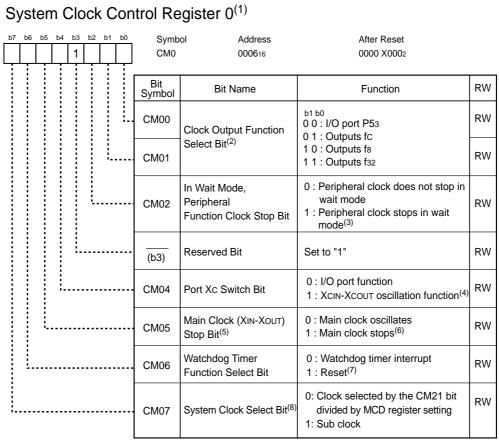

| 000616         System Clock Control Register 0 (CM0)         67           000716         System Clock Control Register 1 (CM1)         68           000916         Address Match Interrupt Enable Register (AIER)         107           000016         External Data Bus Wirdth Control Register (CM2)         52           000016         Main Clock Division Register (MCD)         69           000016         Watchdog Timer Start Register (WDTS)         70           0001616         Watchdog Timer Control Register (DRA)         107           0011616         Address Match Interrupt Register 0 (RMAD0)         107           0011616         Address Match Interrupt Register 1 (RMAD1)         107           001516         Address Match Interrupt Register 2 (RMAD2)         107           001516         DOC Control Register (VDCO)         72           001516         Address Match Interrupt Register 3 (RMAD3)         107           001516         Address Match Interrupt Register (MDC)         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 000416  | Processor Mode Register 0 (PM0)                | 49   | 003416  |                                             |      |

| 000716         System Clock Control Register 1 (WCR)         58           000816         Valid Control Register 1 (WCR)         58           000816         Protect Register (PRCR)         88           000816         External Data Bus Width Control Register (MCD)         69           000016         Main Clock Division Register (MCD)         69           000016         Watchdog Timer Start Register (WDC)         70           001116         Address Match Interrupt Register of (RMAD)         117           001116         Address Match Interrupt Register (RMAD)         107           001318         Address Match Interrupt Register (RMAD)         107           001318         Address Match Interrupt Register (RMAD)         107           001518         Address Match Interrupt Register (RMAD)         107           001181         Address Match Interrupt Register (MDC)         004316                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 000516  | Processor Mode Register 1 (PM1)                | 50   | 003516  |                                             |      |

| 000816 Nati Control Register 1 (WCR)         58           000816 Address Match Interrupt Enabla Register (AIER)         107           000816 External Data Bus Width Control Register (DKC)         88           000816 External Data Bus Width Control Register (MCD)         70           000016 Oscillation Stop Detect Register (MCD)         70           000116 Watchdog Timer Control Register (WDC)         107           001116 Address Match Interrupt Register 0 (RMADD)         107           001118 Address Match Interrupt Register 1 (RMAD1)         107           00118 Address Match Interrupt Register 1 (RMAD1)         107           00118 Address Match Interrupt Register 2 (RMAD2)         107           00119 Address Match Interrupt Register 2 (RMAD2)         107           001116 Address Match Interrupt Register 2 (RMAD2)         107           00118 OD151 Address Match Interrupt Register 3 (RMAD3)         107           00118 OD151 Address Match Interrupt Register 3 (RMAD3)         107           00116 OD151 Address Match Interrupt Register 3 (RMAD3)         107           00116 OD151 Address Match Interrupt Register 3 (RMAD3)         107           00116 OD151 Address Match Interrupt Register 3 (RMAD3)         107           00116 OD151 Address Match Interrupt Register 3 (RMAD3)         107           00116 OD151 Address Match Interrupt Register (WDC)         100 MD16 (MD16)<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 000616  | System Clock Control Register 0 (CM0)          | 67   | 003616  |                                             |      |

| 000466 Address Match Interrupt Enable Register (AIER)         107           000460 Protect Register (PRCR)         88           000016 Exemal Data Bus Width Control Register (DS)         52           00016 Main Clock Division Register (MCD)         69           00016 Watchdog Timer Start Register (WDC)         70           000116 Watchdog Timer Control Register (WDC)         112           001116 Online         Address Match Interrupt Register 0 (RMADD)         117           001316 Online         Address Match Interrupt Register 1 (RMADD)         107           001416 Online         Address Match Interrupt Register 1 (RMADD)         107           001510 Online         Address Match Interrupt Register 2 (RMADD)         107           001516 Online         Address Match Interrupt Register 2 (RMADD)         72           001518 Online         Address Match Interrupt Register 2 (RMADD)         72           001519 Address Match Interrupt Register 3 (RMADD)         107           001510 Online         000510 Online           001510 Address Match                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 000716  | System Clock Control Register 1 (CM1)          | 68   | 003716  |                                             |      |

| 0000146   Once   Protect Register (PRCR)   External Data Bus Wirdth Control Register (MCD)   69         52           000016   Machodg Timer Start Register (MCD)   000016   Watchdog Timer Start Register (WDC)   00116   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146   001146                                                                                                                                                                                                                                       | 000816  | Wait Control Register 1 (WCR)                  | 58   | 003816  |                                             |      |

| 0000161 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 00000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 0000160 00000160 00000160 00000160 00000160 00000160 00000160 00000160 00000160 00000160 00000160 00000160 00000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 000916  | Address Match Interrupt Enable Register (AIER) | 107  | 003916  |                                             |      |

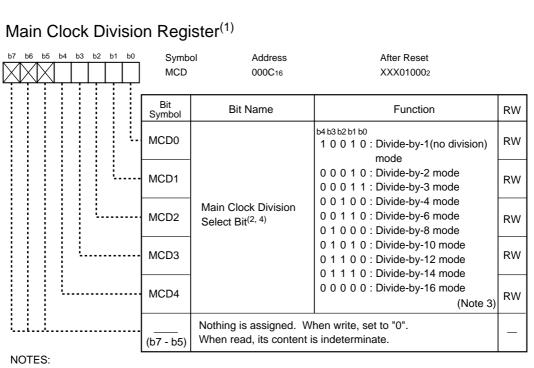

| 000016   Main Clock Division Register (MCD)         69           000016   Watchdog Timer Star Register (WDTS)         112           001016   Octobrol Register (MCD)         112           00016   Watchdog Timer Star Register (WDC)         1107           00116   Octobrol Register (MCD)         1107           00116   Octobrol Register (MCD)         1107           001316   Octobrol Register (MCD)         1107           001316   Octobrol Register (MCD)         1107           001516   Octobrol Register (MCD)         107           001516   Octobrol Register (MCD)         107           001716   Octobrol Register (MCD)         107           001816   Octobrol Register (MCD)         107           001816   Octobrol Register (MCD)         107           001916   Octobrol Register (MCD)         004           001916                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 000A16  | Protect Register (PRCR)                        | 88   | 003A16  |                                             |      |

| 00016 0 Ocillation Stop Detect Register (CM2) 0000F16 Watchdog Timer Start Register (WDTS) 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016 001016                                                                                                                                                                                                     | 000B16  | External Data Bus Width Control Register (DS)  | 52   | 003B16  |                                             |      |

| 000E16         Watchdog Timer Start Register (WDC)         003E16         003F16         004M Control Register (REFCNT)         00416         004M Refresh Interval Set Register (REFCNT)         004216         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 000C16  | Main Clock Division Register (MCD)             | 69   | 003C16  |                                             |      |

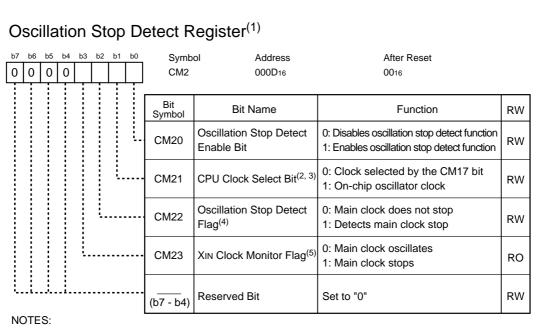

| 000166 000166 000166 000166 000166 000166 000166 000166 000166 000166 000166 000166 000166 000166 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 0001666 00016                                                                                                                                                                                                    | 000D16  | Oscillation Stop Detect Register (CM2)         | 70   | 003D16  |                                             |      |

| 0001-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010-16   0010                                                                                                                                                                               | 000E16  | Watchdog Timer Start Register (WDTS)           |      | 003E16  |                                             |      |

| 001116 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216 001216                                                                                                                                                                                                     | 000F16  | Watchdog Timer Control Register (WDC)          | 112  | 003F16  |                                             |      |

| 001116 001216 001216 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316 001316                                                                                                                                                                                                     | 001016  |                                                |      | 004016  | DRAM Control Register (DRAMCONT)            | 360  |

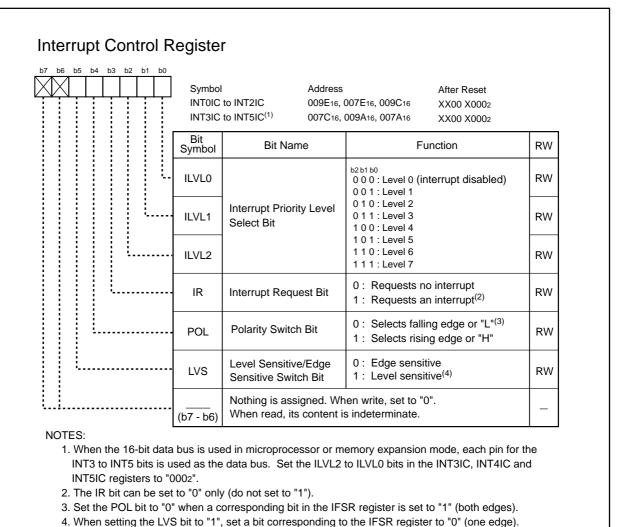

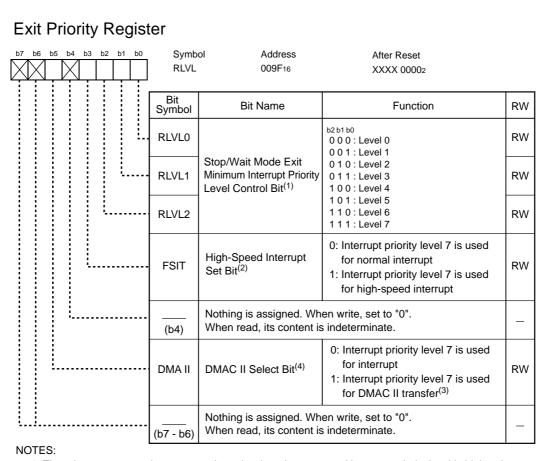

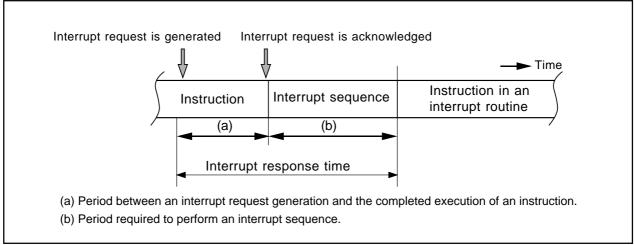

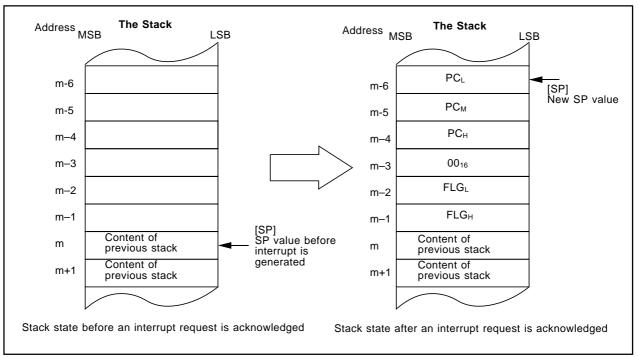

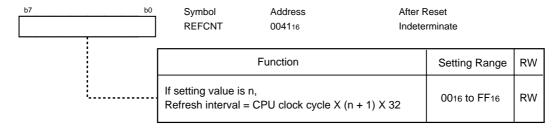

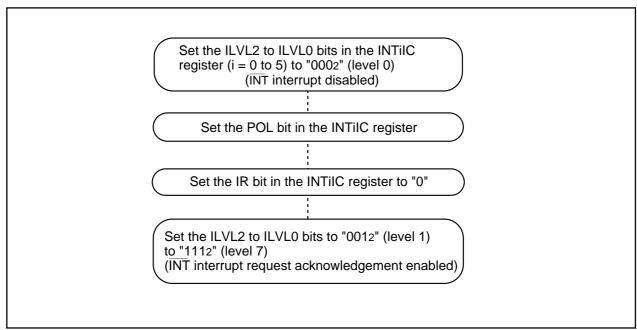

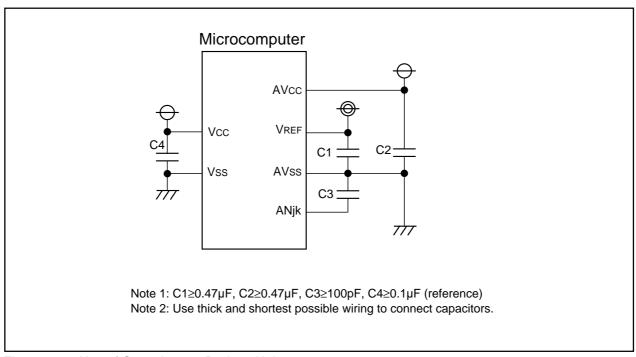

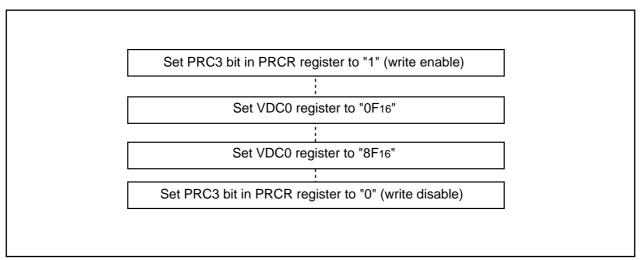

| 001316         001416         001416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004518         004518         004518         004518         004518         004716         004716         004716         004716         004716         004716         004716         004716         004716         004716         004818         004716         004816         004716         004816         004816         004816         004816         004816         004816         004816         004816         004816         004816         004816         004816         004816         004816         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416         004416<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 001116  | Address Match Interrupt Register 0 (RMAD0)     | 107  | 004116  | DRAM Refresh Interval Set Register (REFCNT) | 300  |