#### **General Description**

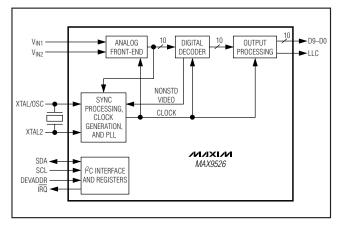

The MAX9526 is a low-power video decoder that converts NTSC or PAL composite video signals to 8-bit or 10-bit YCbCr component video compliant with the ITU-R BT.656 standard. The device powers up in fully operational mode and automatically configures itself to decode the detected input standard. The MAX9526 typically consumes 200mW of power in normal operation and typically less than 100µW in shutdown mode.

An internal 10-bit, 54MHz analog-to-digital converter (ADC) samples the input with four times oversampling. The MAX9526 features a DC restoration circuit with offset correction and automatic gain control to accurately optimize the full-scale range of the ADC.

An integrated analog anti-aliasing filter eliminates the need for external filtering. The MAX9526 includes a 2:1 input multiplexer with automatic signal selection based on activity at the inputs.

An internal line-locked phase-locked loop (PLL) generates the sample clock and the line-locked clock (LLC) output to provide an ITU-compliant output. Alternatively, the PLL can be configured to provide a sample clock and output clock at 2x and 1x the frequency of the crystal oscillator, respectively.

The MAX9526 provides a multiline adaptive comb filter to reduce cross-chrominance and cross-luminance artifacts.

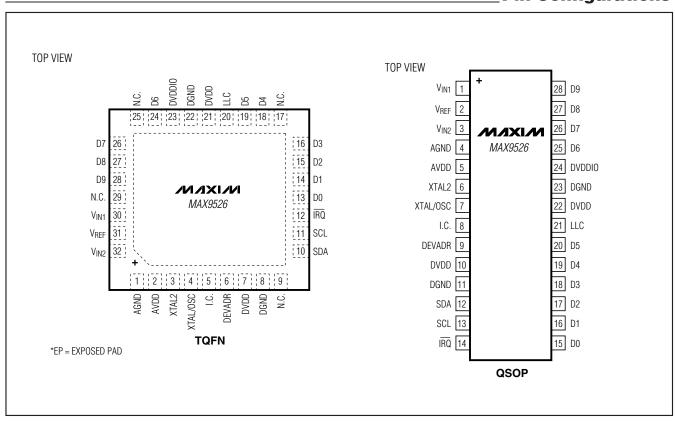

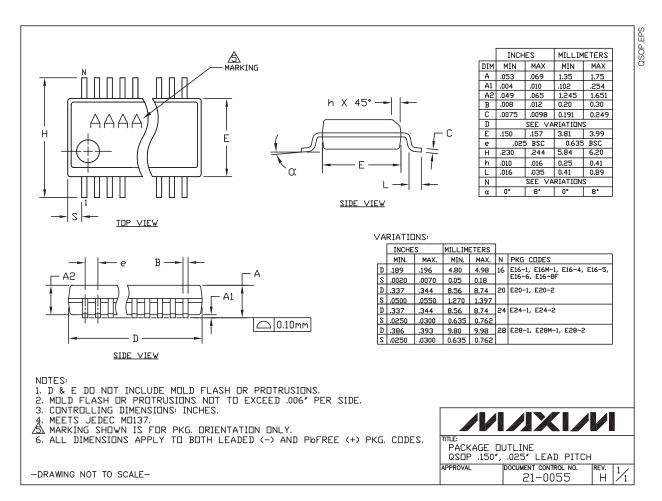

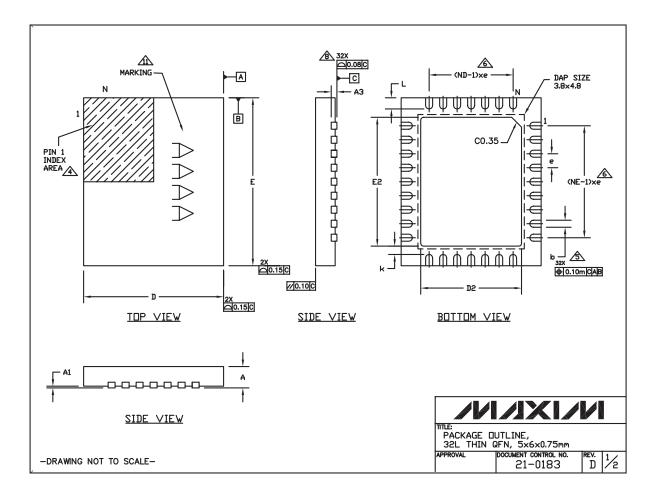

A single 1.8V supply is used for both the digital and analog supplies. The digital outputs operate from a separate +1.7V to +3.45V supply to allow direct connection to a wide range of digital processors. The MAX9526 operates over the -40°C to +125°C automotive temperature range and is available in both a 28-pin QSOP and a 32-pin TQFN (5mm x 6mm).

#### **Applications**

Automotive Entertainment Systems Collision Avoidance Systems Security Surveillance/CCTV Systems **Televisions**

#### **Features**

- ♦ Supports All NTSC and PAL Standards NTSC M. NTSC J. NTSC 4.43. PAL B/G/H/I/D, PAL M, PAL N, PAL 60

- **♦** Easy to Configure and Operate with Only 16 User-Programmable Registers

- ♦ Automatic Configuration and Standard Select

- ♦ 10-Bit 4x Oversampling (54Msps) ADC with True 10-Bit Digital Processing

- ♦ Flexible Output Formatting

- 10-Bit Parallel ITU-R BT.656 Output with **Embedded TRS**

- 8-Bit Parallel ITU-R BT.656 Output with Separate **HS and VS**

- ♦ +1.8V Digital and Analog Supply Voltage

- ♦ +1.7V to +3.45V Digital I/O Supply Voltage

- **♦** Full Automotive Temperature Range (-40°C to +125°C)

- **♦ Low-Power Modes** Shutdown (< 100µW typ) **Sleep Mode with Continuous Activity Detection** (< 5mW typ)

- ♦ 2-to-1 Video Input Mux with AGC

#### **Ordering Information**

| PART        | TEMP RANGE      | PIN-PACKAGE |

|-------------|-----------------|-------------|

| MAX9526AEI+ | -40°C to +125°C | 28 QSOP     |

| MAX9526ATJ+ | -40°C to +125°C | 32 TQFN-EP* |

<sup>+</sup>Denotes lead(Pb)-free/RoHS-compliant package.

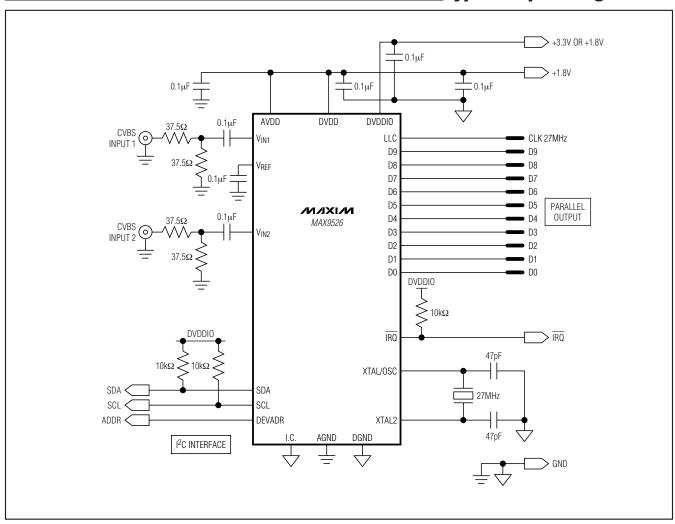

#### Functional Diagram

<sup>\*</sup>EP = Exposed pad.

#### **ABSOLUTE MAXIMUM RATINGS**

| AVDD to AGND0.3V to +2V                                                             |

|-------------------------------------------------------------------------------------|

| DVDD to DGND0.3V to +2V                                                             |

| DVDDIO to DGND0.3V to +3.6V                                                         |

| AGND to DGND0.1V to +0.1V                                                           |

| D9–D0, LLC to DGND0.3V to (DVDDIO + 0.3V)                                           |

| V <sub>IN1</sub> , V <sub>IN2</sub> , V <sub>REF</sub> to AGND0.3V to (AVDD + 0.3V) |

| XTAL/OSC, XTAL2 to AGND0.3V to +2V                                                  |

| TRQ, SDA, SCL, DEVADR to DGND0.3V to +3.6V                                          |

| Continuous Current In/Out All Pins±50mA                                             |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C)                               |

| 28-Pin QSOP Single-Layer Board                                                      |

| (derate 10.8mW/°C above +70°C)860mW                                                 |

| 28-Pin QSOP Multilayer Board      |                |

|-----------------------------------|----------------|

| (derate 12.6mW°C above +70°C)     | 1009mW         |

| 32-Pin TQFN Multilayer Board      |                |

| (derate 20.8mW/°C above +70°C)    | 1663mW         |

| Operating Temperature Range       | 40°C to +125°C |

| Junction Temperature              | +150°C         |

| Storage Temperature Range         |                |

| Lead Temperature (soldering, 10s) | +300°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{AVDD} = V_{DVDD} = +1.8V, V_{DVDDIO} = +3.3V, AGND = DGND = 0, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}C.)$  (Note 1)

| PARAMETER                                 | SYMBOL             | CONDITIONS                                   | MIN    | TYP | MAX  | UNITS            |

|-------------------------------------------|--------------------|----------------------------------------------|--------|-----|------|------------------|

| SUPPLIES                                  | •                  |                                              |        |     |      |                  |

| Analog Supply Voltage Range               | AVDD               |                                              | 1.7    | 1.8 | 1.9  | V                |

| Digital Supply Voltage Range              | DVDD               |                                              | 1.7    | 1.8 | 1.9  | V                |

| Digital I/O Supply Voltage Range          | DVDDIO             |                                              | 1.7    | 3.3 | 3.45 | V                |

|                                           |                    | Normal operation                             |        | 42  | 55   | mA               |

| Analog Supply Current (Note 2)            | IAVDD              | Sleep mode                                   |        | 2.2 | 3    | MA               |

| (Note 2)                                  |                    | Shutdown                                     |        | 0.5 | 100  | μΑ               |

|                                           |                    | Normal operation                             |        | 70  | 110  | mA               |

| Digital Supply Current (Note 2)           | I <sub>DVDD</sub>  | Sleep mode                                   |        | 5   | 1000 |                  |

| (Note 2)                                  |                    | Shutdown                                     |        | 5   | 1000 | μΑ               |

|                                           | IDVDDIO            | Normal operation, V <sub>DVDDIO</sub> = 1.8V | 3.5    |     | mA   |                  |

| Digital I/O Supply Current                |                    | Normal operation, V <sub>DVDDIO</sub> = 3.3V |        | 6.4 |      |                  |

| (Note 2)                                  |                    | Sleep mode, V <sub>DVDDIO</sub> = 3.3V       | 0.8 10 |     |      |                  |

|                                           |                    | Shutdown, V <sub>DVDDIO</sub> = 3.3V         |        | 0.8 | 10   | μΑ               |

| VIDEO INPUTS, V <sub>REF</sub> , AND CLAN | IP                 |                                              |        |     |      |                  |

| Input Voltage Range                       |                    | Guaranteed by full-scale conversion range    | 0.27   | 0.5 | 0.83 | V <sub>P-P</sub> |

| Input Resistance                          | RIN                |                                              |        | 2   |      | МΩ               |

| Input Capacitance                         | CIN                |                                              |        | 8   |      | рF               |

| Video Input Reference Voltage (VREF)      | V <sub>REF</sub>   |                                              |        | 850 |      | mV               |

| Sync-Tip Clamp Level                      | V <sub>CLMP2</sub> | Activity detect clamp                        |        | 550 |      | mV               |

| Input Clamping Current                    |                    | Activity detect clamp, VVIN = VCLMP2 + 150mV |        | 2.0 |      | μА               |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = V_{DVDD} = +1.8V, V_{DVDDIO} = +3.3V, AGND = DGND = 0, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}C.) \text{ (Note 1)}$

| PARAMETER                              | SYMBOL           | CONDITIONS                                                                                                            |                                                                        | MIN | TYP   | MAX | UNITS             |  |

|----------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-----|-------|-----|-------------------|--|

| Sync Slice Comparator Level            |                  | Activity detect slicer, refe                                                                                          | renced to V <sub>CLMP</sub>                                            |     | 50    |     | mV                |  |

|                                        |                  | Slow                                                                                                                  |                                                                        |     | 3     |     |                   |  |

| DC Restore Current DAC Full-           |                  | Medium                                                                                                                |                                                                        |     | 6     |     | μΑ                |  |

| Scale Range (Source and Sink) (Note 3) |                  | Medium-fast (default)                                                                                                 |                                                                        |     | 12    |     |                   |  |

| (Note 3)                               |                  | Fast                                                                                                                  |                                                                        |     | 24    |     |                   |  |

| DC Restore Sync-Tip Level at           |                  | AGCGAIN = 0x0, ADAGC                                                                                                  | C = 1                                                                  |     | 0.51  |     | V                 |  |

| $V_{IN1}N_{IN2}$                       |                  | AGCGAIN = 0xF, ADAGC                                                                                                  | C = 1                                                                  |     | 0.72  |     | ]                 |  |

| ANALOG INPUT FILTER AND AD             | OC (Note 4)      |                                                                                                                       |                                                                        |     |       |     |                   |  |

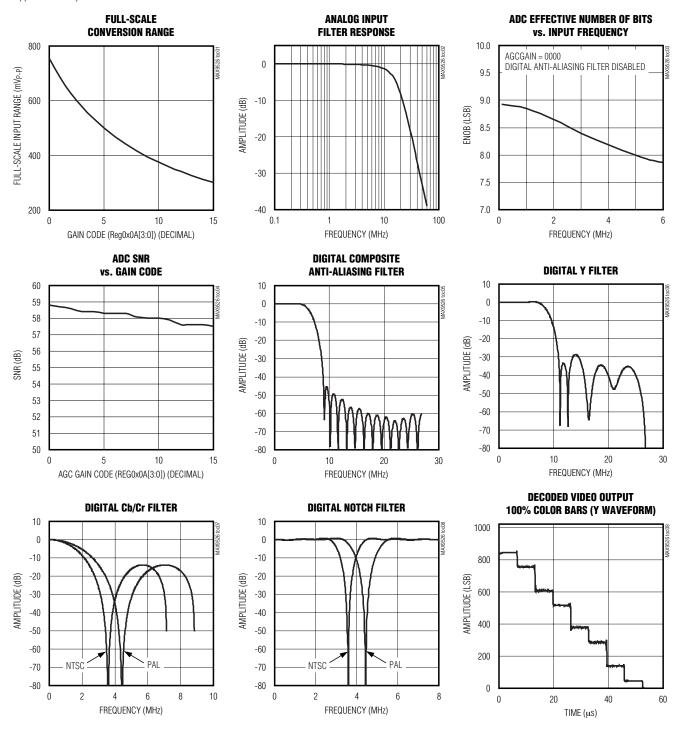

| Cutoff Frequency (3dB)                 | f <sub>3dB</sub> |                                                                                                                       |                                                                        |     | 13    |     | MHz               |  |

| Passband Flatness                      |                  | f < 5MHz, V <sub>VIN</sub> = 0.65V <sub>P-1</sub><br>measured at 1MHz                                                 | P, reference level                                                     |     | 0.25  |     | dB                |  |

| Stopband Cutoff                        | fSB              |                                                                                                                       |                                                                        |     | 53    |     | MHz               |  |

| Stopband Attenuation                   |                  | f > f <sub>SB</sub> , V <sub>VIN</sub> = 0.65V <sub>P-P</sub> , r<br>measured at 1MHz                                 | reference level                                                        |     | 36    |     | dB                |  |

| Full Scale Conversion Dange            |                  | AGC disabled, gain programmed                                                                                         | AGCGAIN = 0x0                                                          | 670 |       | 830 | m\/a a            |  |

| Full-Scale Conversion Range            |                  | using I <sup>2</sup> C (ADAGC = 1), referenced to V <sub>IN1</sub> /V <sub>IN2</sub>                                  | AGCGAIN = 0xF                                                          | 270 |       | 330 | mV <sub>P-P</sub> |  |

| AGC Gain Stepsize                      |                  |                                                                                                                       |                                                                        |     | 0.167 |     | V/V               |  |

| Differential Nonlinearity              | DNL              | AGCGAIN = 0x0, ADAGC                                                                                                  | C = 1                                                                  |     | ±0.5  |     | LSB               |  |

| Integral Nonlinearity                  | INL              | AGCGAIN = 0x0, ADAGC                                                                                                  | C = 1                                                                  |     | ±1    |     | LSB               |  |

| Signal-to-Noise Ratio                  | SNR              | Includes filter + ADC + dig<br>filter, input is -1dBFS; ADA<br>AGCGAIN[3:0] = 0x0, defi<br>RMS signal to RMS noise in | GC = 1,<br>ned as ratio of                                             |     | 58.8  |     | dB                |  |

|                                        |                  |                                                                                                                       | 1.7V < V <sub>AVDD</sub> <<br>1.9V, 1.7V <<br>V <sub>DVDD</sub> < 1.9V |     |       | -40 |                   |  |

| Power-Supply Rejection                 | DOD              | ADAGC = 1<br>AGCGAIN[3:0] = 0x0                                                                                       | V <sub>AVDD</sub> = 1.8V +<br>100mV <sub>P-P</sub> at<br>500kHz        |     | -67   |     | 4DE0              |  |

|                                        | PSR              | input level = 1MHz sine<br>wave at -2dBFS                                                                             | $V_{AVDD} = 1.8V + 100 \text{mV}_{P-P} \text{ at}$ 3.58MHz             |     | -58   |     | - dBFS            |  |

|                                        |                  |                                                                                                                       | V <sub>AVDD</sub> = 1.8V +<br>100mV <sub>P-P</sub> at<br>4.43MHz       |     | -57   |     |                   |  |

| Differential Phase                     | DP               | 5-step modulated staircas<br>f = 3.58MHz or 4.43MHz                                                                   | Se,                                                                    |     | 1.0   |     | degrees           |  |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = V_{DVDD} = +1.8V, V_{DVDDIO} = +3.3V, AGND = DGND = 0, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}C.) \text{ (Note 1)}$

| PARAMETER                                           | SYMBOL          | CONDITIONS                                                                                            | MIN TYP | MAX | UNITS  |

|-----------------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------|---------|-----|--------|

| Differential Gain                                   | DG              | 5-step modulated staircase,<br>f = 3.58MHz or 4.43MHz                                                 | 1       |     | %      |

| 2T Pulse Response                                   |                 | 2T = 200ns or 250ns                                                                                   | 0.4     |     | %      |

| 2T Bar Response                                     |                 | Bar time is 18µs, the beginning 2.5% and ending 2.5% of the bar time are ignored, 2T = 200ns or 250ns | 0.2     |     | %      |

| 2T Pulse to Bar Rating                              |                 | Bar time is 18µs, the beginning 2.5% and ending 2.5% of the bar time are ignored, 2T = 200ns or 250ns | 0.2     |     | %      |

| Group Delay Distortion                              |                 | 100kHz < f < 5MHz                                                                                     | ±1      |     | ns     |

| DECODED LUMINANCE AND CHR                           | OMINANCE (      | CHANNELS (Note 5)                                                                                     |         |     | •      |

| Chroma Bandwidth                                    | BW <sub>C</sub> |                                                                                                       | 1       |     | MHz    |

| Luma Bandwidth                                      | BWL             |                                                                                                       | 5.5     |     | MHz    |

| Luma Nonlinearity                                   |                 | 5-step staircase                                                                                      | 1       |     | %      |

| Luma Line Time Distortion (H-Tilt)                  | LD              | Measured at the output regarding active video                                                         | 0.5     |     | %      |

| Luma Field Time Distortion (V-Tilt)                 | FD              | Measured at the output regarding active video                                                         | 0.1     |     | %      |

| DIGITAL COMPOSITE DECODER                           |                 |                                                                                                       |         |     |        |

| Lock Time                                           |                 |                                                                                                       | 3       |     | frames |

| Horizontal Line Time Static Variation               |                 |                                                                                                       | -5      | +5  | %      |

| Maximum Horizontal Line Time<br>Jitter (Async Mode) |                 |                                                                                                       | 5       |     | μs     |

| Maximum Horizontal Line Time<br>Jitter (LLC mode)   |                 |                                                                                                       | 160     |     | ns     |

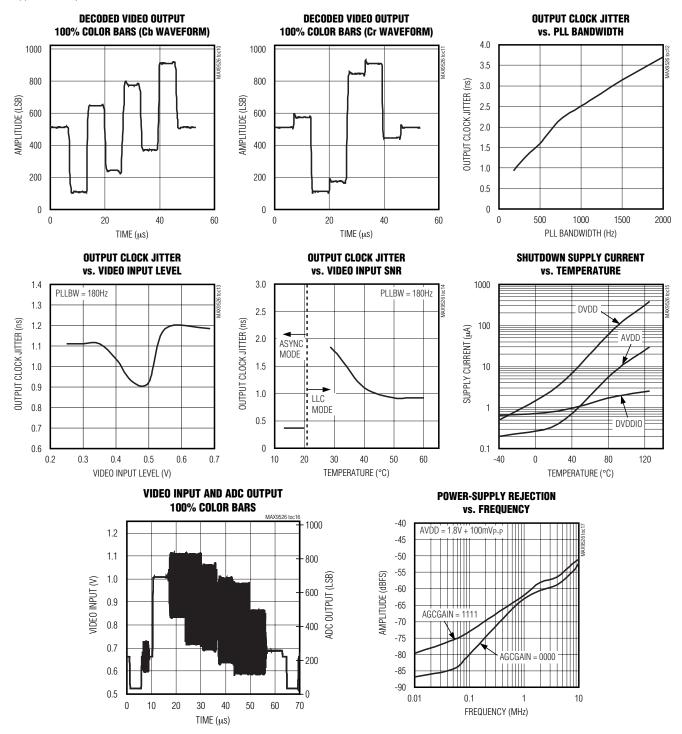

| Line-Locked Clock Frequency                         | fLLC            | Varies with input line rate                                                                           | 27      |     | MHz    |

| Minimum Peak Signal to RMS Noise                    |                 | Proper composite decoder operation                                                                    | 23      |     | dB     |

| PLL                                                 |                 |                                                                                                       |         |     |        |

| Async Mode Jitter                                   |                 | Ideal input clock                                                                                     | 20      |     | psrms  |

|                                                     |                 | 000                                                                                                   | 180     |     |        |

|                                                     |                 | 001                                                                                                   | 250     |     |        |

|                                                     |                 | 010                                                                                                   | 375     |     |        |

| Line-Locked PLL Loop Bandwidth                      |                 | 011 (default)                                                                                         | 500     |     | 1.1-   |

| Set by Register 0x0E[2:0]                           |                 | 100                                                                                                   | 750     |     | Hz     |

|                                                     |                 | 101                                                                                                   | 1000    |     |        |

|                                                     |                 | 110                                                                                                   | 1500    |     |        |

|                                                     |                 | 111                                                                                                   | 2000    |     |        |

\_\_\_\_\_\_NIXIN

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = V_{DVDD} = +1.8V, V_{DVDDIO} = +3.3V, AGND = DGND = 0, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                                       | SYMBOL                                    | CONDITIONS                                               | MIN                        | TYP    | MAX                        | UNITS |

|-------------------------------------------------|-------------------------------------------|----------------------------------------------------------|----------------------------|--------|----------------------------|-------|

| CRYSTAL OSCILLATOR                              | •                                         |                                                          |                            |        |                            | -     |

| Frequency                                       |                                           | Fundamental mode only                                    |                            | 27.000 |                            | MHz   |

| XTAL/OSC, XTAL2 Input<br>Capacitance            | C <sub>XTAL</sub> ,<br>C <sub>XTAL2</sub> |                                                          |                            | 4      |                            | рF    |

| Maximum Load Capacitor                          | C <sub>L1</sub> , C <sub>L2</sub>         |                                                          |                            | 45     |                            | рF    |

| Frequency Accuracy                              |                                           |                                                          |                            | ±50    |                            | ppm   |

| XTAL/OSC Logic-Low Threshold                    | VIL                                       | XTAL oscillator disabled, clock input mode (XTALDIS = 1) |                            |        | 0.3 x<br>V <sub>DVDD</sub> | V     |

| XTAL/OSC Logic-High Threshold                   | VIH                                       | XTAL oscillator disabled, clock input mode (XTALDIS = 1) | 0.7 x<br>V <sub>DVDD</sub> |        |                            | V     |

| XTAL/OSC Input Leakage Current                  | lih, lil                                  | XTAL oscillator disabled, clock input mode (XTALDIS = 1) | -10                        | ±0.01  | +10                        | μΑ    |

| Maximum Input Clock Jitter                      |                                           |                                                          |                            | 500    |                            | psp-p |

| I <sup>2</sup> C SERIAL INTERFACE (Note 6)      |                                           |                                                          |                            |        |                            |       |

| Serial-Clock Frequency                          | fscl                                      |                                                          | 0                          |        | 400                        | kHz   |

| Bus Free Time Between STOP and START Conditions | tBUF                                      |                                                          | 1.3                        |        |                            | μs    |

| Hold Time (REPEATED) START Condition            | thd,sta                                   |                                                          | 0.6                        |        |                            | μs    |

| SCL Pulse-Width Low                             | t <sub>LOW</sub>                          |                                                          | 1.3                        |        |                            | μs    |

| SCL Pulse-Width High                            | thigh                                     |                                                          | 0.6                        |        |                            | μs    |

| Setup Time for a REPEATED START Condition       | tsu,sta                                   |                                                          | 0.6                        |        |                            | μs    |

| Data Hold Time                                  | thd,dat                                   |                                                          | 0                          |        | 900                        | ns    |

| Data Setup Time                                 | tsu,dat                                   |                                                          | 100                        |        |                            | ns    |

| SDA and SCL Receiving Rise<br>Time (Note 7)     | t <sub>R</sub>                            |                                                          | 20 +<br>0.1C <sub>B</sub>  |        | 300                        | ns    |

| SDA and SCL Receiving Fall<br>Time (Note 7)     | tF                                        |                                                          | 20 +<br>0.1C <sub>B</sub>  |        | 300                        | ns    |

| SDA Transmitting Fall Time (Note 7)             | tϝ                                        | V <sub>DVDDIO</sub> = 3.3V                               | 20 +<br>0.1C <sub>B</sub>  |        | 250                        | ns    |

| (Note 1)                                        |                                           | V <sub>DVDDIO</sub> = 1.8V                               |                            | 150    |                            |       |

| Setup Time for STOP Condition                   | tsu,sto                                   |                                                          | 0.6                        |        |                            | μs    |

| Bus Capacitance                                 | CB                                        |                                                          |                            |        | 400                        | рF    |

| Pulse Width of Suppressed Spike                 | tsp                                       |                                                          | 0                          |        | 50                         | ns    |

| HIGH-SPEED LOGIC OUTPUTS (                      | D9-D0, LLC)                               |                                                          | •                          |        |                            | Ī     |

| Output Low Voltage                              | V <sub>OL</sub>                           | I <sub>OL</sub> = 5mA, V <sub>DVDDIO</sub> = 3.3V        |                            |        | 0.4                        | V     |

| Calpat Low Voltago                              | \ \vec{v}CL                               | $I_{OL} = 2mA$ , $V_{DVDDIO} = 1.7V$                     |                            |        | 0.4                        | ٧     |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = V_{DVDD} = +1.8V, V_{DVDDIO} = +3.3V, AGND = DGND = 0, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}C.)$  (Note 1)

| PARAMETER                             | SYMBOL                           | CONDITIONS                                             | MIN                          | TYP   | MAX                           | UNITS |

|---------------------------------------|----------------------------------|--------------------------------------------------------|------------------------------|-------|-------------------------------|-------|

|                                       | Vou                              | I <sub>OH</sub> = 5mA, V <sub>DVDDIO</sub> = 3.3V      | V <sub>DVDDIO</sub><br>0.8V  | X     |                               | V     |

| Output High Voltage                   | Voн                              | I <sub>OH</sub> = 2mA, V <sub>DVDDIO</sub> = 1.7V      | V <sub>D</sub> VDDIO<br>0.4V | -     |                               | V     |

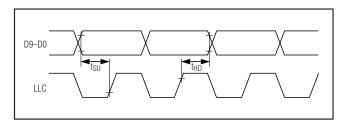

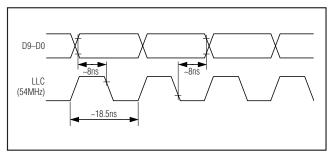

| Data to LLC Rising Edge Hold Time     | tHD                              |                                                        | 13.5                         | 18.5  | 23.5                          | ns    |

| Data to LLC Rising Edge Setup<br>Time | tsu                              |                                                        | 13.5                         | 18.5  | 23.5                          | ns    |

| Rise and Fall Time                    | to to                            | $C_L = 10pF, V_{DVDDIO} = 1.8V$                        |                              | 3     |                               | ns    |

| nise and rail fillie                  | t <sub>R</sub> , t <sub>F</sub>  | $C_L = 25pF, V_{DVDDIO} = 3.3V$ 3                      |                              |       |                               | 115   |

| Output Leakage                        | IOH, IOL                         | Outputs in high-impedance mode                         | -10                          | ±0.01 | +10                           | μΑ    |

| OPEN-DRAIN OUTPUTS (SDA an            | ıd ÎRQ)                          |                                                        |                              |       |                               |       |

| Output Low Voltage                    | V <sub>OL</sub>                  | I <sub>OL</sub> = 3mA, 1.7V < V <sub>DVDDIO</sub> < 2V |                              |       | 0.2 x<br>V <sub>DVDDIO</sub>  | V     |

|                                       |                                  | I <sub>OL</sub> = 3mA, 2V < V <sub>DVDDIO</sub> < 3.3V |                              |       | 0.4                           |       |

| Output High Current                   | Іон                              | V <sub>OUT</sub> = 3.3V                                |                              | ±0.01 | 10                            | μΑ    |

| LOGIC INPUTS (SDA, SCL, DEVA          | ADR)                             |                                                        |                              |       |                               |       |

| Logic-Low Threshold                   | V <sub>IL</sub>                  |                                                        |                              |       | 0.3 x<br>V <sub>D</sub> VDDIO | V     |

| Logic-High Threshold                  | VIH                              |                                                        | 0.7 x<br>V <sub>DVDDIO</sub> |       |                               | V     |

| Input Leakage Current                 | I <sub>IH,</sub> I <sub>IL</sub> |                                                        | -10                          | ±0.01 | +10                           | μΑ    |

| SDA/SCL Off Leakage Current           | lін                              | AVDD = DVDD = DVDDIO = 0V                              | -10                          | ±0.01 | +10                           | μΑ    |

- Note 1: All devices are 100% production tested at T<sub>A</sub> = +25°C. Specifications over temperature limits are guaranteed by design.

- Note 2: NTSC 75% color bar signal applied to video input.  $C_L = 10pF$  on D9–D0 and LLC. External XTAL.

- **Note 3:** Internal test only. Digital core controls sync level adjustment current to adjust offset in analog signal path. Adjust level is based on value of sync level as converted by ADC. Digital core switches sourcing or sinking current into V<sub>IN1</sub> or V<sub>IN2</sub> nodes. Speed of correction (value of current) is controlled through I<sup>2</sup>C.

- Note 4: Filter and ADC performance measured using ADC outputs prior to composite digital demodulation (decoding).

- **Note 5:** Decoded luminance and chrominance specifications measured using entire signal path from video input to digital component outputs.

- Note 6:  $V_{DVDDIO} = 1.8V$  and 3.3V.

- Note 7: C<sub>B</sub> is in pF.

#### **Typical Operating Characteristics**

$(V_{AVDD} = V_{DVDD} = +1.8V, V_{DVDDIO} = 3.3V, V_{AGND} = V_{DGND} = 0V, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

#### Typical Operating Characteristics (continued)

$(V_{AVDD} = V_{DVDD} = +1.8V, V_{DVDDIO} = 3.3V, V_{AGND} = V_{DGND} = 0V, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25$ °C.)

### Pin Description

| PI           | N                                   |                  |                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------|-------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QSOP         | QSOP TQFN-EP NAME                   |                  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1            | 30                                  | V <sub>IN1</sub> | Single-Ended Composite Video Input 1. AC-couple the input video signal with a 0.1µF capacitor.                                                                                                                                                                                                                                                                                                            |

| 2            | 31                                  | V <sub>REF</sub> | Video Reference Bypass. Bypass $V_{\text{REF}}$ to AGND with a 0.1 $\mu\text{F}$ capacitor as close as possible to the device.                                                                                                                                                                                                                                                                            |

| 3            | 32                                  | V <sub>IN2</sub> | Single-Ended Composite Video Input 2. AC-couple the input video signal with a 0.1µF capacitor.                                                                                                                                                                                                                                                                                                            |

| 4            | 1                                   | AGND             | Analog Ground                                                                                                                                                                                                                                                                                                                                                                                             |

| 5            | 2                                   | AVDD             | Analog Power-Supply Input. Connect to a +1.8V supply. Bypass AVDD to AGND with a 0.1µF capacitor.                                                                                                                                                                                                                                                                                                         |

| 6            | 3                                   | XTAL2            | External Crystal. Connect XTAL2 to one terminal of the crystal oscillator. Ground XTAL2 when applying an external clock to XTAL/OSC.                                                                                                                                                                                                                                                                      |

| 7            | 4                                   | XTAL/OSC         | External Crystal/Oscillator. Connect XTAL/OSC to one terminal of a crystal or an external clock source. Connect XTAL2 to the other terminal of the crystal oscillator.                                                                                                                                                                                                                                    |

| 8            | 5                                   | I.C.             | Internal connection. Connect to DGND.                                                                                                                                                                                                                                                                                                                                                                     |

| 9            | 6                                   | DEVADR           | I2C Device Address Select Input. Connect to DVDD, DGND, or SDA to select 1 of 3 available I2C slave addresses (see Table 5).                                                                                                                                                                                                                                                                              |

| 10, 22       | 7, 21                               | DVDD             | Digital Power-Supply Input. Connect to a +1.8V supply. Bypass DVDD to DGND with a 0.1µF capacitor in parallel with a 10µF capacitor.                                                                                                                                                                                                                                                                      |

| 11, 23       | 8, 22                               | DGND             | Digital Ground. Connect both DGND terminals together.                                                                                                                                                                                                                                                                                                                                                     |

| 12           | 10                                  | SDA              | I2C-Compatible Serial-Data Input/Output. Connect a 10k $\Omega$ pullup resistor from SDA to DVDDIO for full output swing.                                                                                                                                                                                                                                                                                 |

| 13           | 11                                  | SCL              | $\mbox{l}^2\mbox{C-Compatible Serial-Clock Input. Connect a 10k}\Omega$ pullup resistor from SCL to DVDDIO for full output swing.                                                                                                                                                                                                                                                                         |

| 14           | 12                                  | ĪRQ              | Hardware Interrupt Open-Drain Output. If not masked, $\overline{\text{IRQ}}$ is pulled low when the bits in the status register change state. Repeated faults have no effect on $\overline{\text{IRQ}}$ until $\overline{\text{IRQ}}$ is cleared by reading the corresponding status register. Connect a $10\text{k}\Omega$ pullup resistor from $\overline{\text{IRQ}}$ to DVDDIO for full output swing. |

| 15–20, 25–28 | 13–16, 18,<br>19, 24, 26,<br>27, 28 | D0-D9            | Digital Video Outputs Bit 0-Bit 9, 10-Bit Component Digital Video Outputs. The output format is 10-bit ITU-R BT.656, 4:2:2 with embedded sync. D1 and D0 can be configured as horizontal and vertical sync outputs using the Clock and Output register 0x0D. D0 is LSB.                                                                                                                                   |

| 21           | 20                                  | LLC              | Line-Locked 27MHz Clock Output. With line-locked mode, the LLC clock varies in response to horizontal line rate of the incoming video. In async mode, the LLC clock is synchronous to the crystal (see Table 1).                                                                                                                                                                                          |

| 24           | 23                                  | DVDDIO           | Digital I/O Power-Supply Input. Accepts a +1.7V to +3.45V voltage input. Bypass to DGND with a 0.1µF capacitor.                                                                                                                                                                                                                                                                                           |

| _            | 9, 17, 25, 29                       | N.C.             | No Connection. Not internally connected.                                                                                                                                                                                                                                                                                                                                                                  |

| _            | _                                   | EP               | Exposed Pad. EP is internally connected to GND. Connect EP to GND.                                                                                                                                                                                                                                                                                                                                        |

#### **Detailed Description**

The MAX9526 is a simple, low-power video decoder that converts all modes of NTSC and PAL composite video signals to 10-bit YCbCr component video compatible with the ITU-R BT.656 standard. The device powers up in fully operational mode and automatically configures itself to standard NTSC or standard PAL.

An internal 10-bit, 54MHz ADC samples at four times the sampling rate specified in ITU-R BT.601. The analog front-end of the MAX9526 features a DC restoration circuit, automatic gain control, and automatic offset correction. These blocks are controlled with digital processing to accurately optimize the full-scale range of the ADC. An integrated analog anti-aliasing filter eliminates the need for off-chip filtering. The device includes a 2:1 input multiplexer that can be configured to automatically select the input based on activity.

The system clock is generated with an external 27MHz crystal and an internal oscillator. Optionally, a 27MHz or 54MHz external clock can be connected to the XTAL/OSC input. An internal line-locked digital PLL is used to generate the 54MHz ADC sample clock that is synchronous to the incoming video signal with up to  $\pm 5\%$  variation in horizontal line length. The digital output data and LLC clock are line locked to the video input and provide a standard ITU output. The PLL can also be configured to asynchronously sample the input using the crystal oscillator or external clock.

The MAX9526 provides a 5-line adaptive comb filter to separate the luminance (Y) and chrominance (C) video components and reduce cross-chrominance and cross-luminance artifacts. The MAX9526 operates with any type of standard composite video signal source including DVD players, video cameras, navigation systems, and VCRs.

The device powers up in fully operational video decoder mode. An I<sup>2</sup>C register interface monitors status and enables programming of many decoder functions including brightness, contrast, saturation, and hue. The 10-bit output can be reconfigured to provide 8-bit data with separate horizontal and vertical syncs.

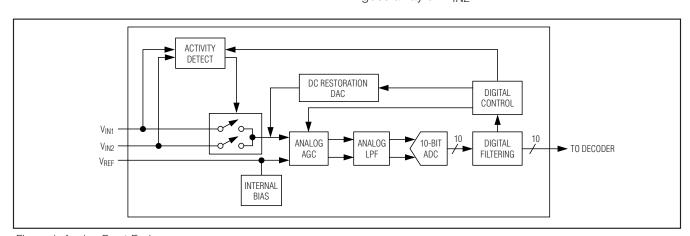

#### **Analog Front-End (AFE)**

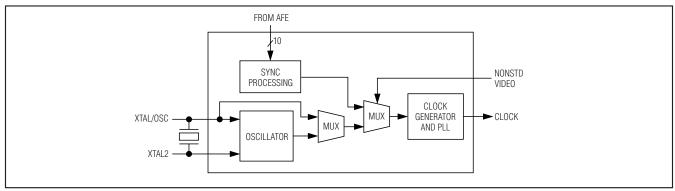

The MAX9526 AFE implements DC restoration, automatic gain control (AGC), analog anti-aliasing filter (LPF), activity detection, channel selection, and analog-to-digital conversion. A block diagram of the AFE is shown in Figure 1.

#### Activity Detect and Automatic Channel Selection

The MAX9526 continuously monitors activity at both video inputs,  $V_{IN1}$  and  $V_{IN2}$ . Activity on the selected channel is detected using the ADC output. On the unselected channel an analog sync-tip clamp and sync slicer are used to detect sync amplitudes greater than 50mV. In sleep mode, the analog sync-tip clamps and sync slicers are used to detect activity on both inputs, while the rest of the AFE is in a shutdown state.

The output of the activity detect circuit is reported through the Status register 0x00. The user must manually select which video input to process by setting INSEL in register 0x09 appropriately.

The MAX9526 can optionally be configured to automatically select the video input that indicates the presence of activity by setting AUTOSEL = 1 in register 0x09. When activity is present on both  $V_{IN1}$  and  $V_{IN2}$  at power-up or when there is no activity on either input channel,  $V_{IN1}$  is selected. When there is activity on  $V_{IN2}$  and there is no activity on  $V_{IN1}$ , then  $V_{IN2}$  is selected. When  $V_{IN2}$  is automatically selected with the presence of activity, the input only switches to  $V_{IN1}$  when activity goes away on  $V_{IN2}$ .

Figure 1. Analog Front-End

MIXIM

Figure 2. Sync Processing, Clock Generation, and PLL

#### **VREF Generation**

A differential signal path is used to process the analog video signal to minimize the effect of noise coupling. A DC reference (VREF) of 850mV is internally generated and decoupled externally with a  $0.1\mu F$  capacitor. Identical signal paths and video buffers are used for both the selected video input and the video reference voltage. The signals are converted to a fully differential signal by the analog AGC circuit.

#### DC Restoration DAC

The video inputs,  $V_{IN1}$  and  $V_{IN2}$ , are AC-coupled to the MAX9526 with 0.1µF capacitors. The DC restoration circuit sets the sync level at the output of the ADC by sinking or sourcing current at the selected video input. A digital control at the ADC output is used to monitor the average sync level. An error signal is generated in the digital control block that is used by a current DAC to source or sink current to the AC-coupled input to restore the DC level. The DC restoration circuit also corrects the offset in the analog signal chain and sets the sync level at the ADC output to code 32 (decimal).

#### Analog Automatic Gain Control (Analog AGC)

The MAX9526 includes an analog variable-gain amplifier with a digitally controlled gain for automatic gain control (AGC). The AGC uses the sync amplitude at the output of the ADC to control the gain. For signals without copy protection, the AGC adjusts the gain until the sync amplitude is 208 (decimal) codes at the ADC output. For inputs with copy protection, the AGC automatically compensates for the reduced sync amplitude on active lines.

The analog AGC loop can be disabled and the gain is set manually to 1 of 16 values using the Gain Control register 0x0A. The range of analog gain is 3.5dB to 12dB.

#### Analog Lowpass Filter (LPF)

The MAX9526 includes a high-performance anti-aliasing analog lowpass filter with a 3dB bandwidth of 13MHz (typ) and better than 0.25dB (typ) passband flatness to 5MHz. This eliminates the need for external filtering on the video inputs. The filter typically provides 36dB attenuation at 53MHz (1MHz below ADC sample rate).

#### 54Msps Video ADC

A 10-bit, 54Msps ADC converts the filtered analog composite video signal for digital signal processing (composite video demodulation).

#### Digital Filtering

Digital filtering at the ADC output removes any out-of-band interference and improves the signal-to-noise ratio before decoding. The signal path includes a digital anti-aliasing lowpass filter that has 1dB of passband flatness to 5.5MHz and a minimum of 45dB of stopband attenuation for frequencies greater than 9MHz.

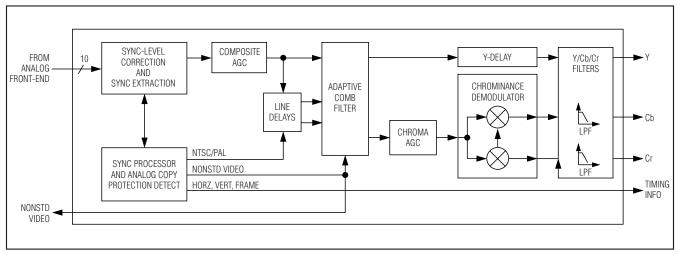

### Sync Processing, Clock Generation, and PLL

The sync processing, clock generation, and PLL extract the timing information from incoming video and generate the clock for the rest of the chip. Figure 2 shows the block diagram for this block.

#### Crystal Oscillator/Clock Input

The MAX9526 includes a low-jitter crystal oscillator circuit optimized for use with an external 27MHz crystal. The device also accepts an external CMOS logic-level clock at either 27MHz or 54MHz. To use an external clock (27MHz or 54MHz) instead of a crystal, set XTAL\_DIS = 1 in register 0x0D. To use a 54MHz external clock instead of a 27MHz clock, SEL\_54MHz must also be set to 1 in register 0x0D.

#### Sync Processing

The sync processing block extracts the sync information and automatically detects 525 line or 625 line inputs.

#### Clock Generator and PLL

The PLL operates in either line-locked clock (LLC) mode or async mode. Selection of the mode is controlled automatically by the MAX9526 or can optionally be overwritten with the LLC\_MODE bits in PLL Control register 0x0E.

In LLC mode, a hybrid analog/digital PLL generates a low-jitter line-locked clock. The 54MHz sample clock is synchronous to the input video. The LLC clock output is also synchronous to the input video. The ITU output has the correct number of samples per line and lines per field. The PLL is designed to lock to signals with up to 160ns peak jitter. When the jitter exceeds the 160ns peak, the PLL coasts until the jitter improves. If the jitter continuously exceeds the 160ns peak, the PLL relocks and the HLOCK status bit in register 0x00 is set to 0.

In LLC mode, the bandwidth of the PLL can be optionally programmed to one of eight values between 180Hz and 2000Hz using the PLLBW bits in PLL Control register 0x0E. The default value for the PLL bandwidth is 500Hz.

In async mode, the sample clock frequency is generated by multiplying the crystal frequency by a factor of two and the video signal is sampled asynchronously with the 2x crystal clock. To eliminate artifacts, the MAX9526 uses an adaptive poly-phase filter to correct timing and phase errors introduced by the asynchronous sampling. The LLC output is generated by dividing the 54MHz sampling clock by two.

The ITU output in async mode has the correct number of lines per frame and the correct number of pixels per line except on the first line of each field. The timing correction block uses this line to compensate for timing errors between the incoming video signal and the crystal. As a result, the first line of each field is longer or shorter for several pixels depending on the magnitude of the frequency difference between the incoming video signal and the local crystal. For example, a 100ppm frequency difference between the incoming video signal and the crystal results in approximately 23 extra or fewer pixels on the first line of each field. Line length errors on line one are of no consequence for most applications since it is in the vertical blanking interval and does not contain active video or any other type of data.

The types of inputs that cause the PLL to automatically switch to async mode are video inputs with a nonstandard carrier frequency. For standard video, the carrier frequency is always a precise multiple of the horizontal frequency. A typical nonstandard input is video cassette recorders in which the carrier is not a precise multiple of the horizontal frequency. The nonstandard detect (NONSTD) status from the decoder is used to automatically switch the PLL to async mode when nonstandard carrier frequencies are detected. The NONSTD status is monitored in the Status register 0x00.

#### Clocking Modes

In addition to automatic configuration, the MAX9526 can also be manually configured to provide maximum flexibility in setting the clock inputs and outputs of the chip. Table 1 summarizes the clocking modes that are supported.

#### **Digital Composite Decoding**

Figure 3 shows a block diagram of the digital composite decoder. This block converts the digitized composite video signal to digital component video.

#### Sync Level Correction and Sync Extraction

The sync extraction function extracts the raw sync signals from the video and the extracted sync information is sent to the sync processor. The sync level from the AFE is code 32 (decimal) on a 10-bit scale and the blanking level is approximately 208 (decimal) codes above the sync level. The sync slicer default threshold is set to approximately the middle of the sync pulse at decimal code 128. The sync slice level can optionally be manually adjusted using the slice bits in register 0x0F.

The sync level correction block features an optional digital clamp that can be enabled in register 0x09. Enabling the digital clamp sets the sync level to code 0 (decimal) and gives higher frequency tracking of the input signals. When the digital clamp is enabled, the sync slice level in register 0x0F should be adjusted accordingly to provide equivalent noise rejection.

#### Sync Processor and Analog Copy Protection Detection

The sync processor extracts the horizontal sync and vertical sync signals. Field pulses and burst gate pulses are generated based on VSYNC and HSYNC, respectively. The sync processing block provides sync timing to measure the sync level and amplitude for the black level control and composite AGC. The sync processor also detects incoming video signal standards (525 line NTSC and 625 line PAL). Video standard information is available in Status register 0x01. The detected video standard is used to automatically configure the decoder. The MAX9526 detects NTSC-M (standard NTSC) and PAL B/G/H/I/D (standard PAL)

Figure 3. Digital Composite Decoding Functional Diagram

standards automatically. See the *Standard Select, Shutdown, and Control Register* section for manual programming.

The sync processor block also detects analog copy protection. Extracted copy protection information is available in Status register 0x01.

#### Composite Automatic Gain Control (AGC)

In addition to the analog AGC that optimizes the ADC full-scale range, a digital AGC is used to more accurately set the video amplitude. The Composite AGC uses the amplitude of the sync signal to set the gain.

#### Adaptive Comb Filter

The MAX9526 uses a 5-line adaptive comb filter to separate luminance and chrominance components from a single composite channel. The adaptation algorithm does not require configuration. The adaptive comb filter adjusts based on the relationship and content of video data between neighboring lines. The filter automatically adapts the comb filter structure between a 5-line filter and a notch filter.

#### Chrominance Signal Demodulator

After luminance (Y) and chrominance (C) components are separated, the Y component passes through a delay line to compensate for the C component delay through the demodulator. The chrominance signal path contains an AGC before the signal demodulator. The chrominance AGC uses the color burst amplitude to set the gain. The chrominance is demodulated using a subcarrier signal locked to the burst. The demodulated chrominance signals, Cb and Cr, are lowpass filtered to eliminate unwanted products of demodulation.

#### **Output Formatting**

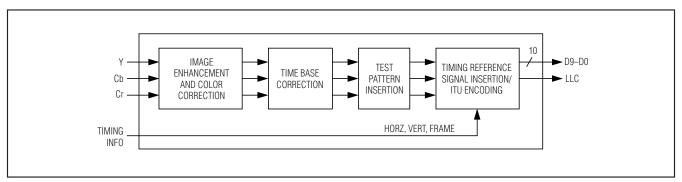

Figure 4 shows the output formatting section of the MAX9526.

#### Image Enhancement and Color Correction

The MAX9526 provides contrast, brightness, hue, and saturation manual control in registers 0x05 to 0x08.

#### Time Base Correction

The MAX9526 provides time base correction (TBC) to allow the decoder to properly process unstable and nonstandard video from sources such as a VCR. The time base correction minimizes the effect of sampling jitter to ensure that there are a correct number of pixels per active line.

#### Test Pattern Insertion

The MAX9526 automatically outputs a black screen when there is no video at the inputs. The test pattern can also be configured to provide a blue screen, 75% color bars, or 100% color bars through register 0x0C.

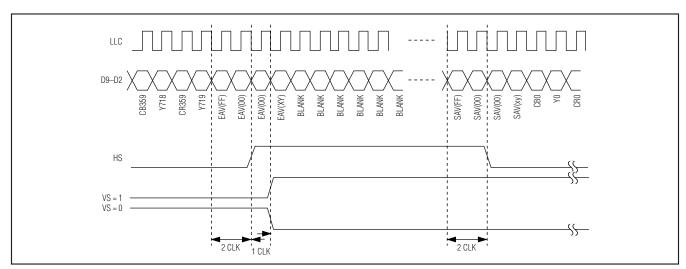

### Timing Reference Signal Insertion and ITU-R BT.656 Encoding

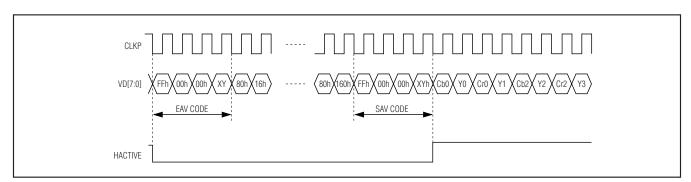

The MAX9526 multiplexes the Y, Cr, and Cb signals with an embedded timing reference signal conforming to the ITU-R BT.656 standard.

SAV and EAV sequences are inserted into the data stream to indicate the active video time in ITU-R BT.656 format. The output timing insertion is illustrated in Figure 5. The SAV and EAV sequences are shown in Table 2.

#### **Output Timing**

The output setup and hold diagram is shown in Figure 6.

Table 1. MAX9526 Clock Mode Summary

| SEL<br>_54MHz<br>REGISTER 0x0D<br>B4 | XTAL_DIS<br>REGISTER 0x0D<br>B3 | PLLBYP<br>REGISTER 0x0E<br>B3 | LLC_MODE<br>REGISTER 0x0E<br>B5-4 | CLOCK MODE DESCRIPTION                                                                                                                                                                           |

|--------------------------------------|---------------------------------|-------------------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                                    | 0                               | 0                             | 00                                | Input clock = 27MHz crystal.  Sample clock = line locked or async (autodetected).  This is the default power-up mode for the MAX9526.                                                            |

| 0                                    | 0                               | 0                             | 10                                | Input clock = 27MHz crystal. Sample clock = line locked (forced on).                                                                                                                             |

| 0                                    | 0                               | 0                             | 11                                | Input clock = 27MHz crystal. Sample clock = 2x input clock.                                                                                                                                      |

| 0                                    | Х                               | 1                             | XX                                | Invalid modes. The PLL can only be bypassed if the input clock is 54MHz.                                                                                                                         |

| 0                                    | 1                               | 0                             | 00                                | Input clock = 27MHz external clock. Sample clock = line locked or async (autodetected).                                                                                                          |

| 0                                    | 1                               | 0                             | 10                                | Input clock = 27MHz external clock. Sample clock = line locked (forced on).                                                                                                                      |

| 0                                    | 1                               | 0                             | 11                                | Input clock = 27MHz external clock. Sample clock = 2x input clock.                                                                                                                               |

| 1                                    | 0                               | Х                             | XX                                | Invalid mode. 54MHz crystal not supported.                                                                                                                                                       |

| 1                                    | 1                               | 0                             | 00                                | Input clock = 54MHz external clock. Sample clock = line locked or async (autodetected).                                                                                                          |

| 1                                    | 1                               | 0                             | 10                                | Input clock = 54MHz external clock. Sample clock = line locked (forced on).                                                                                                                      |

| 1                                    | 1                               | 0                             | 11                                | Input clock = 54MHz external clock.  Sample clock = input clock divided by 2, then multiplied by 2x through the PLL. This mode uses the PLL to filter high-frequency jitter on the input source. |

| 1                                    | 1                               | 1                             | X0                                | Invalid mode. The PLL can only be bypassed when the output is not a line-locked clock.                                                                                                           |

| 1                                    | 1                               | 1                             | 11                                | Input clock = 54MHz external clock.  Sample clock = input clock. Use this mode when a low-jitter, 54MHz input clock is used.                                                                     |

Figure 4. Digital Output Processing

#### Table 2. ITU-R BT.656 SAV and EAV Code Sequence

|       | CONDITION |        |   | FVH |   |       | VALUE SAV/EAV CODE SEQUENCE |       |      |

|-------|-----------|--------|---|-----|---|-------|-----------------------------|-------|------|

| FIELD | V TIME    | H TIME | F | ٧   | Н | FIRST | SECOND                      | THIRD | TRS  |

| Even  | Blank     | EAV    | 1 | 1   | 1 | 0xFF  | 0x00                        | 0x00  | 0xF1 |

| Even  | Blank     | SAV    | 1 | 1   | 0 | 0xFF  | 0x00                        | 0x00  | 0xEC |

| Even  | Active    | EAV    | 1 | 0   | 1 | 0xFF  | 0x00                        | 0x00  | 0xDA |

| Even  | Active    | SAV    | 1 | 0   | 0 | 0xFF  | 0x00                        | 0x00  | 0xC7 |

| Odd   | Blank     | EAV    | 0 | 1   | 1 | 0xFF  | 0x00                        | 0x00  | 0xB6 |

| Odd   | Blank     | SAV    | 0 | 1   | 0 | 0xFF  | 0x00                        | 0x00  | 0xAB |

| Odd   | Active    | EAV    | 0 | 0   | 1 | 0xFF  | 0x00                        | 0x00  | 0x9D |

| Odd   | Active    | SAV    | 0 | 0   | 0 | 0xFF  | 0x00                        | 0x00  | 0x80 |

Figure 5. Timing Diagram of ITU-R BT.656 Format

Figure 6. Output Setup and Hold

Figure 7. Multiple Video Input Processing

Figure 8. MAX9526 Typical Application Circuit with Additional Supply Isolation

**Table 3. Recommended Crystal Parameters**

| PARAMETER           | CONDITIONS                        | MIN        | TYP    | MAX | UNITS |

|---------------------|-----------------------------------|------------|--------|-----|-------|

| Frequency           | Fundamental mode only             |            | 27.000 |     | MHz   |

| Maximum Crystal ESR | Room temperature                  |            | 30     |     | Ω     |

| Accuracy            | Line-locked mode                  | ±50<br>±50 |        |     | nnm   |

|                     | Async mode with multiple decoders |            |        |     | ppm   |

### Applications Information

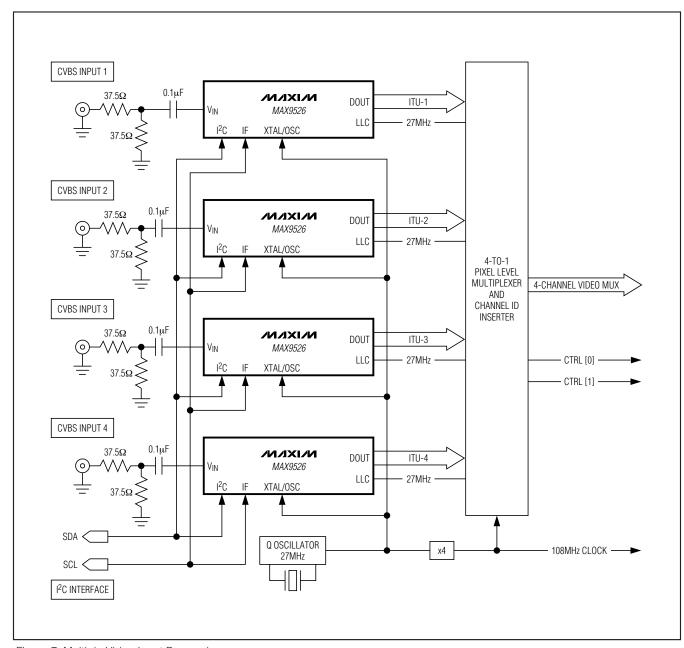

#### **Multiple Decoder Operation**

Multiple asynchronous video input signals can be decoded synchronously using multiple MAX9526s in asynchronous (async) sampling mode. Figure 7 shows an example of decoding four video input signals.

The MAX9526 is configured for async sampling mode by writing the following registers:

Register 0x0D, B3 (XTAL\_DIS) = 1 (disables the crystal oscillator)

Register 0x0E, B5-4 (LLC\_MODE) = 11 (forces sampling to async mode)

When the MAX9526 is in async sampling mode, the data outputs, D9–D0, of all decoders are synchronous with the input clock (XTAL/OSC). The video content in the data outputs is not frame aligned because the video sources into each MAX9526 is asynchronous. A small FPGA can be implemented to multiplex all four channels into a single 8- or 10-bit bus. This FPGA can also format the outputs to be compatible for input into a compression processor, which is commonly used in digital video recorders (DVRs).

The crystal oscillator (external or internal) must have better than ±50ppm accuracy for acceptable decoding in this mode. An accuracy of ±10ppm is recommended for optimal performance.

#### **Recommended Crystal Parameters**

Recommended crystal parameters are shown in Table 3.

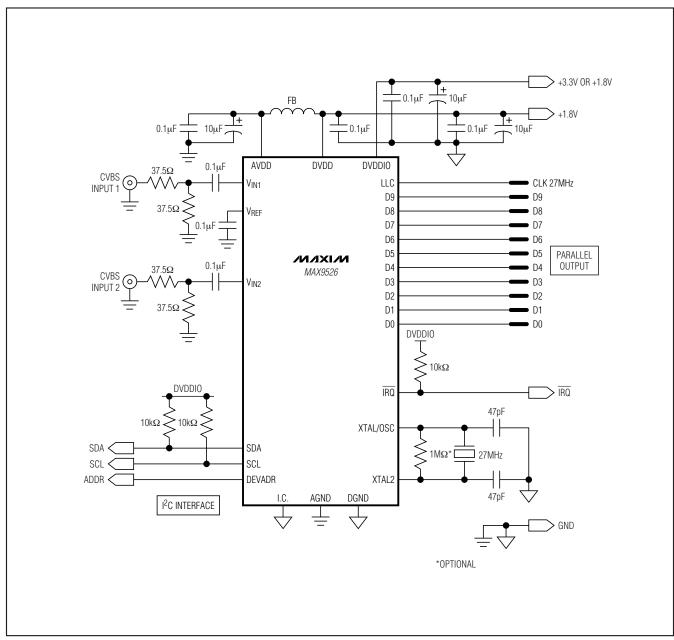

#### **Power-Supply Decoupling**

For systems where additional power-supply isolation is required, the circuit shown in Figure 8 can be used. Additional supply decoupling is added and analog power (AVDD) isolation is increased with the use of a ferrite bead (FB). The analog ground connection (AGND) should be connected to a separate ground plane that has a small bridge to the main ground plane of the system. The video input termination (V<sub>IN1</sub>/V<sub>IN2</sub>), video reference (V<sub>REF</sub>) decoupling, and AVDD supply decoupling should also be connected to the AGND ground plane.

SMBus is a trademark of Intel Corp.

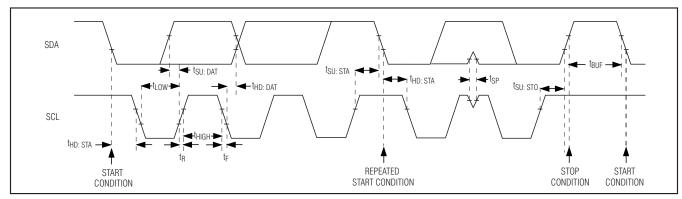

#### I<sup>2</sup>C Serial Interface

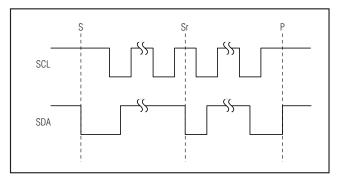

The MAX9526 features an I<sup>2</sup>C/SMBus<sup>™</sup>-compatible, 2-wire serial interface consisting of a serial-data line (SDA) and a serial-clock line (SCL). SDA and SCL facilitate communication between the MAX9526 and the master at clock rates up to 400kHz. Figure 9 shows the 2-wire interface timing diagram. The master generates SCL and initiates data transfer on the bus. The master device writes data to the MAX9526 by transmitting the proper slave address followed by the register address and then the data word. Each transmit sequence is framed by a START (S) or REPEATED START (Sr) condition and a STOP (P) condition. Each word transmitted to the MAX9526 is 8 bits long and is followed by an acknowledge clock pulse. A master reading data from the MAX9526 transmits the proper slave address followed by a series of nine SCL pulses. The MAX9526 transmits data on SDA in sync with the master-generated SCL pulses. The master acknowledges receipt of each byte of data. Each read sequence is framed by a START or REPEATED START condition, a not acknowledge, and a STOP condition. SDA operates as both an input and an open-drain output. A pullup resistor, typically greater than  $500\Omega$ , is required on SDA. SCL operates only as an input. A pullup resistor, typically greater than  $500\Omega$ , is required on SCL if there are multiple masters on the bus, or if the single master has an opendrain SCL output. Series resistors in line with SDA and SCL are optional. Series resistors protect the digital inputs of the MAX9526 from high-voltage spikes on the bus lines, as well as minimize crosstalk and undershoot of the bus signals.

#### Bit Transfer

One data bit is transferred during each SCL cycle. The data on SDA must remain stable during the high period of the SCL pulse. Changes in SDA while SCL is high are control signals (see the *START and STOP Conditions* section).

#### START and STOP Conditions

SDA and SCL idle high when the bus is not in use. A master initiates communication by issuing a START condition. A START condition is a high-to-low transition on SDA with SCL high. A STOP condition is a low-to-high

18 \_\_\_\_\_\_ /VI/IXI/VI

transition on SDA while SCL is high (Figure 10). A START condition from the master signals the beginning of a transmission to the MAX9526. The master terminates transmission, and frees the bus, by issuing a STOP condition. The bus remains active if a REPEATED START condition is generated instead of a STOP condition.

#### Early STOP Conditions

The MAX9526 recognizes a STOP (P) condition at any point during data transmission except if the STOP condition occurs in the same high pulse as a START (S) condition. For proper operation, do not send a STOP condition during the same SCL high pulse as the START condition.

#### Slave Address

The slave address is defined as the seven most significant bits (MSBs) followed by the read/write bit. For DEV\_ADDR connected to DGND, setting the read/write bit to 1 (slave address = 0x43) configures the MAX9526 for read mode. Setting the read/write bit to 0 (slave address = 0x42) configures the MAX9526 for write mode. The address is the first byte of information sent to the MAX9526 after the START condition. The MAX9526 slave address is configurable with DEV\_ADDR. Table 5 shows the addresses of the MAX9526.

#### Acknowledge

The acknowledge bit (ACK) is a clocked 9th bit that the MAX9526 uses to handshake receipt each byte of data when in write mode (see Figure 11). The MAX9526 pulls down SDA during the entire master-generated 9th clock pulse if the previous byte is successfully received. Monitoring ACK allows for detection of unsuccessful data transfers. An unsuccessful data transfer occurs if a receiving device is busy or if a system fault has occurred. In the event of an unsuccessful data transfer, the bus master retries communication. The master pulls

down SDA during the 9th clock cycle to acknowledge receipt of data when the MAX9526 is in read mode. An acknowledge is sent by the master after each read byte to allow data transfer to continue. A not acknowledge is sent when the master reads the final byte of data from the MAX9526, followed by a STOP condition.

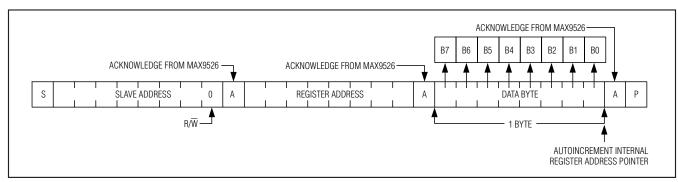

#### Write Data Format

A write to the MAX9526 includes transmission of a START condition, the slave address with the R/W bit set to 0, one byte of data to configure the internal register address pointer, one or more bytes of data, and a STOP condition. Figure 12 illustrates the proper frame format for writing one byte of data to the MAX9526. Figure 13 illustrates the frame format for writing n bytes of data to the MAX9526.

The slave address with the  $R/\overline{W}$  bit set to 0 indicates that the master intends to write data to the MAX9526. The MAX9526 acknowledges receipt of the address byte during the master-generated 9th SCL pulse.

The second byte transmitted from the master configures the MAX9526's internal register address pointer. The pointer tells the MAX9526 where to write the next byte of data. An acknowledge pulse is sent by the MAX9526 upon receipt of the address pointer data.

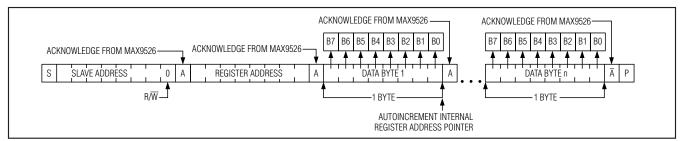

The third byte sent to the MAX9526 contains the data that is written to the chosen register. An acknowledge pulse from the MAX9526 signals receipt of the data byte. The address pointer autoincrements to the next register address after each received data byte. This autoincrement feature allows a master to write to sequential registers within one continuous frame. Figure 13 illustrates how to write to multiple registers with one frame. The master signals the end of transmission by issuing a STOP (P) condition.

Figure 9. I<sup>2</sup>C Serial Interface Timing Diagram

Figure 10. START, STOP, and REPEATED START Conditions

# START CONDITION SCL 1 2 8 9 NOT ACKNOWLEDGE SDA ACKNOWLEDGE

Figure 11. Acknowledge

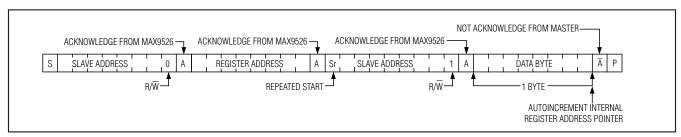

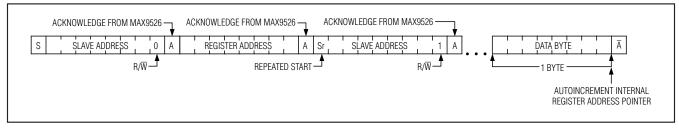

#### Read Data Format

Send the slave address with the R/W bit set to 1 to initiate a read operation. The MAX9526 acknowledges receipt of its slave address by pulling SDA low during the 9th SCL clock pulse. A START (S) command followed by a read command resets the address pointer to register 0x00.

The first byte transmitted from the MAX9526 is the contents of register 0x00. Transmitted data is valid on the rising edge of SCL. The address pointer autoincrements after each read data byte. This autoincrement feature allows all registers to be read sequentially within one continuous frame. A STOP (P) condition can be issued after any number of read data bytes. If a STOP condition is issued followed by another read operation, the first data byte to be read is from register 0x00.

The address pointer can be preset to a specific register before a read command is issued. The master presets the address pointer by first sending the MAX9526's slave address with the R/W bit set to 0 followed by the register address. A REPEATED START (Sr) condition is then sent followed by the slave address with the R/W bit set to 1. The MAX9526 then transmits the contents of the specified register. The address pointer autoincrements after transmitting the first byte.

The master acknowledges receipt of each read byte during the acknowledge clock pulse. The master must acknowledge all correctly received bytes except the last byte. The final byte must be followed by a not acknowledge from the master and then a STOP condition. Figure 14 illustrates the frame format for reading one byte from the MAX9526. Figure 15 illustrates the frame format for reading multiple bytes from the MAX9526.

Figure 12. Writing a Byte of Data to the MAX9526

Figure 13. Writing n Bytes of Data to the MAX9526

Figure 14. Reading One Indexed Byte of Data from the MAX9526

Figure 15. Reading n Bytes of Indexed Data from the MAX9526

#### **Programming the MAX9526**

I<sup>2</sup>C Register Map

Table 4 shows an I<sup>2</sup>C register map. All static bits should not be programmed to any values other than the default value listed in Table 4.

#### **Table 4. Register Map Overview**

| REGISTER                                     | В7      | В6                                      | B5      | В4            | В3      | B2     | B1             | В0      | REG<br>ADDR | POWER-<br>ON<br>STATE |