### **General Description**

The MAX16821A/MAX16821B/MAX16821C pulsewidth-modulation (PWM) LED driver controllers provide high output-current capability in a compact package with a minimum number of external components. The MAX16821A/MAX16821B/MAX16821C are suitable for use in synchronous and nonsynchronous step-down (buck), boost, buck-boost, SEPIC, and Cuk LED drivers. A logic input (MODE) allows the devices to switch between synchronous buck and boost modes of operation. These devices are the first high-power drivers designed specifically to accommodate common-anode HBLEDs.

The ICs offer average current-mode control that enable the use of MOSFETs with optimal charge and on-resistance figure of merit, thus minimizing the need for external heatsinking even when delivering up to 30A of LED current.

The differential sensing scheme provides accurate control of the LED current. The ICs operate from a 4.75V to 5.5V supply range with the internal regulator disabled (VCC connected to IN). These devices operate from a 7V to 28V input supply voltage with the internal regulator enabled.

The MAX16821A/MAX16821B/MAX16821C feature a clock output with 180° phase delay to control a second out-of-phase LED driver to reduce input and output filter capacitor size and to minimize ripple currents. The wide switching frequency range (125kHz to 1.5MHz) allows the use of small inductors and capacitors.

Additional features include programmable overvoltage protection and an output enable function.

### **Applications**

Front Projectors/Rear Projection TVs Portable and Pocket Projectors Automotive Exterior Lighting LCD TVs and Display Backlight Automotive Emergency Lighting and Signage

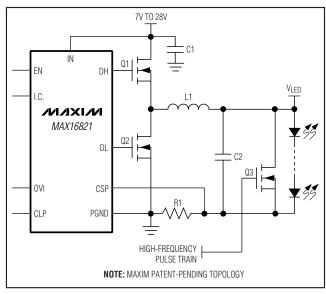

Typical Operating Circuit and Selector Guide appear at end of data sheet.

#### **Features** ♦ Up to 30A Output Current

- **♦ True-Differential Remote Output Sensing**

- **♦** Average Current-Mode Control

- ♦ 4.75V to 5.5V or 7V to 28V Input-Voltage Range

- ♦ 0.1V/0.03V LED Current-Sense Options Maximize Efficiency (MAX16821B/MAX16821C)

- ♦ Thermal Shutdown

- ♦ Nonlatching Output Overvoltage Protection

- **♦ Low-Side Buck Mode with or without** Synchronous Rectification

- ♦ High-Side Buck and Low-Side Boost Mode with or without Synchronous Rectification

- 125kHz to 1.5MHz Programmable/Synchronizable **Switching Frequency**

- ♦ Integrated 4A Gate Drivers

- ♦ Clock Output for 180° Out-of-Phase Operation for Second Driver

- ◆ -40°C to +125°C Operating Temperature Range

### **Ordering Information**

| PART          | TEMP RANGE      | PIN-<br>PACKAGE |

|---------------|-----------------|-----------------|

| MAX16821AATI+ | -40°C to +125°C | 28 TQFN-EP*     |

| MAX16821BATI+ | -40°C to +125°C | 28 TQFN-EP*     |

| MAX16821CATI+ | -40°C to +125°C | 28 TQFN-EP*     |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package. \*EP = Exposed pad.

### Simplified Diagram

MIXIM

Maxim Integrated Products 1

### **ABSOLUTE MAXIMUM RATINGS**

| IN to SGND              |                                                      | All Other Pins to SGNDContinuous Power Dissipation (TA = + |                |

|-------------------------|------------------------------------------------------|------------------------------------------------------------|----------------|

| BST to LX               |                                                      | 28-Pin TQFN 5mm x 5mm (derate 3                            |                |

| DH to LX                | 0.3V to (V <sub>BST</sub> - V <sub>LX</sub> ) + 0.3V | above +70°C)                                               | 2758mW         |

| DL to PGND              | 0.3V to (V <sub>DD</sub> + 0.3V)                     | Operating Temperature Range                                | 40°C to +125°C |

| V <sub>CC</sub> to SGND | 0.3V to +6V                                          | Junction Temperature                                       | +150°C         |

| VCC, VDD to PGND        | 0.3V to +6V                                          | Storage Temperature Range                                  |                |

| SGND to PGND            | 0.3V to +0.3V                                        | Lead Temperature (soldering, 10s)                          | +300°C         |

| V <sub>CC</sub> Current | 300mA                                                |                                                            |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = 5V, V_{DD} = V_{CC}, T_A = T_J = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                                   | SYMBOL                            | CONDITIONS                                                               | MIN   | TYP   | MAX   | UNITS           |

|---------------------------------------------|-----------------------------------|--------------------------------------------------------------------------|-------|-------|-------|-----------------|

| Innut Valtage Denge                         | V.                                | Internal LDO on                                                          | 7     |       | 28    | V               |

| Input-Voltage Range                         | VIN                               | Internal LDO off (V <sub>CC</sub> connected to V <sub>IN</sub> )         | 4.75  |       | 5.50  | V               |

| Quiescent Supply Current                    | ΙQ                                | V <sub>EN</sub> = V <sub>CC</sub> or SGND, no switching                  |       | 2.7   | 5.5   | mA              |

| LED CURRENT REGULATOR                       |                                   |                                                                          |       |       |       |                 |

|                                             |                                   | $V_{IN} = V_{CC} = 4.75V \text{ to } 5.5V, f_{SW} = 500kHz $ (MAX16821A) | 0.594 | 0.600 | 0.606 |                 |

|                                             |                                   | V <sub>IN</sub> = 7V to 28V, f <sub>SW</sub> = 500kHz<br>(MAX16821A)     | 0.594 | 0.600 | 0.606 |                 |

| Differential Set Value                      |                                   | $V_{IN} = V_{CC} = 4.75V$ to 5.5V, $f_{SW} = 500kHz$ (MAX16821B)         | 0.098 | 0.100 | 0.102 | .,              |

| (VSENSE+ to VSENSE-) (Note 2)               |                                   | V <sub>IN</sub> = 7V to 28V, f <sub>SW</sub> = 500kHz<br>(MAX16821B)     | 0.098 | 0.100 | 0.102 | V               |

|                                             |                                   | $V_{IN} = V_{CC} = 4.75V \text{ to } 5.5V, f_{SW} = 500kHz $ (MAX16821C) | 0.028 | 0.030 | 0.032 |                 |

|                                             |                                   | V <sub>IN</sub> = 7V to 28V, f <sub>SW</sub> = 500kHz<br>(MAX16821C)     | 0.028 | 0.030 | 0.032 |                 |

| Soft-Start Time                             | tss                               |                                                                          |       | 1024  |       | Clock<br>Cycles |

| STARTUP/INTERNAL REGULATO                   | R                                 | •                                                                        |       |       |       |                 |

| V <sub>CC</sub> Undervoltage Lockout (UVLO) | UVLO                              | V <sub>CC</sub> rising                                                   | 4.1   | 4.3   | 4.5   | V               |

| UVLO Hysteresis                             |                                   | V <sub>CC</sub> falling                                                  |       | 200   |       | mV              |

| V <sub>CC</sub> Output Voltage              |                                   | V <sub>IN</sub> = 7V to 28V, I <sub>SOURCE</sub> = 0 to 60mA             | 4.85  | 5.10  | 5.30  | V               |

| MOSFET DRIVER                               |                                   |                                                                          |       |       |       |                 |

| Output Driver Impedance                     |                                   | Low or high output, ISOURCE/SINK = 20mA                                  |       | 1.1   | 3     | Ω               |

| Output Driver Source/Sink Current           | I <sub>DH</sub> , I <sub>DL</sub> |                                                                          |       | 4     |       | А               |

| Nonoverlap Time                             | t <sub>NO</sub>                   | C <sub>DH/DL</sub> = 5nF                                                 |       | 35    |       | ns              |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = 5V, V_{DD} = V_{CC}, T_A = T_J = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                                               | SYMBOL                | CONDITIONS                                                  | MIN  | TYP  | MAX  | UNITS     |

|---------------------------------------------------------|-----------------------|-------------------------------------------------------------|------|------|------|-----------|

| OSCILLATOR                                              | •                     |                                                             |      |      |      |           |

| Switching Frequency Range                               |                       |                                                             | 125  |      | 1500 | kHz       |

|                                                         |                       | $R_T = 500k\Omega$                                          | 120  | 125  | 130  |           |

| Switching Frequency                                     | fsw                   | $R_T = 120k\Omega$                                          | 495  | 521  | 547  | kHz       |

|                                                         |                       | $R_T = 39.9k\Omega$                                         | 1515 | 1620 | 1725 |           |

| Switching Fraguency Accuracy                            |                       | $120$ k $\Omega$ < R <sub>T</sub> $\leq$ $500$ k $\Omega$   | -5   |      | +5   | %         |

| Switching Frequency Accuracy                            |                       | $40k\Omega \le R_T \le 120k\Omega$                          | -8   |      | +8   | 70        |

| CLKOUT Phase Shift with<br>Respect to DH (Rising Edges) |                       | f <sub>SW</sub> = 125kHz, MODE connected to SGND            |      | 180  |      | - Degrees |

| CLKOUT Phase Shift with<br>Respect to DL (Rising Edges) |                       | f <sub>SW</sub> = 125kHz, MODE connected to V <sub>CC</sub> |      | 180  |      | Degrees   |

| CLKOUT Output-Voltage Low                               | V <sub>OL</sub>       | I <sub>SINK</sub> = 2mA                                     |      |      | 0.4  | V         |

| CLKOUT Output-Voltage High                              | Voh                   | ISOURCE = 2mA                                               | 4.5  |      |      | V         |

| SYNC Input High Pulse Width                             | tsync                 |                                                             | 200  |      |      | ns        |

| SYNC Input Clock High Threshold                         | Vsynch                |                                                             | 2    |      |      | V         |

| SYNC Input Clock Low Threshold                          | VSYNCL                |                                                             |      |      | 0.4  | V         |

| SYNC Pullup Current                                     | ISYNC_OUT             | VRT/SYNC = 0V                                               |      | 250  | 500  | μΑ        |

| SYNC Power-Off Level                                    | V <sub>SYNC_OFF</sub> |                                                             |      |      | 0.4  | V         |

| INDUCTOR CURRENT LIMIT                                  |                       |                                                             |      |      |      |           |

| Average Current-Limit Threshold                         | $V_{CL}$              | CSP to CSN                                                  | 26.4 | 27.5 | 33.0 | mV        |

| Reverse Current-Limit Threshold                         | V <sub>CLR</sub>      | CSP to CSN                                                  |      | -2.0 |      | mV        |

| Cycle-by-Cycle Current Limit                            |                       | CSP to CSN                                                  |      | 60   |      | mV        |

| Cycle-by-Cycle Overload                                 |                       | V <sub>CSP</sub> to V <sub>CSN</sub> = 75mV                 |      | 260  |      | ns        |

| CURRENT-SENSE AMPLIFIER                                 |                       |                                                             |      |      |      |           |

| CSP to CSN Input Resistance                             | Rcs                   |                                                             |      | 4    |      | kΩ        |

| Common-Mode Range                                       | VCMR(CS)              | V <sub>IN</sub> = 7V to 28V                                 | 0    |      | 5.5  | V         |

| Input Offset Voltage                                    | Vos(cs)               |                                                             |      | 0.1  |      | mV        |

| Amplifier Voltage Gain                                  | Av(cs)                |                                                             |      | 34.5 |      | V/V       |

| 3dB Bandwidth                                           | f <sub>3dB</sub>      |                                                             |      | 4    |      | MHz       |

| CURRENT-ERROR AMPLIFIER (T                              | RANSCONDU             | CTANCE AMPLIFIER)                                           |      |      |      |           |

| Transconductance                                        | Яm                    |                                                             |      | 550  |      | μS        |

| Open-Loop Gain                                          | Avl(ce)               |                                                             |      | 50   |      | dB        |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = 5V, V_{DD} = V_{CC}, T_A = T_J = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                                  | SYMBOL             | CONDITIONS                          | MIN      | TYP   | MAX   | UNITS |

|--------------------------------------------|--------------------|-------------------------------------|----------|-------|-------|-------|

| LED CURRENT SIGNAL DIFFER                  | ENTIAL VOLTA       | AGE AMPLIFIER (DIFF)                | <u>.</u> |       |       | •     |

| Common-Mode Voltage Range                  | VCMR(DIFF)         |                                     | 0        |       | 1.0   | V     |

| DIFF Output Voltage                        | VCM                | VSENSE+ = VSENSE- = 0V              |          | 0.6   |       | V     |

| lanut Offeet Veltere                       | \/                 | MAX16821A                           | -3.7     |       | +3.7  | .,    |

| Input Offset Voltage                       | Vos(DIFF)          | MAX16821B/MAX16821C                 | -1.5     |       | +1.5  | mV    |

|                                            |                    | MAX16821A                           | 0.992    | 1     | 1.008 |       |

| Amplifier Voltage Gain                     | Av(DIFF)           | MAX16821B                           | 5.85     | 6     | 6.1   | V/V   |

|                                            |                    | MAX16821C                           | 18.5     | 20    | 21.5  |       |

|                                            |                    | MAX16821A, C <sub>DIFF</sub> = 20pF |          | 1.7   |       | MHz   |

| 3dB Bandwidth                              | f <sub>3dB</sub>   | MAX16821B, C <sub>DIFF</sub> = 20pF |          | 1600  |       | kHz   |

|                                            |                    | MAX16821C, C <sub>DIFF</sub> = 20pF |          | 550   |       | KΠZ   |

| OFNIOE 1 OFNIOE 1                          |                    | MAX16821A                           | 50       | 100   |       |       |

| SENSE+ to SENSE- Input Resistance          | Rvs                | MAX16821B                           | 30       | 60    |       | kΩ    |

| riesistarice                               |                    | MAX16821C                           | 10       | 20    |       |       |

| OUTV AMPLIFIER                             |                    |                                     |          |       |       |       |

| Gain-Bandwidth Product                     |                    | V <sub>OUTV</sub> = 2V              |          | 4     |       | MHz   |

| 3dB Bandwidth                              |                    | V <sub>OUTV</sub> = 2V              |          | 1     |       | MHz   |

| Output Sink Current                        |                    |                                     | 30       |       |       | μΑ    |

| Output Source Current                      |                    |                                     | 80       |       |       | μΑ    |

| Maximum Load Capacitance                   |                    |                                     |          | 50    |       | рF    |

| OUTV to (CSP - CSN) Transfer Function      |                    | $4mV \le C_{SP} - C_{SN} \le 32mV$  | 132.5    | 135   | 137.7 | V/V   |

| Input Offset Voltage                       |                    |                                     |          | 1     |       | mV    |

| VOLTAGE-ERROR AMPLIFIER (I                 | EAOUT)             |                                     |          |       |       |       |

| Open-Loop Gain                             | Avolea             |                                     |          | 70    |       | dB    |

| Unity-Gain Bandwidth                       | fgBW               |                                     |          | 3     |       | MHz   |

| EAN Input Bias Current                     | I <sub>B(EA)</sub> | VEAN = 2V                           | -0.2     | +0.03 | +0.2  | μΑ    |

| Error Amplifier Output Clamping<br>Voltage | VCLAMP(EA)         | With respect to V <sub>CM</sub>     | 905      | 930   | 940   | mV    |

| INPUTS (MODE AND OVI)                      | -                  |                                     |          |       |       |       |

| MODE Input-Voltage High                    |                    |                                     | 2        |       |       | V     |

| MODE Input-Voltage Low                     |                    |                                     |          |       | 0.8   | V     |

| MODE Pulldown Current                      |                    |                                     | 4        | 5     | 6     | μΑ    |

| OVI Trip Threshold                         | OVPTH              |                                     | 1.244    | 1.276 | 1.308 | V     |

| OVI Hysteresis                             | OVI <sub>HYS</sub> |                                     |          | 200   |       | mV    |

| OVI Input Bias Current                     | lovi               | V <sub>OVI</sub> = 1V               |          | 0.2   |       | μΑ    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = 5V, V_{DD} = V_{CC}, T_A = T_J = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                   | SYMBOL          | CONDITIONS | MIN   | TYP  | MAX   | UNITS |

|-----------------------------|-----------------|------------|-------|------|-------|-------|

| ENABLE INPUT (EN)           |                 |            |       |      |       |       |

| EN Input-Voltage High       |                 | EN rising  | 2.437 | 2.5  | 2.562 | V     |

| EN Input Hysteresis         |                 |            |       | 0.28 |       | V     |

| EN Pullup Current           | I <sub>EN</sub> |            | 13.5  | 15   | 16.5  | μΑ    |

| THERMAL SHUTDOWN            |                 |            |       |      |       |       |

| Thermal Shutdown            |                 |            |       | 165  |       | °C    |

| Thermal-Shutdown Hysteresis |                 |            |       | 20   |       | °C    |

Note 1: All devices are 100% production tested at +25°C. Limits over temperature are guaranteed by design.

Note 2: Does not include an error due to finite error amplifier gain. See the Voltage-Error Amplifier section.

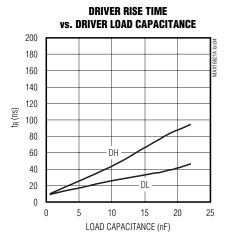

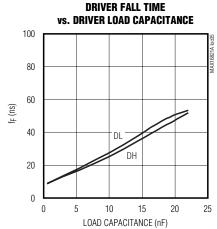

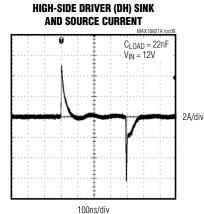

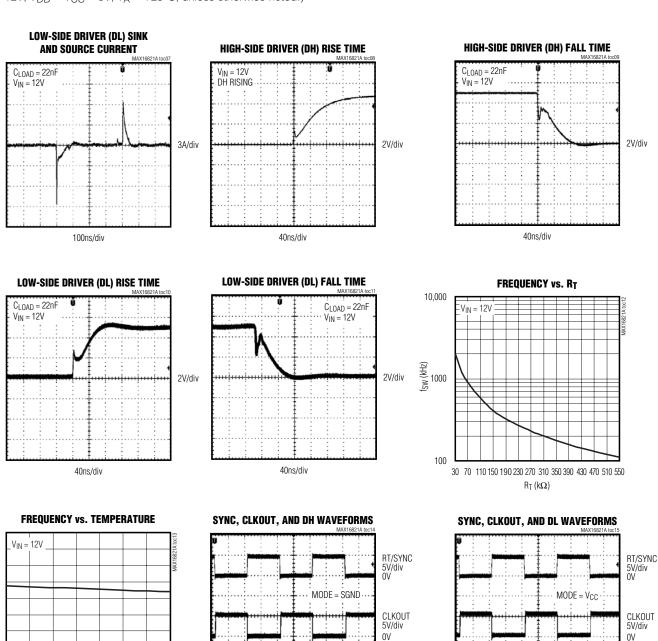

### **Typical Operating Characteristics**

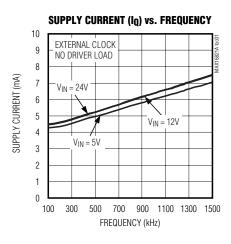

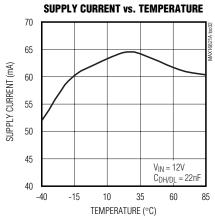

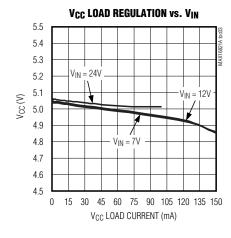

(V<sub>IN</sub> = 12V, V<sub>DD</sub> = V<sub>CC</sub> = 5V, T<sub>A</sub> = +25°C, unless otherwise noted.)

260

258

256

254

252 250

248

246 244

242 240 0 5

15 20

TEMPERATURE (°C)

30

## High-Power Synchronous HBLED Drivers with Rapid Current Pulsing

### Typical Operating Characteristics (continued)

$(V_{IN} = 12V, V_{DD} = V_{CC} = 5V, T_A = +25$ °C, unless otherwise noted.)

1μs/div

5V/div 0V 5V/div 0V

1µs/div

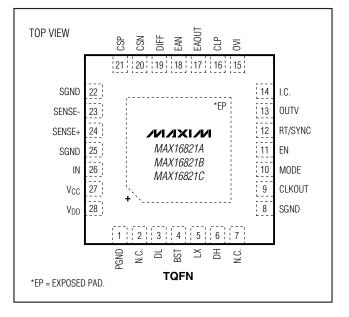

### **Pin Description**

| PIN       | NAME     | FUNCTION                                                                                                                                                                                                                                                                            |

|-----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1         | PGND     | Power-Supply Ground                                                                                                                                                                                                                                                                 |

| 2, 7      | N.C.     | No Connection. Not internally connected.                                                                                                                                                                                                                                            |

| 3         | DL       | Low-Side Gate-Driver Output                                                                                                                                                                                                                                                         |

| 4         | BST      | Boost-Flying Capacitor Connection. Reservoir capacitor connection for the high-side MOSFET driver supply. Connect a ceramic capacitor between BST and LX.                                                                                                                           |

| 5         | LX       | High-Side MOSFET Source Connection                                                                                                                                                                                                                                                  |

| 6         | DH       | High-Side Gate-Driver Output                                                                                                                                                                                                                                                        |

| 8, 22, 25 | SGND     | Signal Ground. SGND is the ground connection for the internal control circuitry. Connect SGND and PGND together at one point near the IC.                                                                                                                                           |

| 9         | CLKOUT   | Oscillator Output. If MODE is low, the rising edge of CLKOUT phase shifts from the rising edge of DH by 180°. If MODE is high, the rising edge of CLKOUT phase shifts from the rising edge of DL by 180°.                                                                           |

| 10        | MODE     | Buck/Boost Mode Selection Input. Drive MODE low for low-side buck mode operation. Drive MODE high for boost or high-side buck mode operation. MODE has an internal 5µA pulldown current to ground.                                                                                  |

| 11        | EN       | Output Enable. Drives EN high or leave unconnected for normal operation. Drive EN low to shut down the power drivers. EN has an internal 15µA pullup current.                                                                                                                       |

| 12        | RT/SYNC  | Switching Frequency Programming. Connect a resistor from RT/SYNC to SGND to set the internal oscillator frequency. Drive RT/SYNC to synchronize the switching frequency with an external clock.                                                                                     |

| 13        | OUTV     | Inductor Current-Sense Output. OUTV is an amplifier output voltage proportional to the inductor current. The voltage at OUTV = 135 x (V <sub>CSP</sub> - V <sub>CSN</sub> ).                                                                                                        |

| 14        | I.C.     | Internally Connected. Connect to SGND for proper operation.                                                                                                                                                                                                                         |

| 15        | OVI      | Overvoltage Protection. When OVI exceeds the programmed output voltage by 12.7%, the low-side and the high-side drivers are turned off. When OVI falls 20% below the programmed output voltage, the drivers are turned on after power-on reset and soft-start cycles are completed. |

| 16        | CLP      | Current-Error-Amplifier Output. Compensate the current loop by connecting an RC network to ground.                                                                                                                                                                                  |

| 17        | EAOUT    | Voltage-Error-Amplifier Output. Connect EAOUT to the external gain-setting network.                                                                                                                                                                                                 |

| 18        | EAN      | Voltage-Error-Amplifier Inverting Input                                                                                                                                                                                                                                             |

| 19        | DIFF     | Differential Remote-Sense Amplifier Output. DIFF is the output of a precision amplifier with SENSE+ and SENSE- as inputs.                                                                                                                                                           |

| 20        | CSN      | Current-Sense Differential Amplifier Negative Input. The differential voltage between CSN and CSP is amplified internally by the current-sense amplifier (Gain = 34.5) to measure the inductor current.                                                                             |

| 21        | CSP      | Current-Sense Differential Amplifier Positive Input. The differential voltage between CSP and CSN is amplified internally by the current-sense amplifier (Gain = 34.5) to measure the inductor current.                                                                             |

| 23        | SENSE-   | Differential LED Current-Sensing Negative Input. Connect SENSE- to the negative side of the LED current-sense resistor or to the negative feedback point.                                                                                                                           |

| 24        | SENSE+   | Differential LED Current-Sensing Positive Input. Connect SENSE+ to the positive side of the LED current-sense resistor, or to the positive feedback point.                                                                                                                          |

| 26        | IN       | Supply Voltage Input. Connect IN to V <sub>CC</sub> , for a 4.75V to 5.5V input supply range.                                                                                                                                                                                       |

| 27        | Vcc      | Internal +5V Regulator Output. V <sub>CC</sub> is derived from V <sub>IN</sub> . Bypass V <sub>CC</sub> to SGND with 4.7µF and 0.1µF ceramic capacitors.                                                                                                                            |

| 28        | $V_{DD}$ | Low-Side Driver Supply Voltage                                                                                                                                                                                                                                                      |

| _         | EP       | Exposed Pad. EP is internally connected to SGND. Connect EP to a large-area ground plane for effective power dissipation. Connect EP to SGND. Do not use as a ground connection.                                                                                                    |

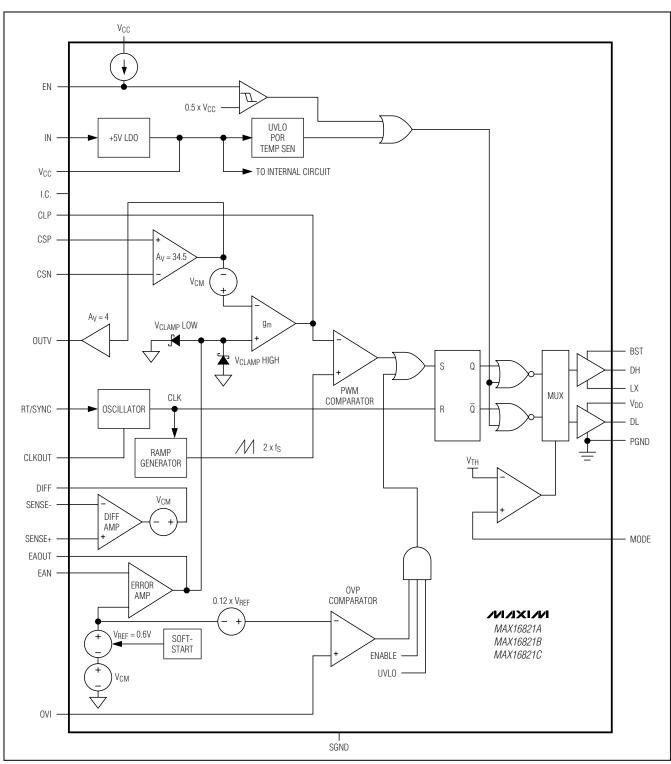

### **Detailed Description**

The MAX16821A/MAX16821B/MAX16821C are high-performance average current-mode PWM controllers for high-power and high-brightness LEDs (HBLEDs). The average current-mode control technique offers inherently stable operation, reduces component derating and size by accurately controlling the inductor current. The devices achieve high efficiency at high currents (up to 30A) with a minimum number of external components. A logic input (MODE) allows the LED driver to switch between buck and boost modes of operation.

The MAX16821A/MAX16821B/MAX16821C feature a CLKOUT output 180° out-of-phase with respect to either the high-side or low-side driver, depending on MODE's logic level. CLKOUT provides the drive for a second out-of-phase LED driver for applications requiring reduced input capacitor ripple current while operating another LED driver.

The MAX16821A/MAX16821B/MAX16821C consist of an inner average current regulation loop controlled by an outer loop. The combined action of the inner current loop and outer voltage loop corrects the LED current errors by adjusting the inductor current resulting in a tightly regulated LED current. The differential amplifier (SENSE+ and SENSE- inputs) senses the LED current using a resistor in series with the LEDs and produces an amplified version of the sense voltage at DIFF. The resulting amplified sensed voltage is compared against an internal 0.6V reference at the error amplifier input.

#### Input Voltage

The MAX16821A/MAX16821B/MAX16821C operate with a 4.75V to 5.5V input supply range when the internal LDO is disabled (VCC connected to IN) or a 7V to 28V input supply range when the internal LDO is enabled. For a 7V to 28V input voltage range, the internal LDO provides a regulated 5V output with 60mA of sourcing capability. Bypass VCC to SGND with 4.7 $\mu$ F and 0.1 $\mu$ F low-ESR ceramic capacitors.

The MAX16821A/MAX16821B/MAX16821C's V<sub>DD</sub> input provides supply voltage for the low-side and the high-side MOSFET drivers. Connect V<sub>DD</sub> to V<sub>CC</sub> using an R-C filter to isolate the analog circuits from the MOSFET drivers. The internal LDO powers up the MAX16821A/MAX16821B/MAX16821C. For applications utilizing a 5V input voltage, disable the internal LDO by connecting IN and V<sub>CC</sub> together. The 5V power source must be in the 4.75V to 5.5V range of for proper operation of the MAX16821A/MAX16821B/MAX16821C.

#### **Undervoltage Lockout (UVLO)**

The MAX16821A/MAX16821B/MAX16821C include UVLO and a 2048 clock-cycle power-on-reset circuit. The UVLO rising threshold is set to 4.3V with 200mV hysteresis. Hysteresis at UVLO eliminates chattering during startup. Most of the internal circuitry, including the oscillator, turns on when the input voltage reaches 4V. The MAX16821A/MAX16821B/MAX16821C draw up to 3.5mA of quiescent current before the input voltage reaches the UVLO threshold.

#### Soft-Start

The MAX16821A/MAX16821B/MAX16821C include an internal soft-start for a glitch-free rise of the output voltage. After 2048 power-on-reset clock cycles, a 0.6V reference voltage connected to the positive input of the internal error amplifier ramps up to its final value after 1024 clock cycles. Soft-start reduces inrush current and stress on system components. During soft-start, the LED current will ramp monotonically towards its final value.

#### **Internal Oscillator**

The internal oscillator generates a clock with the frequency inversely proportional to the value of R<sub>T</sub> (see the *Typical Operating Circuit*). The oscillator frequency is adjustable from 125kHz to 1.5MHz range using a single resistor connected from RT/SYNC to SGND. The frequency accuracy avoids the overdesign, size, and cost of passive filter components like inductors and capacitors. Use the following equation to calculate the oscillator frequency:

For  $120k\Omega \le R_T \le 500k\Omega$ :

$$f_{SW} = \frac{6.25 \times 10^{10}}{R_T} \text{ (Hz)}$$

For  $40k\Omega \le R_T \le 120k\Omega$ :

$$f_{SW} = \frac{6.40 \times 10^{10}}{R_T} \text{ (Hz)}$$

The oscillator also generates a 2V<sub>P-P</sub> ramp signal for the PWM comparator and a 180° out-of-phase clock signal at CLKOUT to drive a second out-of-phase LED current regulator.

Figure 1. Internal Block Diagram

#### **Synchronization**

The MAX16821A/MAX16821B/MAX16821C synchronize to an external clock connected to RT/SYNC. The application of an external clock at RT/SYNC disables the internal oscillator. Once the MAX16821A/MAX16821B/MAX16821C are synchronized to an external clock, the external clock cannot be removed if reliable operation is to be maintained.

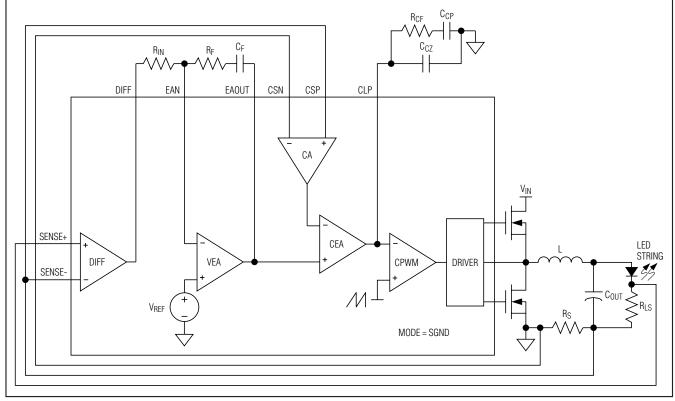

#### **Control Loop**

The MAX16821A/MAX16821B/MAX16821C use an average current-mode control scheme to regulate the output current (Figure 2). The main control loop consists of an inner current regulation loop for controlling the inductor current and an outer current regulation loop for regulating the LED current. The inner current regulation loop absorbs the double pole of the inductor and output capacitor combination reducing the order of the outer current regulation loop to that of a single-pole system. The inner current regulation loop consists of a current-sense resistor (Rs), a current-sense amplifier (CSA), a current-error amplifier (CEA), an oscillator providing the carrier ramp, and a PWM comparator (CPWM) (Figure 2). The MAX16821A/MAX16821B/

MAX16821C outer LED-current control loop consists of a differential amplifier (DIFF), a reference voltage, and a voltage-error amplifier (VEA).

#### **Inductor Current-Sense Amplifier**

The differential current-sense amplifier (CSA) provides a 34.5V/V DC gain. The typical input offset voltage of the current-sense amplifier is 0.1mV with a 0 to 5.5V common-mode voltage range ( $V_{IN}=7V$  to 28V). The current-sense amplifier senses the voltage across Rs. The maximum common-mode voltage is 3.2V when  $V_{IN}=5V$ .

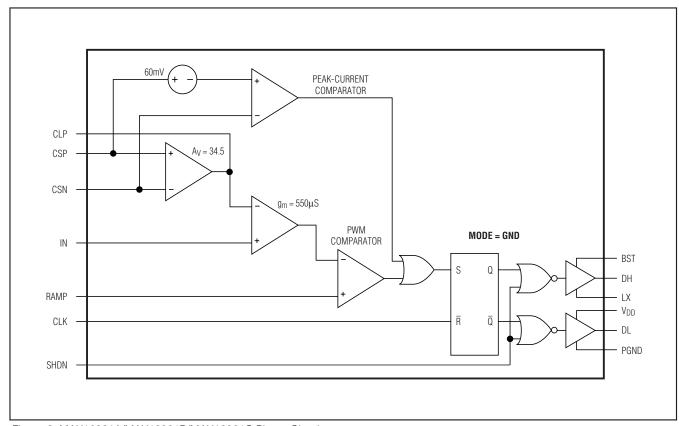

#### **Inductor Peak-Current Comparator**

The peak-current comparator provides a path for fast cycle-by-cycle current limit during extreme fault conditions, such as an inductor malfunction (Figure 3). Note the average current-limit threshold of 27.5mV still limits the output current during short-circuit conditions. To prevent inductor saturation, select an inductor with a saturation current specification greater than the average current limit. The 60mV threshold for triggering the peak-current limit is twice the full-scale average current-limit voltage threshold. The peak-current comparator has only a 260ns delay.

Figure 2. MAX16821A/MAX16821B/MAX16821C Control Loop

10 \_\_\_\_\_\_ /\/\lambda \lambda \

#### **Current-Error Amplifier**

The MAX16821A/MAX16821B/MAX16821C include a transconductance current-error amplifier with a typical g<sub>m</sub> of 550µS and 320µA output sink and source capability. The current-error amplifier output (CLP) is connected to the inverting input of the PWM comparator. CLP is also externally accessible to provide frequency compensation for the inner current regulation loop (Figure 2). Compensate CEA so the inductor current negative slope, which becomes the positive slope to the inverting input of the PWM comparator, is less than the slope of the internally generated voltage ramp (see the *Compensation* section). In applications without synchronous rectification, the LED driver can be turned off and on instantaneously by shorting or opening the CLP to ground.

#### **PWM Comparator and R-S Flip-Flop**

An internal PWM comparator sets the duty cycle by comparing the output of the current-error amplifier to a

2VP-P ramp signal. At the start of each clock cycle, an R-S flip-flop resets and the high-side driver (DH) turns on if MODE is connected to SGND, and DL turns on if MODE is connected to VCC. The comparator sets the flip-flop as soon as the ramp signal exceeds the CLP voltage, thus terminating the ON cycle. See Figure 3.

### **Differential Amplifier**

The differential amplifier (DIFF) allows LED current sensing (Figure 2). It provides true-differential LED current sensing, and amplifies the sense voltage by a factor of 1 (MAX16821A), 6 (MAX16821B), and 20 (MAX16821C), while rejecting common-mode voltage errors. The VEA provides the difference between the differential amplifier output (DIFF) and the desired LED current-sense voltage. The differential amplifier has a bandwidth of 1.7MHz (MAX16821A), 1.6MHz (MAX16821B), and 550kHz (MAX16821C). The difference between SENSE+ and SENSE- is regulated to +0.6V (MAX16821A), +0.1V (MAX16821B), or +0.03V (MAX16821C).

Figure 3. MAX16821A/MAX16821B/MAX16821C Phase Circuit

#### Voltage-Error Amplifier (VEA)

The VEA sets the gain of the voltage control loop, and determines the error between the differential amplifier output and the internal reference voltage. The VEA output clamps to 0.93V relative to the internal common-mode voltage, V<sub>CM</sub> (+0.6V), limiting the average maximum current. The maximum average current-limit threshold is equal to the maximum clamp voltage of the VEA divided by the gain (34.5) of the current-sense amplifier. This results in accurate settings for the average maximum current.

#### **MOSFET Gate Drivers**

The high-side (DH) and low-side (DL) drivers drive the gates of external n-channel MOSFETs. The drivers' 4A peak sink- and source-current capability provides ample drive for the fast rise and fall times of the switching MOSFETs. Faster rise and fall times result in reduced cross-conduction losses. Size the high-side and low-side MOSFETs to handle the peak and RMS currents during overload conditions. The driver block also includes a logic circuit that provides an adaptive nonoverlap time to prevent shoot-through currents during transition. The typical nonoverlap time is 35ns between the high-side and low-side MOSFETs.

#### BST

The MAX16821A/MAX16821B/MAX16821C provide power to the low-side and high-side MOSFET drivers through V<sub>DD</sub>. A bootstrap capacitor from BST to LX provides the additional boost voltage necessary for the high-side driver. V<sub>DD</sub> supplies power internally to the low-side driver. Connect a 0.47µF low-ESR ceramic capacitor between BST and LX and a Schottky diode from BST to V<sub>DD</sub>.

#### **Protection**

The MAX16821A/MAX16821B/MAX16821C include output overvoltage protection (OVP). During fault conditions when the load goes to high impedance (output opens), the controller attempts to maintain LED current. The OVP disables the MAX16821A/MAX16821B/MAX16821C whenever the output voltage exceeds the OVP threshold, protecting the external circuits from undesirable voltages.

#### **Current Limit**

The error amplifier (VEA) output is clamped between -0.050V and +0.93V with respect to common-mode voltage (VCM). Average current-mode control limits the average current sourced by the converter during a fault condition. When a fault condition occurs, the VEA output clamps to +0.93V with respect to the common-mode voltage (0.6V) to limit the maximum current sourced by the converter to ILIMIT = 0.0275 / Rs.

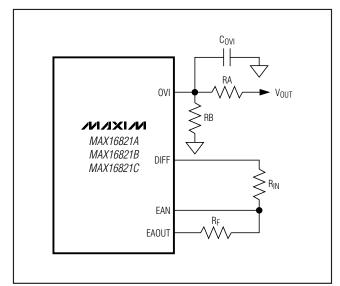

#### **Overvoltage Protection**

The OVP comparator compares the OVI input to the overvoltage threshold. The overvoltage threshold is typically 1.127 times the internal 0.6V reference voltage plus V<sub>CM</sub> (0.6V). A detected overvoltage event trips the comparator output turning off both high-side and low-side MOSFETs. Add an RC delay to reduce the sensitivity of the overvoltage circuit and avoid unnecessary tripping of the converter (Figure 4). After the OVI voltage falls below 1.076V (typ.), high-side and low-side drivers turn on only after a 2048 clock-cycle POR and a 1024 clock-cycle soft-start have elapsed. Disable the overvoltage function by connecting OVI to SGND.

Figure 4. Overvoltage Protection Input Delay

### \_Applications Information

#### **Boost LED Driver**

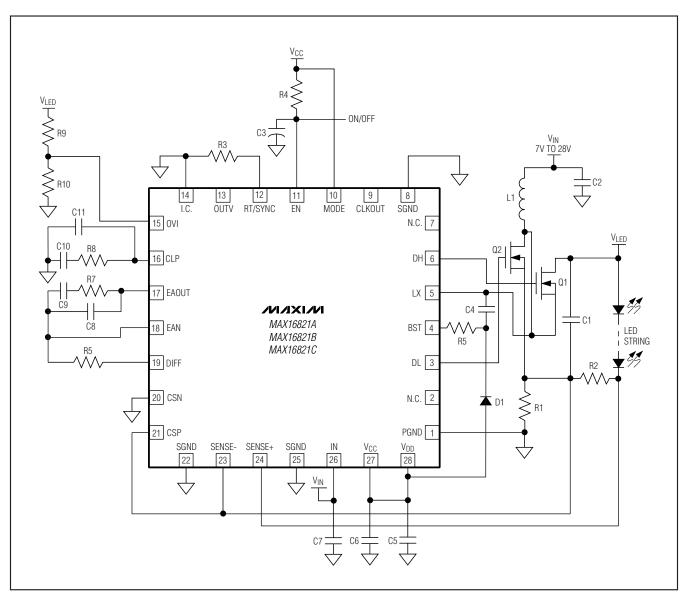

Figure 5 shows the MAX16821A/MAX16821B/MAX16821C configured as a synchronous boost converter with MODE connected to  $V_{CC}$ . During the on-time, the input voltage charges the inductor. During the off-time, the

inductor discharges to the output. The output voltage cannot go below the input voltage in this configuration. Resistor R1 senses the inductor current and resistor R2 senses the LED current. The outer LED current regulation loop programs the average current in the inductor, thus achieving tight LED current regulation.

Figure 5. Synchronous Boost LED Driver (Output Voltage Not to Exceed 28V)

#### Input-Referenced Buck-Boost LED Driver

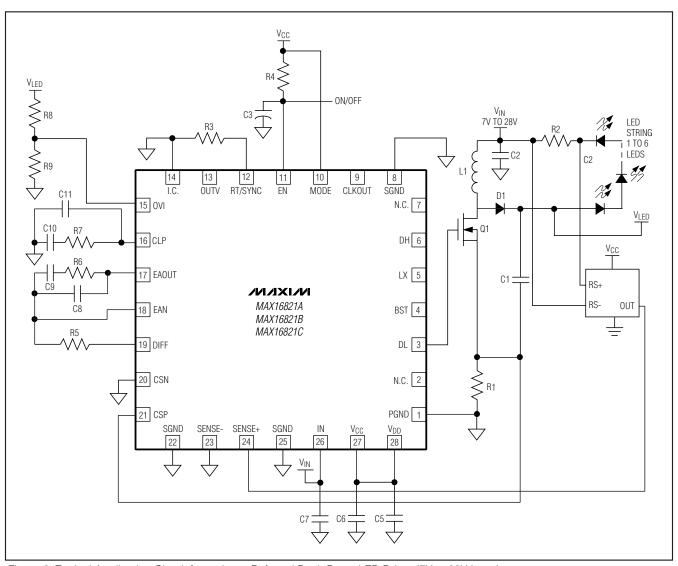

The circuit in Figure 6 shows a step-up/step-down regulator. It is similar to the boost converter in Figure 5 in that the inductor is connected to the input and the MOSFET is essentially connected to ground. However, rather than going from the output to ground, the LEDs

span from the output to the input. This effectively removes the boost-only restriction of the regulator in Figure 5, allowing the voltage across the LED to be greater or less than the input voltage. LED current-sensing is not ground-referenced, so a high-side current-sense amplifier is used to measure current.

Figure 6. Typical Application Circuit for an Input-Referred Buck-Boost LED Driver (7V to 28V Input)

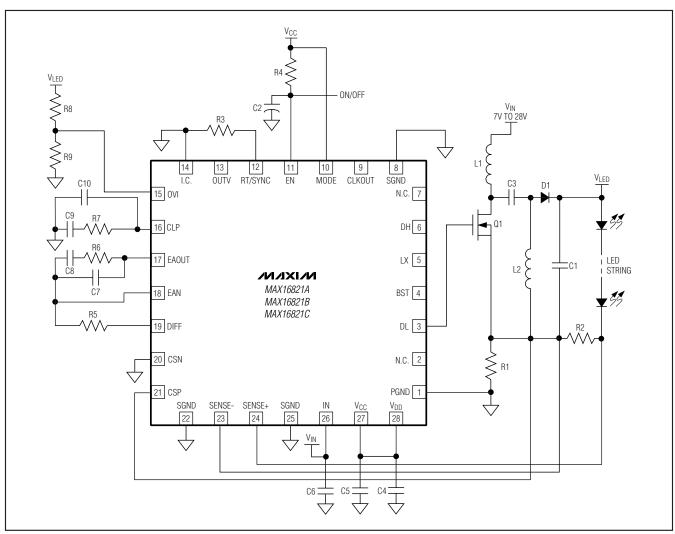

#### **SEPIC LED Driver**

Figure 7 shows the MAX16821A/MAX16821B/MAX16821C configured as a SEPIC LED driver. While buck topologies produce an output always lower than the input, and boost topologies produce an output always greater than the input, a SEPIC topology allows the output voltage to be greater than, equal to, or less than the input. In a SEPIC topology, the voltage across C3 is the same as the input voltage, and L1 and L2 have the same inductance. Therefore, when Q1 turns on (ontime), the currents in both inductors (L1 and L2) ramp up at the same rate. The output capacitor supports the output voltage during this time. When Q1 turns off (off-time), L1 current recharges C3 and combines with L2 to

provide current to recharge C1 and supplies the load current. Since the voltage waveform across L1 and L2 are exactly the same, it is possible to wind both inductors on the same core (a coupled inductor). Although voltages on L1 and L2 are the same, RMS currents can be quite different so the windings may require a different gauge wire. Because of the dual inductors and segmented energy transfer, the efficiency of a SEPIC converter is lower than the standard buck or boost configurations. As in the boost driver, the current-sense resistor connects to ground, allowing the output voltage of the LED driver to exceed the rated maximum voltage of the MAX16821A/MAX16821B/MAX16821C.

Figure 7. Typical Application Circuit for a SEPIC LED Driver

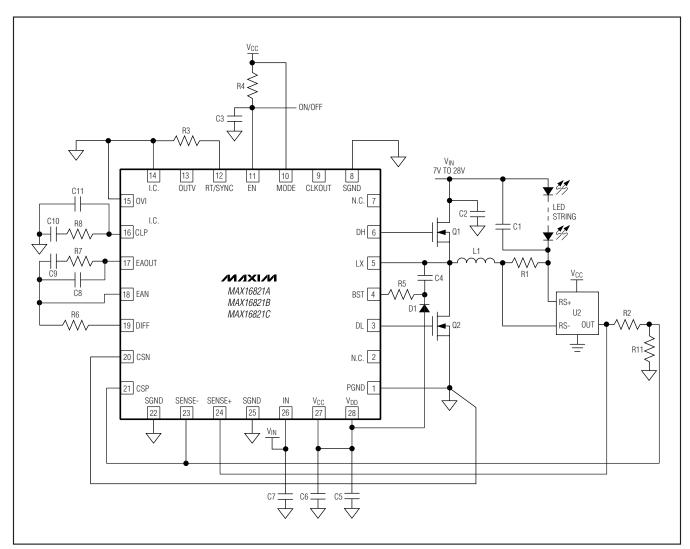

### Low-Side Buck Driver with Synchronous Rectification

In Figure 8, the input voltage goes from 7V to 28V and, because of the ground-based current-sense resistor, the output voltage can be as high as the input. The synchronous MOSFET keeps the power dissipation to a minimum, especially when the input voltage is large compared to the voltage on the LED string. For the

inner average current-loop inductor, current is sensed by resistor R1. To regulate the LED current, R2 creates a voltage that the differential amplifier compares to 0.6V. Capacitor C1 is small and helps reduce the ripple current in the LEDs. Omit C1 in cases where the LEDs can tolerate a higher ripple current. The average current-mode control scheme converts the input voltage to a current source feeding the LED string.

Figure 8. Application Circuit for a Low-Side Buck LED Driver

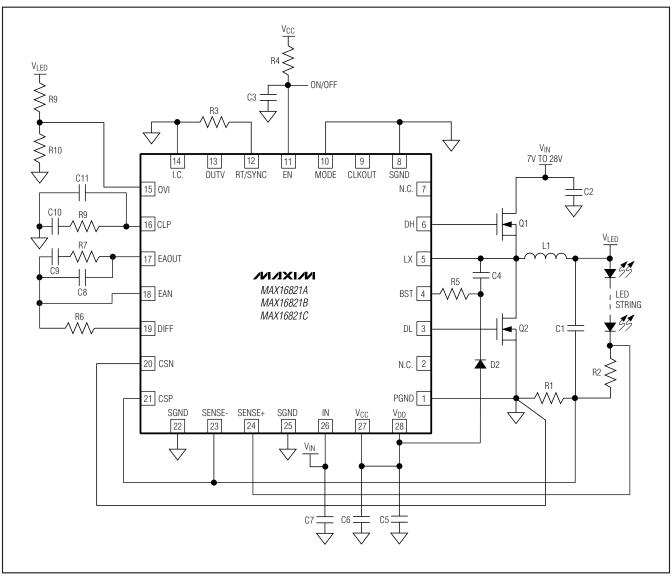

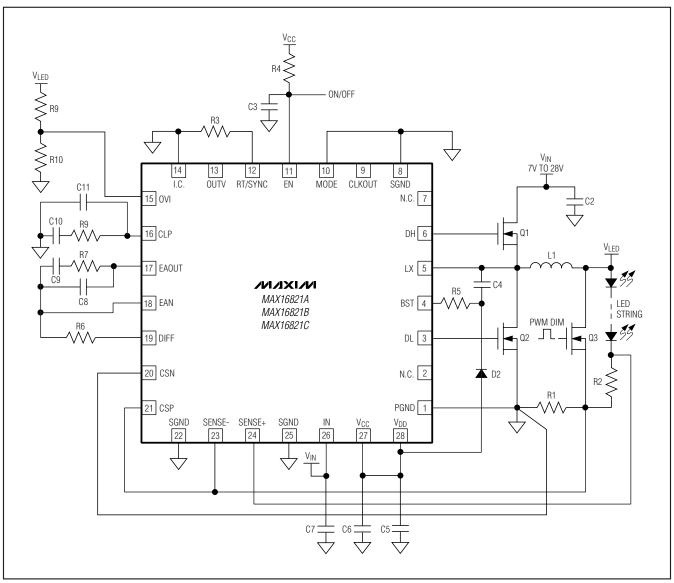

### **High-Side Buck Driver** with Synchronous Rectification

In Figure 9, the input voltage goes from 7V to 28V, the LED load is connected from the positive side to the current-sense resistor (R1) in series with the inductor, and MODE is connected to VCC. For the inner average current-loop inductor, current is sensed by resistor R1 and is then transferred to the low side by the high-side current-sense

amplifier, U2. The voltage appearing across resistor R11 becomes the average inductor current-sense voltage for the inner average current loop. To regulate the LED current, R2 creates a voltage that the differential amplifier compares to its internal reference. Capacitor C1 is small and is added to reduce the ripple current in the LEDs. In cases where the LEDs can tolerate a higher ripple current, capacitor C1 can be omitted.

Figure 9. Application Circuit for a High-Side Buck LED Driver

#### **Inductor Selection**

The switching frequency, peak inductor current, and allowable ripple at the output determine the value and size of the inductor. Selecting higher switching frequencies reduces inductance requirements, but at the cost of efficiency. The charge/discharge cycle of the gate and drain capacitance in the switching MOSFETs create switching losses worsening at higher input voltages, since switching losses are proportional to the square of the input voltage. The MAX16821A/MAX16821B/MAX16821C operate up to 1.5MHz.

Choose inductors from the standard high-current, surface-mount inductor series available from various manufacturers. Particular applications may require custom-made inductors. Use high-frequency core material for custom inductors. High  $\Delta I_{\rm L}$  causes large peak-to-peak flux excursion increasing the core losses at higher frequencies. The high-frequency operation coupled with high  $\Delta I_{\rm L}$  reduces the required minimum inductance and makes the use of planar inductors possible.

The following discussion is for buck or continuous boost-mode topologies. Discontinuous boost, buck-boost, and SEPIC topologies are quite different in regards to component selection. Use the following equations to determine the minimum inductance value:

Buck regulators:

$$L_{MIN} = \frac{(V_{INMAX} - V_{LED}) \times V_{LED}}{V_{INMAX} \times f_{SW} \times \Delta I_{L}}$$

Boost regulators:

$$L_{MIN} = \frac{\left(V_{LED} - V_{INMAX}\right) \times V_{INMAX}}{V_{I,ED} \times f_{SW} \times \Delta I_{I}}$$

where V<sub>LED</sub> is the total voltage across the LED string.

The average current-mode control feature of the MAX16821A/MAX16821B/MAX16821C limits the maximum peak inductor current and prevents the inductor from saturating. Choose an inductor with a saturating current greater than the worst-case peak inductor current. Use the following equation to determine the worst-case current in the average current-mode control loop.

$$I_{LPEAK} = \frac{V_{CL}}{R_S} + \left(\frac{\Delta I_{CL}}{2}\right)$$

where Rs is the sense resistor and  $V_{CL} = 0.030V$ . For the buck converter, the sense current is the inductor current and for the boost converter, the sense current is the input current.

#### **Switching MOSFETs**

When choosing a MOSFET for voltage regulators, consider the total gate charge, RDS(ON), power dissipation, and package thermal impedance. The product of the MOSFET gate charge and on-resistance is a figure of merit, with a lower number signifying better performance. Choose MOSFETs optimized for high-frequencv switching applications. The average current from the MAX16821A/MAX16821B/MAX16821C gate-drive output is proportional to the total capacitance it drives from DH and DL. The power dissipated in the MAX16821A/MAX16821B/MAX16821C is proportional to the input voltage and the average drive current. The gate charge and drain capacitance losses (CV2), the cross-conduction loss in the upper MOSFET due to finite rise/fall time, and the I2R loss due to RMS current in the MOSFET RDS(ON) account for the total losses in the MOSFET. Estimate the power loss (PDMOS ) in the high-side and low-side MOSFETs using the following equations:

$$\begin{split} \text{PD}_{\text{MOS\_HI}} &= \left(Q_{\text{G}} \times V_{\text{DD}} \times f_{\text{SW}}\right) + \\ & \left[\frac{V_{\text{IN}} \times I_{\text{LED}} \times \left(t_{\text{R}} + t_{\text{f}}\right) \times f_{\text{SW}}}{2}\right] + \\ & R_{\text{DSON}} \times I^{2}_{\text{RMS-HI}} \end{split}$$

where QG, RDS(ON), tR, and tF are the upper-switching MOSFET's total gate charge, on-resistance, rise time, and fall time, respectively.

$$I_{RMS-HI} = \sqrt{(I^2VALLEY + I^2PK + I_{VALLEY} \times I_{PK}) \times \frac{D}{3}}$$

For the buck regulator, D is the duty cycle,  $|VALLEY| = (|OUT - \Delta I_L / 2)$  and  $|PK| = (|OUT + \Delta I_L / 2)$ .

$$\begin{split} & \text{PD}_{\text{MOS\_LO}} = \left( \text{Q}_{\text{G}} \times \text{V}_{\text{DD}} \times \text{f}_{\text{SW}} \right) + \, \text{R}_{\text{DSON}} \times \text{I}^2 \text{RMS\_LO} \\ & \text{I}_{\text{RMS\_LO}} = \sqrt{ \left( \text{I}^2 \text{VALLEY} + \text{I}^2 \text{PK} + \text{I}_{\text{VALLEY}} \times \text{I}_{\text{PK}} \right) \times \frac{\left( \text{1-D} \right)}{3} } \end{split}$$

#### **Input Capacitors**

The discontinuous input-current waveform of the buck converter causes large ripple currents in the input capacitor. The switching frequency, peak inductor current, and the allowable peak-to-peak voltage ripple reflected back to the source dictate the capacitance requirement. The input ripple is comprised of  $\Delta V_Q$  (caused by the capacitor discharge) and  $\Delta V_{ESR}$  (caused by the ESR of the capacitor).

\_\_ /VI/IXI/VI

Use low-ESR ceramic capacitors with high ripple-current capability at the input. In the case of the boost topology where the inductor is in series with the input, the ripple current in the capacitor is the same as the inductor ripple and the input capacitance is small.

#### **Output Capacitors**

The function of the output capacitor is to reduce the output ripple to acceptable levels. The ESR, ESL, and the bulk capacitance of the output capacitor contribute to the output ripple. In most of the applications, the output ESR and ESL effects can be dramatically reduced by using low-ESR ceramic capacitors. To reduce the ESL effects, connect multiple ceramic capacitors in parallel to achieve the required bulk capacitance.

In a buck configuration, the output capacitance,  $C_{\text{OUT}}$ , is calculated using the following equation:

$$C_{OUT} \ge \frac{(V_{INMAX} - V_{LED}) \times V_{LED}}{\Delta V_{R} \times 2 \times L \times V_{INMAX} \times f_{SW}^{2}}$$

where  $\Delta V_R$  is the maximum allowable output ripple.

In a boost configuration, the output capacitance,  $C_{\text{OUT}}$ , is calculated as:

$$C_{OUT} \ge \frac{(V_{LED} - V_{INMIN}) \times 2 \times I_{LED}}{\Delta V_{R} \times V_{LED} \times f_{SW}}$$

where ILED is the output current.

In a buck-boost configuration, the output capacitance,  $C_{\mbox{OUT}}$  is:

$$C_{OUT} \geq \frac{2 \times V_{LED} \times I_{LED}}{\Delta V_{R} \times (V_{LED} + V_{INMIN}) \times f_{SW}}$$

where  $V_{\text{LED}}$  is the voltage across the load and  $I_{\text{LED}}$  is the output current.

#### **Average Current Limit**

The average current-mode control technique of the MAX16821A/MAX16821B/MAX16821C accurately limits the maximum output current in the case of the buck configuration. The MAX16821A/MAX16821B/MAX16821C sense the voltage across the sense resistor and limit the peak inductor current (I<sub>L-PK</sub>) accordingly. The on-cycle terminates when the current-sense voltage reaches 26.4mV (min). Use the following equation to calculate the maximum current-sense resistor value:

$$R_{SENSE} = \left(\frac{0.0264}{I_{ED}}\right)$$

Select a 5% lower value of Rs to compensate for any parasitics associated with the PCB. Select a non-inductive resistor with the appropriate wattage rating. In the case of the boost configuration, the MAX16821A/MAX16821B/MAX16821C accurately limits the maximum input current. Use the following equation to calculate the current-sense resistor value:

$$R_{SENSE} = \left(\frac{0.0264}{I_{IN}}\right)$$

where I<sub>IN</sub> is the input current.

#### Compensation

The main control loop consists of an inner current loop (inductor current) and an outer LED current regulation loop. The MAX16821A/MAX16821B/MAX16821C use an average current-mode control scheme to regulate the LED current (Figure 2). The VEA output provides the controlling voltage for the current source. The inner current loop absorbs the inductor pole reducing the order of the LED current loop to that of a single-pole system. The major consideration when designing the current control loop is making certain that the inductor downslope (which becomes an upslope at the output of the CEA) does not exceed the internal ramp slope. This is a necessary condition to avoid subharmonic oscillations similar to those in peak current mode with insufficient slope compensation. This requires that the gain at the output of the CEA be limited based on the following equation:

Buck:

$$R_{CF} \le \frac{V_{RAMP} \times f_{SW} \times L}{A_V \times R_S \times V_{LED} \times g_m}$$

where  $V_{RAMP}$  = 2V,  $g_m$  = 550 $\mu$ S,  $A_V$  = 34.5V/V, and  $V_{LED}$  is the voltage across the LED string.

The crossover frequency of the inner current loop is given by:

$$f_C = \frac{R_S}{V_{BAMP}} \times \frac{V_{IN}}{2 \times \pi \times L} \times 34.5 \times g_m \times R_{CF}$$

For adequate phase margin place the zero formed by RCF and CCZ at least 3 to 5 times below the crossover frequency. The pole formed by RCF and CCP may not be required in most applications but can be added to minimize noise at a frequency at or above the switching frequency.

Boost:

$$\mathsf{R}_{\mathsf{CF}} \, \leq \, \frac{\mathsf{V}_{\mathsf{RAMP}} \, \times \, \mathsf{f}_{\mathsf{SW}} \, \times \, \mathsf{L}}{\mathsf{A}_{\mathsf{V}} \, \times \, \mathsf{R}_{\mathsf{S}} \, \times \, (\mathsf{V}_{\mathsf{LED}} \, - \, \mathsf{V}_{\mathsf{IN}}) \times \, \mathsf{g}_{\mathsf{m}}}$$

The crossover frequency of the inner current loop is given by:

$$f_C = \frac{R_S}{V_{BAMP}} \times \frac{V_{LED}}{2 \times \pi \times L} \times 34.5 \times g_m \times R_{CF}$$

For adequate phase margin at crossover, place the zero formed by RCF and CCZ at least 3 to 5 times below the crossover frequency. The pole formed by RCF and CCP is added to eliminate noise spikes riding on the current waveform and is placed at the switching frequency.

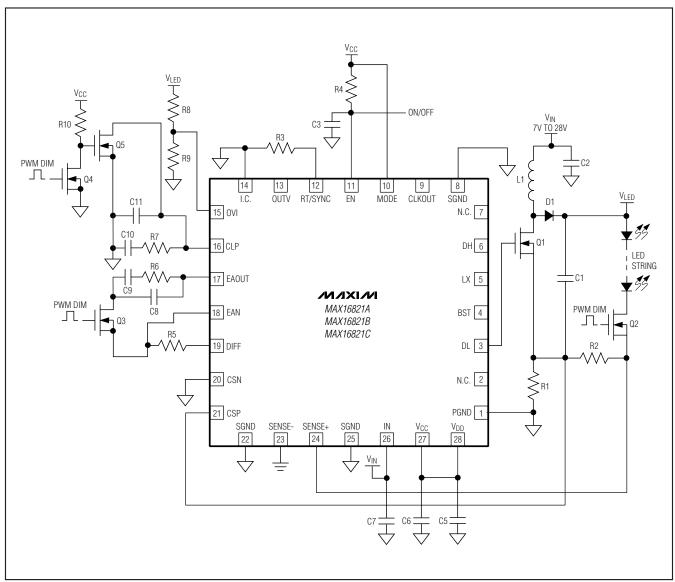

#### **PWM Dimming**

Even though the MAX16821A/MAX16821B/MAX16821 $\bar{C}$  do not have a separate PWM input, PWM dimming can be easily achieved by means of simple external circuitry. See Figures 10 and 11.

Figure 10. Low-Side Buck LED Driver with PWM Dimming (Patent Pending)

Figure 11. Boost LED Driver with PWM Dimming

#### **Power Dissipation**

Calculate power dissipation in the MAX16821A/ MAX16821B/MAX16821C as a product of the input voltage and the total VCC regulator output current (ICC). ICC includes quiescent current (IQ) and gate-drive current (IDD):

$$PD = VIN \times ICC$$

$$ICC = IQ + [fsw \times (QG1 + QG2)]$$

where  $Q_{G1}$  and  $Q_{G2}$  are the total gate charge of the low-side and high-side external MOSFETs at  $V_{GATE} = 5V$ ,  $I_{Q}$  is the supply current, and  $f_{SW}$  is the switching frequency of the LED driver.

Use the following equation to calculate the maximum power dissipation ( $P_{DMAX}$ ) in the chip at a given ambient temperature ( $T_A$ ):

$$P_{DMAX} = 34.5 \times (150 - T_A) \text{ mW}$$

#### **PCB** Layout

Use the following guidelines to layout the LED driver.

- 1) Place the IN, VCC, and VDD bypass capacitors close to the MAX16821A/MAX16821B/MAX16821C.

- 2) Minimize the area and length of the high-current switching loops.

- Place the necessary Schottky diodes that are connected across the switching MOSFETs very close to the respective MOSFET.

- 4) Use separate ground planes on different layers of the PCB for SGND and PGND. Connect both of these planes together at a single point and make this connection under the exposed pad of the MAX16821A/MAX16821B/MAX16821C.

- 5) Run the current-sense lines CSP and CSN very close to each other to minimize the loop area. Run the sense lines SENSE+ and SENSE- close to each other. Do not cross these critical signal lines with power circuitry. Sense the current right at the pads of the current-sense resistors. The current-sense signal has a maximum amplitude of 27.5mV. To prevent contamination of this signal from high dv/dt and high di/dt components and traces, use a ground plane layer to separate the power traces from this signal trace.

- 6) Place the bank of output capacitors close to the load.

- 7) Distribute the power components evenly across the board for proper heat dissipation.

- 8) Provide enough copper area at and around the switching MOSFETs, inductor, and sense resistors to aid in thermal dissipation.

- 9) Use 2oz or thicker copper to keep trace inductances and resistances to a minimum. Thicker copper conducts heat more effectively, thereby reducing thermal impedance. Thin copper PCBs compromise efficiency in applications involving high currents.

#### **Selector Guide**

| PART      | DIFFERENTIAL<br>SET VALUE<br>(VSENSE+ - VSENSE-)<br>(V) | DIFFERENTIAL<br>AMP GAIN<br>(V/V) |

|-----------|---------------------------------------------------------|-----------------------------------|

| MAX16821A | 0.60                                                    | 1                                 |

| MAX16821B | 0.10                                                    | 6                                 |

| MAX16821C | 0.03                                                    | 20                                |

### Pin Configuration

**Chip Information**

PROCESS: BICMOS

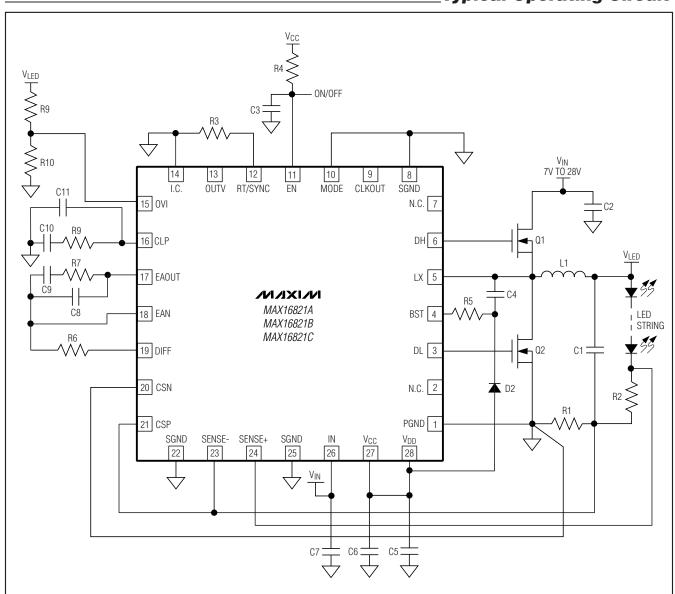

### **Typical Operating Circuit**

### Package Information

For the latest package outline information and land patterns, go to www.maxim-ic.com/packages

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO.   |

|--------------|--------------|----------------|

| 28 TQFN-EP   | T2855-8      | <u>21-0140</u> |

**Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                               | PAGES<br>CHANGED |

|--------------------|------------------|-------------------------------------------|------------------|

| 0                  | 7/07             | Initial release                           | _                |

| 1                  | 3/09             | Updated Electrical Characteristics table. | 3, 4             |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.