# **DAC1203D160**

Dual 12 bits DAC, up to 160 MHz, 2 x interpolating

Rev. 02 — 14 August 2008

**Product data sheet**

# 1. General description

The DAC1203D160 is optimized to reduce architecture complexity and overall system cost. The Digital-to-Analog Converter (DAC) leads dynamic performance in multi-carrier support, because of its direct IF conversion capabilities. With an internal sampling rate up to 160 MHz, the DAC1203D160 is an extremely competitive solution for broadband wireless systems transmitters, as well as a wide range of other applications.

# 2. Features

- Dual 12-bit resolution

- Spurious Free Dynamic Range (SFDR) = 80 dBc at 2.5 MHz

- Input data rate up to 80 MHz

- 2 × interpolation filter

- Output data rate up to 160 MHz

- Single 3.3 V power supply

- Low noise capacitor free integrated PLL

- Low power dissipation

- HTQFP80 package

- Ambient temperature from -40 °C to +85 °C

# 3. Applications

- Broadband wireless systems

- Digital radio links

- Cellular base stations

- Instrumentation

- Cable modems

- Cable Modem Termination System (CMTS)/Data Over Cable Service Interface Specification (DOCSIS)

# 4. Ordering information

Table 1. Ordering information

| Type number   | Package |                                                                                                 |          |

|---------------|---------|-------------------------------------------------------------------------------------------------|----------|

|               | Name    | Description                                                                                     | Version  |

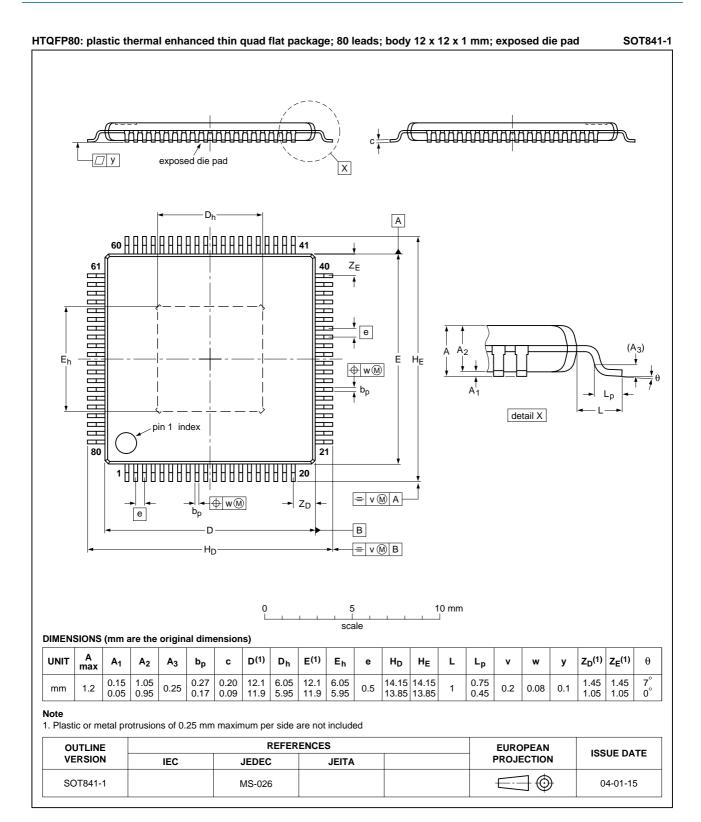

| DAC1203D160HW | HTQFP80 | plastic thermal enhanced thin quad flat package; 80 leads; body 12 × 12 × 1 mm; exposed die pad | SOT841-1 |

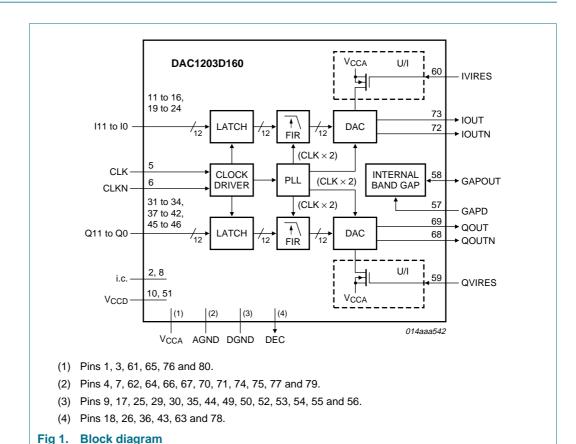

# 5. Block diagram

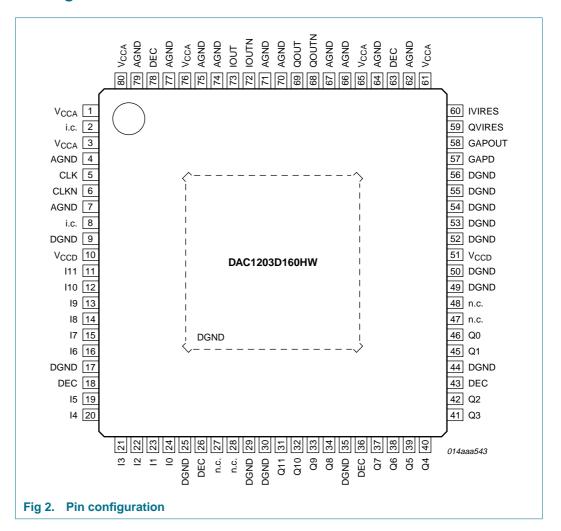

# 6. Pinning information

### 6.1 Pinning

### 6.2 Pin description

Table 2. Pin description

| Symbol    | Pin | Type[1] | Description                      |

|-----------|-----|---------|----------------------------------|

| $V_{CCA}$ | 1   | S       | analog supply voltage            |

| i.c.      | 2   | I/O     | internally connected; leave open |

| $V_{CCA}$ | 3   | S       | analog supply voltage            |

| AGND      | 4   | G       | analog ground                    |

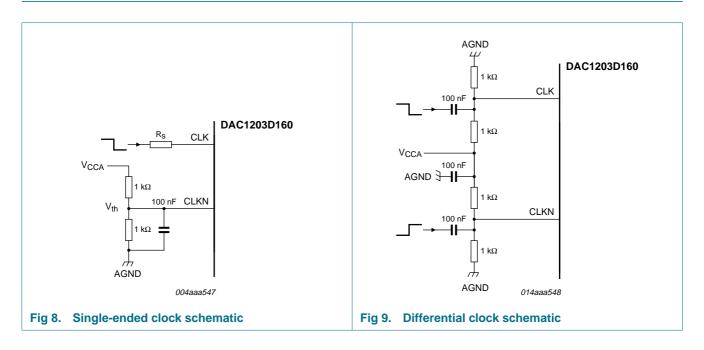

| CLK       | 5   | I       | clock input                      |

| CLKN      | 6   | I       | complementary clock input        |

| AGND      | 7   | G       | analog ground                    |

| i.c.      | 8   | 0       | internally connected; leave open |

| DGND      | 9   | G       | digital ground                   |

Table 2.

Pin description ...continued

| Table 2.   | Pin descripti |                     | ueu                                              |

|------------|---------------|---------------------|--------------------------------------------------|

| Symbol     | Pin           | Type <sup>[1]</sup> | Description                                      |

| $V_{CCD}$  | 10            | S                   | digital supply voltage                           |

| l11        | 11            | I                   | I data input bit 11 (Most Significant Bit (MSB)) |

| l10        | 12            | l                   | I data input bit 10                              |

| 19         | 13            | I                   | I data input bit 9                               |

| 18         | 14            | I                   | I data input bit 8                               |

| 17         | 15            | I                   | I data input bit 7                               |

| 16         | 16            | I                   | I data input bit 6                               |

| DGND       | 17            | G                   | digital ground                                   |

| DEC        | 18            | Ο                   | decoupling node                                  |

| 15         | 19            | I                   | I data input bit 5                               |

| 14         | 20            | I                   | I data input bit 4                               |

| 13         | 21            | I                   | I data input bit 3                               |

| 12         | 22            | I                   | I data input bit 2                               |

| <b>I</b> 1 | 23            | I                   | I data input bit 1                               |

| 10         | 24            | I                   | I data input bit 0 (Least Significant Bit (LSB)) |

| DGND       | 25            | G                   | digital ground                                   |

| DEC        | 26            | 0                   | decoupling node                                  |

| n.c.       | 27            | I                   | not connected                                    |

| n.c.       | 28            | I                   | not connected                                    |

| DGND       | 29            | G                   | digital ground                                   |

| DGND       | 30            | G                   | digital ground                                   |

| Q11        | 31            | I                   | Q data input bit 11 (MSB)                        |

| Q10        | 32            | I                   | Q data input bit 10                              |

| Q9         | 33            | I                   | Q data input bit 9                               |

| Q8         | 34            | I                   | Q data input bit 8                               |

| DGND       | 35            | G                   | digital ground                                   |

| DEC        | 36            | Ο                   | decoupling node                                  |

| Q7         | 37            | l                   | Q data input bit 7                               |

| Q6         | 38            | ı                   | Q data input bit 6                               |

| Q5         | 39            | ı                   | Q data input bit 5                               |

| Q4         | 40            | ı                   | Q data input bit 4                               |

| Q3         | 41            | ı                   | Q data input bit 3                               |

| Q2         | 42            | ı                   | Q data input bit 2                               |

| DEC        | 43            | 0                   | decoupling node                                  |

| DGND       | 44            | G                   | digital ground                                   |

| Q1         | 45            | l                   | Q data input bit 1                               |

| Q0         | 46            | l                   | Q data input bit 0 (LSB)                         |

| n.c.       | 47            | I                   | not connected                                    |

| n.c.       | 48            | I                   | not connected                                    |

| DGND       | 49            | G                   | digital ground                                   |

| DGND       | 50            | G                   | digital ground                                   |

Table 2.

Pin description ...continued

| Iddic 2.  | i ili acsori | ptioncomm | aca -                                 |

|-----------|--------------|-----------|---------------------------------------|

| Symbol    | Pin          | Type[1]   | Description                           |

| $V_{CCD}$ | 51           | S         | digital supply voltage                |

| DGND      | 52           | G         | digital ground                        |

| DGND      | 53           | G         | digital ground                        |

| DGND      | 54           | G         | digital ground                        |

| DGND      | 55           | G         | digital ground                        |

| DGND      | 56           | G         | digital ground                        |

| GAPD      | 57           | I         | internal band gap power disable input |

| GAPOUT    | 58           | I/O       | band gap output voltage               |

| QVIRES    | 59           | I         | Q DAC biasing resistor                |

| IVIRES    | 60           | I         | I DAC biasing resistor                |

| $V_{CCA}$ | 61           | S         | analog supply voltage                 |

| AGND      | 62           | G         | analog ground                         |

| DEC       | 63           | 0         | decoupling node                       |

| AGND      | 64           | G         | analog ground                         |

| $V_{CCA}$ | 65           | S         | analog supply voltage                 |

| AGND      | 66           | G         | analog ground                         |

| AGND      | 67           | G         | analog ground                         |

| QOUTN     | 68           | 0         | complementary Q DAC output current    |

| QOUT      | 69           | 0         | Q DAC output current                  |

| AGND      | 70           | G         | analog ground                         |

| AGND      | 71           | G         | analog ground                         |

| IOUTN     | 72           | 0         | complementary I DAC output current    |

| IOUT      | 73           | 0         | I DAC output current                  |

| AGND      | 74           | G         | analog ground                         |

| AGND      | 75           | G         | analog ground                         |

| $V_{CCA}$ | 76           | S         | analog supply voltage                 |

| AGND      | 77           | G         | analog ground                         |

| DEC       | 78           | 0         | decoupling node                       |

| AGND      | 79           | G         | analog ground                         |

| $V_{CCA}$ | 80           | S         | analog supply voltage                 |

|           |              |           |                                       |

<sup>[1]</sup> Type description: S: Supply; G: Ground; I: Input; O: Output.

# 7. Functional description

The DAC1203D160 is a segmented architecture composed of a 7-bit thermometer sub-DAC and the remaining 5-bit in a binary weighted sub-DAC.

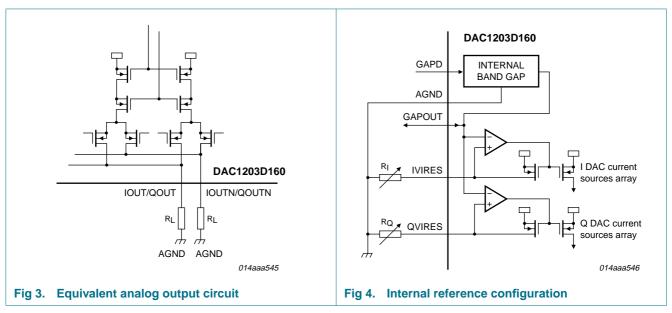

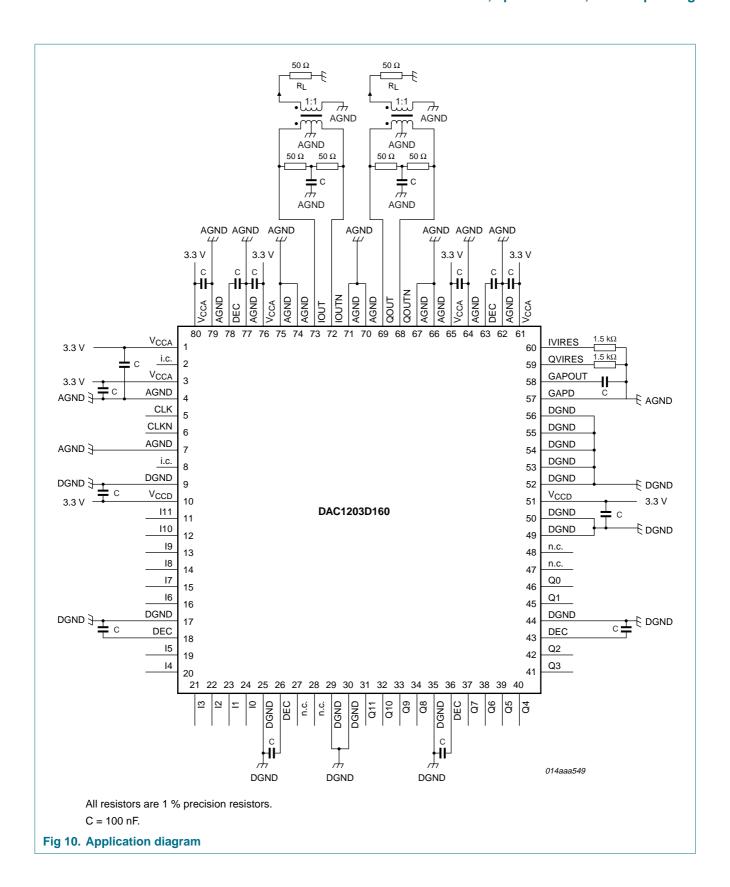

The device produces two complementary current outputs on both channels, respectively pins IOUT/IOUTN and QOUT/QOUTN which need to be connected via a load resistor to the ground.

<u>Figure 3</u> shows the equivalent analog output circuit of one DAC, which consists of a parallel combination of PMOS current sources and associated switches for each segment.

The cascode source configuration enables the increasing of the output impedance of the source and set to improve the dynamic performance of the DAC by introducing less distortion.

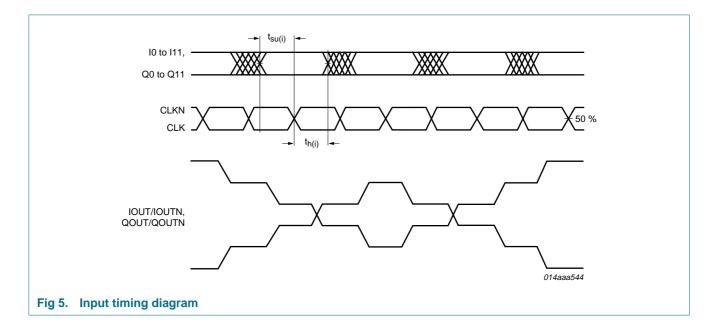

<u>Figure 4</u> shows the internal reference configuration. In this case the bias current is given by the output of the internal regulator connected to the inverting input of the internal operational amplifiers, while external resistors  $R_I$  and  $R_Q$  are connected respectively to pins IVIRES and QVIRES. Thus the output current of the two DACs is typically fixed to 20 mA with an appropriate choice of these resistors. This configuration is optimal for temperature drift compensation because the band gap can be matched with the voltage on the feedback resistors.

The relation between full-scale output current  $I_{O(fs)}$  and the  $R_I$  ( $R_Q$ ) is:

$$R_I = \frac{2048 \times V_{GAPOUT}}{82 \times I_{O(FS)}} \Omega$$

The output current can also be adjusted by imposing an external reference voltage to the inverting input pin GAPOUT and disabling the internal band gap with pin GAPD set to HIGH. At a voltage lower than 1.2 V the current can be set at values lower than 20 mA. The input references at pins IVIRES and QVIRES may also be driven by separate reference voltages to independently adjust the two DAC currents.

DAC1203D160\_2 © NXP B.V. 2008. All rights reserved.

# 8. Limiting values

Table 3. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

|                  |                           | 0 , ,                                                            | ,               |                        |      |

|------------------|---------------------------|------------------------------------------------------------------|-----------------|------------------------|------|

| Symbol           | Parameter                 | Conditions                                                       | Min             | Max                    | Unit |

| $V_{CCD}$        | digital supply voltage    |                                                                  | <u>[1]</u> –0.3 | +3.9                   | V    |

| $V_{CCA}$        | analog supply voltage     |                                                                  | <u>[1]</u> –0.3 | +3.9                   | V    |

| $\Delta V_{CC}$  | supply voltage difference | between the analog and digital supply voltages                   | -150            | +150                   | mV   |

| VI               | input voltage             | pins Qn and In referenced to DGND                                | -0.3            | V <sub>CCD</sub> + 0.3 | V    |

|                  |                           | pins IVIRES, QVIRES,<br>GAPD, CLK and CLKN<br>referenced to AGND | -0.3            | V <sub>CCA</sub> + 0.3 | V    |

| V <sub>O</sub>   | output voltage            | pins IOUT, IOUTN, QOUT<br>and QOUTN referenced to<br>AGND        | -0.3            | V <sub>CCA</sub> + 0.3 | V    |

| T <sub>stg</sub> | storage temperature       |                                                                  | -55             | +150                   | °C   |

| T <sub>amb</sub> | ambient temperature       |                                                                  | -40             | +85                    | °C   |

| Tj               | junction temperature      |                                                                  | -               | 125                    | °C   |

|                  |                           |                                                                  |                 |                        |      |

<sup>[1]</sup> All supplies are connected together.

## 9. Thermal characteristics

Table 4. Thermal characteristics

| Symbol               | Parameter                                   | Conditions  | Тур  | Unit |

|----------------------|---------------------------------------------|-------------|------|------|

| $R_{th(j-a)}$        | thermal resistance from junction to ambient | in free air | 27.1 | K/W  |

| R <sub>th(c-a)</sub> | thermal resistance from case to ambient     | in free air | 11.8 | K/W  |

## 10. Characteristics

#### Table 5. Characteristics

$V_{CCD} = V_{CCA} = 3.0 \text{ V}$  to 3.6 V; AGND and DGND connected together;  $T_{amb} = -40 \,^{\circ}\text{C}$  to +85  $^{\circ}\text{C}$ ; typical values measured at  $V_{CCD} = V_{CCA} = 3.3 \text{ V}$ ,  $I_{O(fs)} = 20 \text{ mA}$  and  $T_{amb} = 25 \,^{\circ}\text{C}$ ; dynamic parameters measured using output schematic given in Figure 10; unless otherwise specified.

| Symbol                | Parameter                            | Conditions                                                           |            | Min           | Тур  | Max            | Unit   |

|-----------------------|--------------------------------------|----------------------------------------------------------------------|------------|---------------|------|----------------|--------|

| Supplies              |                                      |                                                                      |            |               |      |                |        |

| V <sub>CCD</sub>      | digital supply voltage               |                                                                      |            | 3.0           | 3.3  | 3.6            | V      |

| $V_{CCA}$             | analog supply voltage                |                                                                      |            | 3.0           | 3.3  | 3.6            | V      |

| I <sub>CCD</sub>      | digital supply current               |                                                                      |            | -             | 55   | 65             | mA     |

| I <sub>CCA</sub>      | analog supply current                |                                                                      |            | -             | 73   | 85             | mA     |

| P <sub>tot</sub>      | total power dissipation              | $f_{clk} = 80 \text{ MHz};$<br>$f_{IOUT} = f_{QOUT} = 5 \text{ MHz}$ |            | -             | 422  | 540            | mW     |

| Clock inpu            | its (CLK and CLKN)                   |                                                                      |            |               |      |                |        |

| $V_{I(cm)}$           | common-mode input voltage            |                                                                      |            | -             | 1.65 | -              | V      |

| $\Delta V_{i(dif)}$   | differential input voltage variation |                                                                      |            | -             | 1.0  | -              | V      |

| Analog ou             | tputs (IOUT, IOUTN, QOUT             | and QOUTN)                                                           |            |               |      |                |        |

| I <sub>O(fs)</sub>    | full-scale output current            | differential outputs                                                 |            | 4             | -    | 20             | mA     |

| R <sub>o</sub>        | output resistance                    |                                                                      | <u>[1]</u> | -             | 150  | -              | kΩ     |

| C <sub>o</sub>        | output capacitance                   |                                                                      | <u>[1]</u> | -             | 3    | -              | pF     |

| Digital inp           | uts (I0 to I11, Q0 to Q11 ar         | nd GAPD)                                                             |            |               |      |                |        |

| V <sub>IL</sub>       | LOW-level input voltage              |                                                                      |            | DGND          | -    | $0.3\ V_{CCD}$ | V      |

| V <sub>IH</sub>       | HIGH-level input voltage             |                                                                      |            | $0.7 V_{CCD}$ | -    | $V_{CCD}$      | V      |

| I <sub>IL</sub>       | LOW-level input current              | $V_{IL} = 0.3 V_{CCD}$                                               |            | -             | 5    | -              | μΑ     |

| l <sub>IH</sub>       | HIGH-level input current             | $V_{IH} = 0.7 V_{CCD}$                                               |            | -             | 5    | -              | μΑ     |

| Reference             | voltage output (GAPOUT)              |                                                                      |            |               |      |                |        |

| $V_{GAPOUT}$          | voltage on pin GAPOUT                |                                                                      |            | -             | 1.31 | -              | V      |

| I <sub>GAPOUT</sub>   | current on pin GAPOUT                | external voltage                                                     |            | -             | 1    | -              | μΑ     |

| $\Delta V_{GAPOUT}$   | voltage variation on pin GAPOUT      |                                                                      |            | -             | ±133 | -              | ppm/°C |

| Clock timi            | ng inputs (CLK and CLKN              | )                                                                    |            |               |      |                |        |

| f <sub>clk</sub>      | clock frequency                      |                                                                      |            | -             | -    | 80             | MHz    |

| t <sub>w(clk)H</sub>  | HIGH clock pulse width               |                                                                      |            | 5             | -    | -              | ns     |

| t <sub>w(clk)</sub> L | LOW clock pulse width                |                                                                      |            | 5             | -    | -              | ns     |

| nput timir            | ng (I0 to I11 and Q0 to Q11          | ); see <u>Figure 5</u>                                               |            |               |      |                |        |

| t <sub>h(i)</sub>     | input hold time                      |                                                                      |            | 1.1           | -    | 3.4            | ns     |

| t <sub>su(i)</sub>    | input set-up time                    |                                                                      |            | -1.5          | -    | +0.7           | ns     |

| Output tim            | ing (IOUT, IOUTN, QOUT a             | and QOUTN)                                                           |            |               |      |                |        |

| s                     | settling time                        | to ±0.5 LSB                                                          | <u>[1]</u> | -             | 40   | -              | ns     |

Table 5.

Characteristics ...continued

$V_{CCD} = V_{CCA} = 3.0 \text{ V}$  to 3.6 V; AGND and DGND connected together;  $T_{amb} = -40 \,^{\circ}\text{C}$  to +85  $^{\circ}\text{C}$ ; typical values measured at  $V_{CCD} = V_{CCA} = 3.3 \text{ V}$ ,  $I_{O(fs)} = 20 \text{ mA}$  and  $T_{amb} = 25 \,^{\circ}\text{C}$ ; dynamic parameters measured using output schematic given in Figure 10; unless otherwise specified.

| Symbol                       | Parameter                               | Conditions                                                                                    | Min     | Тур                 | Max  | Unit   |

|------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------|---------|---------------------|------|--------|

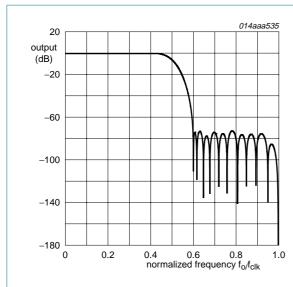

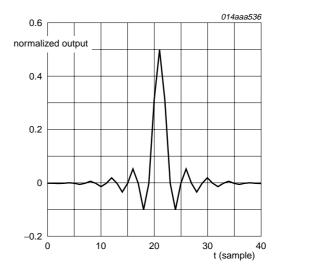

| Digital filt                 | er specification (FIR); Orde            | er N = 42; see <u>Figure 6</u> and <u>7</u> and <u>1</u>                                      | Table 7 |                     |      |        |

| f <sub>data</sub>            | data rate                               |                                                                                               | -       | -                   | 80   | MHz    |

| $\alpha_{\text{ripple(pb)}}$ | pass-band ripple                        | f <sub>data</sub> /f <sub>clk</sub> ; 0.005 dB attenuation                                    | -       | 0.405               | -    | MHz    |

|                              |                                         | f <sub>data</sub> /f <sub>clk</sub> ; 3 dB attenuation                                        | -       | 0.479               | -    | MHz    |

| $\alpha_{\text{stpb}}$       | stop-band attenuation                   | $f_{data}/f_{clk} = 0.6 \text{ to } 1$                                                        | -       | 69                  | -    | dB     |

| t <sub>d(grp)</sub>          | group delay time                        |                                                                                               | -       | 11 T <sub>clk</sub> | -    | ns     |

| Analog si                    | gnal processing                         |                                                                                               |         |                     |      |        |

| Linearity                    |                                         |                                                                                               |         |                     |      |        |

| INL                          | integral non-linearity                  |                                                                                               | -       | ±0.75               | -    | LSB    |

| DNL                          | differential non-linearity              |                                                                                               | -       | ±0.4                | -    | LSB    |

| I <sub>n(o)</sub>            | output noise current                    |                                                                                               | -       | 120                 | -    | pA/√Hz |

| E <sub>offset</sub>          | offset error                            | relative to full scale                                                                        | -       | -0.3                | -    | %      |

| E <sub>G</sub>               | gain error                              | relative to full scale                                                                        | -5.4    | -                   | +5.4 | %      |

| $\Delta G_{IQ}$              | IQ gain mismatch                        | between I and Q, relative to full scale                                                       | -       | ±0.2                | -    | %      |

| Spurious f                   | ree dynamic range                       |                                                                                               |         |                     |      |        |

| SFDR                         | spurious free dynamic                   | f <sub>clk</sub> = 80 MHz; B = Nyquist                                                        |         |                     |      |        |

|                              | range                                   | f <sub>o</sub> = 2.5 MHz at 0 dBFS                                                            | -       | 80                  | -    | dBc    |

|                              |                                         | f <sub>o</sub> = 5 MHz at 0 dBFS                                                              | -       | 72                  | -    | dBc    |

|                              |                                         | f <sub>o</sub> = 13 MHz at 0 dBFS                                                             | -       | 64                  | -    | dBc    |

| Harmonic                     | 3                                       |                                                                                               |         |                     |      |        |

| $\alpha_{2H}$                | second harmonic level                   | f <sub>o</sub> = 5 MHz                                                                        | -       | 73                  | -    | dBc    |

|                              |                                         | f <sub>o</sub> = 13 MHz                                                                       | -       | 65                  | -    | dBc    |

| αзн                          | third harmonic level                    | f <sub>o</sub> = 5 MHz                                                                        | -       | 88                  | -    | dBc    |

|                              |                                         | f <sub>o</sub> = 13 MHz                                                                       | -       | 86                  | -    | dBc    |

| THD                          | total harmonic distortion               | $f_{clk} = 80 \text{ MHz}; B = Nyquist; T_{amb} =$                                            | 25 °C   |                     |      |        |

|                              |                                         | f <sub>o</sub> = 2.5 MHz                                                                      | -       | 75                  | -    | dBc    |

|                              |                                         | f <sub>o</sub> = 5 MHz                                                                        | 68      | 71                  | -    | dBc    |

| Two-tone i                   | intermodulation                         |                                                                                               |         |                     |      |        |

| IMD2                         | second-order intermodulation distortion | $f_{clk} = 80 \text{ MHZ}; f_0 1 = 10 \text{ MHz};$<br>$f_0 2 = 12 \text{ MHz}; B = Nyquist;$ | -       | 65                  | -    | dBc    |

| IMD3                         | third-order intermodulation distortion  | $f_{clk} = 80 \text{ MHz}; f_0 1 = 10 \text{ MHz};$<br>$f_0 2 = 12 \text{ MHz}$               | -       | 84                  | -    | dBc    |

Table 5.

Characteristics ...continued

$V_{CCD} = V_{CCA} = 3.0 \text{ V}$  to 3.6 V; AGND and DGND connected together;  $T_{amb} = -40 \,^{\circ}\text{C}$  to +85  $^{\circ}\text{C}$ ; typical values measured at  $V_{CCD} = V_{CCA} = 3.3 \text{ V}$ ,  $I_{O(fs)} = 20 \text{ mA}$  and  $T_{amb} = 25 \,^{\circ}\text{C}$ ; dynamic parameters measured using output schematic given in Figure 10; unless otherwise specified.

| Symbol     | Parameter               | Conditions                             | Min            | Тур  | Max    | Unit   |

|------------|-------------------------|----------------------------------------|----------------|------|--------|--------|

| Signal-to- | noise ratio             |                                        |                |      |        |        |

| NSD        | noise spectral density  | f <sub>clk</sub> = 80 MHz              |                |      |        |        |

|            | $f_o = 2.5 \text{ MHz}$ | -                                      | -155           | -    | dBm/Hz |        |

|            | f <sub>o</sub> = 5 MHz  | -                                      | -155           | -    | dBm/Hz |        |

|            |                         | f <sub>o</sub> = 19 MHz                | -              | -153 | -      | dBm/Hz |

| S/N        | signal-to-noise ratio   | f <sub>clk</sub> = 80 MHz; B = Nyquist |                |      |        |        |

|            |                         | $f_0 = 2.5 \text{ MHz}$                | -              | 80   | -      | dBc    |

|            | f <sub>o</sub> = 5 MHz  | 70                                     | 80             | -    | dBc    |        |

|            |                         | f <sub>o</sub> = 19 MHz                | -              | 78   | -      | dBc    |

| ACPR       | adjacent channel power  | baseband; 5 MHz channel spacir         | ng; B = 3.84 N | 1Hz  |        |        |

| ratio      | ratio                   | $f_0 = 2.5 \text{ MHz}$                | -              | 68   | -      | dBc    |

|            |                         | f <sub>o</sub> = 20 MHz                | -              | 70   | -      | dBc    |

#### [1] Guaranteed by design.

Table 6. Band gap

| Band gap disable (GAPD) | Band gap input/output (GAPOUT)          | Internal band gap |

|-------------------------|-----------------------------------------|-------------------|

| LOW                     | output ( $V_{GAPOUT} = 1.2 \text{ V}$ ) | enable            |

| HIGH                    | input                                   | disable           |

Fig 6. FIR filter frequency response

Fig 7. FIR filter impulse response

Table 7. Interpolation FIR filter coefficient

| Coefficient | Coefficient | Value |

|-------------|-------------|-------|

| H(1)        | H(43)       | 10    |

| H(2)        | H(42)       | 0     |

| H(3)        | H(41)       | -31   |

| H(4)        | H(40)       | 0     |

| H(5)        | H(39)       | 69    |

| H(6)        | H(38)       | 0     |

| H(7)        | H(37)       | -138  |

| H(8)        | H(36)       | 0     |

| H(9)        | H(35)       | 248   |

| H(10)       | H(34)       | 0     |

| H(11)       | H(33)       | -419  |

| H(12)       | H(32)       | 0     |

| H(13)       | H(31)       | 678   |

| H(14)       | H(30)       | 0     |

| H(15)       | H(29)       | -1083 |

| H(16)       | H(28)       | 0     |

| H(17)       | H(27)       | 1776  |

| H(18)       | H(26)       | 0     |

| H(19)       | H(25)       | -3282 |

| H(20)       | H(24)       | 0     |

| H(21)       | H(23)       | 10364 |

| H(22)       | -           | 16384 |

# 11. Application information

# 11.1 Alternative parts

The following alternative parts are also available:

Table 8. Alternative parts

| Type number | Description      |            | Sampling frequency                |

|-------------|------------------|------------|-----------------------------------|

| DAC1403D160 | Dual 14 bits DAC | <u>[1]</u> | 160 MHz; $2 \times$ interpolating |

| DAC1003D160 | Dual 10 bits DAC | <u>[1]</u> | 160 MHz; 2 × interpolating        |

<sup>[1]</sup> Pin to pin compatible

# 12. Package outline

Fig 11. Package outline SOT841-1 (HTQFP80)

DAC1203D160\_2 © NXP B.V. 2008. All rights reserved.

#### 13. Abbreviations

Table 9. Abbreviations

| Acronym | Description                        |

|---------|------------------------------------|

| FIR     | Finite Impulse Response            |

| IF      | Intermediate Frequency             |

| LSB     | Least Significant Bit              |

| MSB     | Most Significant Bit               |

| PLL     | Phase-Locked Loop                  |

| PMOS    | Positive-Metal Oxide Semiconductor |

# 14. Glossary

### 14.1 Static parameters

**DNL** — Differential Non-Linearity. The difference between the ideal and the measured output value between successive DAC codes.

**INL** — Integral Non-Linearity. The deviation of the transfer function from a best-fit straight line (linear regression computation).

## 14.2 Dynamic parameters

**IMD2** — Second-order intermodulation distortion. From a dual-tone digital input sine wave (these two frequencies are close together), the intermodulation distortion product IMD2 is the ratio of the RMS value of either tone and the RMS value of the worst 2nd-order intermodulation product.

**IMD3** — Third-order intermodulation distortion. From a dual-tone digital input sine wave (these two frequencies are close together), the intermodulation distortion product IMD3 is the ratio of the RMS value of either tone and the RMS value of the worst 3rd-order intermodulation product.

**SFDR** — Spurious Free Dynamic Range. The ratio between the RMS value of the reconstructed output sine wave and the RMS value of the largest spurious observed (harmonic and non-harmonic, excluding DC component) in the frequency domain.

**S/N** — Signal-to-Noise ratio. The ratio of the RMS value of the reconstructed output sine wave to the RMS value of the noise excluding the harmonics and the DC component.

**THD** — Total Harmonic Distortion. The ratio of the RMS value of the harmonics of the output frequency to the RMS value of the output sine wave. Usually, the calculation of THD is done on the first 5 harmonics.

**DAC1203D160**

Dual 12 bits DAC, up to 160 MHz, 2 x interpolating

# 15. Revision history

### Table 10. Revision history

| Document ID    | Release date                                                             | Data sheet status  | Change notice | Supersedes    |  |

|----------------|--------------------------------------------------------------------------|--------------------|---------------|---------------|--|

| DAC1203D160_2  | 20080814                                                                 | Product data sheet | -             | DAC1203D160_1 |  |

| Modifications: | <ul> <li>Corrections to values in <u>Figure 1</u>.</li> </ul>            |                    |               |               |  |

|                | <ul> <li>Addition to description of row Q0 in <u>Table 2</u>.</li> </ul> |                    |               |               |  |

|                | <ul> <li>Corrections to row sequence in <u>Table 5</u>.</li> </ul>       |                    |               |               |  |

|                | <ul> <li>Corrections to n.c pins in <u>Figure 10</u>.</li> </ul>         |                    |               |               |  |

| DAC1203D160_1  | 20080613                                                                 | Product data sheet | -             | -             |  |

|                |                                                                          |                    |               |               |  |

# 16. Legal information

#### 16.1 Data sheet status

| Document status[1][2]          | Product status[3] | Definition                                                                            |

|--------------------------------|-------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet   | Development       | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet | Qualification     | This document contains data from the preliminary specification.                       |

| Product [short] data sheet     | Production        | This document contains the product specification.                                     |

- [1] Please consult the most recently issued document before initiating or completing a design.

- [2] The term 'short data sheet' is explained in section "Definitions"

- [3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL http://www.nxp.com.

#### 16.2 Definitions

Draft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

#### 16.3 Disclaimers

**General** — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

**Suitability for use** — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or

malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) may cause permanent damage to the device. Limiting values are stress ratings only and operation of the device at these or any other conditions above those given in the Characteristics sections of this document is not implied. Exposure to limiting values for extended periods may affect device reliability.

Terms and conditions of sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at <a href="http://www.nxp.com/profile/terms">http://www.nxp.com/profile/terms</a>, including those pertaining to warranty, intellectual property rights infringement and limitation of liability, unless explicitly otherwise agreed to in writing by NXP Semiconductors. In case of any inconsistency or conflict between information in this document and such terms and conditions, the latter will prevail.

**No offer to sell or license** — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

#### 16.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

#### 17. Contact information

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: <a href="mailto:salesaddresses@nxp.com">salesaddresses@nxp.com</a>

## 18. Contents

| 1    | General description        |

|------|----------------------------|

| 2    | Features                   |

| 3    | Applications               |

| 4    | Ordering information       |

| 5    | Block diagram 2            |

| 6    | Pinning information        |

| 6.1  | Pinning                    |

| 6.2  | Pin description            |

| 7    | Functional description 6   |

| 8    | Limiting values 7          |

| 9    | Thermal characteristics 7  |

| 10   | Characteristics 8          |

| 11   | Application information 12 |

| 11.1 | Alternative parts          |

| 12   | Package outline 15         |

| 13   | Abbreviations              |

| 14   | Glossary                   |

| 14.1 | Static parameters          |

| 14.2 | Dynamic parameters         |

| 15   | Revision history 17        |

| 16   | Legal information          |

| 16.1 | Data sheet status          |

| 16.2 | Definitions                |

| 16.3 | Disclaimers                |

| 16.4 | Trademarks18               |

| 17   | Contact information 18     |

| 18   | Contents 19                |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.