#### **General Description**

The MAX8900\_ is a high-frequency, switch-mode charger for a 1-cell lithium ion (Li+) or lithium polymer (Li-Poly) battery. It delivers up to 1.2A of current to the battery from 3.4V to 6.3V (MAX8900A) or 3.4V to 8.7V (MAX8900B). The 3.25MHz switch-mode charger is ideally suited to small portable devices such as headsets and ultra-portable media players because it minimizes component size and heat.

Several features make the MAX8900\_ perfect for highreliability systems. The MAX8900\_ is protected against input voltages as high as +22V and as low as -22V. Battery protection features include low voltage prequalification, charge fault timer, die temperature monitoring, and battery temperature monitoring. The battery temperature monitoring adjusts the charge current and termination voltage as described in the JEITA\* specification for safe use of secondary lithium-ion batteries.

Charge parameters are easily adjustable with external components. An external resistance adjusts the charge current from 50mA to 1200mA. Another external resistance adjusts the prequalification and done current thresholds from 10mA to 200mA. The done current threshold is very accurate achieving ±1mA at the 10mA level. The charge timer is adjustable with an external capacitor.

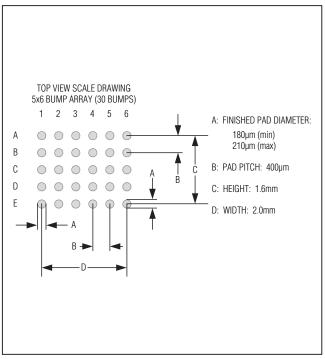

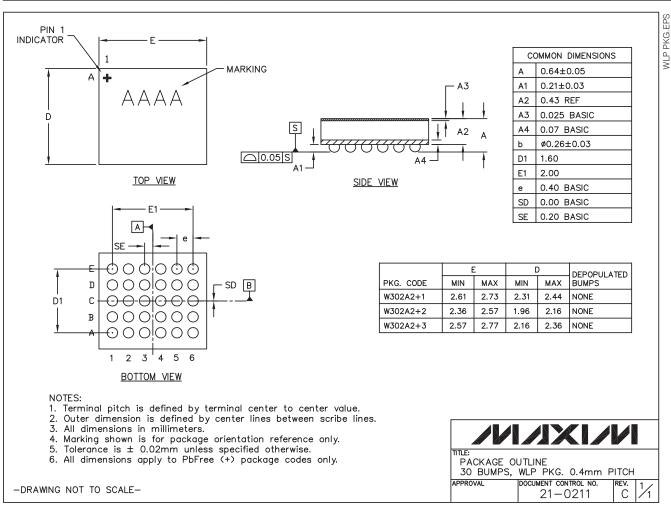

The MAX8900\_ is available in a 0.4mm pitch, 2.44mm x 2.67mm x 0.64mm WLP package.

### **Applications**

| USB Charging       | Digital Cameras |

|--------------------|-----------------|

| Headsets and Media | GPS, PND        |

| Players            | eBook           |

| Smartphones        |                 |

### **Ordering Information**

| PART          | TEMP<br>RANGE     | PIN-<br>PACKAGE | OPTIONS                                                              |

|---------------|-------------------|-----------------|----------------------------------------------------------------------|

| MAX8900AEWV+T | -40°C to<br>+85°C | 30 WLP          | V <sub>OVLO</sub> = 6.5V<br>T1 = 0°C<br>2-pin status<br>indicators   |

| MAX8900BEWV+T | -40°C to<br>+85°C | 30 WLP          | V <sub>OVLO</sub> = 9.0V<br>T1 = -15°C<br>3-pin status<br>indicators |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package. T = Tape and reel.

Ordering Information continued at end of data sheet.

#### **Features**

- ♦ 3.25MHz Switching Li+/Li-Poly Battery Charger

- ◆ JEITA Battery Temperature Monitor Adjusts Charge Current and Termination Voltage

- ◆ 4.2V ±0.5% Battery Regulation Voltage (Alternate 4.1V Target Available on Request)

- ◆ Adjustable Done Current Threshold Adjustable from 10mA to 200mA ±1mA Accuracy at 10mA

- ♦ High-Efficiency and Low Heat

- ♦ Uses a 2.0mm x 1.6mm Inductor

- Positive and Negative Input Voltage Protection (±22V)

- ♦ Up to +20V Operating Range (Alternate OVLO Ranges Available on Request)

- ♦ Supports No-Battery Operation

- **♦ Fault Timer**

- ♦ Charge Status Outputs

- ♦ 2.44mm x 2.67mm x 0.64mm Package

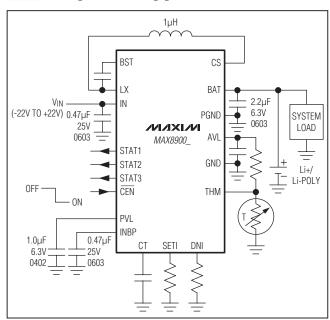

### Simplified Applications Circuit

\*JEITA (Japan Electronics and Information Technology Industries Association) standard, "A Guide to the Safe Use of Secondary Lithium Ion Batteries in Notebook-type Personal Computers" April 20, 2007.

Maxim Integrated Products 1

| TABLE OF CONTENTS                                             |    |

|---------------------------------------------------------------|----|

| Absolute Maximum Ratings                                      | 4  |

| Electrical Characteristics                                    | 4  |

| Typical Operating Characteristics                             | 8  |

| Pin Configuration                                             | 13 |

| Pin Description                                               | 13 |

| Detailed Description                                          | 17 |

| Control Scheme                                                | 17 |

| Soft-Start                                                    | 17 |

| Setting the Fast-Charge Current (SETI)                        | 17 |

| Setting the Prequalification Current and Done Threshold (DNI) | 18 |

| Charge Enable Input (CEN)                                     | 18 |

| Charger States                                                | 19 |

| Charger Disabled State                                        |    |

| Dead-Battery State                                            |    |

| Dead Battery + Prequalification State                         |    |

| Prequalification State                                        |    |

| Fast-Charge Constant Current State                            |    |

| Fast-Charge Constant Voltage State                            |    |

| Top-Off State                                                 |    |

| Done State                                                    | 23 |

| Timer Fault State                                             | 23 |

| Battery Hot/Cold State                                        | 23 |

| V <sub>IN</sub> Too High State                                | 23 |

| Charge Timer (CT)                                             | 23 |

| Thermal Management                                            | 23 |

| Thermistor Monitor (THM)                                      | 24 |

| Thermal Foldback                                              | 26 |

| Thermal Shutdown                                              | 26 |

| PVL and AVL Regulator                                         | 27 |

| Charge Status Outputs (3 Pin)                                 | 27 |

| Charge Status Outputs (2 Pin + > T4)                          | 27 |

| Inductor Selection                                            | 28 |

| BAT Capacitor                                                 | 29 |

| INBP Capacitor                                                | 29 |

| Other Capacitors                                              |    |

| Applications Information                                      | 30 |

| Dynamic Charge Current Programming                            |    |

| No-Battery Operation                                          | 30 |

| TABLE OF CONTENTS (continued)                                                                                                                        |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------|----|

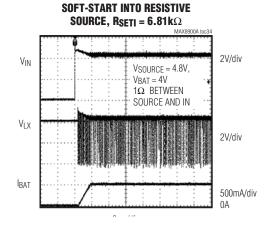

| Charge-Source Issues                                                                                                                                 | 30 |

| Charge-Source Impedance                                                                                                                              |    |

| Inductive Kick                                                                                                                                       |    |

| Overvoltage and Reverse Voltage Protection                                                                                                           | 31 |

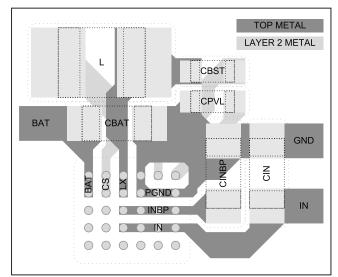

| PCB Layout                                                                                                                                           | 31 |

| Chip Information                                                                                                                                     | 33 |

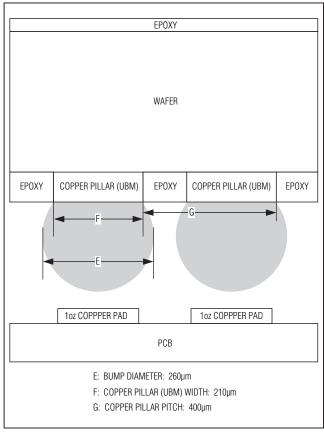

| Package Information                                                                                                                                  | 34 |

| Revision History                                                                                                                                     | 35 |

| LIST OF FIGURES                                                                                                                                      |    |

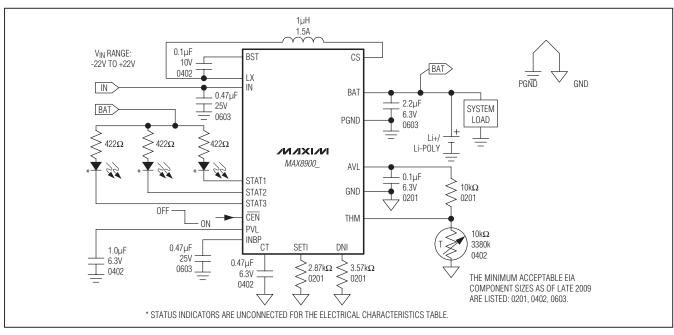

| Figure 1. Applications Circuit: Single SETI Resistor, Status Indicators Connected to LEDs                                                            | 15 |

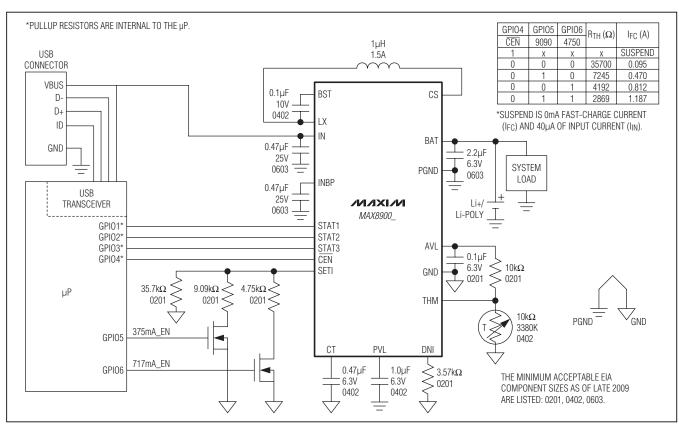

| Figure 2. Applications Circuit: Multiple Charge Rates Managed by µP to Be USB Compliant, Status Indicators                                           |    |

| Connected to a µP                                                                                                                                    |    |

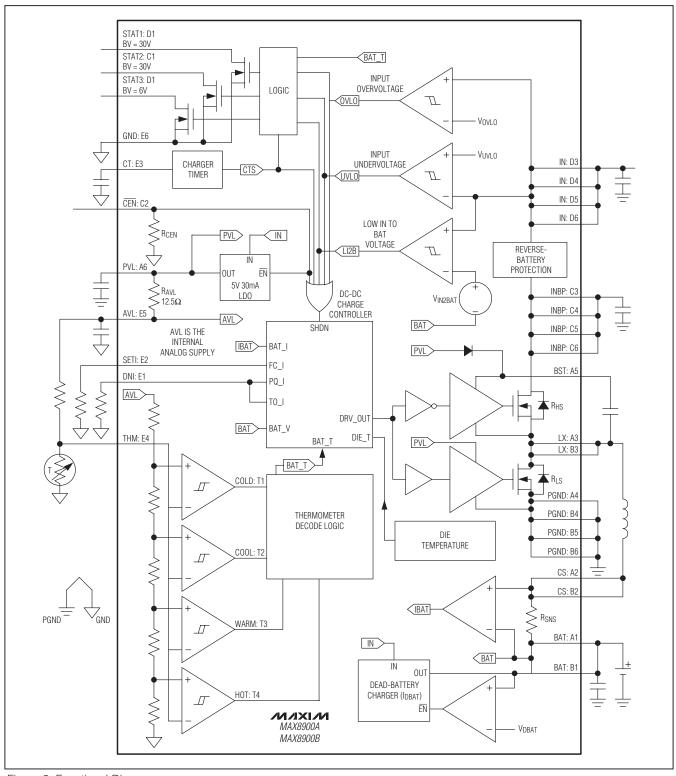

| Figure 3. Functional Diagram                                                                                                                         |    |

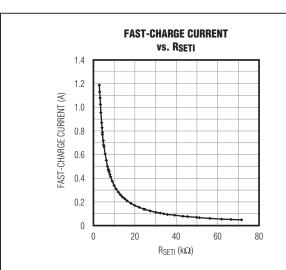

| Figure 4. Fast-Charge Current vs. R <sub>SETI</sub> ( <u>www.maxim-ic.com/tools/other/software/MAX8900-RSETI.XLS</u> ).                              | 18 |

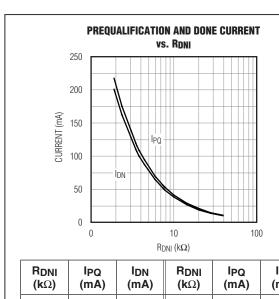

| Figure 5. Prequalification Current and Done Threshold vs. R <sub>DNI</sub> ( <u>www.maxim-ic.com/tools/other/software/</u> <u>MAX8900-DNI.XLS</u> ). | 1Ω |

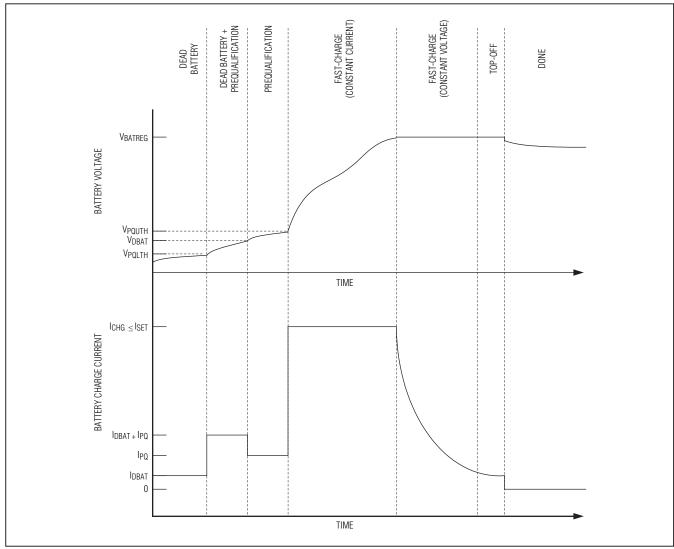

| Figure 6. Li+/Li-Poly Charge Profile                                                                                                                 |    |

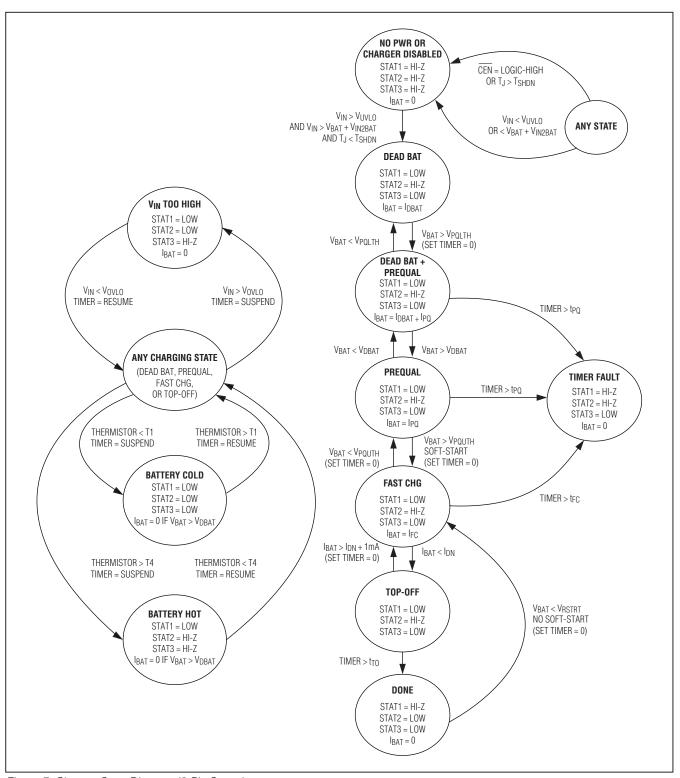

| Figure 7. Charger State Diagram (3-Pin Status)                                                                                                       |    |

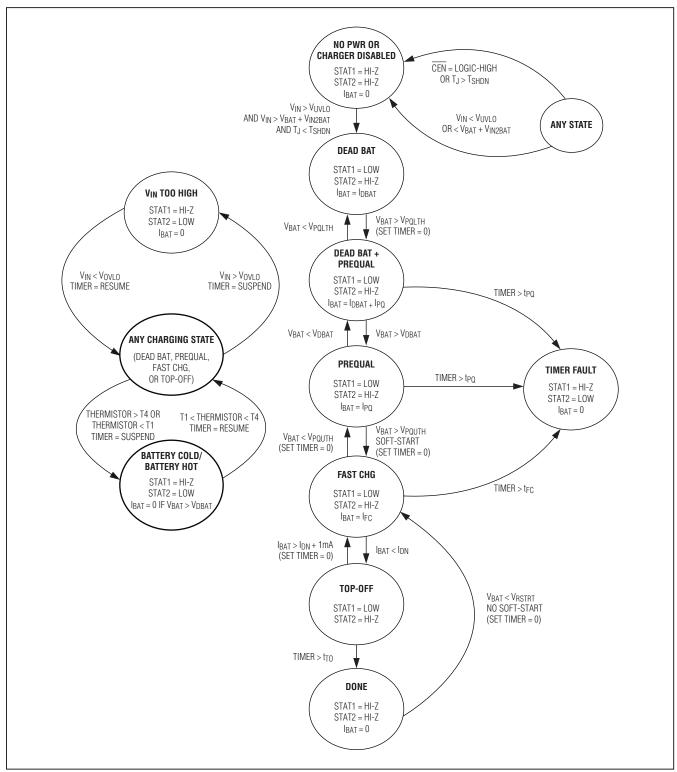

| Figure 8. Charger State Diagram (2-Pin Status)                                                                                                       |    |

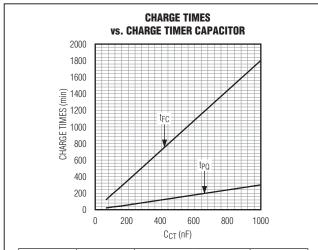

| Figure 9. Charge Times vs. Cct.                                                                                                                      |    |

| Figure 10. JEITA Battery Safety Regions                                                                                                              |    |

| Figure 11. Thermistor Monitor Detail.                                                                                                                |    |

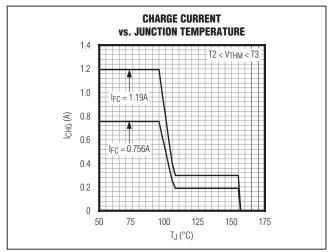

| Figure 12. Charge Current vs. Junction Temperature                                                                                                   |    |

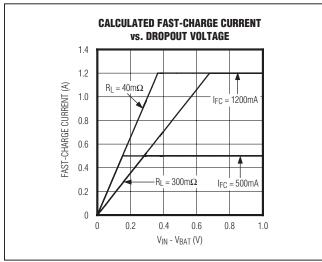

| Figure 13. Calculated Fast-Charge Current vs. Dropout Voltage                                                                                        |    |

| Figure 14. Power PCB Layout Example                                                                                                                  |    |

| Figure 15. Recommended Land Pattern                                                                                                                  |    |

| Figure 16. Bump Cross Section and Copper Pillar Detail                                                                                               | 33 |

| LIST OF TABLES                                                                                                                                       |    |

| Table 1. 2.44mm x 2.67mm x 0.64mm, 0.4mm Pitch WLP Thermal Characteristics                                                                           | 24 |

| Table 2. Trip Temperatures for Different Thermistors                                                                                                 | 25 |

| Table 3. 3-Pin Status Output Truth Table                                                                                                             | 27 |

| Table 4. 2-Pin Status Output Truth Table                                                                                                             | 27 |

| Table 5. Recommended Inductor Selection                                                                                                              | 28 |

| Table 6. Recommended Inductor                                                                                                                        | 28 |

|                                                                                                                                                      |    |

#### **ABSOLUTE MAXIMUM RATINGS**

| IN to PGND                  | 22V to +22V                  |

|-----------------------------|------------------------------|

| INBP to PGND                |                              |

| IN to INBP                  | 30V to +1.2V                 |

| STAT1, STAT2 to GND         | 0.3V to +30V                 |

| BST to PGND                 | 0.3V to +36V                 |

| BST to LX                   | 0.3V to +6.0V                |

| BST to PVL                  | 0.3V to +30V                 |

| PVL, BAT, CS to PGND        | 0.3V to +6.0V                |

| AVL, STAT3, CEN, THM to GND |                              |

| PVL to AVL                  |                              |

| CT to GND                   | 0.3V to (AVL + 0.3V)         |

| SETI, DNI to GND            | $0.3V$ to $(V_{BAT} + 0.3V)$ |

| PGND to GND                                           | 0.3V to +0.3V       |

|-------------------------------------------------------|---------------------|

| IN Continuous Current                                 | 2.4ARMS             |

| LX Continuous Current (Note 1)                        | 1.6A <sub>RMS</sub> |

| CS Continuous Current                                 | 1.3ARMS             |

| BAT Continuous Current                                | 1.3ARMS             |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) |                     |

| 30-Bump WLP (derate 20.4mW/°C above +7                | ,                   |

| Operating Temperature Range                           | 40°C to +85°C       |

| Junction Temperature                                  |                     |

| Storage Temperature Range                             |                     |

| Soldering Temperture (reflow)                         | +260°C              |

Note 1: LX has an internal clamp diode to PGND and INBP. Applications that forward bias these diodes should take care not to exceed the power dissipation limits of the device.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{IN}=6V,\,V_{BAT}=4V,\,R_{SETI}=2.87k\Omega,\,R_{DNI}=3.57k\Omega,\,V_{THM}=V_{AVL/2},\,circuit\,of\,Figure\,1,\,T_{A}=-40^{\circ}C\,to\,+85^{\circ}C,\,unless\,otherwise\,noted.\,Typical\,values\,are\,at\,T_{A}=+25^{\circ}C.)\,(Note\,2)$

| PARAMETER                       | SYMBOL                        |                                                                                                                                                                      | CONE                                                           | DITIONS                | MIN  | TYP   | MAX  | UNITS |  |

|---------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------------------------|------|-------|------|-------|--|

| GENERAL                         | 1                             |                                                                                                                                                                      |                                                                |                        |      |       |      |       |  |

|                                 |                               | Withstand v                                                                                                                                                          | oltage/                                                        |                        | -20  |       | +20  | V     |  |

| IN Input Voltage Range (Note 3) | VIN                           | Operation                                                                                                                                                            | , alta a a                                                     | MAX8900B               | 3.4  |       | 8.7  | V     |  |

|                                 |                               | Operating                                                                                                                                                            | voltage                                                        | MAX8900A               | 3.4  |       | 6.3  | ]     |  |

| IN Undervoltage Threshold       | Vuvlo                         | V <sub>IN</sub> falling,                                                                                                                                             | 400mV hy                                                       | steresis (Note 4)      | 3.1  | 3.2   | 3.3  | V     |  |

| IN to BAT Shutdown Threshold    | VIN2BAT                       | When charged hysteresis                                                                                                                                              | When charging stops, V <sub>IN</sub> falling, 200mV hysteresis |                        |      | 15    | 30   | mV    |  |

| IN Overvoltage Threshold        | Varia                         | V. riging                                                                                                                                                            | 0.40V hy                                                       | /steresis (MAX8900B)   | 8.80 | 9.00  | 9.20 | V     |  |

| (Note 3)                        | Vovlo                         | V <sub>IN</sub> rising                                                                                                                                               | 0.26V hy                                                       | /steresis (MAX8900A)   | 6.35 | 6.50  | 6.65 | ] V   |  |

|                                 | Charger enabled, no switching |                                                                                                                                                                      | switching                                                      |                        | 1    | 2     |      |       |  |

| IN Supply Current               | I <sub>IN</sub>               | Charger enabled, f = 3.25MHz, V <sub>IN</sub> = 6V                                                                                                                   |                                                                |                        |      | 20    |      | mA    |  |

|                                 |                               | Charger disabled, CEN = high                                                                                                                                         |                                                                |                        |      | 0.04  | 0.2  |       |  |

| LX High-Side Resistance         | RHS                           |                                                                                                                                                                      |                                                                |                        |      | 0.10  |      | Ω     |  |

| LX Low-Side Resistance          | RLS                           |                                                                                                                                                                      |                                                                |                        |      | 0.15  |      | Ω     |  |

| IV Looke as Current             |                               | LX = GND                                                                                                                                                             | or INI                                                         | T <sub>A</sub> = +25°C |      | 0.01  | 10   |       |  |

| LX Leakage Current              |                               | LX = GND                                                                                                                                                             | OF IIN                                                         | T <sub>A</sub> = +85°C |      | 0.1   |      | - μΑ  |  |

| DCT Laglaga Current             |                               | TA = +25°C                                                                                                                                                           |                                                                | T <sub>A</sub> = +25°C |      | 0.01  | 10   |       |  |

| BST Leakage Current             |                               | VBST - VLX                                                                                                                                                           | $T_{A} = +85^{\circ}C$                                         |                        |      | 0.1   |      | μΑ    |  |

| Current-Sense Resistor          | Rsns                          | VBAT = 2.6V                                                                                                                                                          |                                                                |                        |      | 0.045 |      | Ω     |  |

| IN to BAT Dropout Resistance    | RIN2BAT                       | Calculation estimates a 40mΩ inductor resistance (R <sub>L</sub> ), R <sub>IN2BAT</sub> = R <sub>IN2INBP</sub> + R <sub>HS</sub> + R <sub>L</sub> + R <sub>SNS</sub> |                                                                |                        |      | 0.3   |      | Ω     |  |

| Switching Frequency             | fsw                           | V <sub>BAT</sub> = 2.6V                                                                                                                                              |                                                                |                        |      | 3.25  |      | MHz   |  |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(VIN = 6V, VBAT = 4V, RSETI = 2.87k\Omega, RDNI = 3.57k\Omega, VTHM = VAVL/2, circuit of Figure 1, TA = -40°C to +85°C, unless otherwise noted. Typical values are at TA = +25°C.) (Note 2)$

| PARAMETER                                                   | SYMBOL          | CONDITIONS                                                                                                                              |                                                                   | MIN   | TYP   | MAX   | UNITS |  |

|-------------------------------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-------|-------|-------|-------|--|

| Minimum On-Time                                             | ton-min         |                                                                                                                                         |                                                                   | 90    |       |       | ns    |  |

| Maximum On-Time                                             | ton-max         |                                                                                                                                         |                                                                   |       | 9     |       | μs    |  |

| Minimum Off-Time                                            | toff            |                                                                                                                                         |                                                                   |       | 75    |       | ns    |  |

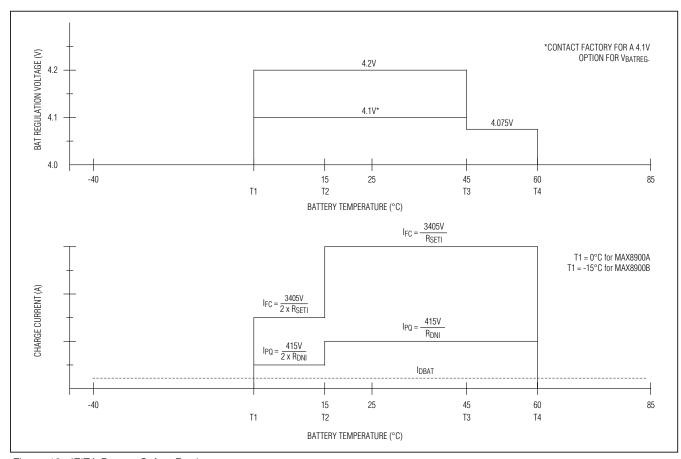

|                                                             |                 |                                                                                                                                         | $A = +25$ °C, $V_{THM}$ between 1 and T3                          | 4.179 | 4.200 | 4.221 |       |  |

| DAT Degulation Valtage (Note 2)                             | \/              |                                                                                                                                         | A = -40°C to +85°C, VTHM<br>etween T1 and T3                      | 4.158 | 4.200 | 4.242 | V     |  |

| BAT Regulation Voltage (Note 3)                             | VBATREG         | ( <del>-</del> )                                                                                                                        | A = +25°C, V <sub>THM</sub> between 3 and T4 (Note 5)             | 4.055 | 4.075 | 4.095 | V     |  |

|                                                             |                 |                                                                                                                                         | A = -40°C to $+85$ °C, V <sub>THM</sub> etween T3 and T4 (Note 5) | 4.034 | 4.075 | 4.100 |       |  |

| Charger Restart Threshold                                   | VPOTRT          | V <sub>THM</sub> between T1                                                                                                             | and T3                                                            | -70   | -100  | -125  | mV    |  |

| (Note 6)                                                    | VRSTRT          | V <sub>THM</sub> between T3                                                                                                             | and T4                                                            |       | -75   |       | TIIV  |  |

| BAT Prequalification Lower Threshold (Figure 6)             | VPQLTH          | VBAT rising,180m                                                                                                                        | V hysteresis                                                      |       | 2.1   |       | V     |  |

| BAT Prequalification Upper<br>Threshold (Figure 6) (Note 3) | VPQUTH          | V <sub>BAT</sub> rising, 180m<br>MAX8900A/MAX8                                                                                          | nV typical hysteresis,<br>900B                                    | 2.7   | 2.8   | 2.9   | V     |  |

|                                                             |                 |                                                                                                                                         | RSETI = $2.87$ k $\Omega$                                         | 1166  | 1190  | 1214  | mA    |  |

| Fast-Charge Current                                         | IFC             | V <sub>THM</sub> between T2 and T4 (Figure 10                                                                                           |                                                                   | 490   | 500   | 510   |       |  |

|                                                             |                 | RSETI = $34.0$ k $\Omega$                                                                                                               |                                                                   | 99    | 101   | 103   |       |  |

| Taot onargo ourront                                         | 110             | VTHM between T1 and T2 (Figure 10); the fast-charge current is reduced to 50% the value programmed by RSETI                             |                                                                   |       |       | %     |       |  |

|                                                             |                 |                                                                                                                                         | Minimum                                                           |       | 50    |       |       |  |

| Fast-Charge Current Set Range                               |                 | (Figure 5)                                                                                                                              | Maximum                                                           |       | 1200  |       | mA    |  |

| Fast-Charge Setting Resistor                                | _               |                                                                                                                                         | Minimum                                                           |       | 2.87  |       |       |  |

| Range                                                       | RSETI           | (Figure 5)                                                                                                                              | Maximum                                                           |       | 68.1  |       | kΩ    |  |

|                                                             |                 |                                                                                                                                         | $R_{DNI} = 3.83k\Omega$ (Note 5)                                  | 93    | 99    | 105   |       |  |

|                                                             |                 | V <sub>THM</sub> between T2 and T4 (Figure 10                                                                                           | PDAIL = 7.69kQ (Note 5)                                           | 47    | 50    | 53    | mA    |  |

| Done Current                                                | IDN             | and 14 (Figure 10                                                                                                                       | $R_{DNI} = 38.3k\Omega$                                           | 9.5   | 10.5  | 11.5  | -     |  |

| Done Current                                                | אוטו            | V <sub>THM</sub> between T1 and T2 (Figure 10); the done current threshold is reduced to 50% the value programmed by R <sub>DNI</sub>   |                                                                   |       | 50    |       | %     |  |

|                                                             |                 | V <sub>THM</sub> between T2                                                                                                             | $R_{DNI} = 3.83k\Omega$ (Note 5)                                  | 95    | 105   | 115   | mA    |  |

|                                                             |                 | and T4 (Figure 10)                                                                                                                      | RDNI = $7.68$ kΩ (Note 5)                                         | 49    | 54    | 59    |       |  |

| Prequalification Current                                    | I <sub>PQ</sub> | VBAT = 2.6V                                                                                                                             | $R_{DNI} = 38.3k\Omega$ (Note 5)                                  | 10    | 11.5  | 13    |       |  |

| Troquamounon ourion                                         | ירע             | V <sub>THM</sub> between T1 and T2 (Figure 10); the prequalification current is reduced to 50% the value programmed by R <sub>DNI</sub> |                                                                   |       | 50    |       | %     |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN}=6V,\,V_{BAT}=4V,\,R_{SETI}=2.87k\Omega,\,R_{DNI}=3.57k\Omega,\,V_{THM}=V_{AVL/2},\,circuit\,of\,Figure\,1,\,T_{A}=-40^{\circ}C\,to\,+85^{\circ}C,\,unless\,otherwise\,noted.\,Typical\,values\,are\,at\,T_{A}=+25^{\circ}C.)\,(Note\,2)$

| PARAMETER                                     | SYMBOL           | CONDITIONS                                                        |                  |                                           | MIN   | TYP   | MAX   | UNITS  |

|-----------------------------------------------|------------------|-------------------------------------------------------------------|------------------|-------------------------------------------|-------|-------|-------|--------|

| Done and Prequalification                     |                  | (Figure 5)                                                        | (E) Minimum      |                                           |       | 9.8   |       | mA     |

| Current Set Range                             |                  | (Figure 5) Maximum                                                |                  |                                           | 200   |       | mA    |        |

| Done and Prequalification                     | Dovu             | (Figure 5)                                                        | Minimum          |                                           |       | 1.91  |       | 1.0    |

| Setting Resistor Range                        | R <sub>DNI</sub> | (Figure 5)                                                        | Maxi             | mum                                       |       | 39.2  |       | kΩ     |

| Dead-Battery Charge Current                   | IDBAT            | 0V ≤ V <sub>BAT</sub> ≤ V <sub>DBAT</sub>                         |                  |                                           |       | 45    |       | mA     |

| Dead-Battery Voltage Threshold (Figure 6)     | Vdbat            |                                                                   |                  |                                           |       | 2.5   |       | V      |

| BAT Leakage Current                           |                  | VIN = 0V, VBAT = 4.2V includes LX leakage of through the inductor |                  | $T_A = +25^{\circ}C$ $T_A = +85^{\circ}C$ |       | 0.02  | 1     | μА     |

| Charger Soft-Start Time (Note 3)              | tss              | MAX8900A, MAX8900                                                 | В                |                                           |       | 1.5   |       | ms     |

| CHARGE TIMER                                  |                  |                                                                   | -                |                                           |       |       |       |        |

| Prequalification Time                         | tpQ              | CCT = 0.1µF                                                       |                  |                                           |       | 30    |       | min    |

| Fast-Charge Time                              | tFC              | C <sub>CT</sub> = 0.1µF                                           |                  |                                           |       | 180   |       | min    |

| Top-Off Time                                  | tTO              |                                                                   |                  |                                           | 16    |       |       | S      |

| Timer Accuracy                                |                  |                                                                   | -                |                                           | -15   |       | +15   | %      |

| THERMISTOR MONITOR                            |                  |                                                                   |                  |                                           |       |       |       |        |

| THM Hot Shutoff Threshold (60°C)              | T4               | VTHM/AVL falling, 1% I<br>(thermistor temperature                 |                  |                                           | 21.24 | 22.54 | 23.84 | %AVL   |

| THM Hot Voltage Foldback<br>Threshold (45°C)  | T3               | VTHM/AVL falling, 1% I<br>(thermistor temperature                 |                  |                                           | 32.68 | 34.68 | 36.68 | %AVL   |

| THM Cold Current Foldback<br>Threshold (15°C) | T2               | VTHM/AVL rising, 1% h<br>(thermistor temperature                  |                  |                                           | 57.00 | 60.00 | 63.00 | %AVL   |

| THM Cold Shutoff Threshold                    | T1               | VTHM/AVL rising, 1% hysteresis (thermistor                        | 0°C, N           | MAX8900A                                  | 71.06 | 74.56 | 78.06 | %AVL   |

| (-15°C/0°C)                                   | 11               | temperature falling)                                              | -15°C            | , MAX8900B                                | 81.43 | 86.07 | 90.98 | /0/AVL |

| TI IM Input I colore                          |                  | TUM CND or AVI                                                    | T <sub>A</sub> = | +25°C                                     | -0.2  | 0.001 | +0.2  |        |

| THM Input Leakage                             |                  | THM = GND or AVL $T_A = +85^{\circ}C$                             |                  |                                           | 0.001 |       | μA    |        |

| CHARGE ENABLE INPUT (CEN)                     |                  |                                                                   |                  |                                           |       |       |       |        |

| CEN Input Voltage Low                         | VIL              |                                                                   |                  |                                           |       |       | 0.6   | V      |

| CEN Input Voltage High                        | VIH              | 1.4                                                               |                  |                                           |       |       | V     |        |

| CEN Internal Pulldown Resistance              | RCEN             |                                                                   |                  |                                           | 100   | 200   | 400   | kΩ     |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(VIN = 6V, VBAT = 4V, RSETI = 2.87k\Omega, RDNI = 3.57k\Omega, VTHM = VAVL/2, circuit of Figure 1, TA = -40°C to +85°C, unless otherwise noted. Typical values are at TA = +25°C.) (Note 2)$

| PARAMETER                            | SYMBOL  | CONDITIONS                                                                                    |                      |         | TYP   | MAX  | UNITS |  |

|--------------------------------------|---------|-----------------------------------------------------------------------------------------------|----------------------|---------|-------|------|-------|--|

| STATUS OUTPUTS (STAT1, STAT2, STAT3) |         |                                                                                               |                      |         |       |      |       |  |

| STAT1 and STAT2 Output               |         | ISINK = 1mA                                                                                   |                      |         | 0.025 | 0.05 | V     |  |

| Voltage Low                          |         | ISINK = 15mA                                                                                  |                      |         | 0.38  |      | V     |  |

| STAT1 and STAT2 Output High          |         | VSTAT_= 28V                                                                                   | $T_A = +25^{\circ}C$ |         | 0.001 | 1    | μA    |  |

| Leakage                              |         | VSTAT 20V                                                                                     | $T_A = +85^{\circ}C$ |         | 0.01  |      | μΑ    |  |

| STAT3 Output Voltage Low             |         | ISINK = 1mA                                                                                   |                      |         | 0.01  |      | V     |  |

| STATS Output Voltage Low             |         | ISINK = 15mA                                                                                  |                      |         | 0.15  | 0.25 | V     |  |

| STAT3 Output High Leakage            |         | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\                                                        | $T_A = +25^{\circ}C$ |         | 0.001 | 1    |       |  |

| STATS Output High Leakage            |         | VSTAT3 = 5.5V                                                                                 | $T_A = +85^{\circ}C$ | 0.01    |       |      | μΑ    |  |

| PVL AND AVL                          |         |                                                                                               |                      |         |       |      |       |  |

|                                      |         | 0 to 30mA internal load, VIN = 6V,<br>TA = 0°C to +85°C<br>0 to 23mA internal load, VIN = 6V, |                      | 4.6 5.0 |       |      |       |  |

| PVL and AVL Output Voltage           |         |                                                                                               |                      |         | 5.1   | V    |       |  |

| l ve and Ave Output voltage          |         |                                                                                               |                      |         | 5.0   | 0.1  | V     |  |

|                                      |         | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                                                 |                      |         |       |      |       |  |

| THERMAL                              |         |                                                                                               |                      |         |       |      |       |  |

| Thermal Regulation Temperature       | TREG    | Junction temperature                                                                          | when charge current  |         | 95    |      | °C    |  |

| Thermal Hegalation Femperature       | TILO    | is reduced                                                                                    |                      |         |       |      |       |  |

|                                      |         | The charge current is                                                                         |                      |         |       |      |       |  |

| Thermal Regulation Gain              | TTREG   | the fast-charge currer                                                                        |                      |         | 6.7   |      | %/°C  |  |

|                                      |         | degree that the junction temperature exceeds the thermal regulation temperature               |                      |         |       |      |       |  |

| Thermal-Shutdown Temperature         | TSHDN   | Junction temperature rising, 15°C hysteresis                                                  |                      |         | +155  |      | °C    |  |

|                                      | אוחשפיי | Touriour terriberature                                                                        | T 100                |         |       |      |       |  |

- Note 2: Parameters are production tested at T<sub>A</sub> = +25°C. Limits over the operating temperature range are guaranteed through correlation using statistical quality control (SQC) methods.

- Note 3: Contact factory for alternative values.

- Note 4: VIN must be greater than VUVLO-RISING for the part to operate when  $\overline{\text{CEN}}$  is pulled low. For example, if  $\overline{\text{CEN}}$  is low and the MAX8900\_ is operating with VUVLO-FALLING < VIN < VUVLO-RISING, then toggling  $\overline{\text{CEN}}$  results in a nonoperating condition.

- **Note 5:** Guaranteed by design, not production tested.

- Note 6: When the charger is in its DONE state, it restarts when the battery voltage falls to the charger restart threshold. The battery voltage that causes a restart (VBAT-RSTRT) is VBAT-RSTRT = 4.2V VRSTRT. For example, with the MAX8900A, VBAT-RSTRT = 4.2V 100mV = 4.1V.

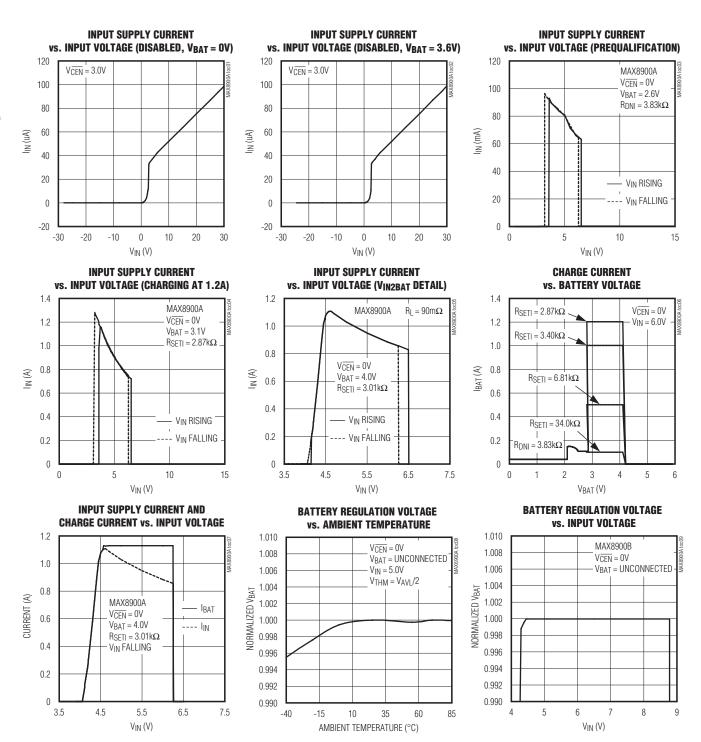

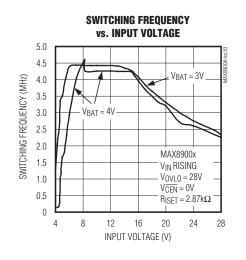

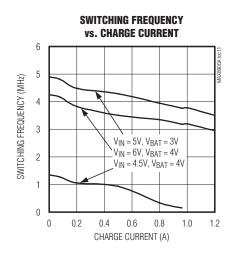

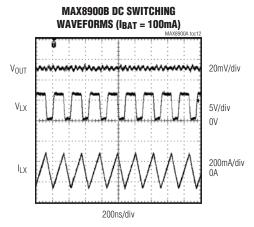

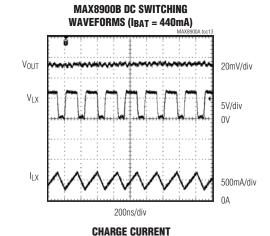

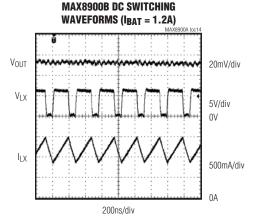

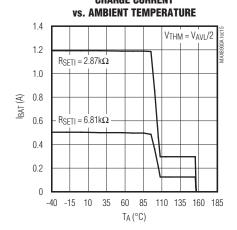

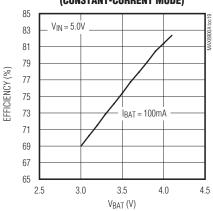

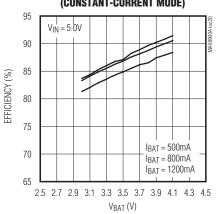

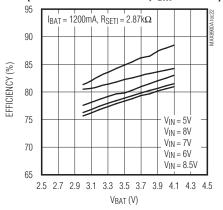

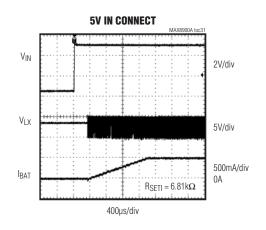

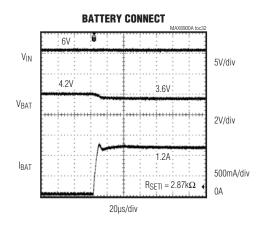

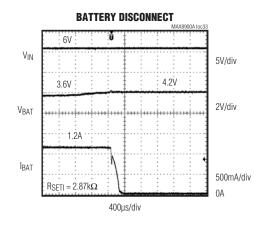

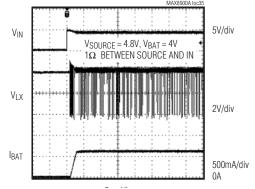

### **Typical Operating Characteristics**

(Circuit of Figure 1, VIN = 6V, VBAT = 3.6V, TA = +25°C, unless otherwise noted.)

Typical Operating Characteristics (continued)

(Circuit of Figure 1, VIN = 6V, VBAT = 3.6V, TA = +25°C, unless otherwise noted.)

**Typical Operating Characteristics (continued)**

(Circuit of Figure 1, VIN = 6V, VBAT = 3.6V, TA = +25°C, unless otherwise noted.)

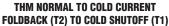

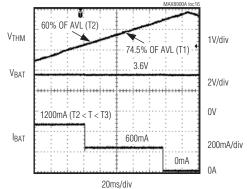

### THM NORMAL TO HOT VOLTAGE FOLDBACK (T3) TO HOT SHUTOFF (T4) THRESHOLD

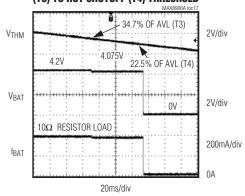

### CHARGER ENABLE

### EFFICIENCY vs. BATTERY VOLTAGE (CONSTANT-CURRENT MODE)

### EFFICIENCY vs. BATTERY VOLTAGE (CONSTANT-CURRENT MODE)

### EFFICIENCY vs. CHARGE CURRENT (CONSTANT-CURRENT MODE)

### EFFICIENCY vs. BATTERY VOLTAGE (CONSTANT-CURRENT MODE, IBAT = 1200mA)

### Typical Operating Characteristics (continued)

(Circuit of Figure 1, V<sub>IN</sub> = 6V, V<sub>BAT</sub> = 3.6V, T<sub>A</sub> = +25°C, unless otherwise noted.)

**Typical Operating Characteristics (continued)**

(Circuit of Figure 1, VIN = 6V, VBAT = 3.6V, TA = +25°C, unless otherwise noted.)

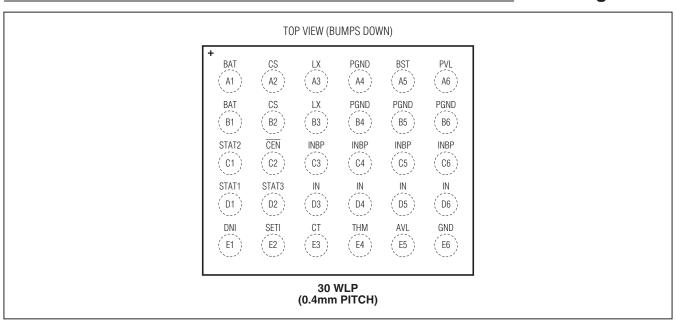

**Pin Configuration**

### Pin Description

| PIN               | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1, B1            | BAT   | Connection to Battery. Connect to a single-cell Li+/Li-Poly battery from BAT to PGND. Connect both BAT pins together externally. Bypass BAT to PGND with a 2.2µF ceramic capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A2, B2            | CS    | $40m\Omega$ Current-Sense Node. Connect the inductor from LX to CS. Connect both CS pins together externally.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| A3, B3            | LX    | Inductor Switching Node. Connect the inductor between LX and CS. Connect both LX pins together externally. When enabled ( $\overline{CEN} = 0$ ), LX switches between INBP and PGND to control the battery charging. When disabled ( $\overline{CEN} = 1$ ), the LX switches are high-impedance however they still have body diodes as shown in Figure 3.                                                                                                                                                                                                                                                                  |

| A4, B4,<br>B5, B6 | PGND  | Power Ground for Step-Down Low-Side Synchronous n-Channel MOSFET. Connect all PGND pins together externally.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| A5                | BST   | Supply for High-Side n-Channel Gate Driver. Bypass BST to LX with a 0.1µF ceramic capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| A6                | PVL   | 5V Linear Regulator to Power Internal Circuits. PVL also charges the BST capacitor. Bypass PVL to PGND with a 1.0µF ceramic capacitor. Powering external loads from PVL is not recommended.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| C1                | STAT2 | Status Output 2. STAT2 is an open-drain output that has a 30V absolute maximum rating and a typical pulldown resistance of $25\Omega$ . For the MAX8900A, STAT1 and STAT2 indicate different states as shown in Table 4. For the MAX8900B, STAT1, STAT2, and STAT3 indicate different operating states of the MAX8900_ as shown in Table 3.                                                                                                                                                                                                                                                                                |

| C2                | CEN   | Charge Enable Input. $\overline{\text{CEN}}$ has an internal $200\text{k}\Omega$ pulldown resistor. Pull $\overline{\text{CEN}}$ low or leave it unconnected to enable the MAX8900 Drive $\overline{\text{CEN}}$ high to disable the MAX8900 Note: $V_{\text{IN}}$ must be greater than $V_{\text{UVLO-RISING}}$ for the MAX8900_ to operate when $\overline{\text{CEN}}$ is pulled low. For example, if $\overline{\text{CEN}}$ is low and the MAX8900_ is operating with $V_{\text{UVLO-FALLING}} < V_{\text{IN}} < V_{\text{UVLO-RISING}}$ , then toggling $\overline{\text{CEN}}$ results in a nonoperating condition. |

### Pin Description (continued)

| PIN   | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C3-C6 | INBP  | Power Input Bypass. Connect all INBP pins together externally. Bypass INBP to PGND with a 0.47µF ceramic capacitor.                                                                                                                                                                                                                                                                                             |

| D1    | STAT1 | Status Output 1. STAT1 is an open-drain output that has a 30V absolute maximum rating and a typical internal pulldown resistance of $25\Omega$ . For the MAX8900A, STAT1 and STAT2 indicate different states as shown in Table 4. For the MAX8900B, STAT1, STAT2, and STAT3 indicate different operating states of the MAX8900_ as shown in Table 3.                                                            |

| D2    | STAT3 | Status Output 3. STAT3 is an open-drain output that is a 6V absolute maximum rating and a typical pulldown resistance of $10\Omega$ . For the MAX8900A, STAT1 and STAT2 indicate different states as shown in Table 4. For the MAX8900B, STAT1, STAT2, and STAT3 indicate different operating states of the MAX8900_ as shown in Table 3.                                                                       |

| D3-D6 | IN    | Power Input. IN is capable of delivering 1.2A to the battery and/or system. Connect all IN pins together externally. Bypass IN to PGND with a 0.47µF ceramic capacitor.                                                                                                                                                                                                                                         |

| E1    | DNI   | Done/Prequalification Program Input. DNI is a dual function pin that sets both the done current threshold and the prequalification charge rate. Connect a resistor from DNI to GND to set the threshold between 10mA and 200mA. DNI is pulled to GND during shutdown.                                                                                                                                           |

| E2    | SETI  | Fast-Charge Current Program Input. Connect a resistor from SETI to GND to set the fast-charge current from 0.05A to 1.2A. SETI is pulled to GND during shutdown.                                                                                                                                                                                                                                                |

| E3    | СТ    | Charge Timer Set Input. A capacitor (C <sub>CT</sub> ) from CT to GND sets the prequalification and fast-charge fault timers. Use 0.1µF for 180-minute fast-charge time limit and 30-minute prequalification time limit. Connect to GND to disable the timer.                                                                                                                                                   |

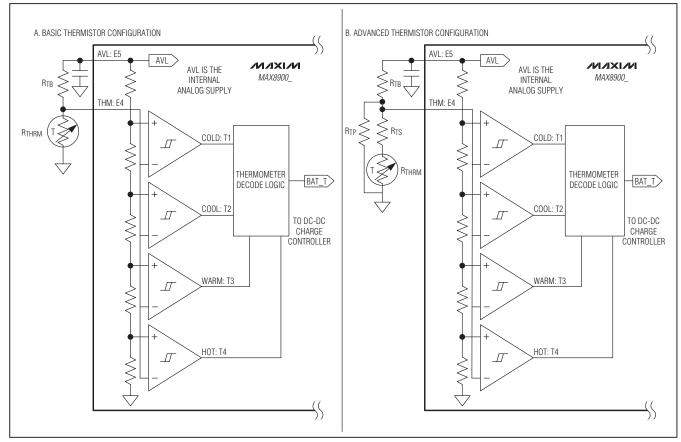

| E4    | THM   | Thermistor Input. Connect a negative temperature coefficient (NTC) thermistor from THM to GND. Connect a resistor equal to the thermistor's +25°C resistance from THM to AVL. Thermistor adjusts the charge current and termination voltage as described in the JEITA specification for safe use of secondary Li+ batteries. See Figure 10. To disable the THM operation, bias VTHM midway between AVL and GND. |

| E5    | AVL   | 5V Linear Regulator to Power Low-Noise Internal Circuits. Bypass AVL to GND with a 0.1µF ceramic capacitor. Powering external loads from AVL is not recommended.                                                                                                                                                                                                                                                |

| E6    | GND   | Ground. GND is the low-noise ground connection for the internal circuitry. See the <i>PCB Layout</i> section for more details.                                                                                                                                                                                                                                                                                  |

Figure 1. Applications Circuit: Single SETI Resistor, Status Indicators Connected to LEDs

Figure 2. Applications Circuit: Multiple Charge Rates Managed by μP to Be USB Compliant, Status Indicators Connected to a μP

Figure 3. Functional Diagram

#### **Detailed Description**

The MAX8900\_ is a full-featured, high-frequency switch-mode charger for a 1-cell Li+ or Li-Poly battery. It delivers up to 1.2A to the battery from 3.4V to 6.3V (MAX8900A) or 3.4V to 8.7V (MAX8900B). Contact the factory for input operating voltage ranges up to +20V. The 3.25MHz switch-mode charger is ideally suited to small portable devices such as headsets and ultra-portable media players because it minimizes component size and heat.

Several features make the MAX8900\_ ideal for high reliability systems. The MAX8900\_ is protected against input voltages as high as +22V and as low as -22V. Battery protection features include low voltage prequalification, charge fault timer, die temperature monitoring, and battery temperature monitoring. The battery temperature monitoring adjusts the charge current and termination voltage as described in the JEITA (Japan Electronics and Information Technology Industries Association) specification for safe use of secondary Li+ batteries. The full title of the standard is A Guide to the Safe Use of Secondary Lithium Ion Batteries in Notebook-Type Personal Computers, April 20, 2007.

Charge parameters are easily adjustable with external components. An external resistance adjusts the charge current from 50mA to 1200mA. Another external resistance adjusts the prequalification and done current thresholds from 10mA to 200mA. The done current threshold is very accurate achieving ±1mA at the 10mA level. The charge timer is adjustable with an external capacitor.

#### **Control Scheme**

A proprietary hysteretic current PWM control scheme ensures high efficiency, fast switching, and physically tiny external components. Inductor ripple current is internally set to provide 3.25MHz. At very high duty factors, when the input voltage is lowered close to the output voltage, the steady-state duty ratio does not allow 3.25MHz operation because of the minimum off-time. The controller then provides minimum off-time, peak current regulation. Similarly, when the input voltage is too high to allow 3.25MHz operation due to the minimum on-time, the controller becomes a minimum on-time, valley current regulator. In this way, the ripple current in the inductor is always as small as possible to reduce the output ripple voltage. The inductor ripple current is made to vary with input and output voltage in a way that reduces frequency variation.

#### Soft-Start

To prevent input current transients, the rate of change of the input current (di/dt) and charge current is limited. When the input is valid, the charge current ramps from 0mA to the fast-charge current value in 1.5ms. Charge current also soft-starts when transitioning from the prequalification state to the fast-charge state. There is no di/dt limiting when transitioning from the done state to the fast-charge state (Figures 7 and 8). Similarly, if RSETI is changed suddenly when using a switch or variable resistor at SETI as shown in Figure 2 there is no di/dt current limiting.

#### **Setting the Fast-Charge Current (SETI)**

As shown in Figure 4, a resistor from SETI to ground (RSETI) sets the fast-charge current (IFC). The MAX8900\_ supports values of IFC from 50mA to 1200mA. Select RSFTI as follows:

#### IFC = 3405V/RSETI

Determine the optimal IFC for a given system by considering the characteristics of the battery and the capabilities of the charge source.

**Example 1:** If you are using a 5V ±5% 1A charge source along with an 800mAh battery that has a 1C fast-charge rating, then choose RSETI to be 4.42kΩ ±1%. This value provides a typical charge current of 770mA. Given the ±2% six sigma limit on the MAX8900\_ fast-charge current accuracy along with the ±1% accuracy of the resistor, we can reasonably expect that the 770mA typical value has an accuracy of ±2.2% ( $2.2 \approx \text{sqrt}(2^2 + 1^2)$ ) or ±17mA. Furthermore, since the MAX8900\_ charger uses a step-down converter topology, we can guarantee that the input current is less than or equal to the output current so we do not violate the 1A rating of the charge source.

Depending on its mode of operation, the MAX8900\_controls the voltage at SETI to be between 0V and 1.5V. Avoid adding capacitance directly to the SETI pin that exceeds 10pF.

As a protection feature, if the battery temperature is between the T2 and T4 thresholds and SETI is shorted to ground, then the MAX8900\_ latches off the battery charger and enters the timer fault state. This protection feature is disabled outside of fast-charge, top-off, done mode and inside thermal foldback. Furthermore, if SETI is unconnected, then the battery fast-charge current is 0A.

### Setting the Prequalification Current and Done Threshold (DNI)

As shown in Figure 5, a resistor from DNI to ground (RDNI) sets the prequalification current (IPQ) and done current (IDN). The MAX8900\_ supports values of RDNI from 1.19k $\Omega$  to 38.2k $\Omega$ . Select RDNI as follows:

IDN = 384V/RDNI

IPQ = 415V/RDNI

Determine the optimal IPQ and IDN for a given system by considering the characteristics of the battery.

| RSETI<br>(kΩ) | IFC<br>(A) | RSETI<br>(kΩ) | IFC<br>(A) | RSETI<br>(kΩ) | IFC<br>(A) |

|---------------|------------|---------------|------------|---------------|------------|

| 2.87          | 1.186      | 7.15          | 0.476      | 24.9          | 0.137      |

| 3.01          | 1.131      | 7.32          | 0.465      | 27.4          | 0.124      |

| 3.16          | 1.078      | 7.87          | 0.433      | 30.1          | 0.113      |

| 3.32          | 1.026      | 8.25          | 0.413      | 32.2          | 0.106      |

| 3.57          | 0.954      | 9.09          | 0.375      | 34.0          | 0.100      |

| 3.92          | 0.869      | 10.0          | 0.341      | 35.7          | 0.095      |

| 4.12          | 0.826      | 11.0          | 0.310      | 39.2          | 0.087      |

| 4.32          | 0.788      | 12.1          | 0.281      | 43.2          | 0.079      |

| 4.42          | 0.770      | 13.0          | 0.262      | 45.5          | 0.075      |

| 4.75          | 0.717      | 14.0          | 0.243      | 49.9          | 0.068      |

| 4.99          | 0.682      | 15.0          | 0.227      | 51.1          | 0.067      |

| 5.11          | 0.666      | 16.2          | 0.210      | 56.2          | 0.061      |

| 5.62          | 0.606      | 18.2          | 0.187      | 61.9          | 0.055      |

| 6.19          | 0.550      | 20.0          | 0.170      | 66.5          | 0.051      |

| 6.81          | 0.500      | 22.1          | 0.154      | 68.1          | 0.050      |

| 7.5           | 0.454      | 24.3          | 0.140      |               |            |

Figure 4. Fast-Charge Current vs. R<sub>SETI</sub> (www.maxim-ic.com/tools/other/software/MAX8900-RSETI.XLS)

Depending on its mode of operation, the MAX8900\_ controls the voltage at DNI from 0 to 1.5V. Avoid adding capacitance directly to the SETI pin that exceeds 10pF.

As shown in Figure 10, the prequalification current and done threshold is set to 50% of programmed value when T1 < THM < T2, and 100% of programmed value when T2 < THM < T4.

As a protection feature, if the battery temperature is between the T2 and T4 thresholds and DNI is shorted to ground, then the MAX8900\_ latches off the battery charger and enters the timer fault state. This protection feature is disabled inside of dead-battery mode and thermal foldback. Furthermore, if DNI is unconnected, then the prequalification and done current is 0A and the charge timer prevents the MAX8900\_ from indefinitely operating in its done state.

#### Charge Enable Input (CEN)

CEN is a digital input. Driving CEN high disables the battery charger. Pull CEN low or leave it unconnected

| R <sub>DNI</sub><br>(kΩ) | I <sub>PQ</sub><br>(mA) | I <sub>DN</sub><br>(mA) | R <sub>DNI</sub><br>(kΩ) | I <sub>PQ</sub><br>(mA) | I <sub>DN</sub><br>(mA) |

|--------------------------|-------------------------|-------------------------|--------------------------|-------------------------|-------------------------|

| 1.91                     | 217.3                   | 201.0                   | 7.5                      | 55.3                    | 51.2                    |

| 2.37                     | 175.1                   | 162.0                   | 7.68                     | 54.0                    | 50.0                    |

| 3.48                     | 119.3                   | 110.3                   | 7.87                     | 52.7                    | 48.8                    |

| 3.57                     | 116.2                   | 107.6                   | 10.0                     | 41.5                    | 38.4                    |

| 3.83                     | 108.4                   | 100.3                   | 14.3                     | 29.0                    | 26.9                    |

| 4.42                     | 93.9                    | 86.9                    | 20.0                     | 20.8                    | 19.2                    |

| 5.9                      | 70.3                    | 65.1                    | 28.0                     | 14.8                    | 13.7                    |

| 7.32                     | 56.7                    | 52.5                    | 39.2                     | 10.6                    | 9.8                     |

Figure 5. Prequalification Current and Done Threshold vs. R<sub>DNI</sub> (www.maxim-ic.com/tools/other/software/MAX8900-DNI.XLS)

to enable the MAX8900\_.  $\overline{\text{CEN}}$  has an internal 200k $\Omega$  pulldown resistor. When disabled, the MAX8900\_ supply current is reduced, the step-down converter high-side and low-side switches are off, and the AVL is disabled.

In many systems, there is no need for the system controller (typically a microprocessor (µP)) to disable the charger because the MAX8900\_ independently manages the charger. In these situations,  $\overline{\text{CEN}}$  can be connected to ground or left unconnected. **Note:** if  $\overline{\text{CEN}}$  is permanently connected to ground or left unconnected, the input power must be cycled to escape from a timer fault state (see Figures 7 and 8 for more information).

VIN must be greater than VUVLO-RISING for the MAX8900\_ to operate when  $\overline{\text{CEN}}$  is pulled low. For example, if  $\overline{\text{CEN}}$  is low and the MAX8900\_ is operating with VUVLO-FALLING < VIN < VUVLO-RISING, then toggling  $\overline{\text{CEN}}$  results in a nonoperating condition.

#### **Charger States**

The MAX8900\_ utilizes several charging states to safely and quickly charge batteries as shown in Figure 7. Figure 6 shows an exaggerated view of a Li+/Li-Poly battery progressing through the following charge states when the die and battery are close to room temperature: dead battery → prequalification → fast-charge → top-off → done.

Figure 6. Li+/Li-Poly Charge Profile

Figure 7. Charger State Diagram (3-Pin Status)

Figure 8. Charger State Diagram (2-Pin Status)

#### Charger Disabled State

When  $\overline{\text{CEN}}$  is high or the input voltage is out of range, the MAX8900\_ disables the charger. To exit this state,  $\overline{\text{CEN}}$  must be low and the input voltage must be within its valid range.

#### **Dead-Battery State**

When a deeply discharged battery is inserted with a voltage of less than VPQLTH, the MAX8900\_ disables the switching charger and linearly charges with IDBAT. Once VBAT increases beyond VPQLTH, the MAX8900\_ clears the prequalification timer and transitions to the dead battery + prequalification state. This state prevents the MAX8900\_ from dissipating excessive power in the event of a shorted battery. The dead-battery linear charger remains on except when in the charger disabled state, timer fault state, thermal shutdown, and VBAT > VDBAT.

#### Dead Battery + Prequalification State

The dead battery + prequalification state occur when the battery voltage is greater than VPQLTH and less than VDBAT. In this state, both the linear dead-battery charger and the switching charger are on and delivering current to the battery. The total battery current is IDBAT + IPQ. If the MAX8900\_ remains in this state for longer than tPQ, then the MAX8900\_ transitions to the timer fault state. A normal battery typically stays in this state for several minutes or less and when the battery voltage rises above VDBAT, the MAX8900\_ transitions to the prequalification state. The dead-battery linear charger remains on except when in the charger disabled state, timer fault state, thermal shutdown, and VBAT > VDBAT.

#### **Prequalification State**

The prequalification state occurs when the battery voltage is greater than VDBAT and less than VPQUTH.

In this state, the linear dead-battery charger is turned off and only the switching charger is on and delivering current to the battery. The total battery current is IPQ. If the MAX8900\_ remains in this state for longer than tPQ, then the MAX8900\_ transitions to the timer fault state. A normal battery typically stays in the prequalification state for several minutes or less and when the battery voltage rises above VPQUTH, the MAX8900\_ transitions to the fast-charge constant current state.

As shown in Figure 10, the prequalification current and done threshold is set to 50% of programmed value when T1 < THM < T2, and 100% of programmed value when T2 < THM < T4.

#### Fast-Charge Constant Current State

The fast-charge constant current state occurs when the battery voltage is greater than VPQUTH and less than

VBATREG. In this state, the switching charger is on and delivering current to the battery. The total battery current is IFC. If the MAX8900\_ remains in this state and the fast-charge constant voltage state for longer than tFC, then the MAX8900\_ transitions to the timer fault state. When the battery voltage rises to VBATREG, the MAX8900\_ transitions to the fast-charge constant voltage state. As shown in Figure 10, the fast-charge constant current is set to 50% of programmed value when T1 < THM < T2, and 100% of programmed value when T2 < THM < T4.

The MAX8900\_ dissipates the most power in the fast-charge constant current state. This power dissipation causes the internal die temperature to rise. If the die temperature exceeds TREG, IFC is reduced. See the *Thermal Foldback* section for more detail.

If there is low input voltage headroom ( $V_{\text{IN}}$  -  $V_{\text{BAT}}$ ), then IFC decreases due to the impedance from IN to BAT. See Figure 13 for more detail.

#### Fast-Charge Constant Voltage State

The fast-charge constant voltage state occurs when the battery voltage is at the VBATREG and the charge current is greater than IDN. In this state, the switching charger is on and delivering current to the battery. The MAX8900\_ maintains VBATREG and monitors the charge current to detect when the battery consumes less than the IDN current. When the charge current decreases below the IDN threshold, the MAX8900\_ transitions to the top-off state. If the MAX8900\_ remains in the fast-charge constant current state and this state for longer than tFC, then the MAX8900\_ transitions to the timer fault state. Please note when the battery temperature is between T3 and T4 the BAT regulation voltage is reduced to 4.075V.

The MAX8900\_ offers an adjustable done current threshold (IDN) from 10mA to 200mA. The accuracy of the top-off current threshold is ±1mA when it is set for 10mA. This accurate threshold allows the maximum amount of charge to be stored in the battery before the MAX8900\_ transitions into done state.

#### Top-Off State

The top-off state occurs when the battery voltage is at VBATREG and the battery current decreases below IDN. In this state, the switching charger is on and delivers current to the battery. The MAX8900\_ maintains VBATREG for a specified time (tTO). When tTO expires, the MAX8900\_ transitions to the done state. If the charging current increases to IDN + 1mA before tTO expires, then the charger re-enters the fast-charge constant voltage state.

#### Done State

The MAX8900\_ enters its done state after the charger has been in the top-off state for tTO. In this state, the switching charger is off and no current is delivered to the battery. Although the charger is off, the SETI and DNI pins are biased in the done state and the MAX8900\_ consumes the associated current from the battery (IBAT = 1.5V/RSETI + 1.5V/RDNI + 3 $\mu$ A). If the system load presented to the battery is low (<< 100 $\mu$ A), then a typical system can remain in the done state for many days. If left in the done state long enough, the battery voltage decays below the restart threshold (VRSTRT) and the MAX8900\_ transitions back into the fast-charge state. There is no soft-start (di/dt limiting) during the done-to-fast-charge state transition.

#### **Timer Fault State**

The timer fault state occurs when either the prequalification or fast-charge timers expire, or SETI/DNI is shorted to ground. See the *Setting the Fast-Charge Current (SETI)* and *Setting the Prequalification Current and Done Threshold (DNI)* sections for more details. In this state the charger is off. The charger can exit the timer fault state by either cycling  $\overline{\text{CEN}}$  or input power.

#### Battery Hot/Cold State

The battery hot/cold state occurs when the MAX8900\_ is in any of its charge states (dead battery, prequalification, fast-charge, top-off) and thermistor temperature is either less than T1 or greater than T4. In this state, the charger is off and timers are suspended. The MAX8900\_ exits the temperature suspend state and returns to the state it came from once the thermistor temperature is greater than T1 and less than T4. The timer resumes once the MAX8900\_ exits this state.

#### VIN Too High State

The V<sub>IN</sub> too high state occurs when the MAX8900\_ is in any of its charge states (dead battery, prequalification, fast-charge, top-off) and V<sub>IN</sub> exceeds V<sub>OVLO</sub>. In this state, the charger is off and timers are suspended. The MAX8900\_ exits the V<sub>IN</sub> too high state and returns to the state it came from when V<sub>IN</sub> decreases below V<sub>OVLO</sub>. The timer resumes once the MAX8900\_ exits this state.

#### Charge Timer (CT)

As shown in Figure 7, a fault timer prevents the battery from charging indefinitely. In prequalification and fast-charge states, the timer is controlled by the capacitance at CT (C<sub>CT</sub>). The MAX8900\_ supports values of C<sub>CT</sub> from 0.01 $\mu$ F to 1.0 $\mu$ F. Calculate the prequalification time (tpQ) and fast-charge time (tFC) as follows (Figure 9):

| Сст  | tpQ   | oQ tFC |       | tто |

|------|-------|--------|-------|-----|

| (nF) | (min) | (min)  | (hrs) | (s) |

| 68   | 20.4  | 122.4  | 2     | 16  |

| 100  | 30.0  | 180.0  | 3     | 16  |

| 150  | 45.0  | 270.0  | 4.5   | 16  |

| 220  | 66.0  | 396.0  | 6.6   | 16  |

| 470  | 141.0 | 846.0  | 14.1  | 16  |

| 1000 | 300.0 | 1800.0 | 30.0  | 16  |

Figure 9. Charge Times vs. CCT

$$t_{PQ} = 30 \text{min} \times \frac{C_{CT}}{0.1 \mu F}$$

$$t_{FC} = 180 \text{min} \times \frac{C_{CT}}{0.1 \mu F}$$

The top-off time (tTO) is fixed at 16s:

$$t_{TO} = 16s$$

Connect CT to GND to disable the prequalification and fast-charge timers. With the internal timers of the MAX8900\_ disabled, an external device, such as a  $\mu P$  can control the charge time through the  $\overline{CEN}$  input.

#### Thermal Management

The MAX8900\_ is packaged in a 2.44mm x 2.67mm x 0.64mm, 0.4mm pitch WLP package and withstands a junction temperature of +150°C. The MAX8900\_ is rated for the extended ambient temperature range from -40°C to +85°C. Table 1 and Application Note 1891: Wafer-Level Packaging (WLP) and Its Applications (www.maxim-ic.com/ucsp) show the thermal characteristics of this package. The MAX8900\_ uses several

Table 1. 2.44mm x 2.67mm x 0.64mm, 0.4mm Pitch WLP Thermal Characteristics

|                              | FOUR-LAYER PCB<br>(JESD51-9:2s2p)                                                                                                                                                                                                          |