# P4C189 HIGH SPEED 16 x 4 STATIC CMOS RAM WITH INVERTING OUTPUTS

#### **FEATURES**

- 16 x 4 Static RAM

- Fast Access Time 35 ns Commercial and Industrial

- Available in the following packages:– 16-Pin PDIP

- Inverted Outputs

- 5V Power Supply ±10% for both commercial and industrial temperature ranges.

- Separate I/O

- Fully static operation with equal access and cycle times

- 3-STATE outputs for data bus applications

#### **DESCRIPTION**

The P4C189 is a 64-bit high-speed Static RAM with a 16 x 4 organization. The memory requires no clocks or refreshing and has equal access and cycle times. Inputs and outputs are fully TTL compatible. Operation is from a single 5 Volt supply. The output data is the complement

of the written data.

The P4C189 is offered in a 16-Pin DIP package. Devices are offered in both commercial and industrial temperature ranges.

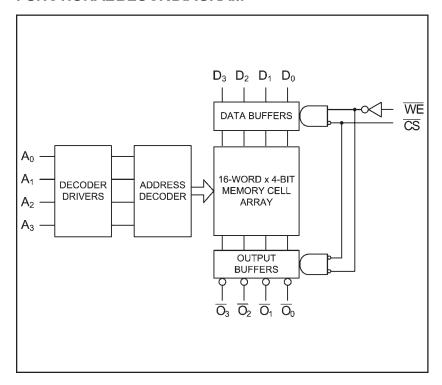

#### **FUNCTIONAL BLOCK DIAGRAM**

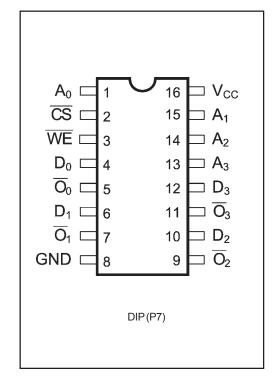

#### **PIN CONFIGURATION**

#### MAXIMUM RATINGS(1)

| Symbol            | Parameter                                               | Value                           | Unit |

|-------------------|---------------------------------------------------------|---------------------------------|------|

| V <sub>cc</sub>   | Power Supply Pin with Respect to GND                    | -0.5 to +7                      | V    |

| V <sub>TERM</sub> | Terminal Voltage with<br>Respect to GND<br>(up to 7.0V) | -0.5 to<br>V <sub>cc</sub> +0.5 | V    |

| T <sub>A</sub>    | Operating Temperature                                   | -55 to +125                     | °C   |

| Symbol            | Parameter                 | Value       | Unit |

|-------------------|---------------------------|-------------|------|

| T <sub>BIAS</sub> | Temperature Under<br>Bias | -55 to +125 | °C   |

| T <sub>STG</sub>  | Storage Temperature       | -65 to +150 | °C   |

| I <sub>OUT</sub>  | DC Output Current         | 20          | mA   |

#### RECOMMENDED OPERATING CONDITIONS

| Grade <sup>(2)</sup> | Ambient Temp  | Gnd | Vcc       |

|----------------------|---------------|-----|-----------|

| Commercial           | 0°C to 70°C   | 0V  | 5.0V ±10% |

| Industrial           | –40°C to 85°C | 0V  | 5.0V ±10% |

# CAPACITANCES<sup>(4)</sup>

$(V_{CC} = 5.0V, T_A = 25^{\circ}C, f = 1.0MHz)$

| Symbol           | Parameter          | Conditions            | Тур. | Unit |

|------------------|--------------------|-----------------------|------|------|

| C <sub>IN</sub>  | Input Capacitance  | V <sub>IN</sub> = 0V  | 5    | pF   |

| C <sub>OUT</sub> | Output Capacitance | V <sub>OUT</sub> = 0V | 7    | рF   |

#### DC ELECTRICAL CHARACTERISTICS

Over recommended operating temperature and supply voltage<sup>(2)</sup>

|                 |                                  | Test Conditions                                             |            | P40  | C189 |       |

|-----------------|----------------------------------|-------------------------------------------------------------|------------|------|------|-------|

| Symbol          | Parameter                        | rest oonditi                                                | 0113       | Min. | Max. | Unit  |

| V <sub>OH</sub> | Output High Voltage              | $V_{CC} = Min., V_{IN} = V_{IH} \text{ or } V_{IL}, I_{OH}$ | = -3.0 mA  | 2.4  |      | V     |

| V <sub>OL</sub> | Output Low Voltage               | $V_{CC} = Min., V_{IN} = V_{IH} \text{ or } V_{IL}, I_{OL}$ | = 24 mA    |      | 0.5  | V     |

| V <sub>IH</sub> | Input High Level                 |                                                             |            | 2.0  |      | V     |

| V <sub>IL</sub> | Input Low Level                  |                                                             |            |      | 0.8  | V     |

| I               | I <sub>I</sub> Input Low Current | $V_{IN} = 0.5 \text{ V (except } \overline{CS})$            |            |      | -0.6 | mA    |

| 'IL             | input Low Guirent                | $V_{IN} = 0.5 \text{ V } (\overline{CS})$                   |            |      | -1.2 | 111/3 |

| I <sub>IH</sub> | Input High Current               | $V_{CC}$ = Max, $V_{IN}$ = 2.7V                             |            |      | 5    | μΑ    |

| I <sub>sc</sub> | Output Short Circuit<br>Current  | V <sub>CC</sub> = Max., V <sub>OUT</sub> = 0.0V             |            | -150 | -60  | mA    |

|                 | Power Supply Current             | wer Supply Current $V_{cc} = Max.$ Commercial Industrial    | Commercial |      | 55   | A     |

| I <sub>cc</sub> | 1 ower ouppry ourrent            |                                                             | Industrial |      | 70   | — mA  |

| I <sub>L</sub>  | Output Leakage Current           | $V_{OUT} = V_{CC}$ , $V_{CC} = Max$ .                       | •          |      | 50   | μΑ    |

#### Notes:

- 1. Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to MAXIMUM rating conditions for extended periods may affect reliability.

- 2. Extended temperature operation guaranteed with 400 linear feet per minute of air flow.

- 3. Transient inputs with  $V_{\parallel}$  and  $I_{\parallel}$  not more negative than -3.0V and -100mA, respectively, are permissible for pulse widths up to 20 ns.

- 4. This parameter is sampled and not 100% tested.

- 5.  $\overline{\text{CE}}$  is LOW and  $\overline{\text{WE}}$  is HIGH for READ cycle.

- WE is HIGH, and address must be valid prior to or coincident with CE transition LOW.

- Transition is measured ±200mV from steady state voltage prior to change with specified loading in Figure 1. This parameter is sampled and not 100% tested.

- 8. Read Cycle Time is measured from the last valid address to the first transitioning address.

#### **FUNCTIONAL DESCRIPTION**

An active LOW write enable  $(\overline{WE})$  controls the writing/reading operation of the memory. When chip select  $(\overline{CS})$  and write enable  $(\overline{WE})$  are LOW, the information on data inputs  $(D_0$  through  $D_3$ ) is written into the addressed memory word. Reading is performed with chip select  $(\overline{CS})$  LOW and write enable  $(\overline{WE})$  HIGH. The information stored in the

addressed word is read out on the inverting outputs  $(\overline{O_0})$  through  $\overline{O_3}$ ). The outputs of the memory go to an inactive high impedance state whenever chip select  $(\overline{CS})$  is HIGH, or during the write operation when write enable  $(\overline{WE})$  is LOW.

#### TRUTH TABLE

| Mode    | <del>CS</del> | WE | Output           |

|---------|---------------|----|------------------|

| Standby | Н             | Х  | HighZ            |

| Read    | L             | Н  | D <sub>out</sub> |

| Write   | L             | L  | HighZ            |

Notes: H = HIGH L = Low

X = Don't Care

HIGH Z = Implies outputs are disabled or off. This condition is defined as high impedance state.

#### AC CHARACTERISTICS—READ CYCLE

$(V_{CC} = 5V \pm 10\%, All Temperature Ranges)^{(2)}$

| Sym.            | Parameter                        | -35 |     | Unit  |

|-----------------|----------------------------------|-----|-----|-------|

| Oyiii.          | i arameter                       | Min | Max | Oilit |

| t <sub>RC</sub> | Read Cycle Time                  | 35  |     | ns    |

| t <sub>AA</sub> | Address Access Time              |     | 35  | ns    |

| t <sub>AC</sub> | Chip Enable Access Time          |     | 15  | ns    |

| t <sub>oh</sub> | Output Hold from Address Change  | 2   |     | ns    |

| t <sub>LZ</sub> | Chip Enable to Output in Low Z   | 2   |     | ns    |

| t <sub>HZ</sub> | Chip Disable to Output in High Z |     | 10  | ns    |

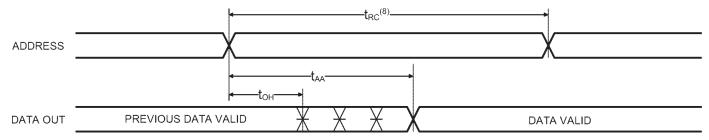

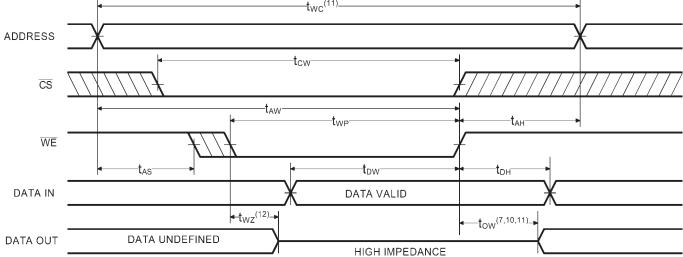

#### TIMING WAVEFORM OF READ CYCLE NO. 1(5)

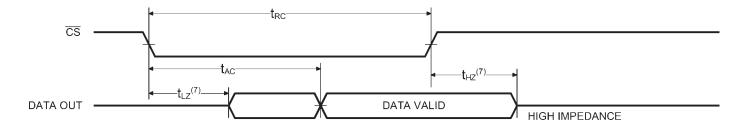

# TIMING WAVEFORM OF READ CYCLE NO. 2 (6)

#### AC CHARACTERISTICS—WRITE CYCLE

$(V_{CC} = 5V \pm 10\%, All Temperature Ranges)^{(2)}$

|                 |                                     | -3  | 5   | I Innit |

|-----------------|-------------------------------------|-----|-----|---------|

| Sym.            | Parameter                           | Min | Max | Unit    |

| t <sub>wc</sub> | Write Cycle Time                    | 35  |     | ns      |

| t <sub>cw</sub> | Chip Enable Time to End of Write    | 15  |     | ns      |

| t <sub>AW</sub> | Address Valid to End of Write       | 15  |     | ns      |

| t <sub>AS</sub> | Address Set-up Time                 | 0   |     | ns      |

| t <sub>wp</sub> | Write Pulse Width                   | 15  |     | ns      |

| t <sub>AH</sub> | Address Hold Time from End of Write | 2   |     | ns      |

| t <sub>DW</sub> | Data Valid to End of Write          | 15  |     | ns      |

| t <sub>DH</sub> | Data Hold Time                      | 2   |     | ns      |

| t <sub>wz</sub> | Write Enable to Output in High Z    |     | 15  | ns      |

| t <sub>ow</sub> | Output Active from End of Write     | 0   |     | ns      |

# TIMING WAVEFORM OF WRITE CYCLE NO. 2 (CS CONTROLLED)(9)

DATA OUT HIGH IMPEDANCE

#### Notes:

- 9. CS and WE must be LOW for WRITE cycle.

10. If CS goes HIGH simultaneously with WE high, the output remains in a high impedance state.

- 11. Write Cycle Time is measured from the last valid address to the first transition address.

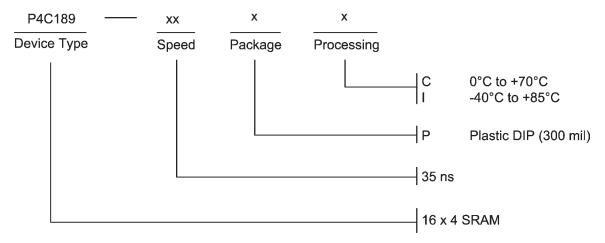

# ORDERING INFORMATION

# **SELECTION GUIDE**

The P4C189 is available in the following temperature range, speed, and package options.

| Temperature Range      | Packago     | Speed (ns) |  |

|------------------------|-------------|------------|--|

| Temperature Kange      | Package     |            |  |

| Commercial Temperature | Plastic DIP | -35PC      |  |

| Industrial Temperature | Plastic DIP | -35PI      |  |

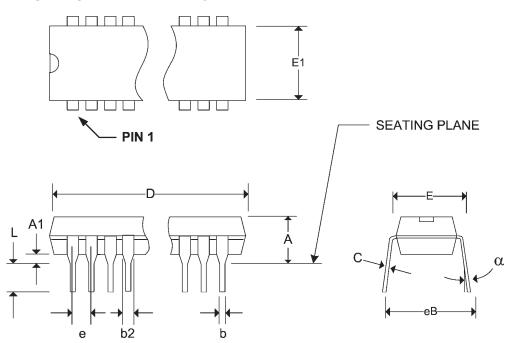

| Pkg#   | P7     |         |  |

|--------|--------|---------|--|

| # Pins | 16 (30 | 00 mil) |  |

| Symbol | Min    | Max     |  |

| Α      | 0.145  | 0.200   |  |

| A1     | 0.020  | -       |  |

| b      | 0.014  | 0.023   |  |

| b2     | 0.040  | 0.060   |  |

| С      | 0.008  | 0.016   |  |

| D      | 0.740  | 0.780   |  |

| E1     | 0.240  | 0.260   |  |

| E      | 0.300  | 0.320   |  |

| е      | 0.100  | BSC     |  |

| eB     | 0.310  | 0.365   |  |

| L      | 0.125  | 0.150   |  |

| α      | 0°     | 15∘     |  |

# PLASTIC DUAL IN-LINE PACKAGE

# **REVISIONS**

DOCUMENT NUMBER: SRAM100 DOCUMENTTITLE: P4C189 HIGH SPEED 16 x 4 Static CMOS RAM with inverting outputs ISSUE ORIG. OF REV. **DESCRIPTION OF CHANGE CHANGE** DATE OR Oct-05 JDB New Data Sheet