### Stereo FM Receiver Radio-on-a-Chip™

### KT0830E

#### Features

Low-cost true single-chip FM radio solution Single-Chip Low IF FM Receiver Direct band, volume, frequency selection Digital FM Demodulator Digital Stereo Processor Low-noise PLL with integrated VCO Extended FM band support (64-109MHz)

Extended FM band support (64-109MHz) Integrated Class AB headphone driver High Fidelity

SNR: 64dB THD: <0.3%

High Sensitivity: -106dBm

Low supply current

19.5mA (operating), <20uA (standby)

High Driving capability

Drive up to 16 ohm load (single-sided)

32.768kHz reference clock/crystal

Automatic Frequency Control (AFC)

Automatic gain control (AGC)

Anti-pop circuit

16-pin SOP package

#### Applications

Single chip FM radio used in PMP, boom box, sporting devices, medical devices and etc

#### Rev. 1.1

Information furnished by KT Micro is believed to be accurate and reliable. However, no responsibility is assumed by KT Micro for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of KT Micro, Inc.

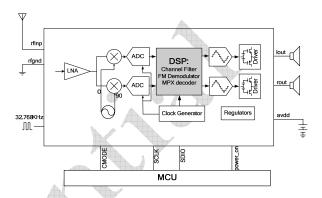

Figure 1: System Diagram

### Description

The KT0830E is a high-quality Monolithic Digital FM Receiver designed to playback high-fidelity FM broadcasting signals under various conditions.

The KT0830E offers a true single-chip FM radio solution. There are no external filters or frequency-tuning devices thanks to a proprietary digital low-IF architecture, a fully-integrated LNA, automatic gain control (AGC), high-performance ADCs, high-quality analog and digital filters, and an on-chip low-noise self-tuning VCO. The on-chip high-fidelity Class-AB driver further eliminates the need for any external audio amplifiers and can drive stereo headphones directly

The on-chip LDO regulator allows the chip to operate with power supply ranging from 1.8 V to 3.6V consuming merely 19mA in full operation mode and less than 20uA when standby – greatly extending the battery life.

The small footprint, high integration level and great flexibility make KT0830E for any standalone FM radio applications.

KT Micro Inc., 22391 Gilberto, Suite D Rancho Santa Margarita, CA 92688

Tel: 949.713.4000 <u>http://www.ktmicro.com.cn</u>

Fax: 949.713.4004 Copyright ©2009, KT Micro, Inc.

### Electrical specification

**Table 1: FM Receiver Characteristics**

(Unless otherwise noted Tj =  $-20\sim110$  °C, AVDD =2.0V to 3.6V)

| Parameter                                                                         | Symbol   | Test/Operating<br>Condition | Min  | Тур    | Max | Units       |

|-----------------------------------------------------------------------------------|----------|-----------------------------|------|--------|-----|-------------|

| FM Frequency Range                                                                | $F_{rx}$ |                             | 64   |        | 109 | MHz         |

| Sensitivity <sup>1,2,3</sup>                                                      | Sen      | (S+N)/N=26dB                |      | 2.2    | 3.5 | uVemf       |

| Input referred 3 <sup>rd</sup> Order<br>Intermodulation Production <sup>4,5</sup> | IIP3     |                             |      | 87     |     | dBuVE<br>MF |

| Adjacent Channel Selectivity                                                      |          | ±200KHz                     | 40   |        | 51  | dB          |

| Alternate Channel Selectivity                                                     |          | ±400KHz                     | 50   |        | 70  | dB          |

| Image Rejection Radio                                                             |          |                             |      | 35     |     | dB          |

| AM suppression                                                                    |          |                             |      | 50     |     | dB          |

| RCLK frequency                                                                    |          |                             |      | 32.768 |     | kHz         |

| RCLK frequency Tolerance                                                          |          |                             | -150 | A      | 150 | ppm         |

| Audio Output Voltage <sup>1,2,3,4</sup>                                           |          | 32ohm load                  | 68   | 70     | 72  | $mV_{RMS}$  |

| Audio Band Limits <sup>1,2,4</sup>                                                |          | $\pm 3dB$                   | 30   |        | 15k | Hz          |

| Audio Stereo Separation 1,4,6                                                     |          |                             | 35   |        |     | dB          |

| Audio Stereo S/N <sup>1,4,6,7</sup>                                               |          |                             |      | 64     |     | dB          |

| Audio THD <sup>1,2,4,6</sup>                                                      |          | <i>P</i>                    |      | 0.3    |     | %           |

| Audio Common Mode Voltage                                                         |          |                             |      | 0.7    |     | V           |

| Audio Output Load Resistance                                                      | $R_{L}$  | Single-ended                | 16   |        |     | Ω           |

| Seek/Tune Time<br>(effective channel)                                             |          |                             |      |        | 50  | ms/ch       |

| Power-up Time                                                                     |          |                             |      |        | 380 | ms          |

#### Notes:

- 1. FMOD=1kHz, 75us de-emphasis

- 2. MONO=1

- 3. △F=22.5kHz

- 4.  $V_{EMF}=1$ mV, Frx=70MHz~110MHz 5. AGCD=1

- △F=75kHz

- VOLUME<3:0>=1111

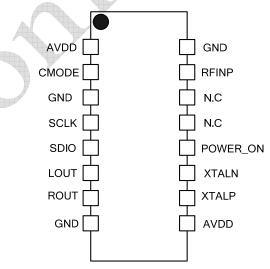

### 2 Pin List

A 16-pin SOP package is used. The chip IO pin-out is listed in Table 2.

#### Table 2 Pin-Out

| Pin Index | Name     | I/O Type      | Function                                        |

|-----------|----------|---------------|-------------------------------------------------|

| 1         | AVDD     | Power         | Power supply                                    |

| 2         | CMODE    | Digital Input | High: 5767 Mode (Register map compatible        |

|           |          |               | with TEA5767 and has the same feature set as    |

|           |          |               | TEA5767)                                        |

|           |          |               | Low: Full Functional Mode (Register map is      |

|           |          |               | self-defined and provides full set of features) |

| 3         | GND      | Ground        | Ground                                          |

| 4         | SCLK     | Digital Input | I2C clock input.                                |

| 5         | SDIO     | Digital IO    | I2C data input/output                           |

| 6         | LOUT     | Analog output | Left channel output with 16 ohm driving         |

|           |          |               | capability.                                     |

| 7         | ROUT     | Analog output | Right channel output with 16 ohm driving        |

|           |          |               | capability.                                     |

| 8         | GND      | Ground        | Ground                                          |

| 9         | AVDD     | Power         | 2.0V - 3.6V power supply.                       |

| 10        | XTALP    | Analog IO     | 32.768KHz crystal input or 32.768KHz            |

|           |          |               | reference clock input                           |

| 11        | XTALN    | Analog IO     | 32.768KHz crystal input                         |

| 12        | POWER_ON | Digital Input | High for normal operating mode and low for      |

|           |          |               | standby mode.                                   |

| 13        | N.C.     | N.C.          | No Connection                                   |

| 14        | N.C.     | N.C.          | No Connection                                   |

| 15        | RFINP    | Analog Input  | RF signal input. External AC coupling cap is    |

|           |          |               | not required                                    |

| 16        | GND      | Ground        | Ground                                          |

Figure 2: Pin out

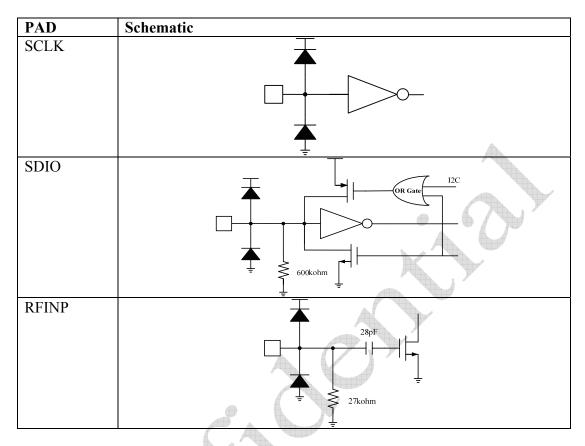

**Table 3: I/O Pin Configuration**

### 3 Functional Description

#### 3.1 Overview

The KT0830E offers a true single-chip FM radio solution by virtually eliminating all the external components. There are no external filters or frequency-tuning devices thanks to a proprietary digital low-IF architecture, a fully-integrated LNA, automatic gain control (AGC), high-performance ADCs, high-quality analog and digital filters, and an on-chip low-noise self-tuning VCO. The on-chip high-fidelity Class-AB driver further eliminates the need for any external audio amplifiers and can drive stereo headphones directly.

#### 3.2 FM Receiver

A high performance digital-IF structure receiver is used in KT0830E to convert RF signal to IF signal. The received IF signal is digitized by a high resolution analog to digital converter (ADC) and all the following signal processing including channel filtering, FM demodulation, stereo decoding is performed digitally. In order to improve the dynamic range of the RF signal, an automatic gain control (AGC) loop is used together with the low noise amplifier (LNA). KT0830E also provides configurations for various types of antenna such as short antenna, long antenna or headphone (audio wire) antenna through register ANTTYP<1:0>.

### 3.3 Digital Signal Processing

#### 3.3.1 Stereo Decoder

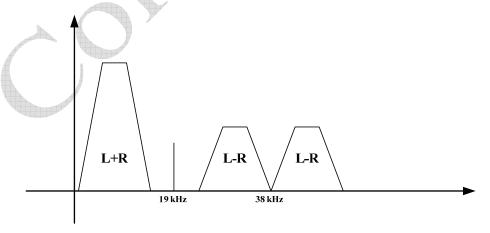

The digitized IF signal is fed to the FM demodulator which demodulates the signal and outputs a digital multiplexed (MPX) signal consisting of L+R audio, L-R audio, 19kHz pilot tone. The left channel signal and the right channel signal can be extracted from the MPX signal by simply adding and subtracting the L+R signal and L-R signal. The spectrum diagram is shown in Figure 3.

Figure 3: Spectrum diagram of the MPX signal

#### 3.3.2 Mute

KT0830E can be hard muted by setting MUTE\_B to 0 and the output of the audio signal is set to the common mode voltage.

There is also a Soft Mute feature that is enabled by setting SMUTE\_B to 0. In this mode, the audio volume is gradually attenuated when the signal reception is bad (i.e. when the RSSI is below a certain level as defined by SMTH<1:0>.) The attenuation attack rate and depth can be configured through SMUTER<1:0> and SMUTEA<1:0>, respectively.

### 3.3.3 Stereo / Mono Blending

In order to provide a comfortable listening experience, KT0830E blends the stereo signal with mono signal gradually when in weak reception. The signal level range over which the blending occurs is set by BLNDADJ<1:0>. The blending is disabled when DBLND is set to 1. MONO playback mode can also be forced by setting the MONO to 1.

### 3.3.4 Bass Boosting

KT0830E provides a digital audio enhancement feature, bass boosting. The gain of the bass boost can be programmed through BASS<1:0> (Reg0x04<9:8>). With BASS<1:0>=00, this feature is disabled.

### 3.4 Stereo DAC, Audio Filter and Driver

Two high-quality single-bit  $\Delta\Sigma$  audio digital to analog converters (DAC) are integrated along with high-fidelity analog audio filters and class AB drivers. Headphones and speakers with impedance as low as 160hms can be directly driven without external audio drivers. An integrated anti-pop circuit eliminates the click-and-pop sound during power up and power down.

#### 3.5 SEEK/TUNE

The fully integrated LO synthesizer supports wide band operation from 64MHz to 110MHz. The reference clock is 32.768 kHz with frequency tolerance of  $\pm 100$ ppm. The chip begins to directly TUNE to a channel when the register TUNE is set to 1. The channel frequency can be programmed and tuned by setting CHAN<9:0> and can be defined as

Freq(MHz) =

$$50 \text{ kHz} \times \text{CHAN} < 9:0 > +64 \text{ MHz}$$

The SEEK process is started by setting SEEK to "1". The seek direction is determined by SEEKUP. The band edges are determined by BAND<1:0> and the seek step is set by SPACE<1:0>. KT0830E automatically seeks and tunes to the first satisfying station. The seeking criterion is set by SEEKTH<3:0>. If no qualified channel is found, the FM receiver returns to the original channel and SF/BL bit is set to "1". When AUTOTUNE bit is set to 1, the chip will automatically tune to the found channel, otherwise, the chip will remain mute after seek is completed. During the seeking, the current channel can be read out from READCH<9:0> bits.

### 3.6 Power on Sequence

KT0830E is powered up by pulling the POWER\_ON pin to high. One needs to wait for 400ms before he/she can configure the chip through the serial interface.

#### 4 Control Interface- I2C

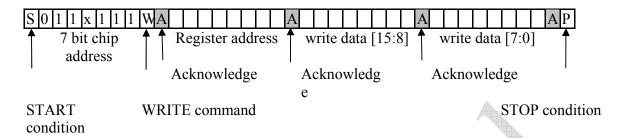

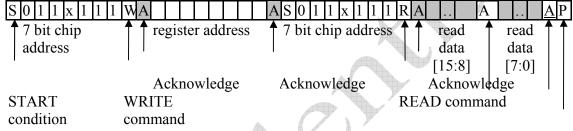

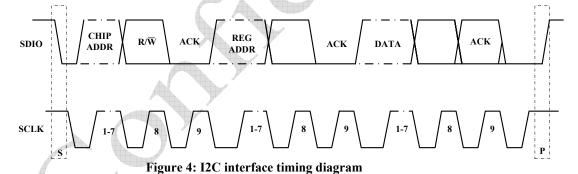

I2C bus mode uses SCLK and SDIO to transfer data. The device always drives data to SDIO at the falling edge of SCLK and captures data from SDIO at the rising edge of SCLK. The device acknowledges the external controller by driving SDIO low at the falling edge of SCLK. Data transfer always begins with START condition and ends with STOP condition. The external controller can read/write one 16-bits data at the specified address or read/write desired number of registers data continuously from the specified address till when STOP condition is occurred.

For write operations, external controller should send command & data in the following sequence: START condition -> 7 bit chip address and Write command ("0") -> 8 bit register address n -> write data n [15:8] -> write data n [7:0] -> write data n+1 [15:8] -> write data n+1 [7:0] -> ...... -> STOP condition.

For read operations, external controller should send command & data in the following sequence: START condition -> 7 bit chip address and Write command ("0") -> 8 bit register address n -> 7 bit chip address and Read command ("1"), then device will send read data n [15:8] -> read data n [7:0] -> read data n+1 [15:8] -> read data n+1 [7:0] -> ...... till STOP condition.

# Table 4: 12C Interface Protocol RANDOM REGISTER WRITE PROCEDURE

#### RANDOM REGISTER READ PROCEDURE

NO Acknowledge STOP condition

Note: The data bits in gray color are sent by KT0830E

# 5 Register Map

| Reg No | 00h DEVICE | 01h CHIPID | 02h SEEK     | 03h TUNE                 | 04h VOLUME  | 05h DSPCFGA  | 09h RFCFG   | 0Ah LOCFGA    | 0Fh SYSCFG | 12h STATUSA | 13h STATUSB | 14h STATUSC     |

|--------|------------|------------|--------------|--------------------------|-------------|--------------|-------------|---------------|------------|-------------|-------------|-----------------|

| Name   | E          | a          |              |                          |             |              | 7.5         | 3A            | 5          |             | SB          | SC              |

| DIS    |            |            | SEEK         | TUNE                     | SMUTE_B     | MONO         |             |               |            | XTAL_OK     |             |                 |

| DI4    | PN<3:0     |            | SEEKDIR      |                          | MUTE_B      |              |             | AF            | SFTRST     | STC         |             |                 |

| DI3    | 3:0>       | RE V<      |              | AUTOVOL AUTOTUN<br>_EN E | SMUTER<1:0> |              |             | AFCRANGE<2:0> | STCIEN     | SF          |             |                 |

| DIZ    |            | REV<5:0>   |              | AUTOTUN                  | R<1:0>      |              |             | <0            |            |             |             |                 |

| DI 1   |            |            |              |                          | SMUTE       | DE           |             |               |            |             |             |                 |

| D10    |            |            | 01           |                          | SMUTEA<1:0> |              |             |               | SEEKMD     |             |             |                 |

| 6Q     |            |            | SEEKTH<4:0>  |                          | BASS        | BLNDA        | ANTIY       |               |            | >LS         |             |                 |

| D8     |            |            |              |                          | BASS<1:0>   | BLNDADJ<1:0> | ANTTYP<1:0> | AFCD          |            | ST<1:0>     |             |                 |

| D7     |            |            |              |                          |             |              |             |               |            |             |             |                 |

| 9Q     | MFID       |            |              |                          |             |              |             | ISTH          |            |             |             |                 |

| SO     | MFID<11:0> |            | FM_BAN       | CHAN<9>0>                | SMTH<1:0>   | DBLND        |             |               |            | RSSI<4:0>   | RDCHAN<9:0> |                 |

| D4     |            |            | FM_BAND<1:0> | <0<6>                    | <[:0>       |              |             |               |            |             | <0:6>N      |                 |

| D3     |            |            | SPACE<1:0>   |                          |             |              |             |               |            |             |             | AFC DELTAF<5:0> |

| D2     |            |            | <0:1>        |                          | VOLUME<3:0> |              |             |               |            |             |             | AF<5:0>         |

| DI     |            |            |              |                          | 3<3:0>      |              |             |               |            |             |             |                 |

| 2      |            |            |              |                          |             |              |             |               |            |             |             |                 |

The register bank stores channel frequency codes, calibration parameters, operation status, mode and power controls, which can be accessed by the internal digital controller, state machines and external micro controllers through the serial interface.

All registers are 16 bits wide. Control logics are active high unless specifically noted. All the registers are automatically set to default values after the chip is powered-on or reset.

### 5.1 Device ID Register (Reg 0x00)

| Bit   | Symbol      | Access | Default | <b>Functional Description</b> |

|-------|-------------|--------|---------|-------------------------------|

| 15:12 | PN<3:0>     | R      |         | Part Number                   |

|       |             |        |         | 1011=FM Receiver              |

| 11:0  | MFGID<11:0> | R      |         | Manufacturer ID               |

### 5.2 CHIP ID (Reg 0x01)

| Bit   | Symbol   | Access | Default | <b>Functional Description</b> |

|-------|----------|--------|---------|-------------------------------|

| 15:10 | REV<5:0> | R      |         | Reserved                      |

| 9     | Reserved | R      |         | Reserved                      |

| 8:6   | Reserved | R      |         | Reserved                      |

| 5:0   | Reserved | R      |         | Reserved                      |

### 5.3 Seek Configuration (Reg 0x02)

| Bit   | Symbol       | Access | Default | <b>Functional Description</b>              |

|-------|--------------|--------|---------|--------------------------------------------|

| 15    | SEEK         | RW     | 0       | Seek enable                                |

|       |              | A      |         | 0 = Disable                                |

|       |              |        |         | 1 = Enable                                 |

| 14    | SEEKDIR      | RW     | 0       | Seek direction                             |

|       |              |        |         | 0 = Seek down                              |

|       |              |        |         | 1 = Seek up                                |

| 13:12 | Reserved     |        | 10      |                                            |

| 11:7  | SEEKTH<4:0>  | RW     | 00110   | Seek Threshold                             |

|       | A ( )        |        |         | 00000 = most sensitive                     |

|       |              |        |         | 11111 = least sensitive                    |

| 6     | Reserved     |        | 0       |                                            |

| 5:4   | FM_Band<1:0> | RW     | 00      | <b>Band Selection (For seek operation)</b> |

|       |              |        |         | 00 = 87-108MHz (USA, Europe)               |

|       |              |        |         | 01 = 76-108MHz (Japan wide band)           |

|       |              |        |         | 10 = 76-90MHz (Japan).                     |

|       |              |        |         | 11 = reserved                              |

| 3:2   | SPACE<1:0>   | RW     | 00      | Channel spacing                            |

|       |              |        |         | 00 = 200KHz (US, Europe)                   |

|       |              |        |         | 01 = 100KHz (Europe, Japan)                |

|       |              |        |         | 10 = 50 KHz                                |

| 1:0   | Reserved     |        | 11      |                                            |

### 5.4 TUNE Register (Reg 0x03)

| Bit   | Symbol     | Access | Default | Functional Description                 |

|-------|------------|--------|---------|----------------------------------------|

| 15    | Tune       | RW     | 0       | Tune Enable                            |

|       |            |        |         | 0 = Disable                            |

|       |            |        |         | 1 = Enable                             |

| 14    | Reserved   |        | 0       |                                        |

|       |            |        |         |                                        |

| 13    | AUTOVOL_EN | RW     | 0       | Automatic Volume Control               |

|       |            |        |         | 1 = enable                             |

| 12    | AUTOTUNE   | RW     | 1       | Automatic tune control                 |

|       |            |        |         | 0 = Will NOT tune after a successful   |

|       |            |        |         | seek until a separated Tune command is |

|       |            |        |         | received from the control interface    |

|       |            |        |         | 1 = Automatically starts Tune process  |

|       |            |        |         | after Seek                             |

| 11:10 | Reserved   |        | 10      |                                        |

|       |            |        |         |                                        |

| 9:0   | Chan<9:0>  | RW     | 1CC     | Tune Channel Value                     |

# 5.5 VOLUME Control Register (Reg 0x04)

| Bit   | Symbol      | Access | Default | <b>Functional Description</b>    |

|-------|-------------|--------|---------|----------------------------------|

| 15    | SMUTE_B     | RW     | 1       | Softmute Disable                 |

|       |             |        |         | 0 = Softmute enable              |

|       |             |        |         | 1 = Softmute disable             |

| 14    | MUTE_B      | RW     | 0       | Hard Mute Disable                |

|       | 4           |        |         | 0 = Mute enable                  |

|       |             |        |         | 1 = Mute disable                 |

| 13:12 | SMUTER<1:0> | RW     | 00      | Softmute Attack/Recover Rate     |

|       |             | 7      |         | 0 = Slow                         |

|       |             |        |         | 01 = Slowest                     |

|       |             |        |         | 10 = Fastest                     |

| A     |             |        |         | 11 = Fast                        |

| 11:10 | SMUTEA<1:0> | RW     | 00      | Softmute Attenuation             |

|       |             |        |         | 00 = Strong                      |

|       |             |        |         | 01 = Strongest                   |

|       |             |        |         | 10 = Weak                        |

|       |             |        |         | 11 = Weakest                     |

| 9:8   | BASS<1:0>   | RW     | 00      | Bass boost effect mode selection |

|       |             |        |         | 00 = Disable                     |

|       |             |        |         | 01 = Low                         |

|       |             |        |         | 10 = Med                         |

|       |             |        |         | 11 = High                        |

| 7:6   | Reserved    |        | 00      |                                  |

| 5:4 | SMTH<1:0>   | RW | 10   | Soft mute start level<br>00 = Highest<br>01 = High<br>10 = Low<br>11 = Lowest                       |

|-----|-------------|----|------|-----------------------------------------------------------------------------------------------------|

| 3:0 | VOLUME<3:0> | RW | 0111 | Volume Control<br>0000 = mute<br>0001 = -42dBFS<br>0010 = -39dBFS<br><br>1110 = -3dBFS<br>1111 = FS |

# 5.6 DSP Configuration Register A (Reg 0x05)

| Bit   | Symbol       | Access | Default | <b>Functional Description</b>        |

|-------|--------------|--------|---------|--------------------------------------|

| 15    | MONO         | RW     | 0       | Mono Select                          |

|       |              |        |         | 0 = Stereo                           |

|       |              |        |         | 1 = Force mono                       |

| 14:12 | Reserved     |        | 101     |                                      |

| 11    | DE           | RW     | 0       | De-emphasis                          |

|       |              | /      | 7       | 0 = 75us. Used in USA.               |

|       |              |        |         | 1 = 50us. Used in Europe, Australia, |

|       |              |        |         | Japan.                               |

| 10    | Reserved     | TA     | 0       |                                      |

| 9:8   | BLNDADJ<1:0> | RW     | 10      | Stereo/Mono Blend Start Level        |

|       | 4            |        |         | 00 = High                            |

|       |              |        |         | 01 = Highest                         |

|       |              |        |         | 10 = Lowest                          |

|       |              |        |         | 11 = Low                             |

| 7:6   | Reserved     |        | 0       |                                      |

| 5     | DBLND        | RW     | 0       | Blend disable                        |

| 4     |              |        |         | 0 = blend enable                     |

|       |              |        |         | 1 = blend disable                    |

| 4:0   | Reserved     |        | 0       |                                      |

# 5.7 RF Configuration (Reg 0x09)

| Bit   | Symbol      | Access | Default  | <b>Functional Description</b> |

|-------|-------------|--------|----------|-------------------------------|

| 15:10 | Reserved    |        | 000001   |                               |

| 9:8   | ANTTYP<1:0> | RW     | 01       | Antenna type selection        |

|       |             |        |          | 00 = Long antenna             |

|       |             |        |          | 01 = earphone/short antenna   |

|       |             |        |          | 10 = Reserved                 |

|       |             |        |          | 11 = Reserved                 |

| 7:0   | Reserved    |        | 00000000 |                               |

### 5.8 LO Synthesizer Configuration A (Reg 0x0A)

| Bit   | Symbol        | Access | Default | <b>Functional Description</b>   |

|-------|---------------|--------|---------|---------------------------------|

| 15    | Reserved      |        | 0       | _                               |

| 14:12 | AFCRANGE<2:0> | RW     | 000     | AFC correction range            |

|       |               |        |         | 000 = 12KHz                     |

|       |               |        |         | 001 = 15 KHz                    |

|       |               |        |         | 010 = 14KHz                     |

|       |               |        |         | 011 = 17KHz                     |

|       |               |        |         | 100 = 16 KHz                    |

|       |               |        |         | 101 = 19KHz                     |

|       |               |        |         | 110 = 22KHz                     |

|       |               |        |         | 111 = 25KHz                     |

| 11:9  | Reserved      |        | 000     |                                 |

| 8     | AFCD          | RW     | 1       | AFC disable control bit         |

|       |               |        |         | 0 = AFC enable                  |

|       |               |        |         | 1 = AFC disable                 |

| 7     | Reserved      |        | 0       |                                 |

| 6     | HLSI          | RW     | 0       | High side or low side injection |

|       |               |        |         | 1 = high side injection         |

|       |               |        |         | 0 = low side injection          |

| 5:0   | Reserved      |        | 000000  |                                 |

# 5.9 Misc Reg (Reg 0x0D)

| Bit  | Symbol   | Access | Default | <b>Functional Description</b> |

|------|----------|--------|---------|-------------------------------|

| 15:1 | Reserved |        | 0x0     |                               |

| 0    | Reserved | TA     | 1       |                               |

### 5.10 System Configuration Register (Reg 0x0F)

| Bit      | Symbol   | Access | Default | Functional Description       |

|----------|----------|--------|---------|------------------------------|

| 15       | Reserved |        | 0       |                              |

| 14       | SFTRST   | RW     | 0       | Soft reset bit               |

|          |          |        |         | 0 = normal operation         |

|          |          | *      |         | 1 = soft reset               |

| 13       | STCIEN   | RW     | 0       | Seek/Tune Complete Interrupt |

| 4        | 1        |        |         | Enable                       |

|          |          |        |         | 0 = Disable Interrupt        |

| <b>\</b> |          |        |         | 1 = Enable Interrupt         |

| 12:11    | Reserved |        | 01      |                              |

| 10       | SEEKMD   | RW     | 0       | Seek mode selection          |

|          |          |        |         | 0 = cycling seek             |

|          |          |        |         | 1 = stop at the band edge.   |

| 9        | Reserved |        | 1       |                              |

| 8:0      | Reserved |        | 0       |                              |

### 5.11 Status Register A (Reg 0x12)

| Bit   | Symbol    | Access | Default | Functional Description           |

|-------|-----------|--------|---------|----------------------------------|

| 15:   | Reserved  | R      | 0       |                                  |

| 14    | STC       | RW     | 0       | Seek/Tune Complete               |

|       |           |        |         | 0 = Not Complete                 |

|       |           |        |         | 1 = Complete                     |

|       |           |        |         | This bit can be cleared manually |

| 13    | SF        | R      | 0       | Seek Fail                        |

|       |           |        |         | 0 = Seek successful              |

|       |           |        |         | 1 = Seek failure                 |

| 12:10 | Reserved  |        | 000     |                                  |

| 9:8   | ST<1:0>   | R      | 0       | Stereo indicator                 |

|       |           |        |         | 11 = Stereo                      |

|       |           |        |         | Other= Mono                      |

|       |           |        |         |                                  |

| 7:3   | RSSI<4:0> | R      | 00000   | RSSI value indicator             |

|       |           |        |         | RSSI indication range is from -  |

|       |           |        |         | 100dBm to -7dBm with 3dB         |

|       |           |        |         | resolution, where 00000 means    |

|       |           |        |         | minimum level and 11111 means    |

|       |           |        | A (     | maximum level.                   |

| 2:0   | Reserved  |        | 0       |                                  |

# 5.12 Status Register B (Reg 0x13)

| Bit   | Symbol        | Access | Default | <b>Functional Description</b>          |

|-------|---------------|--------|---------|----------------------------------------|

| 15:10 | Reserved      |        | 000000  |                                        |

| 9:0   | READCHAN<9:0> | R      | 0       | The current Channel                    |

|       |               |        |         | READCHAN<9:0> provides the             |

|       | A             |        |         | current channel during seek or after a |

|       |               | 7      |         | seek or tune operation is completed    |

# 5.13 Status Register C (Reg 0x14)

| Bit  | Symbol           | Access | Default          | <b>Functional Description</b>            |  |

|------|------------------|--------|------------------|------------------------------------------|--|

| 15:6 | Reserved         | R      | 0                |                                          |  |

| 5:0  | AFC_DELTAF<5:0>  | R      | 000000           | Frequency difference between CHAN and    |  |

| 4    |                  |        |                  | received signal, calculated by AFC block |  |

|      |                  |        |                  | in two's complement format. Range is -   |  |

|      |                  |        |                  | 31 to +31. Unit is KHz. This register is |  |

|      | valid when STC=1 |        | valid when STC=1 |                                          |  |

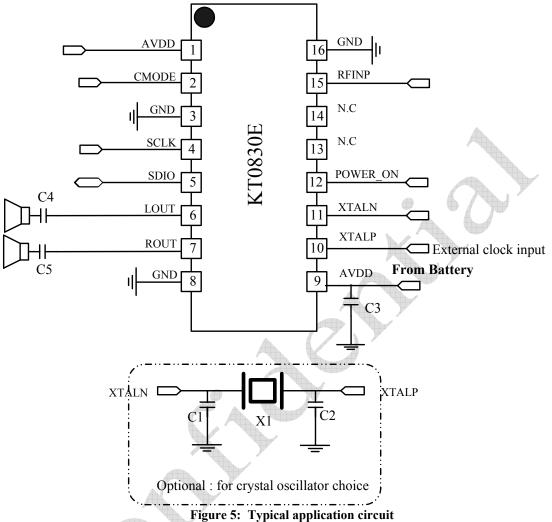

# Application circuit

Note: The decoupling C5 should be closed to Pin 8 and Pin 9.

**Table 5: Bill of Material**

| VIII VIII VIII VIII VIII VIII VIII VII | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |           |

|----------------------------------------|-----------------------------------------|-----------|

| Components                             | Value/Description                       | Suppliers |

| C1,C2                                  | Crystal load capacitor, 20pF            |           |

| C3                                     | Supply decoupling                       |           |

|                                        | capacitor, 0.1uF                        |           |

| C4,C5                                  | AC decoupling capacitor,                |           |

|                                        | 100uF                                   |           |

| X1                                     | 32.768kHz crystal                       |           |

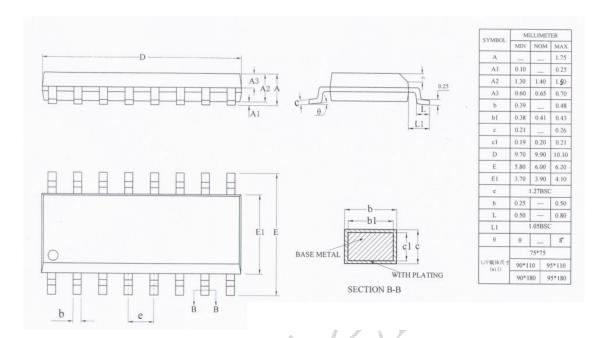

# 7 Package

# 8 Order Information

| Part Number | Description                    | Package | MOQ  |

|-------------|--------------------------------|---------|------|

| KT0830      | Single-chip stereo FM receiver | SOP-16  | 5000 |

### 9 Revision History

V1.0 Official ReleaseV1.1 Update the first page

### 10 Contact Information

#### KT Micro, Inc.

22391 Gilberto, Suite D Rancho Santa Margarita, CA 92688 USA

Tel: 949-713-4000 Fax: 949-713-4004

Email: sales@ktmicro.com

#### 北京昆腾微电子有限公司

北京市海淀区蓝靛厂东路 2 号金源时代商务中心

2号楼 B座 8层 (100089) 电话: 8610-88891955 传真: 8610-88891977

电子邮件: <u>sales@ktmicro.com</u> 网站: http://www.ktmicro.com.cn