# NAND08GAH0A NAND16GAH0D

1 Gbyte, 2 Gbyte, 1.8 V/3 V supply, NAND Flash memories with MultiMediaCard™ interface

Preliminary Data

### **Features**

- Packaged NAND Flash memory with MultiMediaCard interface

- 1, 2 Gbytes of formatted data storage

- eMMC/MultiMediaCard system specification, compliant with V4.1

- Full backward compatibilty with previous MultiMediaCard system specification

- Bus mode

- High-speed MultiMediaCard protocol

- SPI protocol

- Three different data bus widths:1 bit, 4 bits, 8 bits

- Data transfer rate: up to 52 Mbyte/s

- Operating voltage range:

- V<sub>CCQ</sub> =1.8 V/3 V

- $-V_{CC} = 3V$

- Supported clock frequencies: 0 to 52 MHz

- Multiple Block Read (x 8 at 52 MHz): up to 3.5 Mbyte/s

- Multiple Block Write (x 8 at 52 MHz): up to 8.5 Mbyte/s

- Power dissipation

- Standby current: down to 200 µA

- Read current: down to 30 mA

- Write current: down to 30 mA

- Error free memory access

- Internal enhanced data management algorithm (wear levelling, bad block management, garbage collection)

- Internal error correction code

- Data integrity

- Data reliability: less than 1 non-recoverable error per 10<sup>14</sup> bits read

- Endurance: more that 2,000,000 Program/Erase cycles

- Security

- Password protection of data

- Built-in write protection (permanent or temporary)

# **Contents**

| 1 | Desc | cription |                                              | 11 |

|---|------|----------|----------------------------------------------|----|

| 2 | Devi | ce phys  | sical description                            | 13 |

|   | 2.1  | Packag   | ge connections                               | 14 |

|   | 2.2  | Form f   | actor                                        | 14 |

| 3 | Mem  | ory arra | ay partitioning                              | 15 |

| 4 | Mult | iMediaC  | Card interface                               | 16 |

|   | 4.1  | Signal   | ls description                               | 16 |

|   |      | 4.1.1    | Clock (CLK)                                  | 16 |

|   |      | 4.1.2    | Command (CMD)                                | 16 |

|   |      | 4.1.3    | Input/outputs (DAT0-DAT7)                    | 16 |

|   |      | 4.1.4    | V <sub>CC</sub> core supply voltage          | 16 |

|   |      | 4.1.5    | V <sub>SS</sub> ground                       | 16 |

|   |      | 4.1.6    | V <sub>CCQ</sub> input/output supply voltage | 16 |

|   |      | 4.1.7    | V <sub>SSQ</sub> supply voltage              | 17 |

|   | 4.2  | Bus to   | pology                                       | 18 |

|   | 4.3  | Power-   | -up and power-down                           | 19 |

|   |      | 4.3.1    | Power-up                                     | 19 |

|   |      | 4.3.2    | Power-down                                   | 19 |

|   | 4.4  | Electri  | cal specifications                           | 21 |

| 5 | High | speed    | MultiMediaCard operation                     | 24 |

|   | 5.1  | Overvi   | iew                                          | 24 |

|   | 5.2  | Card Id  | dentification mode                           | 25 |

|   |      | 5.2.1    | Card reset                                   | 25 |

|   |      | 5.2.2    | Input/output voltage range validation        | 26 |

|   |      | 5.2.3    | From Busy to Ready state                     | 26 |

|   |      | 5.2.4    | Card Identification process                  | 26 |

|   | 5.3  | Data T   | ransfer mode                                 | 28 |

|   |      | 5.3.1    | Active command set selection                 | 28 |

|   |      | 5.3.2    | High speed mode selection                    | 28 |

|   |      | 5.3.3    | Power class selection                        | 29 |

|   |      |          |                                              |    |

|   |       | 5.3.4     | Bus test procedure                       | 29 |

|---|-------|-----------|------------------------------------------|----|

|   |       | 5.3.5     | Bus width selection                      | 31 |

|   |       | 5.3.6     | Data Read                                | 33 |

|   |       | 5.3.7     | Single Block/Multiple Block Read         | 33 |

|   |       | 5.3.8     | Data Write                               | 34 |

|   |       | 5.3.9     | Single Block/Multiple Block Write        | 35 |

|   |       | 5.3.10    | Group Erase                              | 36 |

|   | 5.4   | Write pr  | otection                                 | 37 |

|   | 5.5   | Device I  | ocking/unlocking (password protection)   | 37 |

|   |       | 5.5.1     | Setting the password                     | 39 |

|   |       | 5.5.2     | Resetting the password                   | 39 |

|   |       | 5.5.3     | Locking the device                       | 40 |

|   |       | 5.5.4     | Unlocking the device                     | 40 |

|   |       | 5.5.5     | Performing a Forced Erase                | 41 |

|   |       | 5.5.6     | Application specific commands            | 41 |

|   | 5.6   | Clock co  | ontrol                                   | 42 |

|   | 5.7   | Error co  | nditions                                 | 43 |

|   |       | 5.7.1     | CRC and illegal commands                 | 43 |

|   |       | 5.7.2     | Read, Write and Erase timeout conditions | 43 |

| 6 | Comn  | nands .   |                                          | 44 |

|   | 6.1   | Comma     | nd classes                               | 44 |

|   | 6.2   | Detailed  | command description                      | 46 |

|   | 6.3   | Device s  | state transition                         | 50 |

| 7 | Respo | onses .   |                                          | 52 |

|   | 7.1   |           | onse (normal response command)           |    |

|   | 7.2   | -         | sponse                                   |    |

|   | 7.3   |           | onse (CID, CSD register)                 |    |

|   | 7.4   | _         | onse (OCR register)                      |    |

|   |       |           |                                          |    |

|   | 7.5   | n4 resp   | oonse (Fast I/O)                         | 53 |

| 8 | Devic | e regist  | ers                                      | 54 |

|   | 8.1   | Operation | on conditions register (OCR)             | 54 |

|   | 8.2   | Card ide  | entification (CID) register              | 55 |

|   | 8.3   | Card sp   | ecific data register (CSD)               | 55 |

|   |       |           |                                          |    |

| 8.3.1   | CSD_STRUCTURE                    |

|---------|----------------------------------|

| 8.3.2   | SPEC_VERS58                      |

| 8.3.3   | TAAC58                           |

| 8.3.4   | NSAC 58                          |

| 8.3.5   | TRAN_SPEED59                     |

| 8.3.6   | CCC59                            |

| 8.3.7   | READ_BL_LEN                      |

| 8.3.8   | READ_BL_PARTIAL60                |

| 8.3.9   | WRITE_BLK_MISALIGN60             |

| 8.3.10  | READ_BLK_MISALIGN60              |

| 8.3.11  | DSR_IMP                          |

| 8.3.12  | C_SIZE60                         |

| 8.3.13  | VDD_R_CURR_MIN, VDD_W_CURR_MIN61 |

| 8.3.14  | VDD_R_CURR_MAX, VDD_W_CURR_MAX61 |

| 8.3.15  | C_SIZE_MULT                      |

| 8.3.16  | ERASE_GRP_SIZE62                 |

| 8.3.17  | ERASE_GRP_MULT62                 |

| 8.3.18  | WP_GRP_SIZE                      |

| 8.3.19  | WP_GRP_ENABLE62                  |

| 8.3.20  | DEFAULT_ECC                      |

| 8.3.21  | R2W_FACTOR62                     |

| 8.3.22  | WRITE_BL_LEN                     |

| 8.3.23  | WRITE_BL_LEN                     |

| 8.3.24  | FILE_FORMAT_GRP63                |

| 8.3.25  | COPY                             |

| 8.3.26  | PERM_WRITE_PROTECT63             |

| 8.3.27  | TMP_WRITE_PROTECT                |

| 8.3.28  | CONTENT_PROT_APP63               |

| 8.3.29  | FILE_FORMAT64                    |

| 8.3.30  | ECC 64                           |

| 8.3.31  | CRC 64                           |

| Extende | ed CSD register                  |

| 8.4.1   | S_CMD_SET                        |

| 8.4.2   | MIN_PERF_a_b_ff                  |

| 8.4.3   | PWR_CL_ff_vvv69                  |

| 8.4.4   | CARD_TYPE                        |

| 8.4.5   | CSD STRUCTURE                    |

8.4

|    |       | 8.4.6     | EXT_CSD_REV                                       | 70 |

|----|-------|-----------|---------------------------------------------------|----|

|    |       | 8.4.7     | CMD_SET                                           | 71 |

|    |       | 8.4.8     | CMD_SET_REV                                       | 71 |

|    |       | 8.4.9     | POWER_CLASS                                       | 71 |

|    |       | 8.4.10    | HS_TIMING                                         | 71 |

|    |       | 8.4.11    | BUS_WIDTH                                         | 71 |

|    | 8.5   | RCA (r    | relative card address) register                   | 72 |

|    | 8.6   | DSR (c    | driver stage register) register                   | 72 |

|    | 8.7   | Status    | register                                          | 72 |

| 9  | Timiı | ngs       |                                                   | 75 |

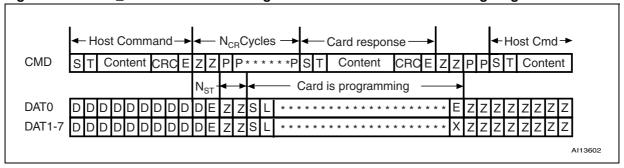

|    | 9.1   | Comma     | and and response timings                          | 76 |

|    |       | 9.1.1     | Card identification and card operation conditions | 76 |

|    |       | 9.1.2     | Assignment of relative card address               | 76 |

|    |       | 9.1.3     | Data Transfer mode                                | 76 |

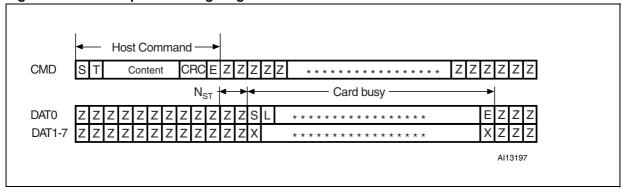

|    |       | 9.1.4     | R1b responses                                     | 77 |

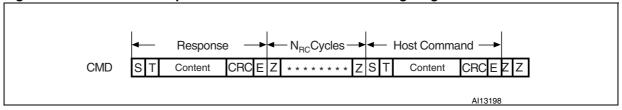

|    |       | 9.1.5     | Last device response to Next Host command         | 77 |

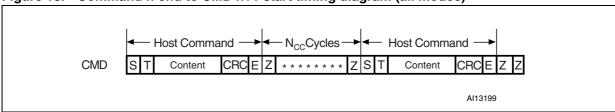

|    |       | 9.1.6     | Last Host command to Next Host command            | 77 |

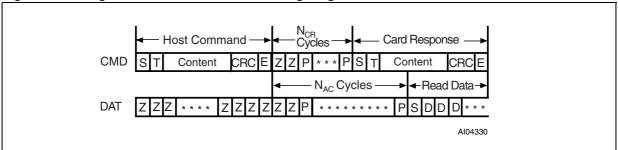

|    | 9.2   | Data R    | lead timings                                      | 78 |

|    |       | 9.2.1     | Single Block Read                                 | 78 |

|    |       | 9.2.2     | Multiple Block Read                               | 78 |

|    | 9.3   | Data W    | Vrite timings                                     | 79 |

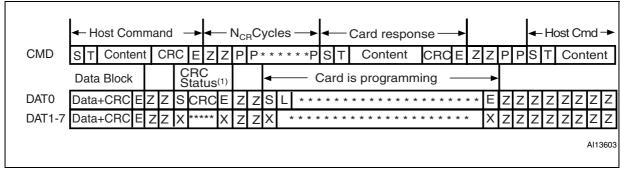

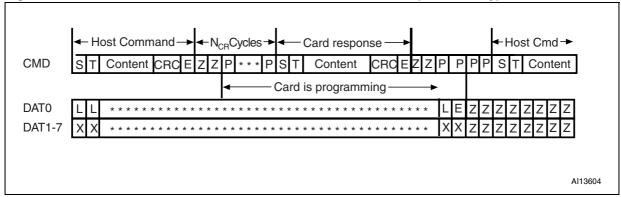

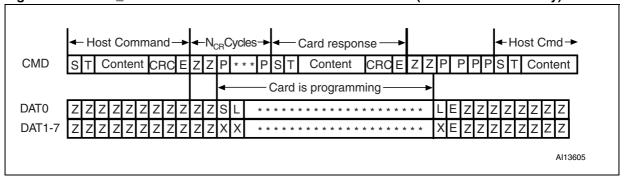

|    |       | 9.3.1     | Single Block Write                                | 79 |

|    |       | 9.3.2     | Multiple Block Write                              | 80 |

|    |       | 9.3.3     | Erase, Set and Clear Write Protect                | 82 |

|    |       | 9.3.4     | Reselecting a busy device                         | 82 |

|    | 9.4   | Bus tes   | st procedure timing                               | 82 |

| 10 | Seria | al periph | neral interface (SPI) mode                        | 83 |

|    | 10.1  | SPI bu    | s topology                                        | 83 |

|    | 10.2  | SPI ele   | ectrical interface                                | 83 |

|    | 10.3  | SPI bu    | s operating conditions                            | 84 |

|    | 10.4  |           | s protocol                                        |    |

|    |       | 10.4.1    | Mode selection                                    |    |

|    |       | 10.4.2    | Bus transfer protection                           |    |

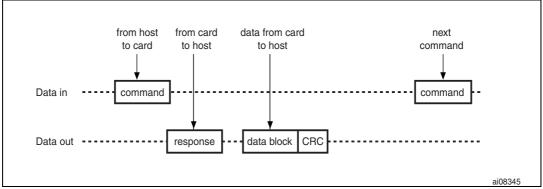

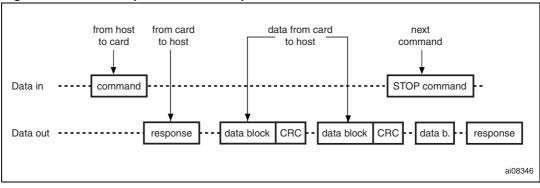

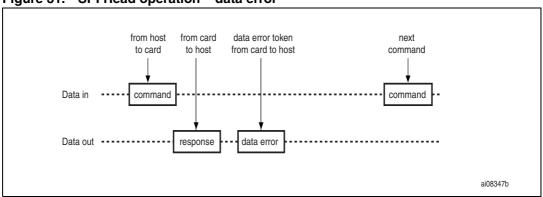

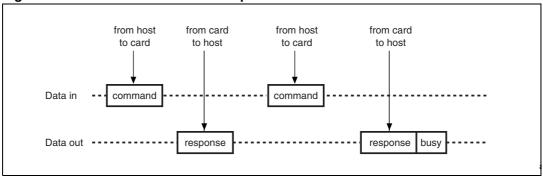

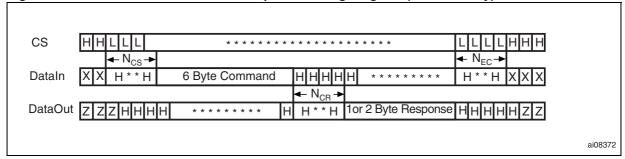

|    |       | 10.4.3    | Data Read                                         | 86 |

|    |       |           |                                                   |    |

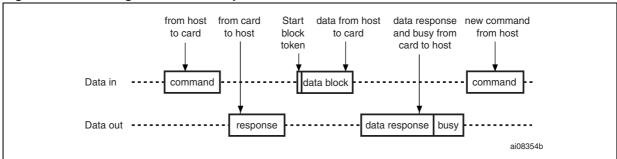

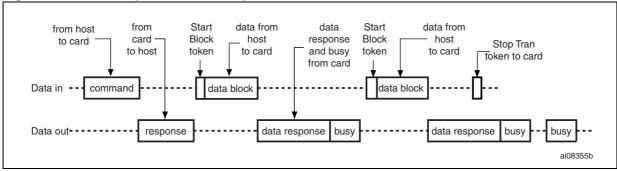

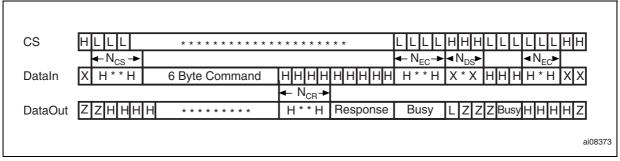

|    |       | 10.4.4    | Data Write                                             |     |

|----|-------|-----------|--------------------------------------------------------|-----|

|    |       | 10.4.5    | Erase and Write Protect management                     |     |

|    |       | 10.4.6    | Read the CID and CSD registers                         | 91  |

|    |       | 10.4.7    | Reset sequence                                         | 91  |

|    |       | 10.4.8    | Clock control                                          | 92  |

|    |       | 10.4.9    | Error conditions                                       | 92  |

|    |       | 10.4.10   | Read, Write, Erase and Forced Erase timeout conditions | 93  |

|    |       | 10.4.11   | Memory array partitioning                              | 93  |

|    |       | 10.4.12   | Lock/Unlock commands                                   | 93  |

|    |       | 10.4.13   | Application specific commands                          | 93  |

|    | 10.5  | SPI mo    | de commands                                            | 94  |

|    | 10.6  | SPI mo    | de responses                                           | 99  |

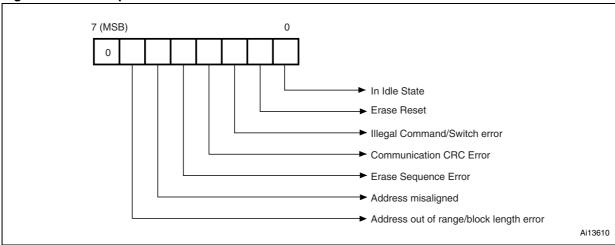

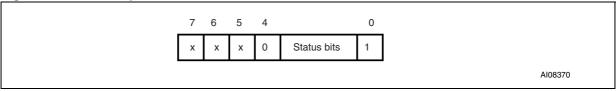

|    |       | 10.6.1    | R1 format                                              | 99  |

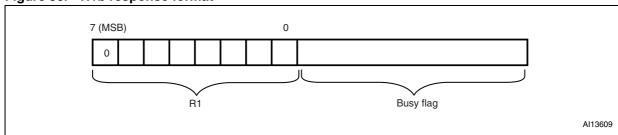

|    |       | 10.6.2    | R1b format                                             | 99  |

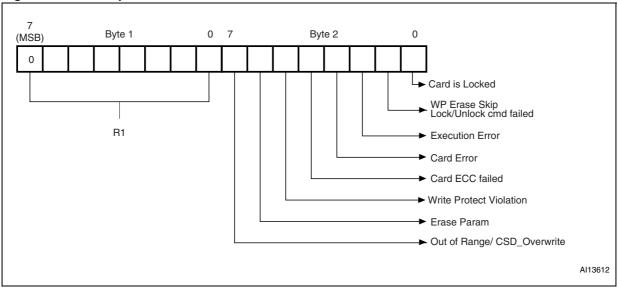

|    |       | 10.6.3    | R2 format                                              | 100 |

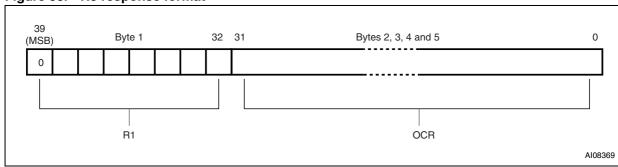

|    |       | 10.6.4    | R3 format                                              | 100 |

|    |       | 10.6.5    | Data response format                                   | 101 |

|    |       | 10.6.6    | Data messages                                          | 101 |

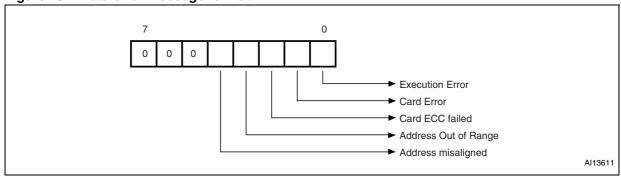

|    |       | 10.6.7    | Data error messages                                    | 102 |

|    | 10.7  | Clearing  | g Status Register bits                                 | 102 |

|    | 10.8  | Device    | registers                                              | 106 |

|    | 10.9  | SPI bus   | s timings                                              | 106 |

|    |       | 10.9.1    | Command/response timings                               | 107 |

|    |       | 10.9.2    | Data Read timings                                      |     |

|    |       | 10.9.3    | Data Write timings                                     | 109 |

| 11 | Error | r protect | iion                                                   | 110 |

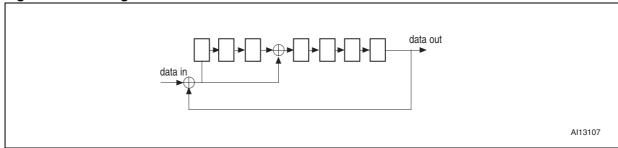

|    | 11.1  | CRC7      |                                                        | 110 |

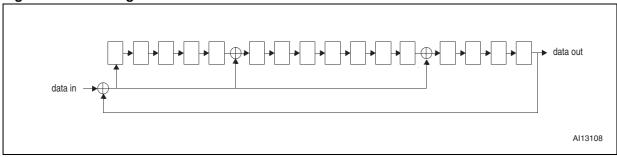

|    | 11.2  |           |                                                        |     |

| 12 | Pack  | age med   | chanical                                               | 112 |

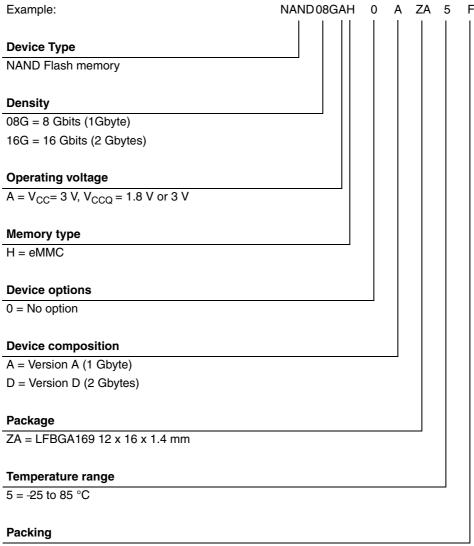

| 13 | Part  | numberi   | ing                                                    | 114 |

| 14 |       |           | tory                                                   |     |

|    |       |           | •                                                      |     |

# **List of tables**

| Table 1.   | System performance                                         | 12 |

|------------|------------------------------------------------------------|----|

| Table 2.   | Current consumption                                        | 12 |

| Table 3.   | System reliability and maintenance                         | 12 |

| Table 4.   | Communication channel performance                          | 12 |

| Table 5.   | Signal names                                               | 17 |

| Table 6.   | Bus operating conditions                                   | 21 |

| Table 7.   | Open-drain mode bus signal level                           | 22 |

| Table 8.   | Push-pull mode bus signal level                            | 22 |

| Table 9.   | Bus AC timings                                             | 23 |

| Table 10.  | Bus modes overview                                         |    |

| Table 11.  | Data format                                                | 29 |

| Table 12.  | 1-bit bus test pattern                                     |    |

| Table 13.  | 4-bit bus test pattern                                     |    |

| Table 14.  | 8-bit bus test pattern                                     |    |

| Table 15.  | Lock/Unlock data block                                     |    |

| Table 16.  | Formulae to calculate typical access and program times     |    |

| Table 17.  | MultiMediaCard command format                              |    |

| Table 18.  | Device command classes (CCCs) - supported commands 0 to 27 |    |

| Table 19.  | Card command classes (CCCs) - supported commands 28 to 56  |    |

| Table 20.  | Basic commands for read-only devices (class 0)             |    |

| Table 21.  | Block oriented Read commands (class 2)                     |    |

| Table 22.  | Block oriented Write commands (class 4)                    |    |

| Table 23.  | Block oriented Write commands (class 6)                    |    |

| Table 24.  | Erase commands (class 5)                                   |    |

| Table 25.  | I/O mode commands (class 9)                                |    |

| Table 26.  | Lock (class 7)                                             |    |

| Table 27.  | Device state transition                                    |    |

| Table 28.  | R1 response                                                |    |

| Table 29.  | R2 response                                                |    |

| Table 30.  | R3 response                                                |    |

| Table 31.  | R4 response                                                |    |

| Table 32.  | OCR register definition                                    |    |

| Table 33.  | Card identification (CID) register                         |    |

| Table 34.  | Card specific data register                                |    |

| Table 35.  | CSD register structure                                     |    |

| Table 36.  | System specification version                               |    |

| Table 37.  | TAAC access time definition                                |    |

| Table 38.  | Maximum bus clock frequency definition                     |    |

| Table 39.  | Supported card command classes                             |    |

| Table 40.  | Data block length                                          |    |

| Table 41.  | DSR implementation code                                    |    |

| Table 42.  | Current consumption at V <sub>CC</sub> min                 |    |

| Table 43.  | Current consumption at V <sub>CC</sub> max                 |    |

| Table 44.  | Multiply factor for the device size                        |    |

| Table 45.  | R2W_FACTOR                                                 |    |

| Table 45.  | File formats                                               |    |

| Table 40.  | ECC type                                                   |    |

| Table 47.  | CSD field command classes                                  |    |

| . 40.0 70. |                                                            |    |

# List of tables

| Table 49. | Extended CSD                                                              | . 66  |

|-----------|---------------------------------------------------------------------------|-------|

| Table 50. | Supported command sets                                                    | . 67  |

| Table 51. | R/W access performance values                                             | . 68  |

| Table 52. | Power classes                                                             | . 69  |

| Table 53. | Card type                                                                 | . 70  |

| Table 54. | CSD Register structure                                                    | . 70  |

| Table 55. | Extended CSD revision                                                     | . 70  |

| Table 56. | Standard MMC command set revisions                                        | . 71  |

| Table 57. | Power class code                                                          | 71    |

| Table 58. | Bus mode values                                                           | 71    |

| Table 59. | Status register                                                           |       |

| Table 60. | Timing symbols                                                            | 75    |

| Table 61. | Timing values                                                             | . 75  |

| Table 62. | SPI interface pin configuration                                           |       |

| Table 63. | MultiMediaCard registers in SPI mode                                      | 84    |

| Table 64. | Command format                                                            | 94    |

| Table 65. | Command classes in SPI mode                                               | 94    |

| Table 66. | Commands and arguments                                                    | 95    |

| Table 67. | Data message first byte                                                   |       |

| Table 68. | Status bits definition in SPI mode                                        | . 103 |

| Table 69. | Status bits versus commands and classes (SPI mode)                        | . 105 |

| Table 70. | SPI timing symbols                                                        | . 106 |

| Table 71. | SPI timing values                                                         | . 106 |

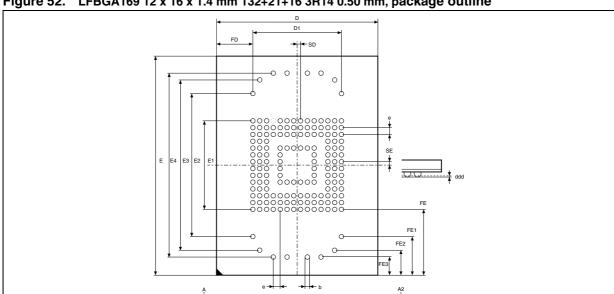

| Table 72. | LFBGA169 12 x 16 x 1.4 mm 132+21+16 3R14 0.50 mm, package mechanical data | . 112 |

| Table 73. | Ordering information scheme                                               | . 114 |

| Table 74. | Document revision history                                                 | . 115 |

# **List of figures**

| Figure 1.  | Device block diagram                                                        | . 13 |

|------------|-----------------------------------------------------------------------------|------|

| Figure 2.  | LFBGA169 package connections (top view through package)                     |      |

| Figure 3.  | Form factor                                                                 |      |

| Figure 4.  | Memory array structure                                                      |      |

| Figure 5.  | Bus circuitry diagram                                                       | . 18 |

| Figure 6.  | Power-up                                                                    |      |

| Figure 7.  | Power cycling                                                               |      |

| Figure 8.  | Bus signal levels                                                           |      |

| Figure 9.  | Timing diagram data input/output referenced to clock                        | . 23 |

| Figure 10. | MultiMediaCard state diagram (Card Identification mode)                     |      |

| Figure 11. | Data transfer formats                                                       |      |

| Figure 12. | MultiMediaCard state diagram (Data Transfer mode)                           |      |

| Figure 13. | Identification timing diagram (Card Identification mode)                    |      |

| Figure 14. | SET_RCA timing diagram (Card Identification mode)                           |      |

| Figure 15. | Command response timing diagram (Data Transfer mode)                        |      |

| Figure 16. | R1b response timing diagram                                                 |      |

| Figure 17. | Last device response to Next Host command timing diagram                    |      |

| Figure 18. | Command n end to CMD n+1 start timing diagram (all modes)                   |      |

| Figure 19. | Single Block Read command timing diagram                                    |      |

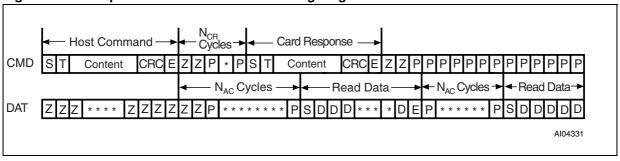

| Figure 20. | Multiple Block Read command timing diagram                                  |      |

| Figure 21. | STOP_TRANSMISSION command timing diagram (CMD12, Data Transfer mode)        |      |

| Figure 22. | Single Block Write command timing diagram                                   |      |

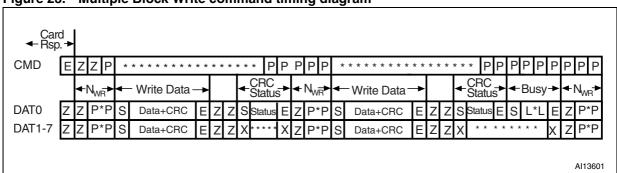

| Figure 23. | Multiple Block Write command timing diagram                                 |      |

| Figure 24. | STOP_TRANSMISSION during data transfer from the host timing diagram         |      |

| Figure 25. | STOP_TRANSMISSION during CRC status transfer from the device timing diagram |      |

| Figure 26. | STOP_TRANSMISSION received after last data block (device busy)              |      |

| Figure 27. | STOP_TRANSMISSION received after last data block (device becomes busy)      |      |

| Figure 28. | 4-bit system bus test procedure                                             |      |

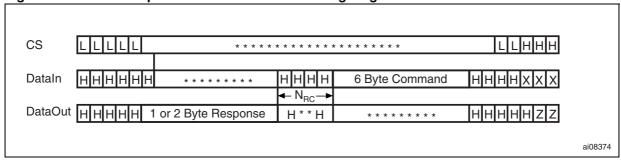

| Figure 29. | SPI Single Block Read operation                                             |      |

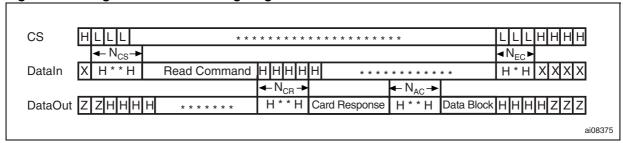

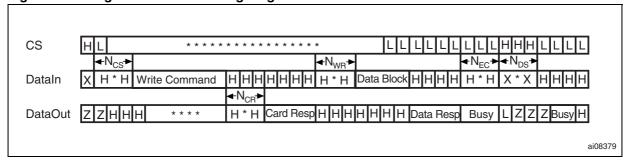

| Figure 30. | SPI Multiple Block Read operation                                           |      |

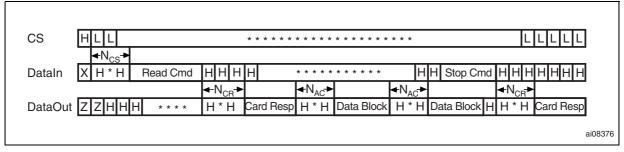

| Figure 31. | SPI Read operation – data error                                             |      |

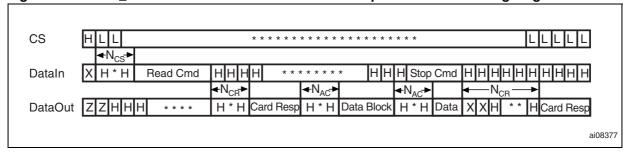

| Figure 32. | SPI Single Block Write operation                                            |      |

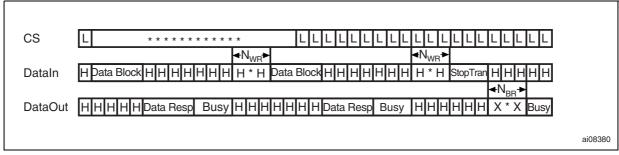

| Figure 33. | SPI Multiple Block Write operation                                          |      |

| Figure 34. | Erase and Write Protect operations                                          |      |

| Figure 35. | R1 response format                                                          |      |

| Figure 36. | R1b response format                                                         |      |

| Figure 37. | R2 response format                                                          | 100  |

| Figure 38. | R3 response format                                                          | 100  |

| Figure 39. | Data response format                                                        |      |

| Figure 40. | Data error message format                                                   |      |

| Figure 41. | Host command to device response timing diagram (device ready)               |      |

| Figure 42. | Host command to device response timing diagram (device busy)                |      |

| Figure 43. | Device response to Host command timing diagram                              |      |

| Figure 44. | Single Block Read timing diagram                                            |      |

| Figure 45. | STOP_TRANSMISSION between blocks in Multiple Block Read timing diagram      |      |

| Figure 46. | STOP_TRANSMISSION within a block in Multiple Block Read timing diagram      |      |

| Figure 47. | CSD and CID register Read timing diagram                                    |      |

| Figure 48. | Single Block Write timing diagram                                           |      |

# List of figures

# NAND08GAH0A, NAND16GAH0D

| Figure 49. | Multiple Block Write timing diagram                               | 109 |

|------------|-------------------------------------------------------------------|-----|

| Figure 50. | CRC7 generator/checker                                            | 110 |

| Figure 51. | CRC16 generator/checker                                           | 111 |

| Figure 52. | LFBGA169 12 x 16 x 1.4 mm 132+21+16 3R14 0.50 mm, package outline | 112 |

# 1 Description

NAND08GAH0A and NAND16GAH0D are embedded Flash memory storage solutions with MultiMediaCard interface (eMMC<sup>TM</sup>). The eMMC<sup>TM</sup> was developed for universal low cost data storage and communication media. They can be considered as high speed MultiMediaCards embedded in LFBGA169 12 x 16 x 1.4 mm, 0.5 mm pitch package instead of an MMC. The devices are fully compatible with MMC bus and hosts.

NAND08GAH0A and NAND16GAH0D communications are made through an advanced 13-pin bus. The bus can be either 1-bit, 4-bit, or 8-bit bus width. The devices operate in high-speed mode at clock frequencies equal or higher than 20 MHz. The communication protocol is defined as a part of this MMC standard and referred to as MultiMediaCard mode. For compatibility with existing controllers the devices may offer, in addition to the MultiMediaCard mode, an alternate communication protocol which is based on the SPI standard.

The devices are designed to cover a wide area of applications such as smart phones, cameras, organizers, PDA, digital recorders, MP3 players, pagers, electronic toys, etc. They feature high performance, low power consumption, low cost and high density.

To meet the requirements of embedded high density storage media and mobile applications, Numonyx NAND08GAH0A and NAND16GAH0D support both 3 V supply voltage ( $V_{CC}$ ), and 1.8 V/3 V input/output voltage ( $V_{CCO}$ ).

The devices have a built-in intelligent controller which manages interface protocols, data storage and retrieval, wear leveling, bad block management, garbage collection, internal ECC.

In order to meet environmental requirements, Numonyx offers the NAND08GAH0A and NAND16GAH0D in ECOPACK® packages. ECOPACK packages are Lead-free. The category of second Level Interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label. ECOPACK is an Numonyx trademark.

The system performance and characteristics are given in *Table 1*, *Table 2*, *Table 3*, and *Table 4*.

#### **Related documentation**

• eMMC<sup>TM</sup>/MultiMediaCard system specification, version 4.1.

Table 1. System performance

| System nerformance   | Typica      | Unit        |         |

|----------------------|-------------|-------------|---------|

| System performance   | NAND08GAH0A | NAND16GAH0D | Offit   |

| Reset to Ready       | 100         | 100         | ms      |

| Multiple Block Read  | 8.9         | 8.5         | Mbyte/s |

| Single Block Read    | 1.0         | 1.0         | Mbyte/s |

| Multiple Block Write | 2.8         | 3.5         | Mbyte/s |

| Single Block Write   | 0.1         | 0.1         | Mbyte/s |

Table 2. Current consumption

| Operation | Test                                                 | Current consumption |      |             |      | l lmit |

|-----------|------------------------------------------------------|---------------------|------|-------------|------|--------|

| Operation | conditions                                           | NAND08GAH0A         |      | NAND16GAH0D |      | Unit   |

|           |                                                      | Тур.                | Max. | Тур.        | Max. |        |

| Read      | V <sub>CC</sub> = 3 V±5%<br>V <sub>CCQ</sub> =3 V±5% | 20                  |      | 25          |      | mA     |

| Write     | V <sub>CCQ</sub> =3 V±5%<br>or 1.8 V±5%              | 40                  |      | 60          |      | mA     |

|           | V <sub>CC</sub> = 3 V±5%                             | 10                  |      | 20          |      |        |

| Standby   | V <sub>CCQ</sub> =3 V±5%<br>or 1.8 V±5%              | 100                 | 200  | 100         | 200  | μA     |

Table 3. System reliability and maintenance

| MTBF                   | > 3 million hours                                                |  |  |

|------------------------|------------------------------------------------------------------|--|--|

| Preventive maintenance | None                                                             |  |  |

| Data reliability       | less than 1 non-recoverable error per 10 <sup>14</sup> bits read |  |  |

| Endurance              | 2 000 000                                                        |  |  |

Table 4. Communication channel performance

| MultiMediaCard communication channel performance            |

|-------------------------------------------------------------|

| Three-wire serial data bus (Clock, command, data)           |

| Variable clock rate 0, 26, 52 MHz                           |

| Easy card identification                                    |

| Error protected data transfer                               |

| Sequential and single/multiple block oriented data transfer |

# 2 Device physical description

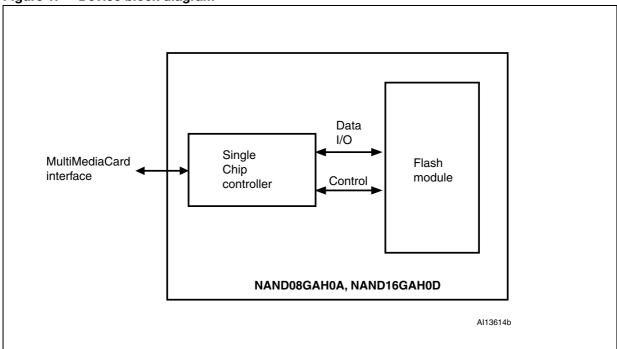

The NAND08GAH0A and NAND16GAH0D contain a single chip controller and Flash memory module, see *Figure 1: Device block diagram*. The microcontroller interfaces with a host system allowing data to be written to and read from the Flash memory module. The controller allows the host to be independent from details of erasing and programming the Flash memory.

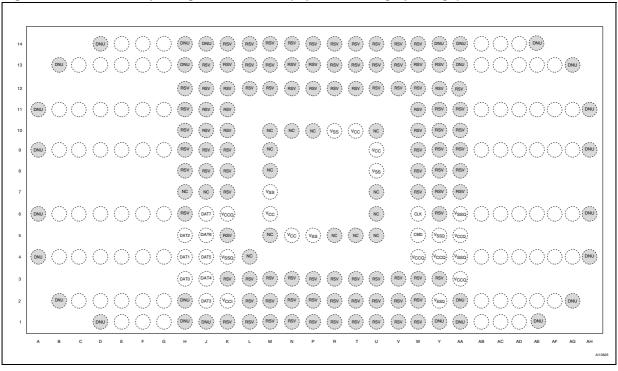

*Figure 2* shows the package connections. See *Table 5: Signal names* for the description of the signals corresponding to the balls.

Figure 1. Device block diagram

# 2.1 Package connections

Figure 2. LFBGA169 package connections (top view through package)

<sup>1.</sup> The ball corresponding to  $V_{CCI}$  must be decoupled with capacitance C5 (see *Table 6*).

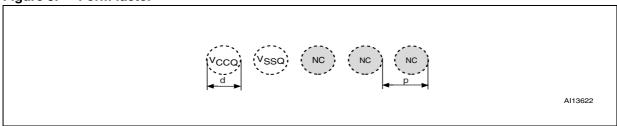

# 2.2 Form factor

The ball diameter, d, and the ball pitch, p, for LFBGA169 12 x 16 x 1.4 mm package are:

- d = 0.30 mm (solder ball diameter)

- p = 0.5 mm (ball pitch)

Figure 3. Form factor

14/116 № numonyx

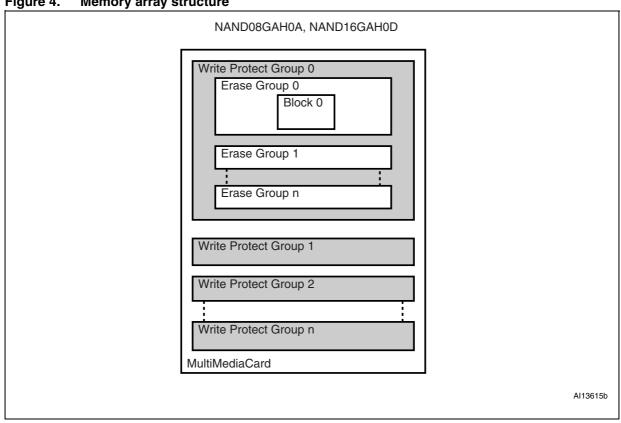

#### Memory array partitioning 3

The basic unit of data transfer to/from the device is one byte. All data transfer operations which require a block size always define block lengths as integer multiples of bytes. Some special functions need other partition granularity.

For block oriented commands, the following definitions are used:

- **Block**: the unit which is related to the block oriented read and write commands. Its size is the number of bytes which are transferred when one block command is issued by the host. The size of a block is either programmable or fixed. The information about allowed block sizes and the programmability is stored in the CSD register.

- **Erase Group**: the unit which is related to special erase and write commands defined for R/W cards. Its size is the smallest number of consecutive write blocks which can be addressed for erase. The size of the Erase Group depends on each device and is stored in the CSD.

- Write Protect Group: the smallest unit that may be individually write protected. Its size is defined in units of erase groups. The size of a WP-group depends on each device and is stored in the CSD.

Figure 4 shows NAND08GAH0A and NAND16GAH0D memory array organization.

Figure 4. Memory array structure

<sup>1.</sup> n = number of last Erase Group or last Write Protect Group.

🚺 numonyx 15/116

# 4 MultiMediaCard interface

The signal/pin assignments are listed in *Table 5*. Refer to this table in conjunction with *Figure 2* and *Figure 3*: *Form factor*.

# 4.1 Signals description

# 4.1.1 Clock (CLK)

The Clock input, CLK, is used to synchronize the memory to the host during command and data transfers. Each clock cycle gates one bit on the command and on all the data lines. The Clock frequency, f<sub>PP</sub> may vary between zero and the maximum clock frequency.

### 4.1.2 Command (CMD)

The CMD signal is a bidirectional command channel used for device initialization and command transfer. The CMD signal has two operating modes: open-drain and push-pull. The open-drain mode is used for initialization, while the push-pull mode is used for fast command transfer. Commands are sent by the MultiMediaCard bus master (or host) to the device who answers by sending back responses.

### 4.1.3 Input/outputs (DAT0-DAT7)

DAT0 to DAT7 are bidirectional data channels. The signals operate in push-pull mode. The NAND08GAH0A and NAND16GAH0D include internal pull ups for all data lines. These signals cannot be driven simultaneously by the host and the NAND08GAH0A device.

By default, after power-up or hardware reset, only DAT0 is used for data transfers. The host can configure the device to use a wider data bus, DAT0, DAT0-DAT3 or DAT0-DAT7, for data transfer.

# 4.1.4 V<sub>CC</sub> core supply voltage

$V_{CC}$  provides the power supply to the internal core of the memory device. It is the main power supply for all operations (read, program and erase).

# 4.1.5 V<sub>SS</sub> ground

Ground, Vss, is the reference for the power supply. It must be connected to the system ground.

# 4.1.6 V<sub>CCQ</sub> input/output supply voltage

$V_{CCQ}$  provides the power supply to the I/O pins and enables all outputs to be powered independently from  $V_{CC}$ .

The input/output voltage (V<sub>CCQ</sub>) can be either within 1.65/1.7 V and 1.95 V (low voltage range) or 2.7 V and 3.6 V (high voltage range).

# 4.1.7 V<sub>SSQ</sub> supply voltage

$V_{SSQ}$  ground is the reference for the input/output circuitry driven by  $V_{CCQ}$ .

Table 5. Signal names

| Name             | Type <sup>(1)</sup> | Description                                                 |

|------------------|---------------------|-------------------------------------------------------------|

| DAT0             | I/O (PP)            | Data                                                        |

| DAT1             | I/O (PP)            | Data                                                        |

| DAT2             | I/O (PP)            | Data                                                        |

| DAT3             | I/O (PP)            | Data                                                        |

| DAT4             | I/O (PP)            | Data                                                        |

| DAT5             | I/O (PP)            | Data                                                        |

| DAT6             | I/O (PP)            | Data                                                        |

| DAT7             | I/O (PP)            | Data                                                        |

| CMD              | I/O (OD or PP)      | Command                                                     |

| CLK              | I (PP)              | Clock                                                       |

| V <sub>CCQ</sub> |                     | Input/output power supply                                   |

| V <sub>CC</sub>  |                     | Core power supply                                           |

| $V_{SSQ}$        |                     | Input/output ground                                         |

| V <sub>CCI</sub> | I                   | Must be decoupled with capacitance C5 (see <i>Table 6</i> ) |

| V <sub>CC</sub>  |                     | Core power supply                                           |

| NC               | NC                  | Not connected <sup>(2)</sup>                                |

| RSV              | RSV                 | Reserved for future use <sup>(2)</sup>                      |

| DNU              | DNU                 | Do not use <sup>(2)</sup>                                   |

<sup>1.</sup> I: input; O: output, OD: open drain, PP: push-pull.

<sup>2.</sup> NC, RSV and DNU pins can be connected to ground or left floating.

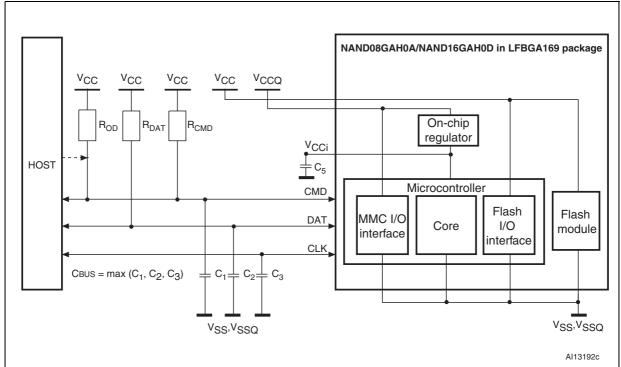

# 4.2 Bus topology

*Figure 5* shows the bus circuitry required for the device. The resistor  $R_{OD}$  is switched on and off, synchronously, by the host for the open-drain and push-pull mode transitions.  $R_{DAT}$  and  $R_{CMD}$  are pull-up resistors that are used to stop the CMD and DAT signals floating when no device is inserted or when all the device drivers are in a high impedance state.

A constant current source can replace  $R_{OD}$  and achieve a better performance (constant slopes for the signal's rising and falling edges). If the host does not allow a switchable  $R_{OD}$  to be implemented, a fixed  $R_{CMD}$  can be used. Consequently, the maximum operating frequency in the open drain mode has to be reduced if the value of  $R_{CMD}$  is higher than the minimum given in *Table 6: Bus operating conditions*.

Figure 5. Bus circuitry diagram

1. See *Table 6* for the values of R<sub>OD</sub>, RD<sub>AT</sub>, RCM<sub>D</sub>, C1, C2, C3, and C5.

# 4.3 Power-up and power-down

# 4.3.1 **Power-up**

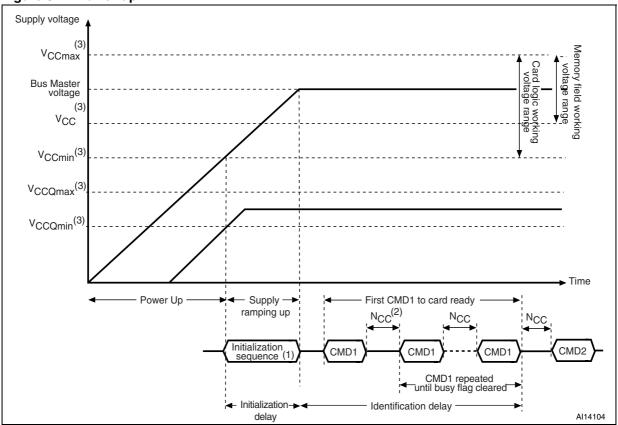

The power-up and hot insertion (e.g. inserting the device when the bus is operating) are handled locally in each device and in the bus master.

$V_{CC}$  must be powered up before or simultaneously with  $V_{CCQ}$ . No delay must be respected between  $V_{CC}$  and  $V_{CCQ}$  ramp up (see *Figure 8*).

After power-up the device enters the Idle state until the CMD1 command is received. The bus master must get the device out of the Idle state. Since the power-up time and the supply voltage ramp up time depend on application parameters such as the bus length and the power supply unit, the host must ensure that the supply voltage has reached the operating level specified in CMD1 before issuing a CMD1 command.

CMD1 is a special synchronization command for the host to poll the device states until the power-up is completed correctly. The response of CMD1 contains a busy flag which indicates that a device is not ready. The host has to wait until this flag is cleared. The time for this flag to be cleared is the Identification delay (see *Figure 6*).

After power-up the host starts the clock and sends the initializing sequence on the CMD line (see *Figure 6*). This sequence is a contiguous stream of logic 1 s. The sequence length is either 1 ms, 74 clock cycles or the supply ramp up time, whichever is the longest. The additional 10 clocks (after the 64 clocks after which the device should be ready for communication) are provided to avoid power-up synchronization problems.

The device ignores all commands until the commands CMD1, CMD2 are issued and the RCA of the device is initialized.

The initialization delay is relevant only after power-up, the identification delay is relevant for both power-up and hot insertion.

After power-up, the maximum initial load the NAND08GAH0A and NAND16GAH0D can present on the  $V_{CC}$  line is C4, in parallel with a minimum of R4. During operation, device capacitance on the  $V_{CC}$  line must not exceed 10  $\mu$ F.

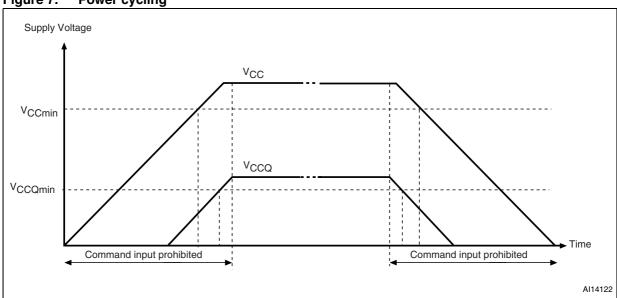

### 4.3.2 Power-down

At power-down,  $V_{CCQ}$  must go Low before or simultaneously with  $V_{CC}$  going Low (see *Figure 9*). Commands from the bus master are accepted till  $V_{CCQ}$  and  $V_{CC}$  start to ramp down.

Figure 6. Power-up

- The initialization sequence is a contiguous stream of logic 1's. Its length is either 1 ms, 74 clocks or the supply ramp up time, whichever is the longest. The device shall complete its initialization within 1 second from the first CMD1 with a valid V range.

- 2. N<sub>CC</sub> is the number of clock cycles. Refer to *Table 61* for its value.

- 3. Refer to Section 8.1: Operation conditions register (OCR) for details on voltage ranges.

Figure 7. Power cycling

#### **Electrical specifications** 4.4

Table 6 defines the bus operating conditions for the device.

The total capacitance C<sub>1</sub> of each line of the bus is given by the below equation:

$$C_L = C_{HOST} + C_{BUS} + C_{CARD}$$

where  $C_{\mbox{\scriptsize HOST}}$  is the bus master capacitance,  $C_{\mbox{\scriptsize BUS}}$  the bus capacitance itself and  $C_{\mbox{\scriptsize CARD}}$  the capacitance of the device connected to this line. The sum of the host and bus capacitance, CHOST+CBUS, must not to exceed 20 pF.

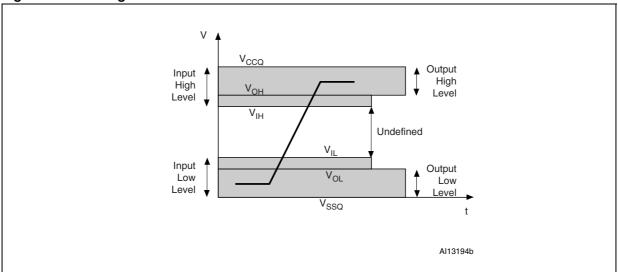

As the bus can be supplied with a variable supply voltage, all bus signal levels are related to the supply voltage (see Figure 8, Table 7, and Table 8).

Bus operating conditions<sup>(1)(2)</sup> Table 6.

| Symbol            | Parameter                                                                                                                       | Min  | Max  | Unit |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------|------|------|------|

|                   | Peak voltage on all lines                                                                                                       | -0.5 | 3.6  | V    |

|                   | Input leakage current on all inputs (before initialization sequence and/or internal pull up resistors connected) <sup>(3)</sup> | 400  | 100  | μΑ   |

|                   | Input leakage current on all inputs (after initialization sequence and/or internal pull up resistors connected) <sup>(3)</sup>  | -10  | 10   | μΑ   |

|                   | Output leakage current on all outputs (before initialization sequence)                                                          | 400  | 100  | μA   |

|                   | Output leakage current on all outputs (after initialization sequence)                                                           | -10  | 10   | μA   |

| V                 | Low supply-voltage range (MultiMediaCard v. 4.1)                                                                                | 1.65 | 1.95 | V    |

| $V_{CCQ}$         | High supply-voltage range                                                                                                       | 2.7  | 3.6  | ]    |

| V <sub>CC</sub>   | Input/output supply voltage                                                                                                     | 2.7  | 3.6  | V    |

| V <sub>SS</sub>   | Supply voltage ground                                                                                                           | -0.5 | 0.5  | V    |

| R <sub>DAT</sub>  | Pull-up resistance (to prevent bus floating)                                                                                    | 50   | 100  | kΩ   |

| R <sub>CMD</sub>  | Pull-up resistance (to prevent bus floating)                                                                                    | 4.7  | 100  | kΩ   |

| R <sub>INT</sub>  | Internal pull up resistance DAT1-DAT7 (to prevent unconnected line floating)                                                    | 50   | 150  | kΩ   |

| R4                | Load resistance on V <sub>CC</sub> line after power-up or hot insertion                                                         | 330  |      | Ω    |

| C4                | Load capacitance on V <sub>CC</sub> line after power-up or hot insertion                                                        |      | 10   | μF   |

| C <sub>L</sub>    | Bus signal line capacitance                                                                                                     |      | 30   | pF   |

| C <sub>CARD</sub> | Single card capacitance                                                                                                         |      | 7    | pF   |

| C1                | Load capacitance on CMD input                                                                                                   | TBD  | TBD  | pF   |

| C2                | Load capacitance on DAT input                                                                                                   | TBD  | TBD  | pF   |

| C3                | Load capacitance on CLK input                                                                                                   | TBD  | TBD  | pF   |

| C5                | Decoupling capacitance on V <sub>CCI</sub> input                                                                                |      | 1    | pF   |

|                   | Maximum signal line inductance (f <sub>PP</sub> ≤52 MHz)                                                                        |      | 16   | nH   |

<sup>1.</sup> The current consumption of the device for the different configurations is defined in the POWER\_CLASS field of the EXT\_CSD register (see Section 8.4).

21/116 N numonyx

<sup>2.</sup> TBD stands for 'to be defined'.

<sup>3.</sup> See Section 4.3: Power-up and power-down.

Figure 8. Bus signal levels

Table 7. Open-drain mode bus signal level<sup>(1)</sup>

| Symbol          | Parameter           | Conditions                | Min                   | Max | Unit |

|-----------------|---------------------|---------------------------|-----------------------|-----|------|

| V <sub>OH</sub> | Output High voltage | I <sub>OH</sub> = -100 μA | V <sub>CCQ</sub> -0.2 |     | V    |

| V <sub>OL</sub> | Output Low voltage  | I <sub>OL</sub> = 2 mA    |                       | 0.3 | V    |

<sup>1.</sup> The values of V<sub>IH</sub> and V<sub>IL</sub> are identical in Open-drain and Push-pull mode (see *Table 8: Push-pull mode bus signal level*).

Table 8. Push-pull mode bus signal level<sup>(1)</sup>

|                 |                     |                                                  | V <sub>CCQ</sub>      |                       |                       |                        |      |

|-----------------|---------------------|--------------------------------------------------|-----------------------|-----------------------|-----------------------|------------------------|------|

| Symbol          | Parameter           | Conditions                                       | 1.65 to               | 1.95 V                | 2.7 to                | 3.6 V                  | Unit |

|                 |                     |                                                  | Min                   | Max                   | Min                   | Max                    |      |

| V <sub>OH</sub> | Output High voltage | $I_{OH} = -100 \mu A$ at $V_{CCQ}$ min           | V <sub>CCQ</sub> -0.2 |                       | 0.75 V <sub>CCQ</sub> |                        | ٧    |

| V <sub>OL</sub> | Output Low voltage  | I <sub>OL</sub> = 100 μA at V <sub>CCQ</sub> min |                       | 0.2                   |                       | 0.125V <sub>CCQ</sub>  | V    |

| V <sub>IH</sub> | Input High voltage  |                                                  | 0.7V <sub>CCQ</sub>   | V <sub>CC</sub> + 0.3 | 0.625V <sub>CCQ</sub> | V <sub>CCQ</sub> + 0.3 | V    |

| $V_{IL}$        | Input Low voltage   |                                                  | V <sub>SSQ</sub> -0.3 | 0.3V <sub>CCQ</sub>   | V <sub>SS</sub> -0.3  | 0.25V <sub>CCQ</sub>   | V    |

<sup>1.</sup> In accordance with the JEDEC specification JESD8-1A, the device input and output voltages should be within the specified ranges for the whole  $V_{CC}$  range.

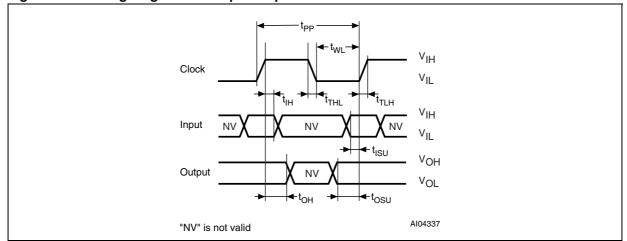

Figure 9. Timing diagram data input/output referenced to clock

Table 9. Bus AC timings

| Symbol                              | Parameter                                               |      | 20 MHz |     | 26/52 MHz <sup>(1)</sup> |      |

|-------------------------------------|---------------------------------------------------------|------|--------|-----|--------------------------|------|

| Symbol                              | Parameter                                               | Min  | Max    | Min | Max                      | Unit |

|                                     | Clock CLK <sup>(2)</sup>                                | •    |        |     | •                        |      |

| f <sub>PP</sub>                     | Clock frequency Data Transfer mode (PP)(3)(4)           | 0    | 20     | 0   | 26/52 <sup>(1)</sup>     | MHz  |

| f <sub>OD</sub>                     | Clock frequency Identification mode (OD) <sup>(5)</sup> | 0    | 400    | 0   | 400                      | kHz  |

| t <sub>WL</sub>                     | Clock Low time <sup>(3)</sup>                           | 10   |        | 6.5 |                          | ns   |

| t <sub>TLH</sub>                    | Clock Rise time <sup>(3)(6)</sup>                       |      | 10     |     | 3                        | ns   |

| t <sub>THL</sub>                    | Clock Fall time <sup>(3)(6)</sup>                       |      | 10     |     | 3                        | ns   |

| Input CMD, I                        | DAT (referenced to CLK)                                 |      |        |     |                          |      |

| t <sub>ISU</sub>                    | Input Set-up time <sup>(3)</sup>                        | 3    |        | 3   |                          | ns   |

| t <sub>IH</sub>                     | Input Hold time <sup>(3)</sup>                          | 3    |        | 3   |                          | ns   |

| Output CMD, DAT (referenced to CLK) |                                                         |      |        |     |                          |      |

| tosu                                | Output Set-up time <sup>(3)</sup>                       | 13.1 |        | 5   |                          | ns   |

| t <sub>OH</sub>                     | Output Hold time <sup>(3)</sup>                         | 9.7  |        | 5   |                          | ns   |

<sup>1.</sup>  $f_{PP}$ =52 MHz is available for  $V_{CC}$ =2.7 to 3.6 V

<sup>2.</sup> All timing values are measured relatively to 50% of the voltage level.

<sup>3.</sup> Parameter measured with a bus line load capacitance, C<sub>L</sub>, lower than 30 pF.

<sup>4.</sup>  $f_{PP}$  is measured with a tolerance of 100 KHz.

<sup>5.</sup>  $f_{OD}$  is measured with a tolerance of 20 KHz.

<sup>6.</sup> Rise and fall times are measured from 10% to 90% of the voltage level for High clock frequencies (26 and 52 MHz). They are measured from  $V_{IL}$  (max) to  $V_{IH}$  (min) of the voltage level for standard clock frequency (20 MHz).

# 5 High speed MultiMediaCard operation

### 5.1 Overview

All communication between the host and the device is controlled by the host (master). The host sends two types of command:

- Broadcast commands intended for all MultimediaCard devices. They are kept for backwards compatibility to previous MultiMediaCard systems, where more than one device was allowed on the bus.

- Addressed (point-to-point) commands which are sent to the addressed device and cause it to respond.

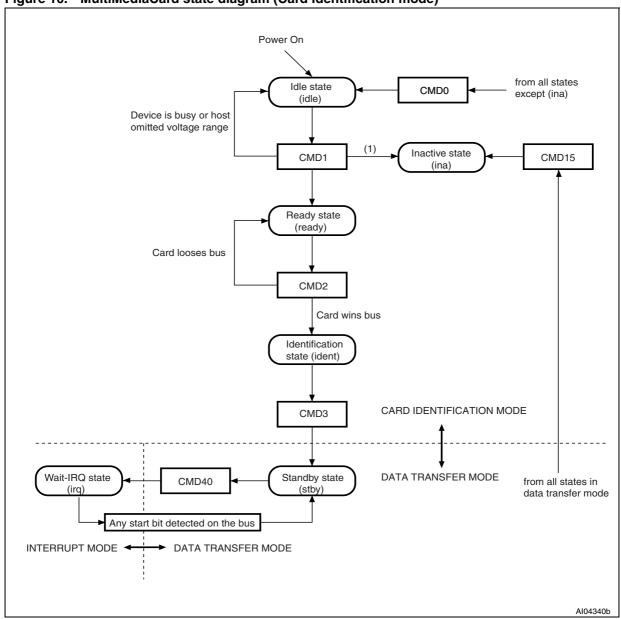

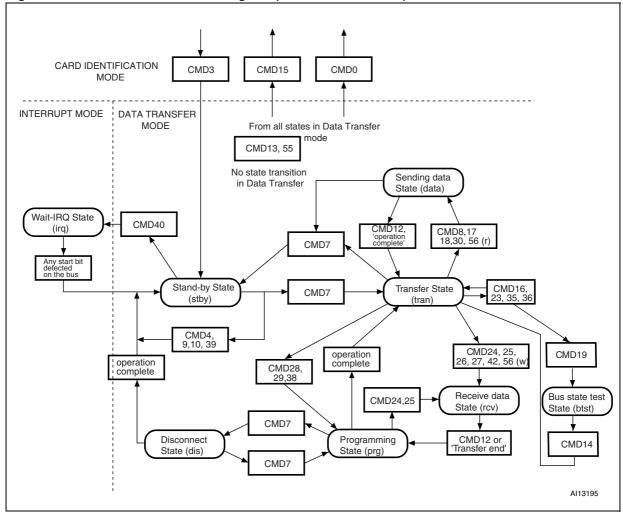

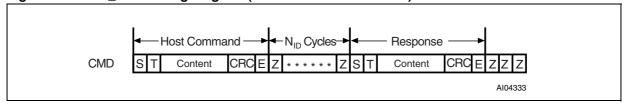

A general overview of the command flow is shown in *Figure 10* for the Card Identification mode and in *Figure 12* for the Data Transfer mode. The commands are listed in the command tables (*Table 20*, *Table 21*, *Table 22*, *Table 23*, and *Table 24*). The relation between the current device state, the received command and the resulting state are listed in *Table 27*. The different operating modes are presented in the following sections, together with the restrictions for controlling the clock signal, and device commands, state transitions and timings.

Three operating modes are defined for MultiMediaCard devices:

#### Card Identification mode

The host enter Card Identification mode after reset and while it is looking for new devices connected to the bus.

MultiMediaCard devices enter this mode after reset until the SET\_RCA command (CMD3) is received.

Interrupt mode (not supported)

#### Data Transfer mode

The device enters Data Transfer mode once an RCA is assigned to it. The host will enter data transfer mode after identifying all the devices on the bus.

*Table 10* shows the relations between bus modes, operation modes and device states. Each state in the device state diagrams is associated with a bus mode and an operation mode (*Figure 10* and *Figure 12*).

A command received with an incorrect CRC is ignored. If the command was issued during an operation (for example block read), the device continues the operation until it receives a correct host command.

**Device state** Operation mode Bus mode Inactive (ina) Inactive Idle Open-drain Ready Card Identification mode Identification (ident) Standby (stby) Transfer (tran) Bus state test (btst) Sending-data (data) Data Transfer mode Push-pull Receiving-data (rcv) Programming (pgr) Disconnect Push-pull Wait-IRQ (irq) Interrupt mode

Table 10. Bus modes overview

# 5.2 Card Identification mode

When in Card Identification mode, the host resets the device, validates the operating voltage range and the access mode, identifies the device and assigns a Relative Card Address (RCA) to it.

In Card Identification mode all data communications are performed using only the command line (CMD).

### 5.2.1 Card reset

After power-up, the device is in Idle state and defaults to operate in MultiMediaCard mode, even if it was previously in the Inactive state.

The GO\_IDLE\_STATE (CMD0) command performs a software reset and puts the device in Idle state. It is also used to switch the device into SPI mode (see *Section 10: Serial peripheral interface (SPI) mode*).

After power-up or a CMD0 command, all outputs are high impedance, and the device is initialized with a default RCA (0x0001) and default Driver Stage Register (DSR) settings. The host starts the device identification process in open-drain mode with the clock frequency set to the identification clock frequency f<sub>OD</sub> (see *Table 9: Bus AC timings*).

CMD0 is valid in all states, with the exception of the Inactive state. While in Inactive state the device does not accept CMD0 commands unless it is used to switch the device into SPI mode.

# 5.2.2 Input/output voltage range validation

All device communicate with the host using an input/output voltage in the  $V_{CCQmin}$  and  $V_{CCQmax}$  range. In Card Identification mode, the minimum and maximum values for  $V_{CCQ}$  are defined in the operation condition register (OCR) and may not cover the whole range.

The SEND\_OP\_COND (CMD1) command is designed to provide hosts with a mechanism to identify and reject devices which do not match the desired  $V_{CCQ}$  range. This is performed by the host sending the required  $V_{CCQ}$  range as the operand of the CMD1 command (see Section 8.1: Operation conditions register (OCR)). If the device can not perform data transfer in the specified range, it switches into the Inactive state. Otherwise, the device answers sending back its  $V_{CCQ}$  range.

By omitting the voltage range when issuing the CMD1 command (by setting CMD1 argument to '0'), the host queries the device about its input/output voltage range. This bus query should be used if the host is able to select a common voltage range, or if the application needs to be notified of non usable devices connected to the bus. The host then chooses an operating voltage, and reissues the CMD1 together with this condition, sending incompatible devices into the Inactive state.

## 5.2.3 From Busy to Ready state

The busy flag in the CMD1 response can be used by the device to notify the host that the power-up/reset sequence is still ongoing and that the device is not ready for communication. In this case the host must reissue the CMD1 command until the busy flag is cleared.

During the initialization procedure, the host should not change the operating voltage range or access mode settings. Any change in the operating conditions is ignored by the device. If this case, the host must reset the device by issuing a CMD0 command, and restart the initialization sequence. However, a hardware reset must be performed for accessing devices that are already in the Inactive state.

The GO\_INACTIVE\_STATE (CMD15) command can be used to send an addressed device into the Inactive state. This command is used when the host explicitly wants to de-activate a device by changing its  $V_{CC}$  range into a range which is known not to be supported by this device.

### 5.2.4 Card Identification process

This process is valid when multiple MultiMediaCard devices are connected to the bus.

The host starts the card identification process in open-drain mode with the identification clock rate f<sub>OD</sub> (see *Table 9: Bus AC timings*). The open drain driver stages on the CMD line allow parallel operation during card identification.

After the bus is activated, the host will request the devices to send its valid operating conditions (CMD1). The response to CMD1 is the 'wired and' operation on the condition restrictions of all devices in the system. Incompatible devices are sent into Inactive state. The host then issues the broadcast command CMD2 and asks all devices for their unique Card Identification (CID) number. All remaining unidentified devices simultaneously start sending their CID numbers serially, while monitoring their outgoing bit stream. The devices, whose outgoing CID bits do not match the corresponding bits on the command line, stop sending their CID immediately and wait for the next identification cycle (devices stay in the Ready state). Since CID numbers are unique for each device, there should be only one device which successfully sends its full CID-number to the host. This device then goes into the Identification state.

The host issues CMD3 to assign this device a relative card address (RCA) which will be used to address the device in future data transfer communication. Once the RCA is received the device goes to the Standby state and does not react to further identification cycles. The device also switches its output drivers from open-drain to push-pull.

The host repeats the identification process as long as it receives a response (CID) to its identification command (CMD2). When no more devices respond to this command, all devices have been identified.

Figure 10. MultiMediaCard state diagram (Card Identification mode)

- 1. Incompatible  $V_{CCQ}$  voltage range.

- 2. See Table 10: Bus modes overview for the definition of the abbreviated forms corresponding to the device state.

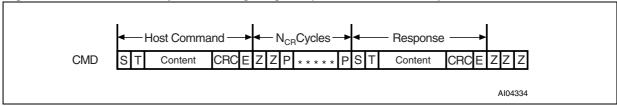

## 5.3 Data Transfer mode

The device enters data transfer mode once an RCA is assigned to it. When the device is in Standby mode, issuing the CMD7 command along with the RCA selects the device and puts it into the Transfer state.

The host enters Data Transfer mode after identifying all the MultiMediaCard devices on the bus. When all devices are in Standby state, communication over the CMD and DAT lines will be in push-pull mode (see *Table 10: Bus modes overview*).

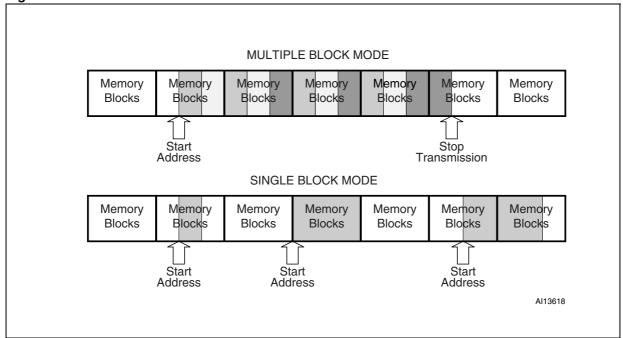

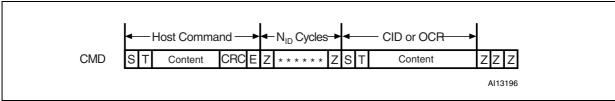

The device supports two Read/Write modes as shown in Figure 11: Data transfer formats.

- Single Block mode

- In this mode the host reads or writes one data block of a pre-specified length. The

data block transmission is protected with a 16 bit Cyclic Redundancy Check

(CRC).

- Multiple Block mode

- This mode is similar to the single block mode, but the host can read/write multiple data blocks (all have the same length) which will be stored or retrieved from contiguous memory addresses.

The host issues CMD9 to obtain the Card Specific Data (CSD register). MultiMediaCard devices which already have an RCA do not respond to the identification command flow in this mode. Until the content of all CSD registers is known by the host, the  $f_{PP}$  clock rate must remain at  $f_{OD}$  because some devices may have operating frequency restrictions.

The relationship between the various operation modes is summarized in *Figure 12: MultiMediaCard state diagram (Data Transfer mode)*.

### 5.3.1 Active command set selection

By default, the device uses the MultiMediaCard standard command set after a power-up or software reset (CMD0). The host can change the active command set by issuing the SWITCH command (CMD6) with the 'Command Set' access mode selected.

The supported command sets, as well as the currently selected command set, are defined in the EXT\_CSD register.

## 5.3.2 High speed mode selection

The device operates in high-speed mode (HS-MMC) at clock frequencies higher than 20 MHz.

The host must first check whether the Numonyx NAND08GAH0A and NAND16GAH0D comply with eMMC<sup>TM</sup>/MultiMediaCard system specification version 4.1.

The high speed mode of the device must then be enables, before changing the clock frequency to a frequency higher than 20 MHz. This is done by using the SWITCH command to write 0x01 to the HS\_TIMING byte, in the modes segment of the EXT\_CSD register.

#### 5.3.3 Power class selection

After checking whether the NAND08GAH0A and NAND16GAH0D complies with eMMC<sup>TM</sup>/MultiMediaCard system specification version 4.0 or higher, the host can change the device power class.

After power-up or software reset (CMD0), the device defaults to operate in power class 0 which corresponds to the minimum current consumption for the card type (either Low or High  $V_{\rm CCO}$  voltage range).

The PWR\_CL\_ff\_vvv bytes of the EXT\_CSD register report the power consumption levels of the device, for a 4-bit or 8-bit bus width, at the supported clock frequencies (26 or 52 MHz). The host can read the PWR\_CL\_ff\_vvv bytes by issuing a SEND\_EXT\_CSD command, and determine if it will allow the device to use a higher power class.

The power class can be changed by using the SWITCH command to program the POWER\_CLASS Byte, in the modes segment of the EXT\_CSD register.

The valid values for the EXT\_CSD register are defined in (see *Section 8.4.3: PWR\_CL\_ff\_vvv*). If the value programmed by the host is invalid, the POWER\_CLASS byte remains unchanged and the SWITCH\_ERROR bit is set.

## 5.3.4 Bus test procedure

The host can detect the bus functional lines by issuing CMD19 and CMD14 commands.

The following steps are required to test the bus functional signals:

- The host must issue a CMD19 command, followed by a specific data pattern on each selected data lines (see *Table 11*). The data pattern sent by the host may optionally include a CRC16 checksum, which is ignored by the device. The data pattern to be sent per data line is defined in *Table 12*, *Table 13* and *Table 14*, according to the bus width.

- 2. The host must then requests the device to send back the reversed data pattern. This is done by issuing a CMD14 command. The device detects the start bit on DAT0 and synchronizes accordingly the reading of all data inputs. It ignores all data pattern bits except for the first two bits. The device buffer size consequently does not limit the maximum length of the data pattern. The minimum length of the data pattern is two bytes, of which the first two bits of each data line are sent back reversed by the device.

- 3. The host detects the bus functional lines by comparing the initial data pattern with the reversed pattern sent back by the device. The host ignores all bits except for the first two bits of the reversed data pattern. The length of the reversed data pattern is eight bytes and is always sent using all the device DAT lines (see *Table 12*, *Table 13* and *Table 14*). The reversed data pattern sent by the device may optionally include a CRC16 checksum, which is ignored by the host.

The device has internal pull-up resistor on DAT1-DAT7 lines. If the device is connected to 1-bit or 4-bit high-speed MMC system, the input value of the upper bits (e.g. DAT1-DAT7 or DAT4-DAT7) are detected as logic "1" by the device.

Table 11. Data format

| Start bit | Data pattern | Checksum<br>bit | End bit |

|-----------|--------------|-----------------|---------|

| 0         | 10xxxxxx     | CRC16           | 1       |

Table 12. 1-bit bus test pattern

| Data<br>line | Data pattern sent by the host | Reversed pattern sent by the device | Notes                                  |

|--------------|-------------------------------|-------------------------------------|----------------------------------------|

| DAT0         | 0,10xxxxxxxxxx,[CRC16],1      | 0,01000000,[CRC16],1                | Start bit defines beginning of pattern |

| DAT1         |                               | 0,00000000,[CRC16],1                | No data pattern sent                   |

| DAT2         |                               | 0,00000000,[CRC16],1                | No data pattern sent                   |

| DAT3         |                               | 0,00000000,[CRC16],1                | No data pattern sent                   |

| DAT4         |                               | 0,00000000,[CRC16],1                | No data pattern sent                   |

| DAT5         |                               | 0,00000000,[CRC16],1                | No data pattern sent                   |

| DAT6         |                               | 0,00000000,[CRC16],1                | No data pattern sent                   |

| DAT7         |                               | 0,00000000,[CRC16],1                | No data pattern sent                   |

Table 13. 4-bit bus test pattern

| Data<br>line | Data pattern sent by the host | Reversed pattern sent by the device | Notes                                  |

|--------------|-------------------------------|-------------------------------------|----------------------------------------|

| DAT0         | 0,10xxxxxxxxxx,[CRC16],1      | 0,01000000,[CRC16],1                | Start bit defines beginning of pattern |

| DAT1         | 0,01xxxxxxxxxx,[CRC16],1      | 0,10000000,[CRC16],1                |                                        |

| DAT2         | 0,10xxxxxxxxxx,[CRC16],1      | 0,01000000,[CRC16],1                |                                        |

| DAT3         | 0,01xxxxxxxxxx,[CRC16],1      | 0,10000000,[CRC16],1                |                                        |

| DAT4         |                               | 0,00000000,[CRC16],1                | No data pattern sent                   |

| DAT5         |                               | 0,00000000,[CRC16],1                | No data pattern sent                   |

| DAT6         |                               | 0,00000000,[CRC16],1                | No data pattern sent                   |

| DAT7         |                               | 0,00000000,[CRC16],1                | No data pattern sent                   |

Table 14. 8-bit bus test pattern

| Data<br>line | Data pattern sent by the host | Reversed pattern sent by the device | Notes                                  |

|--------------|-------------------------------|-------------------------------------|----------------------------------------|

| DAT0         | 0,10xxxxxxxxxx,[CRC16],1      | 0,01000000,[CRC16],1                | Start bit defines beginning of pattern |

| DAT1         | 0,01xxxxxxxxxx,[CRC16],1      | 0,10000000,[CRC16],1                |                                        |

| DAT2         | 0,10xxxxxxxxxx,[CRC16],1      | 0,01000000,[CRC16],1                |                                        |

| DAT3         | 0,01xxxxxxxxxx,[CRC16],1      | 0,10000000,[CRC16],1                |                                        |

| DAT4         | 0,10xxxxxxxxxx,[CRC16],1      | 0,01000000,[CRC16],1                |                                        |

| DAT5         | 0,01xxxxxxxxxx,[CRC16],1      | 0,10000000,[CRC16],1                |                                        |

| DAT6         | 0,10xxxxxxxxxx,[CRC16],1      | 0,01000000,[CRC16],1                |                                        |

| DAT7         | 0,01xxxxxxxxxx,[CRC16],1      | 0,10000000,[CRC16],1                |                                        |

### 5.3.5 Bus width selection

After checking the bus functional lines, the host must change the bus width configuration accordingly. This is done by using the SWITCH command to program the BUS\_WIDTH byte in the modes segment of the EXT\_CSD register.

The BUS\_WIDTH byte is write only.

By default (after power-up or software reset (CMD0)), the contents of the BUS\_WIDTH byte is set to 0x00.

The valid values for this register are defined in Section 8.4.11: BUS\_WIDTH.

If the value programmed by the host is invalid, the BUS\_WIDTH byte remains unchanged and the SWITCH ERROR bit is set.

Figure 11. Data transfer formats

Figure 12. MultiMediaCard state diagram (Data Transfer mode)

- 1. See Table 10: Bus modes overview for the definition of the abbreviated forms corresponding to the device state.

- 2. 'r' and 'w' stand for read and write.

- 3. If the device was previously selected and was in Transfer state, its connection with the host is released and it moves back to the Standby state when a CMD7 command is issued along with any address different from the device own RCA.

- 4. Issuing the CMD7 command along with the reserved RCA 0x0000 returns to Standby state.

- 5. CMD7 commands issued along with the device RCA while the device is in Transfer state are ignored and may be treated as illegal commands.

- 6. After the device is assigned an RCA it will not respond to identification commands, CMD1, CMD2, or CMD3.

- The SET\_DSR (CMD4) broadcast command configures the device driver stages. It programs its DSR register according to the application bus length and the data transfer rate. The clock rate must then be switched from f<sub>OD</sub> to f<sub>PP</sub>.

- 8. The busy (Dat0=Low) is always active when the device is in Programming state. A host should not send CMD24/CMD25 while the device is in the Programming state and busy is active. However to ensure compatibility with previous MultiMediaCard specification, the device treats CMD24 and CMD25 as legal or illegal commands when in Programming state (while busy is active).

#### 5.3.6 Data Read

The DAT0-DAT7 input/outputs are High when no data is transmitted.

Data Reads allow data to be transferred from the device to the host. All Data Read commands can be aborted at any time by the STOP\_TRANSMISSION command (CMD12), which will terminate the data transfer and return the device to the Transfer state.

The DAT bus line is High when no data is transmitted. A transmitted data block consists of a start bit (Low), followed by a continuous data stream. The data stream contains the net payload data (and error correction bits if a non-embedded Error Correction is used). The data stream ends with an end bit (High) (see *Figure 19*, *Figure 20*, and *Figure 21*). The data transmission is synchronous to the clock signal.

The payload for block oriented data transfer is preserved by a CRC (Cyclic Redundancy Check) check sum.

# 5.3.7 Single Block/Multiple Block Read

The command CMD17 starts a single Block Read at the address specified in the command. After completion of the Single Block Read command, the device returns to the Transfer state

The command CMD18 starts a Multiple Block Read where several consecutive blocks of data are read. The starting address is specified in the command. The blocks will be continuously transferred until a STOP-TRANSMISSION command (CMD12) is issued. Note that the host CMD12 command has an execution delay due to the serial command transmission. The data transfer stops after the end bit of the CMD12 command.

The start address for a read operation can be any byte address in the valid address space of the memory card.

During Single or Multiple Block Read operations, the basic unit of data transferred is a block whose maximum size is defined in the CSD Register. If READ\_BL\_PARTIAL is set, smaller blocks whose starting and ending address are contained within one physical block may also be transmitted. A 16 bit CRC (Cyclic Redundancy Check) is appended to the end of each block ensuring data transfer integrity.

Multiple Block Read operations can be of two types:

# Open-ended Multiple Block Read operations the number of blocks is not defined and the device keeps transferring data blocks until a STOP\_TRANSMISSION command is issued.

### Multiple Block Read with pre-defined block count

The number of blocks to be transferred is pre-determined so the operation stops after the pre-set number of blocks has been transmitted. When the block count is pre-defined, the STOP\_TRANSMISSION command is not required unless an error occurs. To issue the Multiple Block Read operation with pre-defined block count, the READ\_MULTIPLE\_BLOCK command must be preceded by the SET\_BLOCK\_COUNT (CMD23) command, failing which the initiated Multiple Block Read operation will be open-ended.

If all the arguments of the CMD23 command are set to 0, the command is accepted. However, a subsequent read will follow the open-ended READ\_MULTIPLE\_BLOCK operation protocol (STOP\_TRANSMISSION command is required) If the host sends a STOP-TRANSMISSION command after the last block of a multiple block operation with a pre-defined number of blocks is transmitted, it is regarded as an illegal command, since the device is no longer in sending data state (Data).

If either one of the following errors is detected when the CMD17/CMD18 command is received, the device rejects the CMD17/CMD18 command, remains in Transfer state and sets the corresponding error bit:

- The address provides by the host as an argument to either CMD17 or CMD18 is out of range. ADDRESS\_OUT\_OF\_RANGE is set.

- The currently defined block length is illegal for a read operation. BLOCK\_LEN\_ERROR is set.

- The address/block-length combination positions the first data block is misaligned to the device physical blocks. ADDRESS\_MISALIGN is set.

If the device detects an error (e.g. address out of range, address misalignment, internal error, etc.) during a Multiple Block Read operation, it stops data transmission and remains in the sending data state (Data). The host must then abort the operation by sending the STOP-TRANSMISSION command. The read error is reported in the response to the STOP-TRANSMISSION command.

When the host uses partial blocks, if block misalignment is not allowed, the device returns a block misalignment condition (ADDRESS\_MISALIGN bit set to '1') if the total length of the partial blocks is not block aligned, and returns to Transfer state.