## 256K x 18 SSRAM

Synchronous Burst SRAM, Flow-Through

#### **FEATURES**

- Fast access times: 8, 10, and 15nsFast clock speed: 113, 100, and 66 MHz

- Fast clock and OE\ access times

- Single +3.3V +0.3V -0.165V power supply  $(V_{DD})$

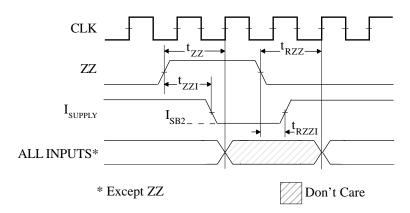

- SNOOZE MODE for reduced-power standby

- Common data inputs and data outputs

- Individual BYTE WRTIE control and GLOBAL WRITE

- Three chip enables for simple depth expansion and address pipelining

- Clock-controlled and registered addresses, data I/Os and control signals

- Interally self-timed WRITE cycle

- Burst control pin (interleaved or linear burst)

- Automatic power-down

- Low capacitive bus loading

- Operating Temperature Ranges:

- Military -55°C to +125°C

- Industrial -40°C to +85°C

| OPTIONS                         | MARKI | NG       |

|---------------------------------|-------|----------|

| • Timing                        |       |          |

| 7.5ns/8ns/113 MHz               | -8*   |          |

| 8.5ns/10ns/100 MHz              | -9    |          |

| 10ns/15ns/66 MHz                | -10   |          |

| • Packages                      |       |          |

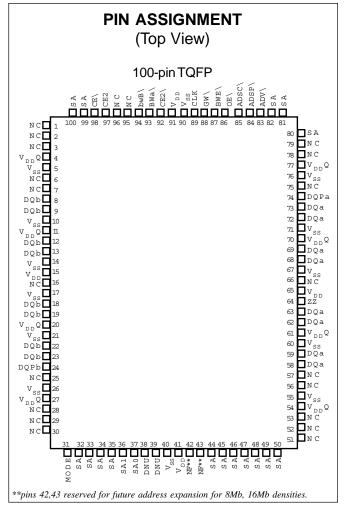

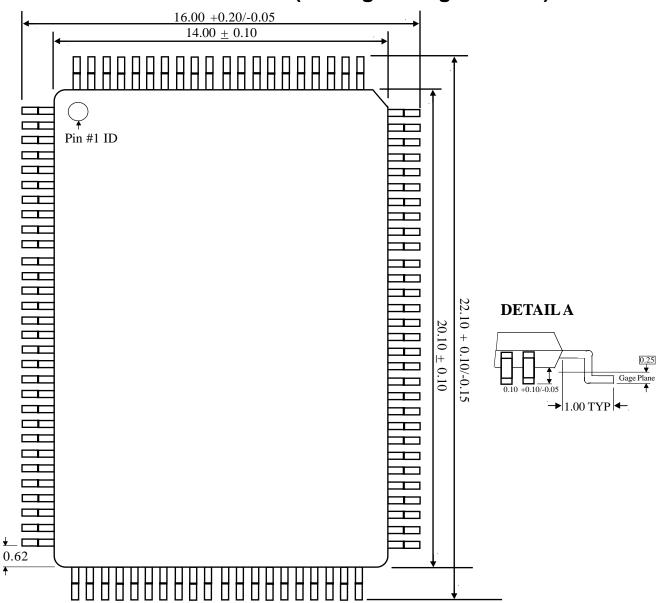

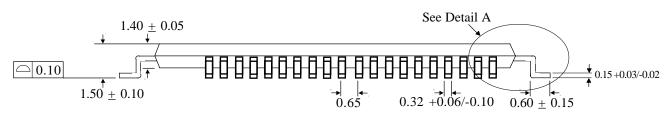

| 100-pin TQFP                    | DQ    | No. 1001 |

| • Operating Temperature Ranges: |       |          |

| - Military -55°C to +125°C      | IΤ    |          |

| - Industrial -45°C to +85°C     | XT    |          |

\*available as IT only

For more products and information please visit our web site at www.austinsemiconductor.com

#### GENERAL DESCRIPTION

The Austin Semiconductor, Inc. Synchronous Burst SRAM family employs high-speed, low power CMOS designs that are fabricated using an advanced CMOS process.

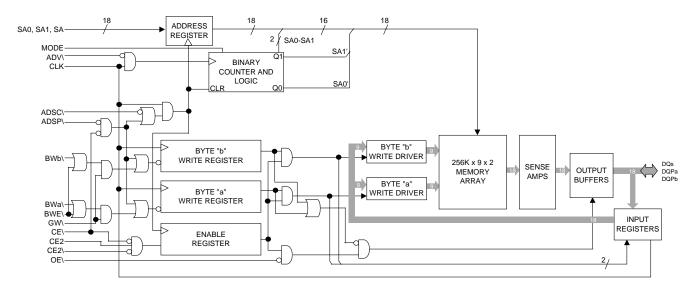

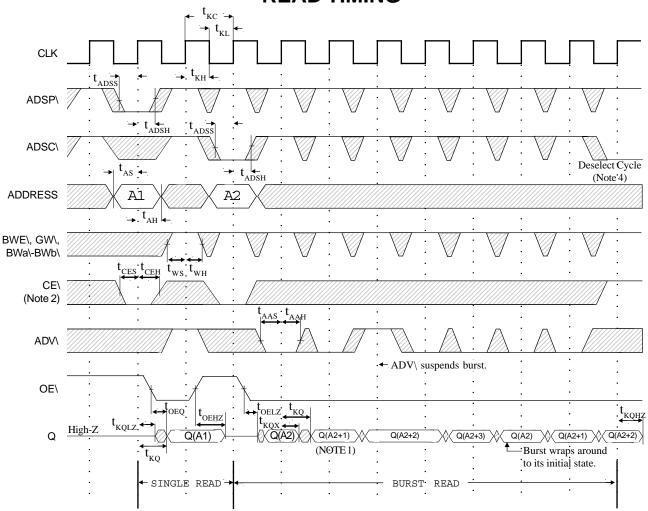

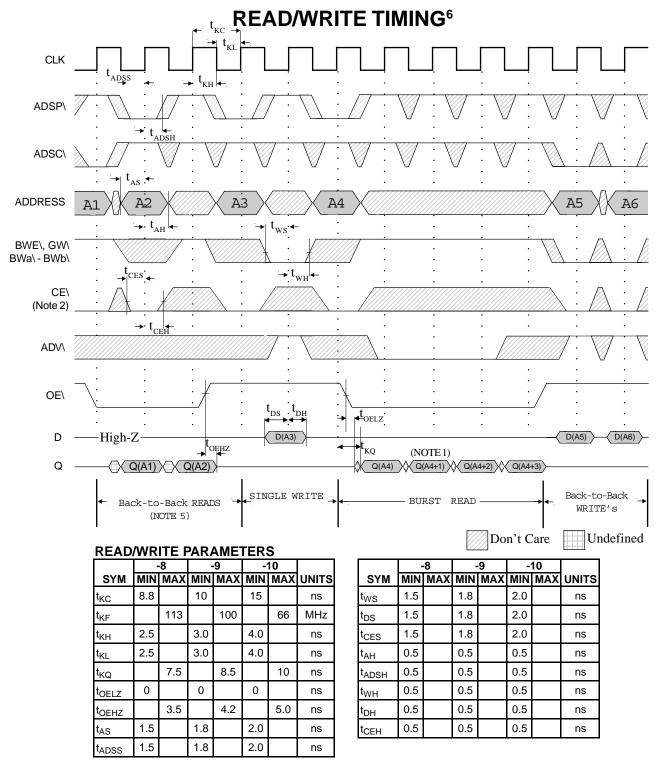

ASI's 4Mb Synchronous Burst SRAMs integrate a 256K x 18, SRAM core with advanced synchronous peripheral circuitry and a 2-bit burst counter. All synchronous inputs pass through registers controlled by a positive-edge-triggered single clock input (CLK). The synchronous inputs include all addresses, all data inputs, active LOW chip enable (CE\), two additional chip enables for easy depth expansion (CE2\),

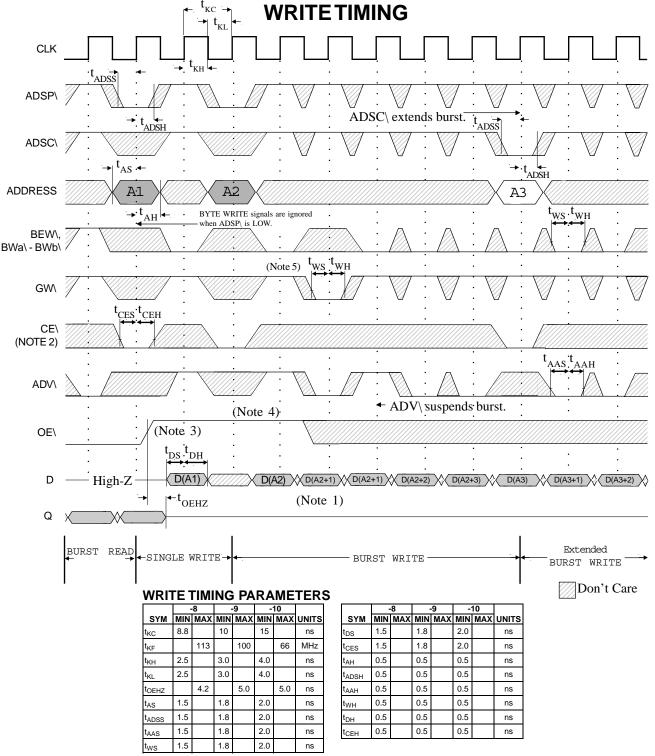

CE2), burst control inputs (ADSC\, ADSP\, ADV\), byte write enables (BWx\) and global write (GW\).

Asynchronous inputs include the output enable  $(OE\)$ , clock (CLK) and snooze enable (ZZ). There is also a burst mode input (MODE) that selects between interleaved and linear burst modes. The data-out (Q), enabled by  $OE\$ , is also asynchronous. WRITE cycles can be from one to two bytes wide, as controlled by the write control inputs.

Burst operation can be initiated with either address status processor (ADSP $\setminus$ ) or address status controller (ADSC $\setminus$ ) inputs. Subsequent burst addresses can be internally generated as controlled by the burst advance input (ADV $\setminus$ ).

Address and write control are registered on-chip to simplify WRITE cycles. This allows self-timed WRITE cycles. Individual byte enables allow individual bytes to be written. During WRITE cycles on this x18 device BWa\ controls DQa pins and DQPa; BWb\ controls DQb pins and DQPb. GW\ LOW causes all bytes to be written. Parity bits are available on this device.

ASI's 4Mb Synchronous Burst SRAMs operate from a  $+3.3 \mathrm{V} \mathrm{V}_{\mathrm{DD}}$  power supply, and all inputs and outputs are TTL-compatible. The device is ideally suited for 486, Pentium®, and PowerPC systems and those systems that benefit from a wide synchronous data bus.

### PIN DESCRIPTIONS

| PIN NUMBERS                            | SYM             | TYPE    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------|-----------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 37, 36, 32-35, 44-50,                  | SA0, SA1,<br>SA | Input   | Synchronous Address Inputs: These inputs are registered and must meet the setup and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 80-82, 99, 100<br>93, 94               | BWa\            | Input   | hold times around the rising edge of CLK.  Synchronous Byte Write Enables: These active LOW inputs allow individual bytes to be                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 00, 01                                 | BWb\            | mpat    | written and must meet the setup and hold times around the rising edge of CLK. A byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                        |                 |         | write enables is LOW for a WRITE cycle and HIGH for a READ cycle. BWa\ controls DQa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                        |                 |         | pins and DQPa; BWb\ controls DQb pins and DQPb.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 87                                     | BWE\            | Input   | Byte Write Enable: This active LOW input permits BYTE WRITE operations and must meet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 88                                     | GW∖             | Input   | the setup and hold times around the rising edge of CLK.  Global Write: This active LOW input allows a full 18-bit WRITE to occur independent of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                        | 0               | put     | BWE\ and BWx\ lines and must meet the setup and hold times around the rising edge of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                        |                 |         | CLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 89                                     | CLK             | Input   | Clock: This signal registers the addresses, data, chip enables, byte write enables and burst                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                        |                 |         | control inputs on its rising edge. All synchronous inputs must meet setup and hold times around the clock's rising edge.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 98                                     | CE\             | Input   | Synchronous Chip Enable: This active LOW input is used to enable the device and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                        |                 | ·       | Conditions the internal use of ADSP\. CE\ is sampled only when a new external address is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                        | 050             |         | loaded.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 92                                     | CE2\            | Input   | Synchronous Chip Enable: This active LOW input is used to enable the device and is sampled only when a new external address is loaded.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 97                                     | CE2             | Input   | Synchronous Chip Enable: This active HIGH input is used to enable the device and is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 31                                     | OLZ             | πραι    | sampled only when a new external address is loaded.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 86                                     | OE\             | Input   | Output Enable: This active LOW, asynchronous input enables the data I/O output drivers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                        | ,               |         | and the supplier of the suppli |

| 83                                     | ADV\            | Input   | Synchronous Address Advance: This active LOW input is used to advance the internal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                        |                 |         | burst counter, controlling burst access after the external address is loaded. A HIGH on this                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                        |                 |         | pin effectively causes wait states to be generated (no address advance). To ensure use of correct address during WRITE cycle, ADV\ must be HIGH at the rising edge of the first                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                        |                 |         | clock after an ADSP\ cycle is initiated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 84                                     | ADSP\           | Input   | Synchronous Address Status Processor: This active LOW input interrupts any ongoing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                        |                 |         | burst, causing a new external address to be registered. A READ is performed using the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                        |                 |         | new address, independent of the byte write enables and ADSC but dependent upon CE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                        |                 |         | CE2, and CE2\. ADSP\ is ignored if CE\ is HIGH. Power-down state is entered if CE2 if LOW or CE2\ is HIGH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 85                                     | ADSC\           | Input   | Synchronous Address Status Controller: This active LOW input interrupts any ongoing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 00                                     | 715001          | mpat    | burst, causing a new external address to be registered. A READ or WRITE is performed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                        |                 |         | using the new address if CE\ is LOW. ADSC\ is also used to place the chip into power-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                        |                 |         | down state when CE\ is HIGH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 31                                     | MODE            | Input   | Mode: This input selects the burst sequence. A LOW on this pin selects LINEAR BURST. A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                        |                 |         | NC or HIGH on this pin selects INTERLEAVED BURST. Do not alter input state while device is operating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 64                                     | ZZ              | Input   | Snooze Enable: This active HIGH, asynchronous input causes the device to enter a low-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |