# Typical Applications

The HMC282 LNA is ideal for:

- Millimeterwave Point-to-Point Radios

- VSAT

- SATCOM

# Features

Noise Figure: 3.5 dB

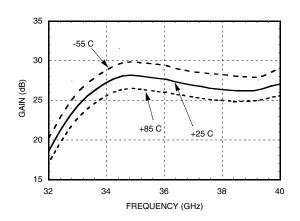

Stable Gain vs. Temperature: 26 dB ± 1.2 dB

Small Size: 1.11 mm x 2.07 mm

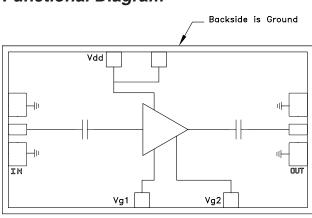

## Functional Diagram

### General Description

The HMC282 chip is a four stage GaAs MMIC Low Noise Amplifier (LNA) which covers the frequency range of 36 to 40 GHz. The chip can easily be integrated into Multi-Chip Modules (MCMs) due to its small (2.30 mm²) size. The chip utilizes a GaAs PHEMT process offering 26 dB gain from a bias supply of +3.5V @ 90mA with a noise figure of 3.5 dB. All data is with the chip in a 50 ohm test fixture connected via ribbon bonds of minimal length. The HMC282 may be used in conjunction with HMC259 mixer to realize a millimeterwave system receiver.

# Electrical Specifications, $T_A = +25^{\circ} C$ , $Vdd = +3.5V^*$ , Idd = 90 mA

| Parameter                                                                            | Min.    | Тур. | Max. | Min.    | Тур. | Max. | Units |

|--------------------------------------------------------------------------------------|---------|------|------|---------|------|------|-------|

| Frequency Range                                                                      | 36 - 40 |      |      | 37 - 39 |      |      | GHz   |

| Gain                                                                                 | 21      | 27   |      | 21      | 26   |      | dB    |

| Gain Flatness (Any 1 GHz BW)                                                         |         | ± 1  |      |         | ± 1  |      | dB    |

| Noise Figure                                                                         |         | 3.8  | 5.8  |         | 3.5  | 5.3  | dB    |

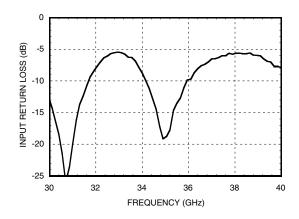

| Input Return Loss                                                                    |         | 7    |      |         | 6    |      | dB    |

| Output Return Loss                                                                   |         | 5    |      |         | 5    |      | dB    |

| Reverse Isolation                                                                    | 40      | 46   |      | 40      | 46   |      | dB    |

| Output Power for 1 dB Compression (P1dB)                                             | 5       | 9    |      | 5       | 9    |      | dBm   |

| Saturated Output Power (Psat)                                                        |         | 12   |      |         | 12   |      | dBm   |

| Output Third Order Intercept (IP3)                                                   | 18      | 25   |      | 21      | 27   |      | dBm   |

| Supply Current (Idd)<br>(Vdd = +3.5V, Vgg1, 2, 3, 4 = -0.15V Typ.)                   |         | 90   | 140  |         | 90   | 140  | mA    |

| *Vdd = +3.5V, adjust Vg1 & Vg2 between -2.0 to +0.4V to achieve ldd = 90 mA typical. |         |      |      |         |      |      |       |

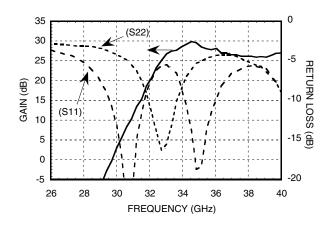

#### **Broadband Gain & Return Loss**

## Gain vs. Temperature

#### Input Return Loss

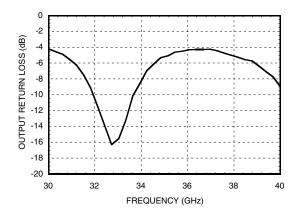

#### **Output Return Loss**

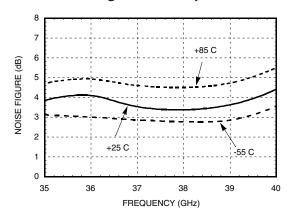

#### Noise Figure vs. Temperature

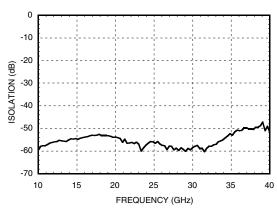

#### Isolation

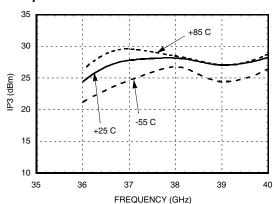

#### Output IP3 @ Vdd = +3.5V

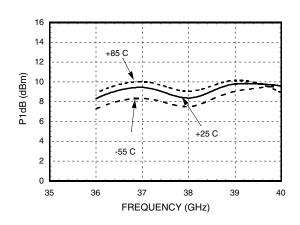

## P1dB @ Vdd = +3.5V

# Absolute Maximum Ratings

| Supply Voltage (Vdd)                         | +4 Vdc         |

|----------------------------------------------|----------------|

| Supply Current (ldd)                         | 200 mA         |

| Gate Bias Voltage (Vgg)                      | -2 to +0.4V    |

| DC Gate Current (Igg)                        | 4 mA           |

| Input Power (RFin) (Vdd = +3V)               | +13 dBm        |

| Channel Temperature (Tc)                     | 175 °C         |

| Thermal Resistance (⊖ jc) (Channel Backside) | 90 °C/W        |

| Storage Temperature                          | -65 to +150 °C |

| Operating Temperature                        | -55 to +85 °C  |

## **Outline Drawing**

ALL DIMENSION IN INCHES. ALL TOLERANCES ARE  $\pm$  0.025 (0.001). DIE THICKNESS IS 0.100 (0.004) BACKSIDE IS GROUND. BOND PADS ARE 0.100 (0.004) SQUARE. BACKSIDE METALLIZATION: GOLD. BOND PAD METALLIZATION: GOLD.

#### Mounting & Bonding Techniques for Millimeterwave GaAs MMICs

The die should be attached directly to the ground plane eutectically or with conductive epoxy (see HMC general Handling, Mounting, Bonding Note).

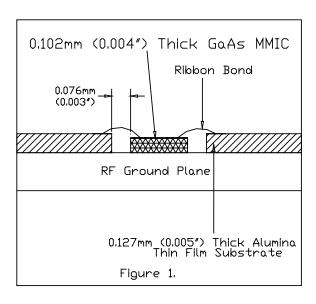

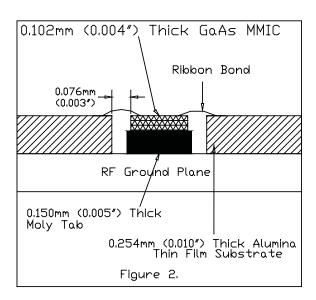

50 Ohm Microstrip transmission lines on 0.127 mm (5 mil) thick alumina thin film substrates are recommended for bringing RF to and from the chip (Figure 1). If 0.254 mm (10 mil) thick alumina thin film substrates must be used, the die should be raised 0.150 mm (6 mils) so that the surface of the die is coplanar with the surface of the substrate. One way to accomplish this is to attach the 0.102 mm (4 mil) thick die to a 0.150 mm (6 mil) thick molybdenum heat spreader (moly-tab) which is then attached to the ground plane (Figure 2).

Microstrip substrates should be brought as close to the die as possible in order to minimize bond wire length. Typical die-to-substrate spacing is 0.076 mm (3 mils). Gold ribbon of 0.076 mm x 0.013 mm (3 mil x 0.5 mil) is recommended to minimize inductance on the RF ports. 0.025 mm (1 mil) diameter ball or wedge bonds are acceptable for DC bias connections.

RF bypass capacitors should be used on the Vdd & Vgg inputs. 100 pF single layer capacitors (mounted eutectically or by conductive epoxy) placed no further than 0.762 mm (30 mils) from the chip are recommended.

## **Handling Precautions**

Follow these precautions to avoid permanent damage.

**Cleanliness:** Handle the chips in a clean environment. DO NOT attempt to clean the chip using liquid cleaning systems.

**Static Sensitivity:** Follow ESD precautions to protect against  $> \pm 250$ V ESD strikes.

**Transients:** Suppress instrument and bias supply transients while bias is applied. Use shielded signal and bias cables to minimize inductive pick-up.

**General Handling:** Handle the chip along the edges with a vacuum collet or with a sharp pair of bent tweezers. The surface of the chip has fragile air bridges and should not be touched with vacuum collet, tweezers, or fingers.

## Mounting

The chip is back-metallized and can be die mounted with AuSn eutectic preforms or with electrically conductive epoxy. The mounting surface should be clean and flat.

#### **Eutectic Die Attach:**

A 80/20 gold tin preform is recommended with a work surface temperature of 255 deg. C and a tool temperature of 265 deg. C. When hot 90/10 nitrogen/hydrogen gas is applied, tool tip temperature should be 290 deg. C. DO NOT expose the chip to a temperature greater than 320 deg. C for more than 20 seconds. No more than 3 seconds of scrubbing should be required for attachment.

#### **Epoxy Die Attach:**

Apply a minimum amount of epoxy to the mounting surface so that a thin epoxy fillet is observed around the perimeter of the chip once it is placed into position. Cure epoxy per the manufacturer's schedule.

# Wire Bonding

Ball or wedge bond with 0.025 mm (1 mil) diameter pure gold wire (DC Bias) or ribbon bond (RF ports) 0.076 mm x 0.013 mm (3 mil x 0.5 mil) size is recommended. Thermosonic wirebonding with a nominal stage temperature of 150 deg. C and a ball bonding force of 40 to 50 grams or wedge bonding force of 18 to 22 grams is recommended. Use the minimum level of ultrasonic energy to achieve reliable wirebonds. Wirebonds should be started on the chip and terminated on the package or substrate. All bonds should be as short as possible <0.31 mm (12 mils).