**Features**

### **Adaptive Step-Up Converters** with 1.5A Flash Driver

### **General Description**

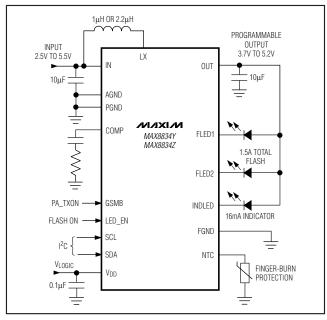

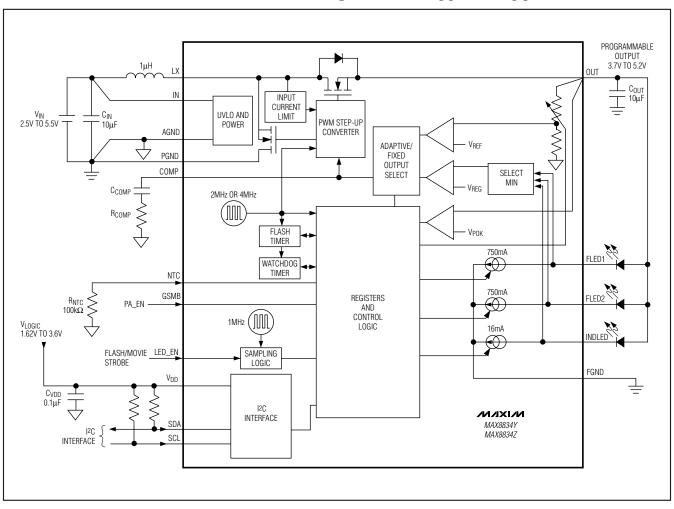

The MAX8834Y/MAX8834Z flash drivers integrate a 1.5A PWM DC-DC step-up converter and three programmable low-side, low-dropout LED current regulators. The step-up converter features an internal switching MOSFET and synchronous rectifier to improve efficiency and minimize external component count. An I<sup>2</sup>C interface provides flexible control of stepup converter output voltage setting, movie/flash mode selection, flash timer duration settings, and current regulator settings. The MAX8834Y/MAX8834Z operate down to 2.5V, making them future proof for new battery technologies.

The MAX8834Y/MAX8834Z consist of two current regulators for the flash/movie mode. Each current regulator can sink 750mA in flash mode and 125mA in movie mode. The MAX8834Y/MAX8834Z also integrate a 16mA lowcurrent regulator that can be used to indicate camera status. The indicator current regulator includes programmable ramp and blink timer settings. A programmable input current limit, invoked using the GSMB control, reduces the total current drawn from the battery during PA transmit events. This ensures the flash current is set to the maximum possible for any given operating condition. Additionally, the MAX8834Y/MAX8834Z include a MAXFLASH\* function that adaptively reduces flash current during low battery conditions to help prevent system undervoltage lockup.

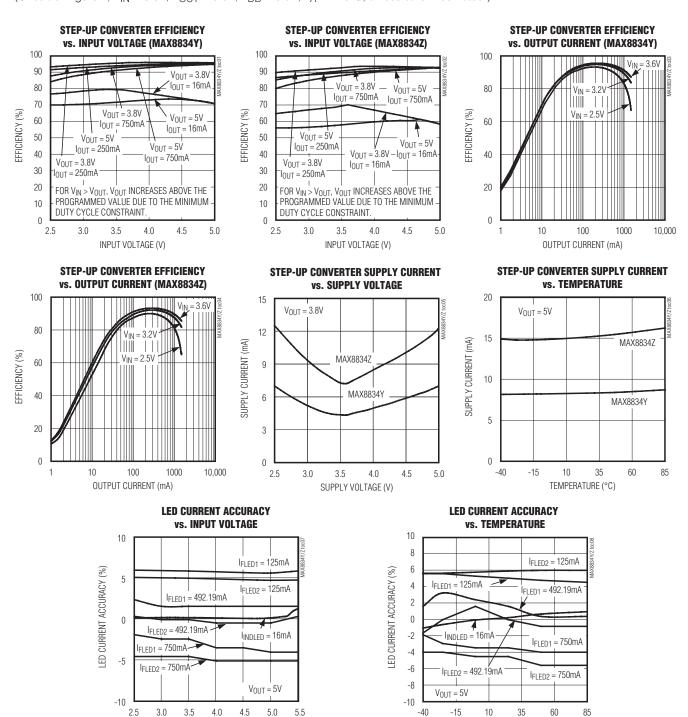

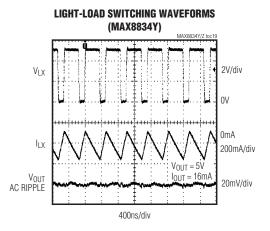

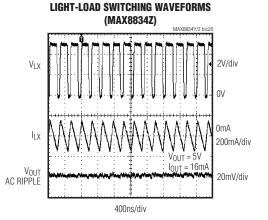

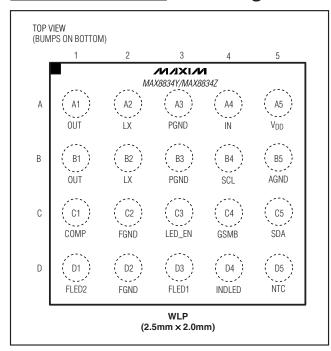

Other features include an optional NTC input for fingerburn protection and open/short LED detection. The MAX8834Y switches at 2MHz, providing best overall efficiency. The MAX8834Z switches at 4MHz, providing smallest overall solution size. The MAX8834Y/ MAX8834Z are available in a 20-bump, 0.5mm pitch WLP package (2.5mm x 2.0mm).

### **Ordering Information**

| PART          | TEMP<br>RANGE     | PIN-PACKAGE               | SWITCHING<br>FREQUENCY<br>(MHz) |

|---------------|-------------------|---------------------------|---------------------------------|

| MAX8834YEWP+T | -40°C to<br>+85°C | 20 WLP<br>(2.5mm x 2.0mm) | 2                               |

| MAX8834ZEWP+T | -40°C to<br>+85°C | 20 WLP<br>(2.5mm x 2.0mm) | 4                               |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package. T = Tape and reel.

Pin Configuration appears at end of data sheet.

### ♦ 2.5V to 5.5V Operation Range

- ♦ Step-Up DC-DC Converter 1.5A Guaranteed Output Current Adaptive or I<sup>2</sup>C Programmable Output Voltage 2MHz and 4MHz Switching Frequency Options

- **♦ Two Flash/Movie LED Current Regulators** I<sup>2</sup>C Programmable Flash and Movie Current Low-Dropout Voltage (110mV max) at 500mA

- **♦ LED Indicator Current Regulator** I<sup>2</sup>C Programmable Output Current Ramp and Blink Timers for Indicator Mode Low-Dropout Voltage (130mV max) at 16mA

- **♦ I<sup>2</sup>C Programmable Safety and Watchdog Timers**

- ♦ GSM Blank Logic Input

- **♦ MAXFLASH System Lockup Protection**

- **♦** Remote Temperature Sensor Input

- ♦ Open/Short LED Detection

- **♦ Thermal Shutdown Protection**

- ♦ < 1µA Shutdown Current

- ♦ 20-Bump, 0.5mm Pitch, 2.5mm x 2.0mm WLP

### **Applications**

Cell Phones and Smart Phones PDAs, Digital Cameras, and Camcorders

### **Typical Operating Circuit**

Maxim Integrated Products 1

<sup>\*</sup>Patent pending.

### **ABSOLUTE MAXIMUM RATINGS**

| IN, OUT, NTC to AGND           | 0.3V to +6.0V              |

|--------------------------------|----------------------------|

| V <sub>DD</sub> to AGND        | 0.3V to +4.0V              |

| SCL, SDA, LED_EN, GSMB to AGND |                            |

| FLED1, FLED2, INDLED to FGND   | 0.3V to $(V_{OUT} + 0.3V)$ |

| COMP to AGND                   | 0.3V to $(V_{IN} + 0.3V)$  |

| PGND, FGND to AGND             | 0.3V to +0.3V              |

| I <sub>L</sub> X Current (rms) | 3A                         |

|                                |                            |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |               |

|-------------------------------------------------------|---------------|

| (derate 17.5mW/°C above +70°C)                        | 1410mW        |

| Operating Temperature Range                           | 40°C to +85°C |

| Junction Temperature                                  | +150°C        |

| Storage Temperature Range                             |               |

| Bump Temperature* (soldering)                         | +260°C        |

|                                                       |               |

<sup>\*</sup>This device is constructed using a unique set of packaging techniques that impose a limit on the thermal profile the device can be exposed to during board level solder attach and rework. This limit permits only the use of the solder profiles recommended in the industry-standard specification, JEDEC 020A, paragraph 7.6, Table 3 for IR/VPR and Convection reflow. Preheating is required. Hand or wave soldering is not allowed.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = 3.6V, V_{AGND} = V_{PGND} = V_{FGND} = 0V, V_{DD} = 1.8V, T_{A} = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_{A} = +25^{\circ}C$ .) (Note 1)

| PARAMETER                                                                          | CONDITIONS                                                                           |                                                                |      | TYP  | MAX                      | UNITS |

|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------|------|------|--------------------------|-------|

| IN Operating Voltage                                                               |                                                                                      |                                                                | 2.5  |      | 5.5                      | V     |

| V <sub>DD</sub> Operating Range                                                    |                                                                                      |                                                                | 1.62 |      | 3.6                      | V     |

| V <sub>DD</sub> Undervoltage Lockout<br>(UVLO) Threshold                           | V <sub>DD</sub> falling                                                              |                                                                | 1.25 | 1.4  | 1.55                     | V     |

| V <sub>DD</sub> UVLO Hysteresis                                                    |                                                                                      |                                                                |      | 50   |                          | mV    |

| IN UVLO Threshold                                                                  | V <sub>IN</sub> falling                                                              |                                                                | 2.15 | 2.3  | 2.45                     | V     |

| IN UVLO Hysteresis                                                                 |                                                                                      |                                                                |      | 50   |                          | mV    |

| IN Standby Supply Current                                                          | $V_{SCL} = V_{SDA} = V_{DD}, V_{IN} = 5.5V,$                                         | I <sup>2</sup> C ready                                         |      |      | 1                        | μΑ    |

| V <sub>DD</sub> Standby Supply Current (All Outputs Off, I <sup>2</sup> C Enabled) | V <sub>SCL</sub> = V <sub>SDA</sub> = V <sub>DD</sub> = 3.6V, I <sup>2</sup> C ready |                                                                |      | 4    | 7                        | μΑ    |

| LOGIC INTERFACE                                                                    |                                                                                      |                                                                |      |      |                          |       |

|                                                                                    |                                                                                      | LED_EN, GSMB                                                   | 1.4  |      |                          |       |

| Logic Input-High Voltage                                                           | V <sub>DD</sub> = 1.62V to 3.6V SCL, SDA                                             | 0.7 x<br>V <sub>DD</sub>                                       |      |      | V                        |       |

|                                                                                    |                                                                                      | LED_EN, GSMB                                                   |      |      | 0.4                      |       |

| Logic Input-Low Voltage                                                            | V <sub>DD</sub> = 1.62V to 3.6V                                                      |                                                                |      |      | 0.3 x<br>V <sub>DD</sub> | V     |

| LED_EN Minimum High Time<br>(LED_EN is Internally Sampled<br>by a 1MHz Clock)      |                                                                                      |                                                                |      | 1    |                          | μs    |

| LED_EN Propagation Delay                                                           | From LED_EN going high to risin regulator                                            |                                                                | 3    |      | μs                       |       |

| LED_EN and GSMB Pulldown<br>Resistor                                               |                                                                                      |                                                                | 400  | 800  | 1600                     | kΩ    |

| Logic Input Current (SCL, SDA)                                                     | $V_{IL} = 0V \text{ or } V_{IH} = 3.6V$                                              | T <sub>A</sub> = +25°C                                         | -1   | 0.01 | +1                       |       |

| Logic input current (SCL, SDA)                                                     | VIL - UV UI VIH = 3.0V                                                               | $V_{IL} = 0V \text{ or } V_{IH} = 3.6V$ $T_{A} = +85^{\circ}C$ |      | 0.1  |                          | μA    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN}=3.6V,\,V_{AGND}=V_{PGND}=V_{FGND}=0V,\,V_{DD}=1.8V,\,T_{A}=-40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_{A}=+25^{\circ}C$ .) (Note 1)

| PARAMETER                                            | COI                                                                                    | NDITIONS              |                      | MIN   | TYP   | MAX   | UNITS |  |

|------------------------------------------------------|----------------------------------------------------------------------------------------|-----------------------|----------------------|-------|-------|-------|-------|--|

| Shutdown Leakage Current                             | IN and V <sub>DD</sub> in UVLO,                                                        |                       | $T_A = +25^{\circ}C$ | -1    | 0.01  | +1    | μA    |  |

|                                                      | VLED_EN = VGSMB = 0V                                                                   |                       | $T_A = +85^{\circ}C$ |       | 0.1   |       | μΑ    |  |

| I <sup>2</sup> C INTERFACE                           |                                                                                        |                       |                      |       |       |       |       |  |

| SDA Output Low Voltage                               | I <sub>SDA</sub> = 3mA                                                                 |                       |                      |       | 0.03  | 0.4   | V     |  |

| I <sup>2</sup> C Clock Frequency                     |                                                                                        |                       |                      |       |       | 400   | kHz   |  |

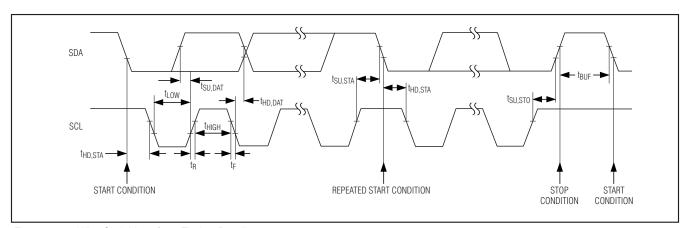

| Bus-Free Time Between STOP and START                 | tBUF                                                                                   |                       |                      | 1.3   |       |       | μs    |  |

| Hold Time Repeated START<br>Condition                | tHD_STA                                                                                |                       |                      | 0.6   | 0.1   |       | μs    |  |

| SCL Low Period                                       | tLOW                                                                                   |                       |                      | 1.3   | 0.2   |       | μs    |  |

| SCL High Period                                      | thigh                                                                                  |                       |                      | 0.6   | 0.2   |       | μs    |  |

| Setup Time Repeated START<br>Condition               | tsu_sta                                                                                |                       |                      | 0.6   | 0.1   |       | μs    |  |

| SDA Hold Time                                        | thd_dat                                                                                |                       |                      | 0     | -0.01 |       | μs    |  |

| SDA Setup Time                                       | tsu_dat                                                                                |                       |                      | 100   | 50    |       | ns    |  |

| Setup Time for STOP Condition                        | tsu_sto                                                                                |                       |                      | 0.6   | 0.1   |       | μs    |  |

| STEP-UP DC-DC CONVERTER                              |                                                                                        |                       |                      |       |       |       |       |  |

| OUT Voltage Range                                    | 100mV steps                                                                            |                       | 3.7                  |       | 5.2   | V     |       |  |

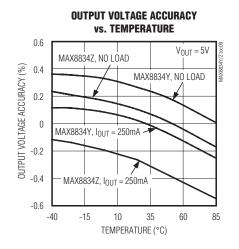

| OUT Voltage Accuracy                                 | No load, Vout = 5V                                                                     |                       |                      | -2.75 | ±0.5  | +2.75 | %     |  |

| OUT Overvoltage Protection                           | When running in adaptive                                                               | e mode                |                      | 5.2   | 5.35  | 5.5   | V     |  |

| Adaptive Output Voltage<br>Regulation Threshold      | I <sub>FLED1</sub> = I <sub>FLED2</sub> = 492.24mA setting, I <sub>INDLED</sub> = 16mA |                       |                      | 150   |       | mV    |       |  |

| PGOOD Window Comparator                              | V <sub>OUT</sub> = 5V, in programma                                                    | able mode             |                      | -15   | -12.5 | -10   | %     |  |

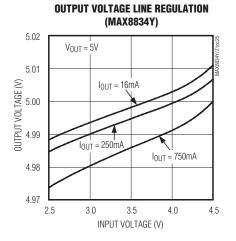

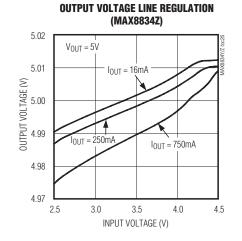

| Line Regulation                                      | V <sub>IN</sub> = 2.5V to 4.2V                                                         |                       |                      |       | 0.1   |       | %/V   |  |

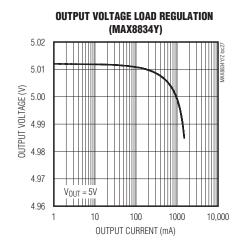

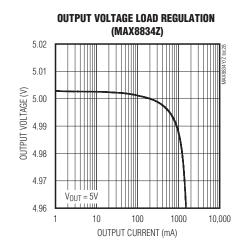

| Load Regulation                                      | I <sub>OUT</sub> = 0mA to 1500mA                                                       |                       |                      |       | 0.5   |       | %/A   |  |

| nFET Current Limit                                   |                                                                                        |                       |                      |       | 3.6   |       | А     |  |

| LX nFET On-Resistance                                | LX to PGND, I <sub>LX</sub> = 200mA                                                    | 4                     |                      |       | 0.055 | 0.130 | Ω     |  |

| LX pFET On-Resistance                                | LX to OUT, I <sub>LX</sub> = 200mA                                                     |                       |                      |       | 0.12  | 0.200 | Ω     |  |

|                                                      |                                                                                        | T <sub>A</sub> = +25  | °C                   |       | 0.1   | 1     |       |  |

| LX Leakage                                           | $V_{LX} = 5.5V$                                                                        | $T_A = +85$           | °C                   |       | 0.1   |       | μΑ    |  |

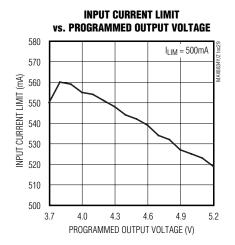

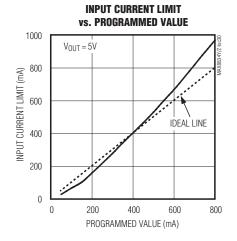

| Input Current Limit Range During<br>GSMB Trigger     | 110                                                                                    |                       | 50                   |       | 800   | mA    |       |  |

| Input Current Limit Step Size<br>During GSMB Trigger |                                                                                        |                       |                      | 50    |       | mA    |       |  |

| Input Current Limit Accuracy                         | I <sub>ILIM</sub> = 100mA, in dropou                                                   | t mode                |                      | -15   |       | +15   | %     |  |

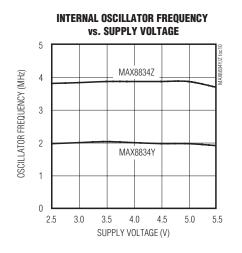

|                                                      | MAYOOAY                                                                                | T <sub>A</sub> = +25  | 5°C                  | 1.8   | 2     | 2.2   |       |  |

| Operation Francisco No. 1                            | MAX8834Y                                                                               | $T_A = -40^{\circ}$   | °C to +85°C          | 1.6   |       | 2.4   | 1     |  |

| Operating Frequency, No Load                         | MAV00047                                                                               | $T_A = +25$           |                      | 3.6   | 4     | 4.4   | - MHz |  |

|                                                      | MAX8834Z                                                                               | $T_{A} = -40^{\circ}$ | °C to +85°C          | 3.2   |       | 4.8   |       |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN}=3.6V,\,V_{AGND}=V_{PGND}=V_{FGND}=0V,\,V_{DD}=1.8V,\,T_{A}=-40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_{A}=+25^{\circ}C$ .) (Note 1)

| PARAMETER                                  | CC                                  | ONDITIONS                                                       | MIN  | TYP  | MAX  | UNITS  |

|--------------------------------------------|-------------------------------------|-----------------------------------------------------------------|------|------|------|--------|

| Maximum Duty Cycle                         | V <sub>OUT</sub> = 4.5V             |                                                                 | 69   | 75   |      | %      |

| Minimum Duty Cycle                         | V <sub>OUT</sub> = 4.5V             |                                                                 |      | 7.5  |      | %      |

| COMP Transconductance                      | V <sub>COMP</sub> = 1.5V            |                                                                 |      | 55   |      | μS     |

| COMP Discharge Resistance                  | During shutdown or UVL              | O, from COMP to AGND                                            |      | 120  |      | Ω      |

| OUT Discharge Resistance                   | During shutdown or UVL              | O, from OUT to LX                                               |      | 10   |      | kΩ     |

| FLED1/FLED2 CURRENT REGU                   | LATOR                               |                                                                 |      |      |      |        |

| IN Supply Current                          | Step-up off, FLED1/FLED             | 02 on, supply current for each                                  |      | 0.6  |      | mA     |

| Maximum Current Catting                    | Flash                               |                                                                 |      | 750  |      | mA     |

| Maximum Current Setting                    | Movie                               |                                                                 |      | 125  |      | 1 IIIA |

|                                            | 23.44mA setting                     | T <sub>A</sub> = +25°C                                          | -5   |      | +20  | %      |

|                                            | 100.01 1 11                         | T <sub>A</sub> = +25°C                                          | -2.5 | ±0.5 | +2.5 | 0,     |

| Current Accuracy                           | 492.24mA setting                    | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                   | -4   |      | +4   | %      |

|                                            | 750mA setting                       | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                   | -10  |      | +5   | %      |

| Current Regulator Dropout                  | 492.24mA setting                    | 1                                                               |      |      | 110  | ,,     |

| (Note 2)                                   | 93.75mA setting                     |                                                                 |      | 50   | 100  | mV     |

| FLED1/FLED2 Leakage in                     | V 5.5V                              | T <sub>A</sub> = +25°C                                          | -1   | 0.01 | +1   | μА     |

|                                            | $V_{FLED1} = V_{FLED2} = 5.5V$      | $T_A = +25^{\circ}C$ $T_A = +85^{\circ}C$                       |      | 0.1  |      |        |

| INDLED CURRENT REGULATO                    | R                                   |                                                                 | '    |      |      |        |

| IN Supply Current                          | Step-up converter off, IN           | Step-up converter off, INDLED on                                |      | 0.6  |      | mA     |

| Maximum Current Setting                    |                                     |                                                                 |      | 16   |      | mA     |

|                                            | 0.5mA setting                       | $T_A = +25^{\circ}C$                                            | -10  |      | +10  | %      |

| Current Accuracy                           | 16mA setting                        | $T_A = +25^{\circ}C$                                            | -3   | ±0.5 | +3   | %      |

|                                            | Toma setting                        | $T_A = -40$ °C to $+85$ °C                                      | -5   |      | +5   | %      |

| Current Regulator Dropout                  | 16mA setting (Note 2)               |                                                                 |      | 55   | 130  | mV     |

| INDLED Leakage in Shutdown                 | VINDLED = 5.5V                      | $T_A = +25^{\circ}C$                                            | -1   | 0.01 | +1   | μΑ     |

| INDEED Leakage III Shuldown                | VINDLED - 3.3V                      | $T_A = +85^{\circ}C$                                            |      | 0.1  |      | μΑ     |

| PROTECTION CIRCUITS                        |                                     |                                                                 |      |      |      |        |

| NTC BIAS Current                           |                                     |                                                                 | 19.4 | 20   | 20.6 | μΑ     |

| NTC Overtemperature Detection Threshold    | V <sub>NTC</sub> falling, 100mV hys | V <sub>NTC</sub> falling, 100mV hysteresis, NTC_CNTL[2:0] = 100 |      | 400  | 412  | mV     |

| NTC Short Detection Threshold              | V <sub>NTC</sub> falling            |                                                                 |      | 100  |      | mV     |

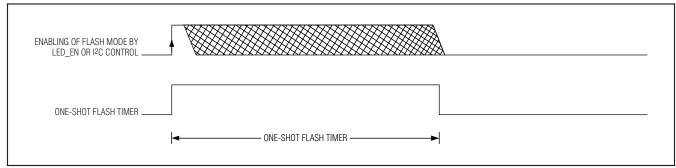

| Flash Duration Timer Range                 | In 50ms steps (Note 3)              |                                                                 | 50   |      | 800  | ms     |

| Flash Duration Timer Accuracy              | T <sub>A</sub> = +25°C              |                                                                 | 360  | 400  | 440  |        |

| (400ms Setting)                            | $T_A = -40$ °C to $+85$ °C          |                                                                 | 320  |      | 480  | ms     |

| Minimum Flash Duration                     | FLASH_EN[2:0] = 1XX                 |                                                                 |      | 2    |      | ms     |

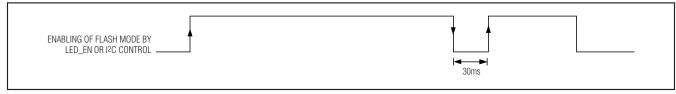

| Flash Safety Timer Reset Inhibit<br>Period | From falling edge of LEI reset      | From falling edge of LED_EN until flash safety timer is         |      | 30   |      | ms     |

| Watchdog Timer Range                       | In 4s steps                         |                                                                 | 4    |      | 16   | S      |

|                                            |                                     |                                                                 |      |      |      |        |

4 \_\_\_\_\_\_*NIAXIN*I

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN}=3.6V,\,V_{AGND}=V_{PGND}=V_{FGND}=0V,\,V_{DD}=1.8V,\,T_{A}=-40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_{A}=+25^{\circ}C$ .) (Note 1)

| PARAMETER                                            | CONDITIONS                                                              | MIN | TYP                      | MAX | UNITS |

|------------------------------------------------------|-------------------------------------------------------------------------|-----|--------------------------|-----|-------|

| Watchdog Timer Accuracy                              | T <sub>A</sub> = +25°C                                                  | 3.6 | 4                        | 4.4 | _     |

| (4s setting)                                         | $T_A = -40$ °C to $+85$ °C                                              | 3.2 |                          | 4.8 | s     |

| Open LED Detection Threshold                         | FLED1, FLED2, INDLED enabled                                            |     |                          | 100 | mV    |

| Shorted LED Detection Threshold                      | FLED1, FLED2, INDLED enabled                                            |     | V <sub>OUT</sub> -<br>1V |     | V     |

| Open and Short Debounce Timer                        | From LED open or short detected until LED current regulator is disabled |     | 30                       |     | ms    |

| Thermal-Shutdown Hysteresis                          |                                                                         |     | 20                       |     | °C    |

| Thermal Shutdown                                     |                                                                         |     | +160                     |     | °C    |

| MAXFLASH                                             |                                                                         |     |                          |     |       |

| Low-Battery Detect Threshold Range                   | 33mV steps                                                              | 2.5 |                          | 3.4 | V     |

| Low-Battery Voltage Threshold Accuracy               |                                                                         |     | ±2.5                     |     | %     |

| Low-Battery Voltage Hysteresis<br>Programmable Range |                                                                         | 100 |                          | 200 | mV    |

| Low-Battery Voltage Hysteresis<br>Step Size          |                                                                         |     | 100                      |     | mV    |

| Low Pottory Popot Time                               | LB_TMR[1:0] = 00                                                        | 200 | 250                      | 300 |       |

| Low-Battery Reset Time                               | LB_TMR[1:0] = 01                                                        | 400 | 500                      | 600 | μs    |

- Note 1: All devices are 100% production tested at T<sub>A</sub> = +25°C. Limits over the operating temperature range are guaranteed by design.

- **Note 2:** LED current regulator dropout voltage is defined as the voltage when current drops 10% from the current level measured at 0.6V.

- Note 3: Flash duration is from rising edge of LED\_EN until IFLED = 0A (safety time in one-shot mode).

- **Note 4:** The adaptive output voltage regulation threshold is individually set on each device to 75mV above the dropout voltage of the LED current regulators. This ensures minimum power dissipation on the IC during a flash event. The dropout voltage chosen is the highest measured dropout voltage of FLED1, FLED2, and INDLED.

### **Typical Operating Characteristics**

(Circuit of Figure 1, V<sub>IN</sub> = 3.6V, V<sub>OUT</sub> = 3.8V, V<sub>DD</sub> = 3.0V, T<sub>A</sub> = +25°C, unless otherwise noted.)

5.0

INPUT VOLTAGE (V)

10

TEMPERATURE (°C)

60

### Typical Operating Characteristics (continued)

(Circuit of Figure 1,  $V_{IN}$  = 3.6V,  $V_{OUT}$  = 3.8V,  $V_{DD}$  = 3.0V,  $T_A$  = +25°C, unless otherwise noted.)

### Typical Operating Characteristics (continued)

(Circuit of Figure 1, V<sub>IN</sub> = 3.6V, V<sub>OUT</sub> = 3.8V, V<sub>DD</sub> = 3.0V, T<sub>A</sub> = +25°C, unless otherwise noted.)

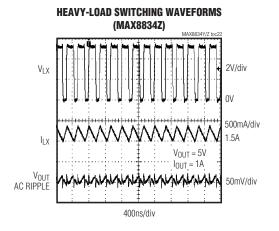

### Typical Operating Characteristics (continued)

(Circuit of Figure 1,  $V_{IN}$  = 3.6V,  $V_{OUT}$  = 3.8V,  $V_{DD}$  = 3.0V,  $T_A$  = +25°C, unless otherwise noted.)

# VLX VLX VOUT = 5V VOUT AC RIPPLE HEAVY-LOAD SWITCHING WAVEFORMS (MAX8834Y) 2V/div 0V 1.5A 500mA/div 50mV/div

### Typical Operating Characteristics (continued)

(Circuit of Figure 1,  $V_{IN} = 3.6V$ ,  $V_{OUT} = 3.8V$ ,  $V_{DD} = 3.0V$ ,  $T_A = +25$ °C, unless otherwise noted.)

10 \_\_\_\_\_\_ /N/XI/V

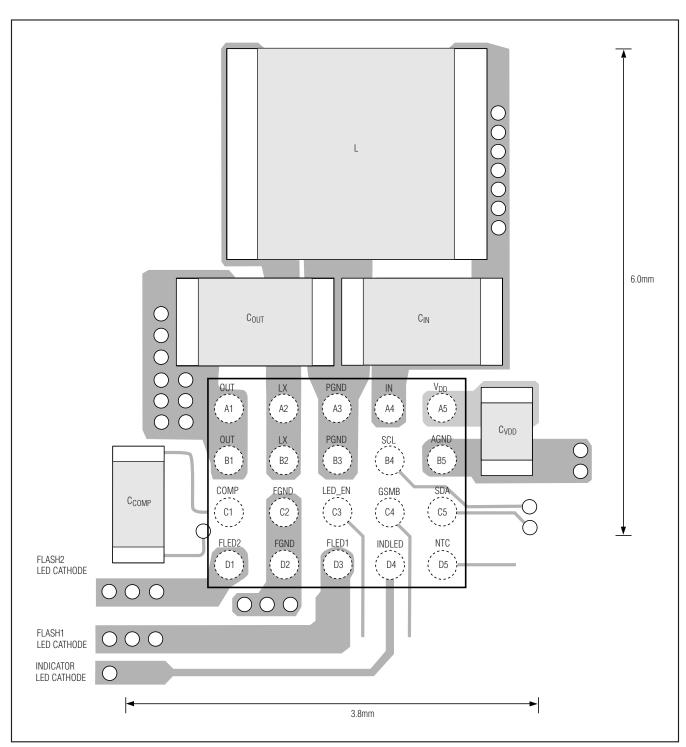

### Pin Description

| PIN    | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|--------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| A1, B1 | OUT             | Regulator Output. Connect OUT to the anodes of the external LEDs. Bypass OUT to PGND with a $10\mu F$ ceramic capacitor. OUT is connected to LX through an internal $10k\Omega$ resistor during shutdown.                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| A2, B2 | LX              | nductor Connection. Connect LX to the switched side of the inductor. LX is internally connected ne drains of the internal MOSFETs. LX is connected to OUT through an internal $10 \text{k}\Omega$ resistor duhutdown.                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| A3, B3 | PGND            | Power Ground. Connect PGND to AGND and to the input capacitor ground. Connect PGND to the PCB ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| A4     | IN              | Analog Supply Voltage Input. The input voltage range is 2.5V to 5.5V. Bypass IN to AGND and PGND with a 10µF ceramic capacitor as close as possible to the IC. IN is high impedance during shutdown.                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| A5     | V <sub>DD</sub> | Logic Input Supply Voltage. Connect V <sub>DD</sub> to the logic supply driving SCL, SDA, LED_EN, and GSMB. Bypass V <sub>DD</sub> to AGND with a 0.1µF ceramic capacitor. When V <sub>DD</sub> is below the UVLO, the I <sup>2</sup> C registers reset and the step-up converter turns off.                                                                                                                                                                                                                                                                              |  |  |  |  |

| B4     | SCL             | I <sup>2</sup> C Clock Input. Data is read on the rising edge of SCL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| B5     | AGND            | Analog Ground. Connect AGND to PGND and to the input capacitor ground. Connect AGND to the PCB ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| C1     | COMP            | Compensation Input. See the <i>Compensation Network Selection</i> section for details. COMP is internally pulled to AGND through a $180\Omega$ resistor in shutdown.                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| C2, D2 | FGND            | FLED1/FLED2 and INDLED Power Ground. Connect FGND to PGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| СЗ     | LED_EN          | LED Enable Logic Input. LED_EN controls FLED1, FLED2, and INDLED, depending on control bits written into the LED_CNTL register. See the LED_EN Control register description for an explanation of this input function. LED_EN has an internal 800kΩ pulldown resistor to AGND.                                                                                                                                                                                                                                                                                            |  |  |  |  |

| C4     | GSMB            | GSM Blank Signal. Assert GSMB to reduce the current regulator settings according to the values programmed into the GSMB_CUR register. The status of the flash safety timer and the flash/movie mode values in the current regulator registers are not affected by the GSMB state. Connect GSMB to the PA module enable signal or other suitable logic signal that indicates a GSM transmit is in process. Polarity of this signal is set by a bit in the GSMB_CUR register (default is active-high). GSMB has an internal $800 \text{k}\Omega$ pulldown resistor to AGND. |  |  |  |  |

| C5     | SDA             | I <sup>2</sup> C Data Input. Data is read on the rising edge of SCL and data is clocked out on the falling edge of SCL.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| D1     | FLED2           | FLED2 Current Regulator. Current flowing into FLED2 is based on the internal I <sup>2</sup> C registers FLASH2_CUR and MOVIE_CUR. Connect FLED2 to the cathode of an external flash LED or LED module. FLED2 is high impedance during shutdown. If unused, connect FLED2 to ground.                                                                                                                                                                                                                                                                                       |  |  |  |  |

| D3     | FLED1           | FLED1 Current Regulator. Current flowing into FLED1 is based on the internal I <sup>2</sup> C registers FLASH1_CUR and MOVIE_CUR. Connect FLED1 to the cathode of an external flash LED or LED module. FLED1 is high impedance during shutdown. If unused, connect FLED1 to ground.                                                                                                                                                                                                                                                                                       |  |  |  |  |

| D4     | INDLED          | INDLED Current Regulator. Current flowing into INDLED is based on the internal I <sup>2</sup> C registers IND_CUR. Connect INDLED to the cathode of an external indicator LED. INDLED is high impedance during shutdown. If unused, connect INDLED to ground.                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| D5     | NTC             | NTC Bias Output. NTC provides 20µA to bias the NTC thermistor. The NTC voltage is compared to the trip threshold programmed by the NTC_CNTL register. NTC is high impedance during shutdown. Connect NTC to IN if not used. See the <i>Finger-Burn Protection (NTC)</i> section for details.                                                                                                                                                                                                                                                                              |  |  |  |  |

### **Detailed Description**

The MAX8834Y/MAX8834Z flash drivers integrate an adaptive 1.5A PWM step-up DC-DC converter, two 750mA white LED camera flash/movie current regulators, and a 16mA indicator LED current regulator. An I<sup>2</sup>C interface controls individual output on/off, the step-up output voltage setting, the movie/flash current, and the flash timer duration settings.

#### Step-Up Converter (LX, OUT, COMP, PGND)

The MAX8834Y/MAX8834Z include a fixed-frequency, PWM step-up converter that supplies power to the flash LEDs. The output voltage is programmable from 3.7V to 5.2V (in 100mV steps) through the I<sup>2</sup>C interface. The output voltage can also be set adaptively based on the LED forward voltage. The step-up converter switches an internal power MOSFET and synchronous rectifier at a constant 2MHz or 4MHz frequency, with varying duty cycle up to 75%, to maintain constant output voltage as the input voltage and load vary. Internal circuitry prevents any unwanted subharmonic switching by forcing a minimum 7% (typ) duty cycle.

When the step-up converter is set to dropout mode, the internal synchronous rectifier is driven fully on, keeping the voltage at OUT equal to the LX input. This mode provides the lowest current consumption when driving LEDs with low forward voltage.

The output voltage is internally monitored for a fault condition. If the output voltage drops below 8% (typ) of the nominal programmed value, a POK fault is indicated in STATUS1 register bit 5. This feature is disabled if the step-up converter is set to operate in adaptive mode.

#### Overvoltage Protection

The MAX8834Y/MAX8834Z include a comparator to monitor the output voltage (VOUT) during adaptive mode operation of the step-up converter. If at anytime the output voltage exceeds a maximum threshold of 5.5V, the COMP capacitor is discharged until the output voltage is reduced by the 200mV (typ) hysteresis. Once the output voltage drops below this threshold, normal charging of the COMP capacitor is resumed.

### Flash Current Regulator (FLED1 and FLED2)

A low-dropout linear current regulator from FLED1/FLED2 to FGND sinks current from the cathode terminal of the flash LED(s). The FLED1/FLED2 current is regulated to I<sup>2</sup>C programmable levels for movie mode (up to 125mA, see Table 5) and flash mode (up to 750mA,

see Tables 3 and 4). The movie mode provides continuous lighting when enabled through I<sup>2</sup>C or LED\_EN. When the flash mode is enabled, a flash safety timer, programmable from 50ms to 800ms through I<sup>2</sup>C, limits the duration of the flash mode. Once the flash safety timer expires, the current regulators return to movie mode if movie mode was active when a flash event was triggered. The flash mode has priority over the movie mode.

#### Flash Safety Timer

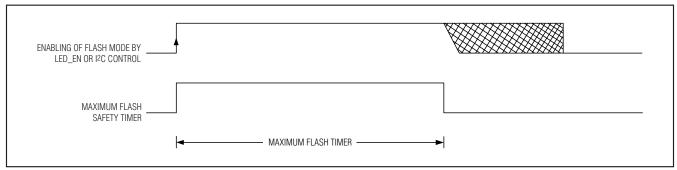

The flash safety timer is activated any time flash mode is selected, either with LED\_EN or through the I<sup>2</sup>C interface.

The flash safety timer, programmable from 50ms to 800ms through  $I^2C$ , limits the duration of the flash mode in case LED\_EN is stuck high or the  $I^2C$  command to turn off has not been sent within the programmed flash safety timer duration. This timer can be configured to operate either in one-shot mode or maximum flash duration mode (see Table 9). In one-shot mode, the flash function is initiated on the rising edge of LED\_EN (or  $I^2C$  bit) and terminated based on the programmed value of the safety timer (see Figure 1). In the maximum flash timer mode, flash function remains enabled as long as LED\_EN (or  $I^2C$  bit) is high, unless the preprogrammed safety timer times out (see Figure 2).

Once the flash mode is disabled, by either LED\_EN, I<sup>2</sup>C, or flash safety timer, the flash has to be off for a minimum time (flash safety timer reset inhibit period), before it can be reinitiated (see Figure 3). This prevents spurious events from re-enabling the flash mode.

#### **Indicator Current Regulator (INDLED)**

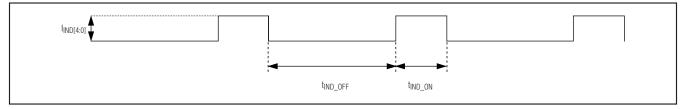

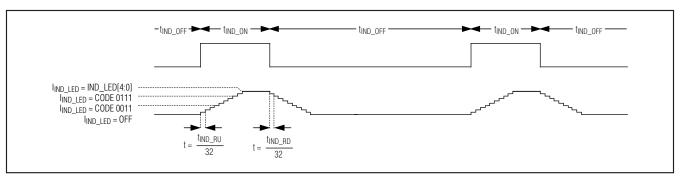

A low-dropout linear current regulator from INDLED to FGND sinks current from the cathode terminal of the indicator LED. The INDLED current is regulated to I<sup>2</sup>C programmable levels up to 16mA. Programmable control is provided for ramp-up (OFF to ON) and ramp-down (ON to OFF) times, as well as blink rate and duty cycle. The user can choose to enable or disable the ramp time and blink rate features. See Tables 6, 7, and 8 for more information.

#### INDLED Blink Function

INDLED current regulator is able to generate a blink function. The OFF and ON time for INDLED are set using the I<sup>2</sup>C interface. See Figure 4.

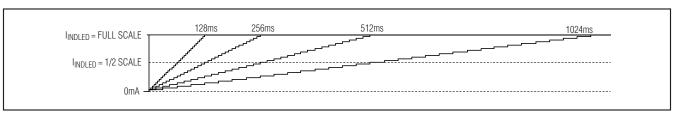

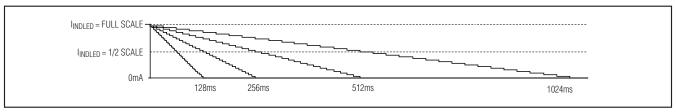

#### INDLED Ramp Function

The INDLED current regulator output provides ramp-up/ down for smooth transition between different brightness settings. The ramp-up/down times are controlled by the

Figure 1. One-Shot Flash-Timer Mode

Figure 2. Maximum Flash-Timer Mode

Figure 3. Flash Safety Timer Reset Inhibit Period

Figure 4. Blink Function Timing

IND\_RU and IND\_RD control bits, and the ramp function is enabled/disabled by the IND\_RP\_EN bit. The current regulator increases/decreases the current onestep every tramp/32 until 0mA or IND[4:0] current is reached. See Figures 5 and 6.

### Combining BLINK Timer and Ramp Function

When using the ramp function for INDLED together with the blink timer, keep the ramp-up timer shorter than the ON blink timer and the ramp-down timer shorter than the OFF timer. Failing to comply with this results in the

Figure 5. Ramp-Up Behavior

Figure 6. Ramp-Down Behavior

Figure 7. Combining RAMP Function and Blink Timer

programmed current not being reached during the ON time, or the INDLED current not returning to 0mA during the OFF time. See Figure 7.

$$\begin{split} t_{\text{IND\_ON}} &\geq \frac{t_{\text{IND\_RU}}}{32} (\text{IND\_LED} + 1) \\ t_{\text{IND\_OFF}} &\geq \frac{t_{\text{IND\_RD}}}{32} (\text{IND\_LED} + 1) \end{split}$$

where IND\_LED is the code from 0 to 31 specified in the IND\_LED[4:0].

#### LED Enable Input (LED\_EN)

The LED\_EN logic input can enable/disable the FLED1, FLED2, and INDLED current regulators. It can be programmed to control movie mode, flash mode, and indicator mode by using the IND\_EN, MOVIE\_EN, and FLASH\_EN bits, respectively. See Table 8 for more information.

If FLED1/FLED2 is enabled for both movie and flash modes at the same time, flash mode has priority. Once the safety timer expires, the current regulator then returns to the movie mode.

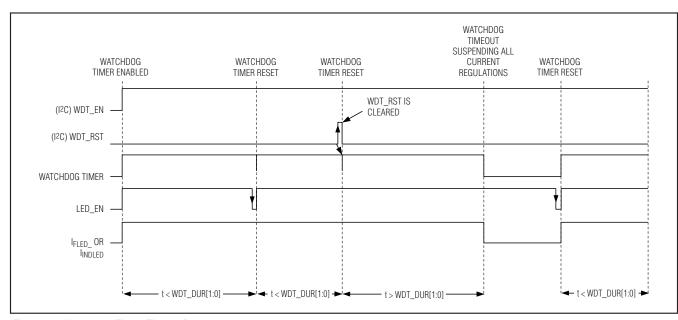

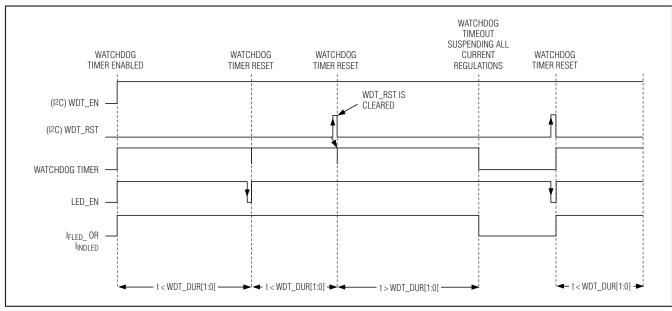

### **Watchdog Timer**

The MAX8834Y/MAX8834Z include a watchdog timer function that can be programmed using the I<sup>2</sup>C interface from 4 seconds to 16 seconds with a 4-second step. If the watchdog timer expires, the MAX8834Y/MAX8834Z interpret it as an indication that the system is no longer responding and enters safe mode. In safe mode, the MAX8834Y/MAX8834Z disable all current regulators and the step-up DC-DC converter to prevent potential damage to the system. The I<sup>2</sup>C setting for the respective registers does not change, therefore, resetting the watchdog timer reverts the MAX8834Y/MAX8834Z back to the state present before entering safe mode.

14 \_\_\_\_\_\_ *NIXIN*

Figure 8. Watchdog Timer Timing Diagram 1

Figure 9. Watchdog Timer Timing Diagram 2

Setting the WDT\_EN bit to 1 in the TMR\_DUR register (Table 9) enables the watchdog timer. Resetting the watchdog timer is achieved by the rising or falling edge

of LED\_EN or by setting bit 0 in the WDT\_RST register (Table 14). See Figures 8 and 9 for two examples of watchdog timer timing diagrams.

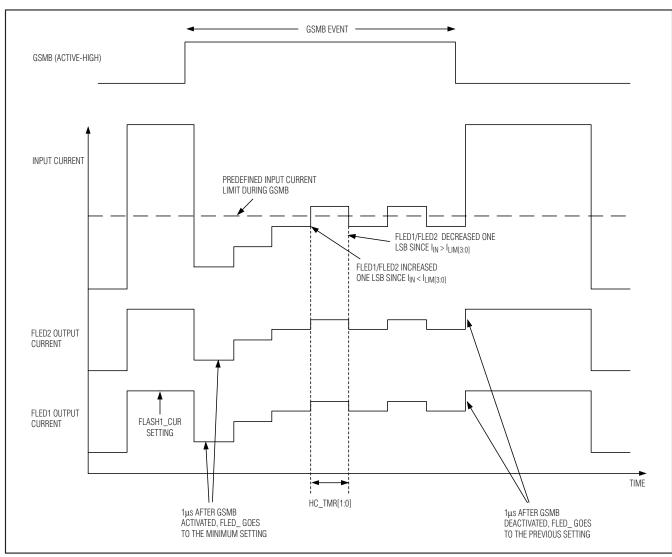

Figure 10. Input Current Limit During GSMB Event

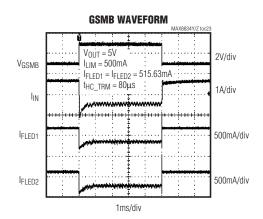

### **GSM Blank Function (GSMB)**

The GSMB input is provided to allow the flash current to be momentarily reduced during a GSM transmit to reduce the peak current drawn from the battery. The input current limit ensures that the maximum possible output current is always provided, regardless of the input voltage and the LED forward voltages.

When a GSMB event is triggered, the FLED1 and FLED2 current regulators go to the lowest setting to ensure the current drawn from the battery is quickly reduced to a safe level. The MAX8834Y/MAX8834Z

then start increasing the FLED1 and FLED2 current by one LSB steps, at a time interval set by HC\_TMR[1:0] (see Table 11). The increasing continues until either the predefined FLED1/FLED2 current setting is reached or the input current exceeds the maximum predefined input current limit during a GSMB event. When the input current exceeds the predefined input current limit, the FLED1/FLED2 current is reduced by one LSB. The MAX8834Y/MAX8834Z continue to adjust the FLED1 and FLED2 up and down depending on the input current limit as long as the GSMB event is present. See Figure 10 for more detailed information.

To use this feature, connect the logic signal used to enable the PA, or equivalent, to the GSMB input. Assertion of this signal does not change the current status of the flash safety timer or the flash current values stored in the I<sup>2</sup>C registers. Once the signal is deasserted, the current regulators change back to their previously programmed values. Polarity of this signal is controlled through bit 6 in the GSMB\_CUR register (Table 11). The default is active-high.

### Finger-Burn Protection (NTC)

An NTC input is provided for the (optional) finger-burn protection feature. To use this feature, connect a  $100k\Omega$  NTC with B = 4550 between NTC and AGND. NTC sources  $20\mu\text{A}$  current and the voltage established by this current and the NTC resistance is compared internally to a voltage threshold in the range of 200mV to 550mV, programmed through bits [2:0] of the NTC Control register (see Table 10).

If the voltage on the NTC pin falls below the programmed threshold during a flash event, the flash cycle is immediately terminated, and an indication is latched through bit 3 in the STATUS1 register (see Table 15).

To disable this function, clear bit 3 (enable bit) in the NTC Control register.

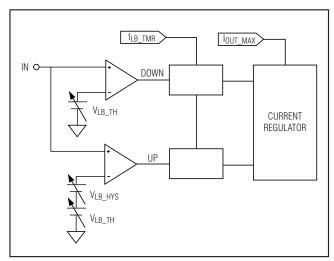

#### **MAXFLASH Function**

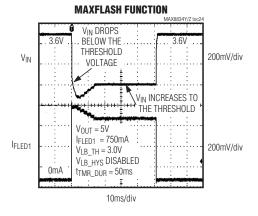

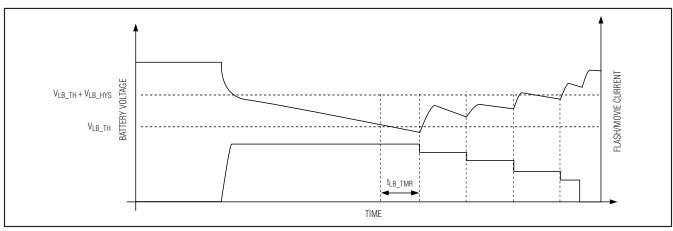

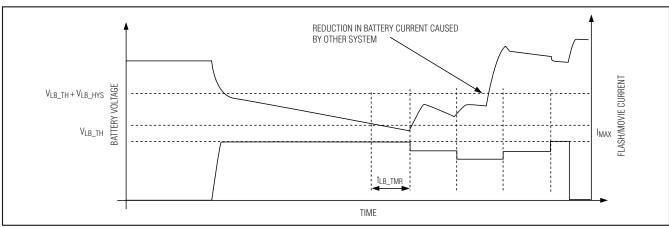

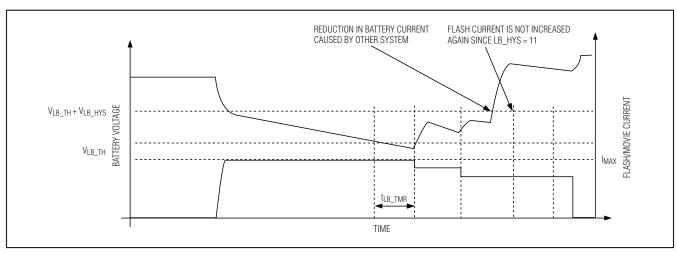

During high load currents, the battery voltage momentarily drops due to its internal ESR, together with the serial impedance from the battery to the load. For equipment requiring a minimum voltage for stable operation, the battery ESR needs to be calculated to estimate the maximum battery current that maintains the battery voltage above the critical threshold. Due to the complicated measurement of the battery ESR, the MAX8834Y/MAX8834Z feature the MAXFLASH function to prevent the battery voltage from dropping below the threshold voltage. See Figure 11 for details.

The MAX8834Y/MAX8834Z input voltage is monitored during a FLASH/MOVIE event. If the input voltage drops below a predefined threshold (VLB\_TH), it indicates that the FLASH/MOVIE event is drawing more current than the battery can support. As a result, the FLED1/FLED2 current regulators start decreasing their output currents by one step. Therefore, the input current is reduced and the input voltage starts to rise due to the internal battery ESR. The input voltage is then sampled again after tLB TMR and compared to VLB TH

plus a predefined hysteresis (V<sub>LB\_HYS</sub>). If it is still below V<sub>LB\_TH</sub> + V<sub>LB\_HYS</sub>, the FLED1/FLED2 current regulators reduce their output current again to ensure that minimum input voltage is available for the system. If the input voltage is above V<sub>LB\_TH</sub> + V<sub>LB\_HYS</sub>, the current regulator increases the output current by one step (if it is less than the user-defined output current). To disable the hysteresis, set LB\_HYS[1:0] to 11. In this case, after the FLED1/FLED2 current is reduced, it stays at the current setting. Figures 12, 13, and 14 show examples of MAXFLASH function operation. See Tables 12 and 13 for control register details.

The MAXFLASH function continues for the entire duration of the FLASH/MOVIE event to ensure that the FLASH/MOVIE output current is always maximized for the specific operating conditions.

### **Undervoltage Lockout**

The MAX8834Y/MAX8834Z contain undervoltage lock-out (UVLO) circuitry that disables the IC until  $V_{IN}$  is greater than 2.3V (typ). Once  $V_{IN}$  rises above 2.3V (typ), the UVLO circuitry does not disable the IC until  $V_{IN}$  falls below the UVLO threshold minus the hysteresis voltage. The MAX8834Y/MAX8834Z also contain a  $V_{DD}$  UVLO circuitry that monitors the  $V_{DD}$  voltage. When the  $V_{DD}$  voltage falls below 1.4V (typ), the contents of all the logic registers are reset to their default states. The logic registers are only reset in a  $V_{DD}$  UVLO condition and not an IN UVLO condition.

Figure 11. Block Diagram of MAXFLASH Function

Figure 12. Example 1 of MAXFLASH Function Operation

Figure 13. Example 2 of MAXFLASH Function Operation

Figure 14. Example 3 of MAXFLASH Function Operation with Hysteresis Disabled

18 \_\_\_\_\_\_ *NIXIN*

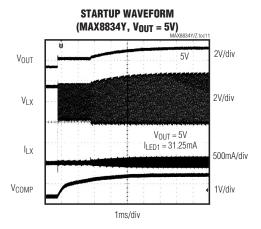

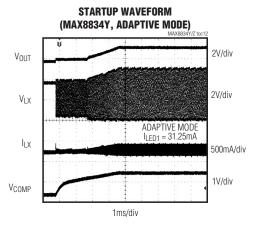

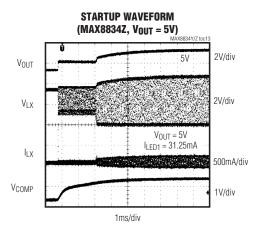

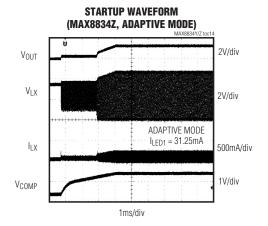

#### Soft-Start

The step-up converter implements a soft-start to control inrush current when it turns on. It soft-starts by charging CCOMP with a 100µA current source. During this time, the internal MOSFET is switching at the minimum duty cycle. Once VCOMP rises above 1V, the duty cycle increases until the output voltage reaches the desired regulation level. COMP is pulled to AGND with a 180Ω (typ) internal resistor during IN, UVLO, dropout mode, or shutdown. See the *Typical Operating Characteristics* for an example of soft-start operation. Soft-start is reinitiated after UVLO or if the step-up converter is reenabled after shutdown or dropout mode.

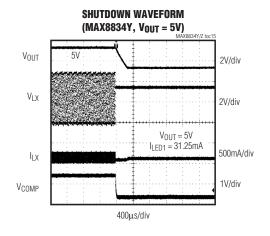

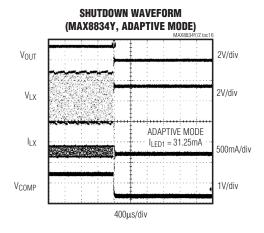

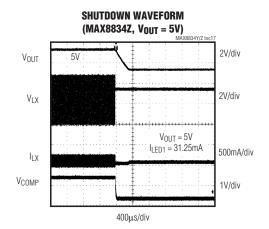

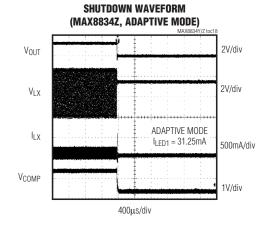

### Shutdown and Standby

The MAX8834Y/MAX8834Z are in shutdown when either  $V_{IN}$  or  $V_{DD}$  are in UVLO. In shutdown, supply current is reduced to 0.1µA (typ). When  $V_{IN}$  is above its UVLO threshold, but  $V_{DD}$  is below its UVLO threshold, the IC disables its internal reference, keeps all registers reset, turns the step-up converter off, and turns the FLED1/FLED2 current regulators off (high impedance). Once a logic-level voltage is supplied to  $V_{DD}$ , the IC enters standby condition and is ready to accept I<sup>2</sup>C commands. The internal MOSFET, synchronous rectifier, and FLED1/FLED2 are also high impedance in standby.

Typical shutdown timing characteristics are shown in the *Typical Operating Characteristics*.

### **Parallel Connection of Current Regulators**

The FLED1/FLED2 current regulators can be connected in parallel as long as the system software properly sets the current levels for each regulator. Unused current regulators may be connected to ground. The FLED1/

FLED2 regulators must be disabled through I<sup>2</sup>C to avoid a fault detection from an open or short.

#### **Open/Short Detection**

The MAX8834Y/MAX8834Z monitor the FLED1, FLED2, and INDLED voltage to detect any open or short LEDs. A short fault is detected when the voltage rises above Vout - 1V (typ), and an open fault is detected when the voltage falls below 100mV. The fault detection circuitry is only activated when the corresponding current regulator is enabled and provides a continuous monitor of the current regulator condition. Once a fault is detected, the corresponding current regulator is disabled and the status is latched into the corresponding fault register bit (see Table 15). This allows the processor to determine the MAX8834Y/MAX8834Z operating condition.

#### **Thermal Shutdown**

Thermal shutdown limits total power dissipation in the MAX8834Y/MAX8834Z. When the junction temperature exceeds +160°C (typ), the IC turns off, allowing itself to cool. The IC turns on and begins soft-start after the junction temperature cools by 20°C. This results in a pulsed output during continuous thermal overload conditions.

#### I<sup>2</sup>C Serial Interface

An I<sup>2</sup>C-compatible, 2-wire serial interface controls the step-up converter output voltage, flash, movie, and indicator current settings, flash duration, and other parameters. The serial bus consists of a bidirectional serial-data line (SDA) and a serial-clock input (SCL). The MAX8834Y/MAX8834Z are slave-only devices, relying upon a master to generate a clock signal. The master initiates data transfer to and from the MAX8834Y/

Figure 15. 2-Wire Serial Interface Timing Detail

Figure 16. Bit Transfer

MAX8834Z and generates SCL to synchronize the data transfer (Figure 15).

I<sup>2</sup>C is an open-drain bus. Both SDA and SCL are bidirectional lines, connected to a positive supply voltage through a pullup resistor. They both have Schmitt triggers and filter circuits to suppress noise spikes on the bus to assure proper device operation.

A bus master initiates communication with the MAX8834Y/MAX8834Z as a slave device by issuing a START (S) condition followed by the MAX8834Y/MAX8834Z address. The MAX8834Y/MAX8834Z address byte consists of 7 address bits and a read/write bit (R/W). After receiving the proper address, the MAX8834Y/MAX8834Z issue an acknowledge bit by pulling SDA low during the ninth clock cycle.

#### Slave Address

The MAX8834Y/MAX8834Z act as a slave transmitter/receiver. Its slave address is 0x94 for write operations and 0x95 for read operations.

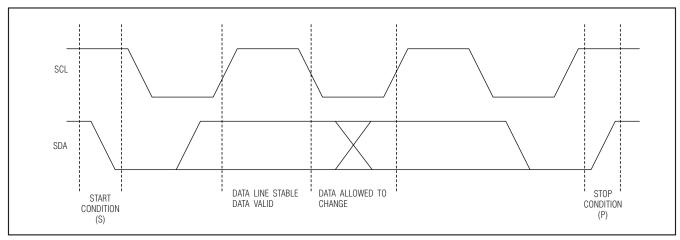

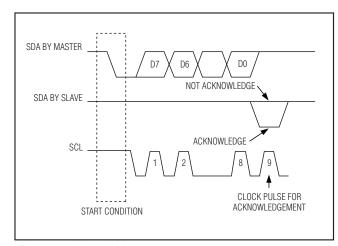

#### Bit Transfer

Each data bit, from the most significant bit to the least significant bit, is transferred one by one during each clock cycle. During data transfer, the SDA signal is allowed to change only during the low period of the SCL clock and it must remain stable during the high period of the SCL clock (Figure 16).

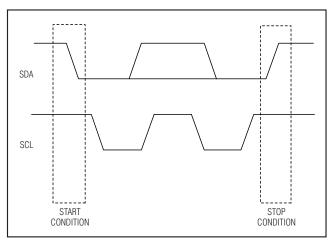

#### START and STOP Conditions

Both SCL and SDA remain high when the bus is not busy. The master signals the beginning of a transmission with a START (S) condition by transitioning SDA from high to low while SCL is high. When the master has finished communicating with the MAX8834Y/MAX8834Z, it issues a STOP (P) condition by transitioning SDA from low to high while SCL is high. The bus is then free for another transmission (Figure 17). Both START and STOP conditions are generated by the bus master.

#### Acknowledge

The acknowledge bit is used by the recipient to handshake the receipt of each byte of data (Figure 18). After data transfer, the master generates the acknowledge clock pulse and the recipient pulls down the SDA line during this acknowledge clock pulse so the SDA line stays low during the high duration of the clock pulse. When the master transmits the data to the MAX8834Y/MAX8834Z, it releases the SDA line and the MAX8834Y/MAX8834Z take control of the SDA line and generate the acknowledge bit. When SDA remains high during this 9th clock pulse, this is defined as the not acknowledge signal. The master can then generate either a STOP condition to abort the transfer, or a repeated START condition to start a new transfer.

Figure 17. START and STOP Conditions

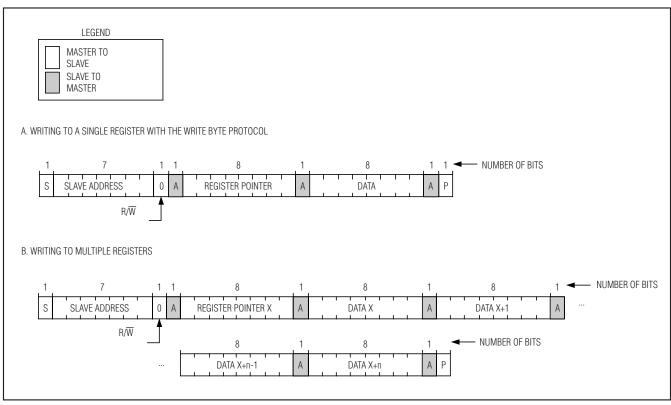

### Write Operations

The MAX8834Y/MAX8834Z recognize the write byte protocol as defined in the SMBus™ specification and shown in section A of Figure 19. The write byte protocol allows the I²C master device to send 1 byte of data to the slave device. The write-byte protocol requires a register pointer address for the subsequent write. The MAX8834Y/MAX8834Z acknowledge any register pointer even though only a subset of those registers actually exists in the device. The write byte protocol is as follows:

- 1) The master sends a start command.

- 2) The master sends the 7-bit slave address followed by a write bit.

- 3) The addressed slave asserts an acknowledge by pulling SDA low.

- 4) The master sends an 8-bit register pointer.

- 5) The slave acknowledges the register pointer.

- 6) The master sends a data byte.

- 7) The slave updates with the new data.

- 8) The slave acknowledges the data byte.

- 9) The master sends a STOP (P) condition.

In addition to the write-byte protocol, the MAX8834Y/ MAX8834Z can write to multiple registers as shown in section B of Figure 19. This protocol allows the I<sup>2</sup>C master device to address the slave only once and then send data to a sequential block of registers starting at the specified register pointer.

Figure 18. Acknowledge

Use the following procedure to write to a sequential block of registers:

- 1) The master sends a start command.

- The master sends the 7-bit slave address followed by a write bit.

- The addressed slave asserts an acknowledge by pulling SDA low.

- 4) The master sends the 8-bit register pointer of the first register to write.

- 5) The slave acknowledges the register pointer.

- 6) The master sends a data byte.

- 7) The slave updates with the new data.

- 8) The slave acknowledges the data byte.

- 9) Steps 6 to 8 are repeated for as many registers in the block, with the register pointer automatically incremented each time.

- 10) The master sends a STOP condition.

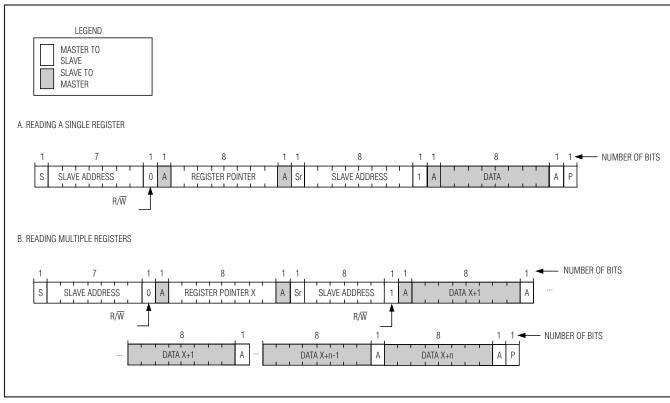

#### Read Operations

The method for reading a single register (byte) is shown in section A of Figure 20. To read a single register:

- 1) The master sends a start command.

- 2) The master sends the 7-bit slave address followed by a write bit.

- 3) The addressed slave asserts an acknowledge by pulling SDA low.

- 4) The master sends an 8-bit register pointer.

SMBus is a trademark of Intel Corp.

Figure 19. Writing to the MAX8834Y/MAX8834Z

- 5) The slave acknowledges the register pointer.

- 6) The master sends a REPEATED START (Sr) condition.

- 7) The master sends the 7-bit slave address followed by a read bit.

- 8) The slave asserts an acknowledge by pulling SDA low

- 9) The slave sends the 8-bit data (contents of the register).

- The master asserts an acknowledge by pulling SDA low.

- 11) The master sends a STOP (P) condition.

In addition, the MAX8834Y/MAX8834Z can read a block of multiple sequential registers as shown in section B of Figure 20. Use the following procedure to read a sequential block of registers:

- 1) The master sends a start command.

- 2) The master sends the 7-bit slave address followed by a write bit.

- 3) The addressed slave asserts an acknowledge by pulling SDA low.

- 4) The master sends an 8-bit register pointer of the first register in the block.

- 5) The slave acknowledges the register pointer.

- 6) The master sends a REPEATED START condition.

- 7) The master sends the 7-bit slave address followed by a read bit.

- The slave asserts an acknowledge by pulling SDA low.

- 9) The slave sends the 8-bit data (contents of the register).

- 10) The master asserts an acknowledge by pulling SDA low.

- 11) Steps 9 and 10 are repeated for as many registers in the block, with the register pointer automatically incremented each time.

- 12) The master sends a STOP condition.

Figure 20. Reading from the MAX8834Y/MAX8834Z

### **Table 1. Register Map**

| NAME                    | TABLE    | REGISTER<br>ADDRESS (hex) | TYPE | DESCRIPTION                                                                                     |

|-------------------------|----------|---------------------------|------|-------------------------------------------------------------------------------------------------|

| BOOST_CNTL              | Table 2  | 00                        | R/W  | Step-up converter control                                                                       |

| FLASH1_CUR              | Table 3  | 01                        | R/W  | FLED1 flash current control                                                                     |

| FLASH2_CUR              | Table 4  | 02                        | R/W  | FLED2 flash current control                                                                     |

| MOVIE_CUR               | Table 5  | 03                        | R/W  | FLED1 and FLED2 movie current control                                                           |

| Reserved for future use | _        | 04                        | R/W  | Reserved for future use                                                                         |

| IND_CUR                 | Table 6  | 05                        | R/W  | Indicator LED current control                                                                   |

| Reserved for future use | _        | 06                        | R/W  | Reserved for future use                                                                         |

| IND_CNTL                | Table 7  | 07                        | R/W  | Indicator LED ramp and blink control                                                            |

| Reserved for future use | _        | 08                        | R/W  | Reserved for future use                                                                         |

| LED_CNTL                | Table 8  | 09                        | R/W  | FLED1, FLED2, and INDLED on/off and mode control, and definition of LED_EN logic input function |

| TMR_DUR                 | Table 9  | 0A                        | R/W  | Watchdog timer and flash safety timer control                                                   |

| NTC_CNTL                | Table 10 | 0B                        | R/W  | NTC function control                                                                            |

| GSMB_CUR                | Table 11 | 0C                        | R/W  | FLED1 and FLED2 current control during GSM transmit                                             |

| MAXFLASH1               | Table 12 | 0D                        | R/W  | MAXFLASH function register 1                                                                    |

| MAXFLASH2               | Table 13 | 0E                        | R/W  | MAXFLASH function register 2                                                                    |

| WDT_RST                 | Table 14 | 16                        | R/W  | Watchdog timer reset                                                                            |

| STATUS1                 | Table 15 | 17                        | R    | Status register                                                                                 |

| STATUS2                 | Table 16 | 18                        | R    | Status register                                                                                 |

| Reserved for future use | _        | 19                        | R/W  | Reserved for future use                                                                         |

| CHIP_ID1                | Table 17 | 1A                        | R    | Die type information                                                                            |

| CHIP_ID2                | Table 18 | 1B                        | R    | Die type and mask revision information                                                          |

4 \_\_\_\_\_\_*NIXIN*

### Table 2. BOOST\_CNTL

This register contains step-up converter control values.

| REGISTER NAME    | BOOST_CNTL |

|------------------|------------|

| Address          | 0x00       |

| Reset Value      | 0x00       |

| Type             | Read/write |

| Special Features | _          |

| BIT      | NAME            | DESCRIPTION                                                                                                                                                                          | DEFAULT VALUE |

|----------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| B7 (MSB) | _               | Reserved for future use                                                                                                                                                              | 0             |

| B6       | BOOST_EN        | 0 = Step-up converter off<br>1 = Step-up converter on                                                                                                                                | 0             |

| B5       |                 | 00 = Step-up voltage set adaptively 01 = Step-up voltage set programmatically according to                                                                                           |               |

| B4       | BOOST_MODE      | BOOST_CNTL[3:0]  10 = Step-up converter runs in dropout  11 = Step-up converter automatically changes between adaptive regulation and dropout mode depending on operating conditions | 00            |

| В3       |                 | 0000 = 3.7V<br>0001 = 3.8V<br>0010 = 3.9V<br>0011 = 4.0V                                                                                                                             |               |

| B2       |                 | 0100 = 4.1V<br>0101 = 4.2V<br>0110 = 4.3V<br>0111 = 4.4V                                                                                                                             |               |

| B1       | BOOST_CNTL[3:0] | 1000 = 4.5V<br>1001 = 4.6V<br>1010 = 4.7V<br>1011 = 4.8V                                                                                                                             | 0000          |

| B0 (LSB) |                 | 1100 = 4.9V<br>1101 = 5.0V<br>1110 = 5.1V<br>1111 = 5.2V                                                                                                                             |               |

### Table 3. FLASH1\_CUR

This register contains FLED1 flash current control values.

| REGISTER NAME    | FLASH1_CUR |

|------------------|------------|

| Address          | 0x01       |

| Reset Value      | 0x00       |

| Туре             | Read/write |

| Special Features | _          |

| BIT      | NAME        | DESCRIPTION                                                                                                                              | DEFAULT VALUE |

|----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| B7 (MSB) |             | FLED1 Flash Mode Current Setting<br>00000 = 23.44mA<br>00001 = 46.88mA<br>00010 = 70.32mA<br>00011 = 93.76mA<br>00100 = 117.20mA         |               |

| В6       |             | 00101 = 140.64mA<br>00110 = 164.08mA<br>00111 = 187.52mA<br>01000 = 210.96mA<br>01001 = 234.40mA<br>01010 = 257.84mA<br>01011 = 281.28mA |               |

| B5       | FLASH1[4:0] | 01100 = 304.72mA<br>01101 = 328.16mA<br>01110 = 351.60mA<br>01111 = 375.04mA<br>10000 = 398.48mA<br>10001 = 421.92mA<br>10010 = 445.36mA | 00000         |

| B4       |             | 10011 = 468.80mA<br>10100 = 492.24mA<br>10101 = 515.68mA<br>10110 = 539.12mA<br>10111 = 562.56mA<br>11000 = 586.00mA<br>11001 = 609.44mA |               |

| В3       |             | 11001 = 609.44MA<br>11010 = 632.88mA<br>11011 = 656.32mA<br>11100 = 679.76mA<br>11101 = 703.20mA<br>11110 = 726.56mA<br>11111 = 750.00mA |               |

| B2       | _           | Reserved for future use                                                                                                                  | _             |

| B1       | _           | Reserved for future use                                                                                                                  | _             |

| B0 (LSB) | _           | Reserved for future use                                                                                                                  | _             |

### Table 4. FLASH2\_CUR

This register contains FLED2 flash current control values.

| REGISTER NAME    | FLASH2_CUR |

|------------------|------------|

| Address          | 0x02       |

| Reset Value      | 0x00       |

| Туре             | Read/write |

| Special Features | _          |

| BIT      | NAME        | DESCRIPTION                           | DEFAULT VALUE |

|----------|-------------|---------------------------------------|---------------|

|          |             | FLED2 Flash Mode Current Setting      |               |

|          |             | 00000 = 23.44mA                       |               |

| D7 (MCD) |             | 00001 = 46.88mA                       |               |

| B7 (MSB) |             | 00010 = 70.32mA                       |               |

|          |             | 00011 = 93.76mA                       |               |

|          |             | 00100 = 117.20mA                      |               |

|          | 1           | 00101 = 140.64 mA                     |               |

|          |             | 00110 = 164.08mA                      |               |

|          |             | 00111 = 187.52mA                      |               |

| B6       |             | 01000 = 210.96mA                      |               |

|          |             | 01001 = 234.40mA                      |               |

|          |             | 01010 = 257.84mA                      |               |

|          | -           | 01011 = 281.28mA                      |               |

|          |             | 01100 = 304.72mA                      |               |

|          |             | 01101 = 328.16mA                      |               |

| B5       | =           | 01110 = 351.60mA                      |               |

|          | FLASH2[4:0] | 01111 = 375.04mA                      | 00000         |

|          |             | 10000 = 398.48mA                      |               |

|          |             | 10001 = 421.92mA                      |               |

|          |             | 10010 = 445.36mA                      |               |

|          |             | 10011 = 468.80mA                      |               |

| D.4      |             | 10100 = 492.24mA                      |               |

| B4       |             | 10101 = 515.68mA                      |               |

|          |             | 10110 = 539.12mA                      |               |

|          |             | 10111 = 562.56mA                      |               |

|          | 1           | 11000 = 586.00mA<br>11001 = 609.44mA  |               |

|          |             | 11010 = 609.44MA<br>11010 = 632.88mA  |               |

|          |             | 11010 = 632.00ffA<br>11011 = 656.32mA |               |

| B3       |             | 11100 = 679.76mA                      |               |

|          |             | 11101 = 703.20mA                      |               |

|          |             | 11110 = 703.20mA<br>11110 = 726.56mA  |               |

|          |             | 11111 = 750.00mA                      |               |

| B2       | _           | Reserved for future use               | _             |

| B1       | _           | Reserved for future use               | _             |

| B0 (LSB) | _           | Reserved for future use               | _             |

| טט (בטט) |             | The served for future use             | _             |

### Table 5. MOVIE\_CUR

This register contains FLED1 and FLED2 movie current control values.