H5RS5223CFR

# 512Mbit (16Mx32) GDDR3 SDRAM H5RS5223CFR

# **Revision History**

| Revision | Page                   | History                                                                                                                                                                        | Date      | Remark      |

|----------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------|

| 0.1      |                        | Defined target spec.                                                                                                                                                           | Oct. 2007 | Preliminary |

| 0.2      |                        | Changed tCK_max to 2ns at (-N0) & PKG drawing value                                                                                                                            | Oct. 2007 | Preliminary |

| 0.3      |                        | <ol> <li>Revised the slew rate from 6V/ns to 3V/ns on page 54.</li> <li>Inserted the code 'C' in Part number, that means 'normal power and commercial temperature'.</li> </ol> | Nov. 2007 | Preliminary |

| 0.4      |                        | Inserted 1.2Ghz speed bin                                                                                                                                                      | Dec. 2007 | Preliminary |

| 1.0      |                        | Added IDD Values                                                                                                                                                               | Jan. 2008 |             |

| 1.1      | 47                     | Changed IDDO/IDD1/IDD5A Values                                                                                                                                                 | Jan. 2008 |             |

| 1.2      | 43                     | Inserted the thermal characteristics table (Table 12)                                                                                                                          | Mar. 2008 |             |

| 1.3      | 44                     | Inserted the note for IO reference voltage (V <sub>REF</sub> )                                                                                                                 | May. 2008 |             |

| 1.4      | 44                     | Inserted the note (VDD/VDDQ)                                                                                                                                                   | Jun. 2008 |             |

| 1.5      | 3<br>48<br>51-52<br>55 | Inserted 1.3Ghz speed bin (-N3C)     Inserted IDD Values for 1.3Ghz     Inserted AC Parameter Values for 1.3Ghz     Inserted Eletrical Characteristics Usage Values for 1.3Ghz | Jul. 2008 |             |

#### DESCRIPTION

$The \ Hynix \ H5RS5223 \ is \ a \ high-speed \ CMOS, \ dynamic \ random-access \ memory \ containing \ 536,870,912 \ bits.$

The Hynix H5RS5223 is internally configured as a eight-bank DRAM.

The Hynix H5RS5223 uses a double data rate architecture to achieve high-speed operation. The double date rate architecture is essentially a 4n-prefetch architecture, with an interface designed to transfer two data words per clock cycle at the I/O pins. A single read or write access for the Hynix H5RS5223 consists of a 4n-bit wide, every two-clock-cycles data transfer at the internal DRAM core and two corresponding n-bit wide, one-half-clock-cycle data transfers at the I/O pins. Read and write accesses to the Hynix H5RS5223 is burst oriented; accesses start at a selected locations and continue for a programmed number of locations in a programmed sequence. Accesses begin with the registration of an ACTIVE command, which is then followed by a READ of WRITE command. The address bits registered coincident with the ACTIVE command are used to select the bank and row to be accessed (BAO,BA1, BA2 select the bank; A0-A11 select the row). The address bits registered coincident with the READ or WRITE command are used to select the starting column location for the burst access. Prior to normal operation, the Hynix H5RS5223 must be initialized.

#### **FEATURES**

- 2.05V/ 1.8V/ 1.5V power supply supports

(For more detail, Please see the Table 12 on page 43)

- Single ended READ Strobe (RDQS) per byte

- Single ended WRITE Strobe (WDQS) per byte

- Internal, pipelined double-data-rate (DDR) architecture;

two data accesses per clock cycle

- On Die Termination

- · Output Driver Strength adjustment by EMRS

- · Calibrated output driver

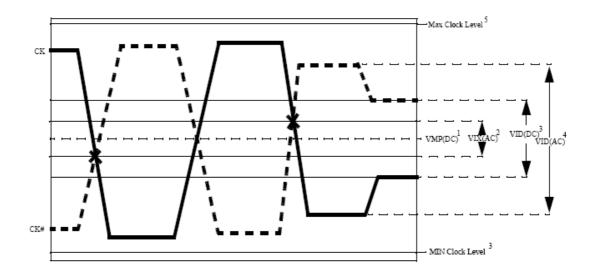

- Differential clock inputs (CK and CK#)

- · Commands entered on each positive CK edge

- RDQS edge-aligned with data for READ; with WDQS center-aligned with data for WRITE

- 8 internal banks for concurrent operation

- CAS Latency: 4~11 (clock)

- · Data mask (DM) for masking WRITE data

- 4n prefetch

- Programmable burst lengths: 4, 8

- 32ms, 8K-cycle auto refresh

- Auto precharge option

- · Auto Refresh and Self Refresh Modes

- 1.8V Pseudo Open Drain I/O

- · Concurrent Auto Precharge support

- tRAS lockout support, Active Termination support

- Programmable Write latency(1, 2, 3, 4, 5, 6)

- Boundary Scan Function with SEN pin

- Mirror Function with MF pin

#### ORDERING INFORMATION

| Part No.        | Power Supply    | Clock Frequency | Max Data Rate | Interface | Package      |

|-----------------|-----------------|-----------------|---------------|-----------|--------------|

| H5RS5223CFR-N3C |                 | 1300MHz         | 2600Mbps/pin  |           |              |

| H5RS5223CFR-N2C | VDD/VDDQ=2.05V  | 1200MHz         | 2400Mbps/pin  |           |              |

| H5RS5223CFR-N0C |                 | 1000MHz         | 2000Mbps/pin  | POD 18    |              |

| H5RS5223CFR-11C |                 | 900MHz          | 1800Mbps/pin  | POD_16    | 10mmx14mm    |

| H5RS5223CFR-14C | VDD/VDDQ=1.8V   | 700MHz          | 1400Mbps/pin  |           | 136Ball FBGA |

| H5RS5223CFR-20C |                 | 500MHz          | 1000Mbps/pin  |           |              |

| H5RS5223CFR-14L | VDD/VDDO=1.5V   | 700MHz          | 1400Mbps/pin  | DOD 1E    |              |

| H5RS5223CFR-18C | 7 VUU/VUUQ=1.5V | 550MHz          | 1100Mbps/pin  | POD_15    |              |

Note) Above Hynix P/N's and their homogeneous Subcomponents are RoHS (& Lead free) compliant

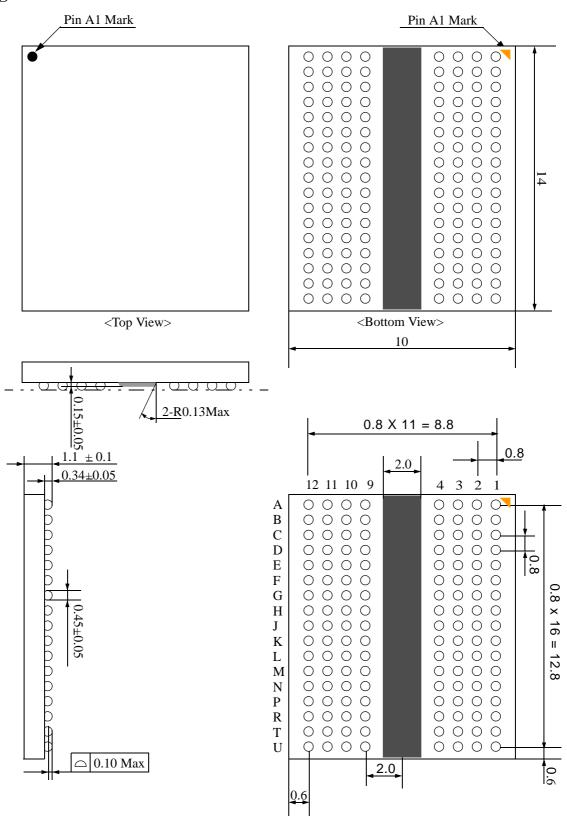

# **BALLOUT CONFIGURATION**

|   | 1 2  |            | 3     | 4    |  |

|---|------|------------|-------|------|--|

| Α | VDDQ | VDD        | VSS   | ZQ   |  |

| В | vssq | DQ0        | DQ1   | vssq |  |

| С | VDDQ | DQ2        | DQ3   | VDDQ |  |

| D | vssq | WDQS0      | RDQS0 | vssq |  |

| Ε | VDDQ | DQ4        | DM0   | VDDQ |  |

| F | VDD  | DQ6        | DQ5   | CAS# |  |

| G | vss  | VSSQ       | DQ7   | BA0  |  |

| Н | VREF | <b>A</b> 1 | RAS#  | CKE  |  |

| J | vss  | NC         | RFU   | VDDQ |  |

| K | VDD  | A10        | A2    | Α0   |  |

| L | vss  | VSSQ       | DQ25  | A11  |  |

| M | VDD  | DQ24       | DQ27  | А3   |  |

| N | VDDQ | DQ26       | DM3   | VDDQ |  |

| Р | vssq | WDQS3      | RDQS3 | vssq |  |

| R | VDDQ | DQ28       | DQ29  | VDDQ |  |

| Т | vssq | DQ30       | DQ31  | vssq |  |

| U | VDDQ | VDD        | vss   | SEN  |  |

| 5 | 6 | 7 | 8 | 9                  | 10                     | 11                         | 12                    |

|---|---|---|---|--------------------|------------------------|----------------------------|-----------------------|

|   |   |   |   | MF                 | vss                    | VDD                        | VDDQ                  |

|   |   |   |   | VSSQ               | DQ9                    | DQ8                        | VSSQ                  |

|   |   |   |   | VDDQ               | DQ11                   | DQ10                       | VDDQ                  |

|   |   |   |   | VSSQ               | RDQS1                  | WDQS1                      | VSSQ                  |

|   |   |   |   | VDDQ               | DM1                    | DQ12                       | VDDQ                  |

|   |   |   |   | CS#                | DQ13                   | DQ14                       | VDD                   |

|   |   |   |   | BA1                | DQ15                   | VSSQ                       | vss                   |

|   |   |   |   | WE#                | BA2                    | A5                         | VREF                  |

|   |   |   |   |                    |                        |                            |                       |

|   |   |   |   | VDDQ               | CK#                    | CK                         | vss                   |

|   |   |   |   | VDDQ<br>A4         | CK#<br>A6              | CK<br>A8/AP                | VSS<br>VDD            |

|   |   |   |   |                    |                        |                            |                       |

|   |   |   |   | A4                 | A6                     | A8/AP                      | VDD                   |

|   |   |   |   | A4<br>A7           | A6<br>DQ17             | A8/AP<br>VSSQ              | VDD<br>VSS            |

|   |   |   |   | A4<br>A7<br>A9     | A6 DQ17 DQ19           | A8/AP VSSQ DQ16            | VDD<br>VSS<br>VDD     |

|   |   |   |   | A4 A7 A9 VDDQ      | A6 DQ17 DQ19 DM2       | A8/AP VSSQ DQ16 DQ18       | VDD VSS VDD VDDQ      |

|   |   |   |   | A4 A7 A9 VDDQ VSSQ | A6 DQ17 DQ19 DM2 RDQS2 | A8/AP VSSQ DQ16 DQ18 WDQS2 | VDD VSS VDD VDDQ VSSQ |

|                | 16M x 32          |

|----------------|-------------------|

| Configuration  | 2M x 32 x 8 banks |

| Refresh Count  | 8 k               |

| Bank Address   | BAO - BA2         |

| Row Address    | A0~A11            |

| Column Address | A0~A7, A9         |

| AP Flag        | A8                |

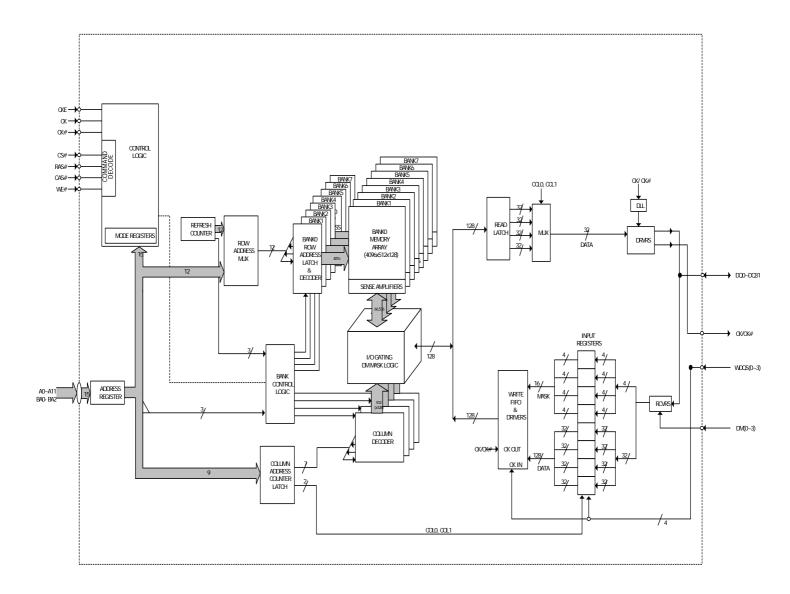

# **FUNCTIONAL BLOCK DIAGRAM**

8Banks x 2Mbit x 32 I/O double Data Rate Synchronous DRAM

# **BALLOUT DESCRIPTIONS**

| FBGA BALLOUT                                                                                                                                                           | SYMBOL          | TYPE   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J10, J11                                                                                                                                                               | CK, CK#         | Input  | Clock: CK and CK# are differential clock inputs. All address and control input signals are sampled on the crossing of the positive edge of CK and negative edge of CK#.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| H4                                                                                                                                                                     | CKE             | Input  | Clock Enable: CKE HIGH activates and CKE LOW deactivates the internal clock, input buffers and output drivers. Taking CKE LOW provides PRECHARGE POWER-DOWN and SELF REFRESH operations(all banks idle), or ACTIVE POWER-DOWN (row ACTIVE in any bank). CKE is synchronous for POWER-DOWN entry and exit, and for SELF REFRESH entry. CKE is asynchronous for SELF REFRESH exit and for disabling the outputs. CKE must be maintained HIGH throughout read and write accesses. Input buffers (excluding CK, CK# and CKE) are disabled during POWER-DOWN. Input buffers (excluding CKE) are disabled during SELF REFRESH. |

| F9                                                                                                                                                                     | CS#             | Input  | Chip Select: CS# enables (registered LOW) and disables (registered HIGH) the command decoder. All commands are masked when CS# is registered HIGH. CS# provides for external bank selection on systems with multiple banks. CS# is considered part of the command code.                                                                                                                                                                                                                                                                                                                                                  |

| H3, F4, H9                                                                                                                                                             | RAS#, CAS#, WE# | Input  | Command Inputs: RAS#, CAS# and WE#(along with CS#) define the command being entered.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| E(3, 10), N(3, 10)                                                                                                                                                     | DM0-DM3         | Input  | Input Data Mask: DM is an input mask signal for write data. Input data is masked when DM is sampled HIGH along with that input data during a WRITE access. DM is sampled on rising and falling edges of WDQS.                                                                                                                                                                                                                                                                                                                                                                                                            |

| G(4, 9), H10                                                                                                                                                           | BA0 - BA2       | Input  | Bank Address Inputs: BAO and BA2 define to which bank an ACTIVE, READ, WRITE or PRECHARGE command is being applied.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| H(2, 11),<br>K(2-4, 9-11),<br>L(4, 9), M(4, 9)                                                                                                                         | A0-A11          | Input  | Address Inputs: Provide the row address for ACTIVE commands, and the column address and auto precharge bit(A8) for READ/WRITE commands, to select one location out of the memory array in the respective bank. A8 sampled during a PRECHARGE command determines whether the PRECHARGE applies to one bank (A8 LOW, bank selected by BAO - BA2) or all banks (A8 HIGH). The address inputs also provide the op-code during a MODE REGISTER SET command. BAO and BA1 define which mode register (mode register or extended mode register) is loaded during the LOAD MODE REGISTER command.                                 |

| B(2, 3), C(2, 3), E2, F(2, 3),<br>G3,B(10, 11), C(10, 11),<br>E11, F(10, 11), G10, L10,<br>M(10, 11), N11, R(10, 11),<br>T(10,11), L3, M(2, 3),<br>N2,R(2, 3), T(2, 3) | DQ0-31          | I/O    | Data Input/Output:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| D(3, 10), P(3, 10)                                                                                                                                                     | RDQS0-3         | Output | READ Data Strobe: Output with read data. RDQS is edge-aligned with read data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| D(2, 11), P(2, 11)                                                                                                                                                     | WDQS0-3         | Input  | WRITE Data strobe: Input with write data. WDQS is center aligned to the input data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| U4                                                                                                                                                                     | SEN             | Input  | Scan Enable Pin. Logic High would enable Scan Mode. Should be tied to GND when not in use. This pin is a CMOS input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| J(2, 3)                                                                                                                                                                | NC/RFU          |        | No Connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

#### **BALLOUT DESCRIPTIONS**

-CONTINUE

| FBGA Ball Out                                                                         | SYMBOL | TYPE      | DESCRIPTION                                                                            |

|---------------------------------------------------------------------------------------|--------|-----------|----------------------------------------------------------------------------------------|

| A(1, 12), C(1, 4, 9, 12),<br>J(4, 9), N(1, 4, 9, 12),<br>R(1, 4, 9, 12), U(1, 12)     | VDDQ   | Supply    | DQ Power Supply: +1.8V. Isolated on the die for improved noise immunity.               |

| B(1, 4, 9, 12), D(1, 4, 9, 12), G(2, 11),<br>L(2, 11), P(1, 4, 9, 12), T(1, 4, 9, 12) | VSSQ   | Supply    | DQ Ground: Isolated on the die for improved noise immunity.                            |

| A(2, 11), F(1, 12),<br>M(1, 12), U(2, 11) K(1, 12)                                    | VDD    | Supply    | Power Supply: +1.8V.                                                                   |

| A(3, 10), G(1, 12),<br>L(1, 12), U(3, 10) J(1, 12)                                    | VSS    | Supply    | Ground                                                                                 |

| H(1, 12)                                                                              | VREF   | Supply    | Reference voltage.                                                                     |

| А9                                                                                    | MF     | Reference | Mirror Function for clamshell mounting of DRAMs                                        |

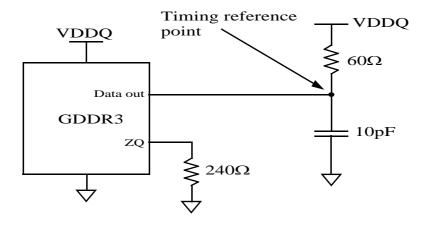

| A4 ZQ Ref                                                                             |        | Reference | External Reference Pin for autocalibration. It should be connected to $RQ(=240\Omega)$ |

| U9                                                                                    | RES    | Reference | Reset Pin. The RES pin is a VDD CMOS input.                                            |

#### Mirror Function

The GDDR3 SDRAM provides a mirror function(MF) ball to change the physical location of the control lines and all address lines, assisting in routing devices back to back. The MF ball will affect RAS#, CAS#, WE#, CS# and CKE on balls H3, F4, H9, F9 and H4 respectively and A0, A1, A2, A3, A4, A5, A6, A7, A8, A9, A10, A11, BA0, BA1 and BA2 on balls K4, H2, K3, M4, K9, H11, K10, L9, K11, M9, K2, L4, G4, G9 and H10 respectively and only detects a DC input. The MF ball should be tied directly to VSS of VDD depending on the control line orientation desired.

When MF ball is tied low the ball orientation is as follows. RAS#-H3, CAS#-F4, WE#-H9, CS#-F9, CKE-H4, A0-K4, A1-H2, A2-K3, A3-M4, A4-K9, A5-H11, A6-K10, A7-L9, A8-K11, A9-M9, A10-K2, A11-L4, BA0-G4, BA1-G9 and BA2-H10. The high condition on the MF ball will change the location of the control balls as follows; CS#-F4, cas#-F9, ras#-H10, WE#-H4, CKE-H9, A0-K9, A1-H11, A2-K10, A3-M9, A4-K4, A5-H2, A6-K3, A7-L4, A8-K2, A9-M4, A10-K11, A11-L9, BA0-G9, BA1-G4 and BA2-H3. This Mirror Fuction does not work under Boundary Scan Test condition.

# **Mirror Function Signal Mapping**

| PIN  | MF LOGIC STATE |     |  |  |  |

|------|----------------|-----|--|--|--|

| PIN  | HIGH           | LOW |  |  |  |

| RAS# | H10            | H3  |  |  |  |

| CAS# | F9             | F4  |  |  |  |

| WE#  | H4             | Н9  |  |  |  |

| CS#  | F4             | F9  |  |  |  |

| CKE  | H9             | H4  |  |  |  |

| A0   | К9             | K4  |  |  |  |

| A1   | H11            | H2  |  |  |  |

| A2   | K10            | K3  |  |  |  |

| A3   | M9             | M4  |  |  |  |

| A4   | K4             | К9  |  |  |  |

| A5   | H2             | H11 |  |  |  |

| A6   | К3             | K10 |  |  |  |

| A7   | L4             | L9  |  |  |  |

| A8   | K2             | K11 |  |  |  |

| A9   | M4             | M9  |  |  |  |

| A10  | K11            | K2  |  |  |  |

| A11  | L9             | L4  |  |  |  |

| BA0  | G9             | G4  |  |  |  |

| BA1  | G4             | G9  |  |  |  |

| BA2  | H3             | H10 |  |  |  |

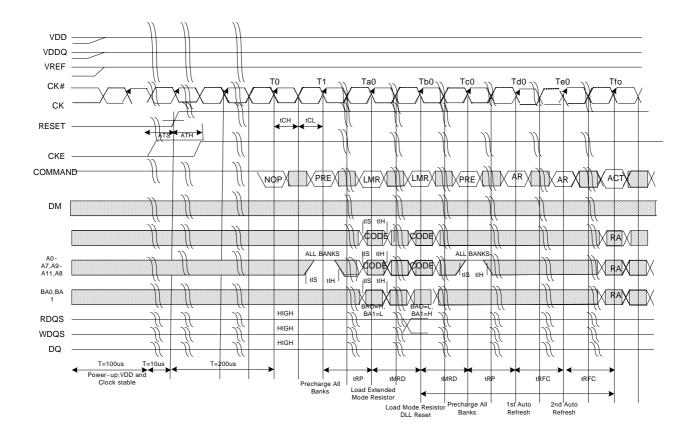

# **GDDR3 Initialization and Power Up**

GDDR3 SDRAMs must be powered up and initialized in a predefined manner. Operational procedures other than those specified may result in undefined operation. Power must be first applied to VDD and VDDQ simultaneously or VDD first and VDDQ later, and then to VREF. VREF can be applied any time after VDDQ. Once power has been applied and the clocks are stable the GDDR3 device requires 200us before the RES pin transitions to high. Upon power-up and after the clock is stable, the on-die termination value for the address and control pins will be set, based on the state of CKE when the RES pin transitions from LOW to HIGH. On the rising edge of RES, the CKE pin is latched to determine the on die termination value for the address and control lines. If CKE is sampled at a logic LOW then the on die termination will be set to 1/2 of ZQ and, if CKE is sampled logic HIGH then the on die termination will be set to the same value as ZQ. CKE must meet tATS and tATH on the rising of RES to set the on die termination for address and control lines. Once tATH is met, set CKE to HIGH. An additional 200us is required for the address and command on die terminations to calibrate and update.

RES must be maintained at a logic LOW-level value and CS# must be maintained HIGH, during the first stage of power-up to ensure that the DQ outputs will be in a High-Z state(un-terminated).

After the RES pin transitions from LOW to HIGH, wait until a 200us delay is satisfied. Issue DESELECT on the command bus during this time. Issue a PRECHARGE ALL command. Next a LOAD MODE REGISTER command must be issued for the extended mode register (BA1 LOW and BA0 HIGH) to activate the DLL and set operating parameters, followed by the LOAD MODE REGISTER command (BA0/BA1 both LOW) to reset the DLL and to program the rest of the operating parameters. 5k clock cycles are required between the DLL reset and any READ command to allow the DLL to lock. A PRECHARGE ALL command should then be applied, placing the device in the all banks idle state.

Once in the idle state, two AUTO REFRESH cycles must be issued. Following these requirements, the GDDR3 SDRAM is ready for normal operation.

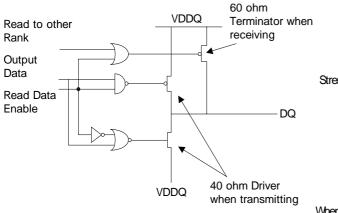

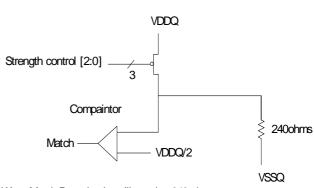

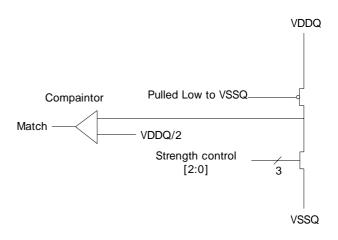

# **ODT Updating**

The GDDR3 SDRAM uses programmable impedance output buffers. This allows a user to match the driver impedance to the system. To adjust the impedance, an external precision resistor (RQ) is connected between the ZQ pin and VSSQ. The value of the resistor must be six times the desired driver impedance. For example, a  $240\Omega$  resistor is required for an output impedance of  $40\Omega$ . To ensure that output impedance is one-sixth the value of RQ (within 10 percent), RQ should be in the range of  $210\Omega$  to  $270\Omega$ . ( $30\Omega$  -  $50\Omega$  output impedance).

CK and CK# are not internally terminated. CK and CK# will be terminated on the system module using external 1% resistors.

The output impedance and on die termination is updated during every AUTO REFRRESH commands to compensate for variations in supply voltage and temperature. The output impedance updates are transparent to the system. Impedance updates do not affect device operation, and all datasheet timings and current specifications are met during an update.

A maximum of eight AUTO REFRESH commands can be posted to any given GDDR3 SDRAM, meaning that the maximum absolute interval between any AUTO REFRESH command and the next AUTO REFRESH command is 8 x 3.9us (31.2us). This maximum absolute interval guarantees that the output drivers and the on die terminations of GDDR3 SDRAMs are recalibrated often enough to keep the impedance characteristics of those within the specified boundaries.

#### **ODT Control**

Bus snooping for READ commands other than CS# is used to control the on die termination in the dual load configuration. The GDDR3 SGRAM will disable the DQ and RDQS on die termination when a READ command is detected regardless of the state of CS#. The on die termination is disabled x clocks after the READ command where x equals CL-1 and stay off for a duration of BL/2+2CK. In a two-rank system, both DRAM devices snoop the bus for READ commands to either device and both will disable the on die termination, for the DQ and DQS pins if a READ command is detected. The on die termination for all other pins on the device is always turned-on for both a single-rank system and a dual-rank system unless it is turned off in the EMRS. Only DQ,WDQS and DM pins can turn off through the EMRS.

DON'T CARE TRANSITIONING DATA

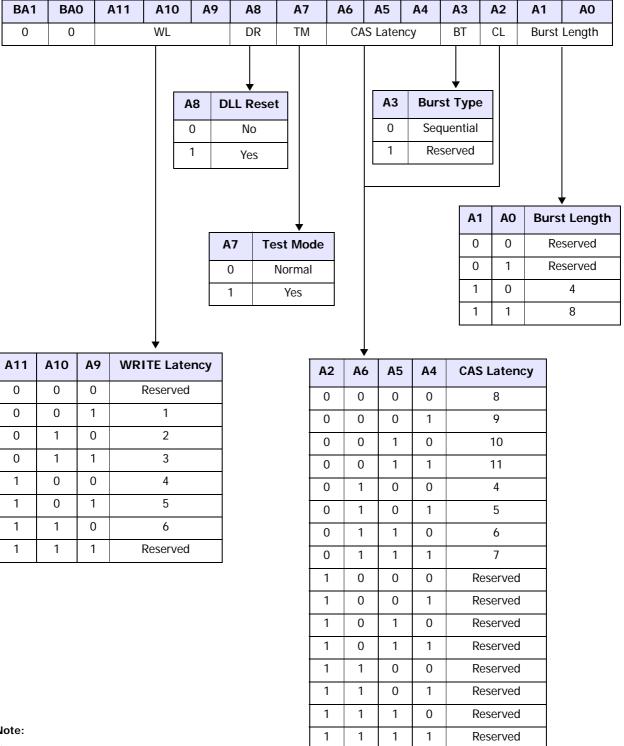

# **Mode Register Definition**

The mode register is used to define the specific mode of operation of the GDDR3 SDRAM. This definition includes the selection of a burst length, CAS latency, WRITE latency, and operating mode, as shown in Figure 3, Mode Register Definition, on page 11. The mode register is programmed via the MODE REGISTER SET command (with BA0=0, BA1=0 and BA2=0) and will retain the stored information until it is programmed again or the device loses power (except for bit A8, which is self-clearing). Re-programming the mode register will not alter the contents of the memory. The mode register must be loaded (reloaded) when all banks are idle and no bursts are in progress, and the controller must wait the specified time before initiating any subsequent operation. Violating either of these requirements will result in unspecified operation.

Mode register bits A2-A0 specify the burst length; A3 specifies the type of burst (sequential); A4-A6 specify the CAS latency; A7 is a test mode; A8 specifies the operating mode; and A9-A11 specifiy the WRITE latency.

Figure 3: Mode Register Definition

#### Note:

1) The DLL reset command is self-clearing.

#### **Burst Length**

Read and write accesses to the GDDR3 SDRAM are burst-oriented, with the burst length being programmable, as shown in Figure 3, Mode Register Definition. The burst length determines the maximum number of column locations that can be accessed for a given READ or WRITE command. Burst lengths of 4 or 8 locations are available for the sequential burst type. Reserved states should not be used, as unknown operation or incompatibility with future versions may result. When a READ or WRITE command is issued, a block of columns equal to the burst length is effectively selected. All accesses for that burst take place within this block, meaning that the burst will wrap within the block if a boundary is reached. The block is uniquely selected by A2. Ai when the burst length is set to four and by A3. Ai when the burst length is set to eight(where Ai is the most significant column address bit for a given configuration). The remaining(least significant) address bit(s) is (are) used to select the starting location within the block. The programmed burst length applies to both read and write bursts.

# **Burst Type**

Accesses within a given burst must be programmed to be sequential; this is referred to as the burst type and is selected via bit A3. This device does not support the interleaved burst mode found in DDR SDRAM devices. The ordering of accesses within a burst is determined by the burst length, the burst type, and the starting column address, as shown in Table3.

**Table 3: Burst Definition**

| Burst <sup>1, 2</sup><br>Length | Startin | ng Column A | ddress | Order of Accesses<br>Within a Burst |

|---------------------------------|---------|-------------|--------|-------------------------------------|

| 20119.11                        |         |             |        | Type=Sequential                     |

| 4                               |         | A1          | A0     |                                     |

| 7                               |         | 0           | 0      | 0-1-2-3                             |

|                                 | A2      | A1          | A0     |                                     |

| 8                               | 0       | 0           | 0      | 0-1-2-3-4-5-6-7                     |

|                                 | 1       | 0           | 0      | 4-5-6-7-0-1-2-3                     |

#### NOTE

- 1. For a burst length of four, A2-A7 select the block of four burst; A0-A1 select the starting column within the block and must be set to zero.

- 2. For a burst length of eight, A3-A7 select the of eight burst; A0-A2 select the starting column within the block.

# **CAS Latency**

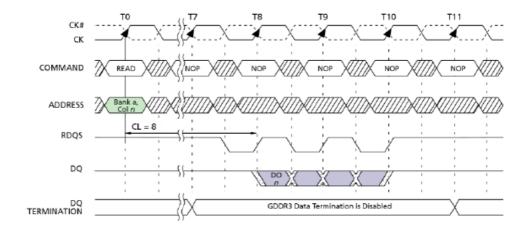

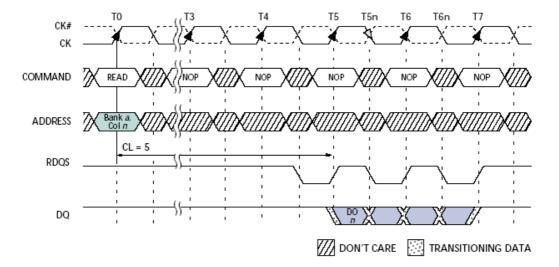

The CAS latency is the delay, in clock cycles, between the registration of a READ command and the availability of the first bit of output data. The latency can be set to 7-11 clocks, as shown in Figure 4, CAS Latency, on page 13. If a READ command is registered at clock edge n, and the latency is m clocks, the data will be available nominally coincident with clock edge n + m. Table4 indicates the operating frequencies at which each CAS latency setting can be used. For the proper operation, do not change the CL without DLL reset. Or proper CL should be set with DLL reset code

Reserved states should not be used as unknown operation or incompatibility with future versions may result.

**Table 4: CAS Latency**

|        | ALLOWABLE OPERATING FREQUENCY (MHz) |                       |       |       |  |  |  |  |  |

|--------|-------------------------------------|-----------------------|-------|-------|--|--|--|--|--|

| SPEED  | CL=11                               | CL=11 CL=10 CL=9 CL=7 |       |       |  |  |  |  |  |

| -N3    | <=1300                              |                       |       |       |  |  |  |  |  |

| -N2    | <=1200                              |                       |       |       |  |  |  |  |  |

| -NO    | <=1000                              |                       |       |       |  |  |  |  |  |

| -11    |                                     | <=900                 |       |       |  |  |  |  |  |

| -14(L) |                                     |                       | <=700 |       |  |  |  |  |  |

| -18    |                                     |                       |       | <=550 |  |  |  |  |  |

| -20    |                                     |                       |       | <=500 |  |  |  |  |  |

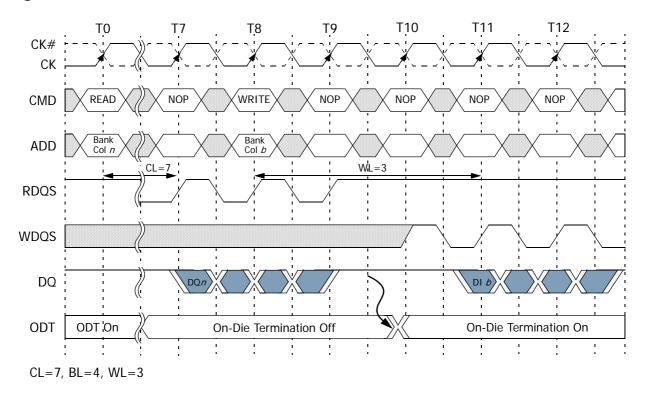

Figure 4: CAS Latency

#### Write Latency

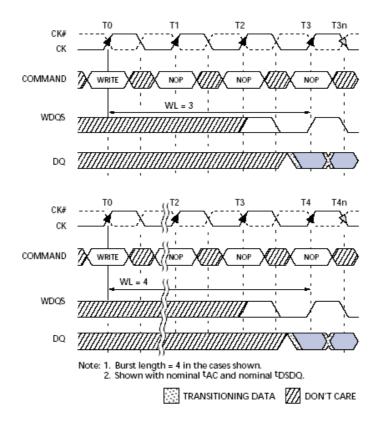

The WRITE latency (WL) is the delay, in clock cycles, between the registration of a WRITE command and the availability of the first bit of input data as shown in Figure 5. The latency can be set from 1 to 6 clocks depending on the operating frequency and desired current draw. When the write latencies are set to 1 or 4 clocks, the input receivers never turn off, in turn, raising the operating power. When the WRITE latency is set to 5 or 6 clocks the input receivers turn on when the WRITE command is registered. If a WRITE command is registered at clock edge n, and the latency is m clocks, the data will be available nominally coincident with clock edge n + m. Reserved states should not be used as unknown operation or incompatibility with future versions may result.

Figure 5: WRITE Latency

#### **Test Mode**

The normal operating mode is selected by issuing a MODE REGISTER SET command with bit A7 set to zero, and bits A0~A6 and A8~A11 set to the desired values. Test Mode is initiated by issuing a MODE REGISTER SET command with bit A7 set to one, and bits A0~A6 and A8~A11 set to the desired values. Test mode funtions are specific to each DRAM vendor and their exact function are hidden from the user.

#### **DLL Reset**

The normal operating mode is selected by issuing a MODE REGISTER SET command with bit A8 set to zero, and bits A0~A7 and A9~A11 set to the desired values. A DLL reset is initiated by issuing a MODE REGISTER SET command with bit A8 set to one, and bits A0~A7 and A9~A11 set to the desired values. When a DLL Reset is complete the GDDR3 SDRAM Reset bit, A8 of the mode register is self clearing (i.e.automatically set to a zero by the DRAM). Test modes and reserved states should not be used because unknown operation or incompatibility with future versions may result.

# **Extended Mode Register**

The extended mode register controls functions beyond those controlled by the mode register; these additional functions are DLL enable/disable, drive strength, data termination, vendor ID. These functions are controlled via the bits shown in Figure 6, Extended Mode Register Definition. The extended mode register is programmed via the LOAD MODE REGISTER command to the mode register (with BAO = 1, BA1 = 0 and BA2=0) and will retain the stored information until it is programmed again or the device loses power. The enabling of the DLL should always be followed by a LOAD MODE REGISTER command to the mode register (BAO/BA1 both low) to reset the DLL. The extended mode register must be loaded when all banks are idle and no bursts are in progress, and the controller must wait the specified time before initiating any subsequent operation. Violating either of these requirements could result in unspecified operation.

BA0 A11 A10 Α9 **A8** Α7 Α4 **A6 A5 A3 A2** Α1 **A0** 0 1 Term VID 0 tWR DLL tWR DT DΖ Ron Ron of Pull-up **Drive Strength A1** AO Α9 Ron Α6 **DLL** enable 0 0 Auto Cal 0 40 0 Enable 0 1 30 60 1 0 40 Disable 1 1 50(48) A10 Vendor ID **A3 A2 Data Termination** Off 0 0 DT disabled 0 1 On 0 RES 1 1 0 1/4 RQ tWR Α7 **A5** Α4 1/2 RQ 1 1 0 0 n 12 A11 **C/A Termination** 0 0 1 14 0 Default 0 1 0 5 0 6 Half of default 1 1 1 0 0 1 7 1 0 1 8 9 0 1 1 10 1

Figure 6: Extended Mode Register Definition

#### NOTE:

- 1. The DT disable function disables all pins.

- 2. The default setting at Power Up for A3,A2 is 10 or 11

- 3. If the user activates bits in the extended mode register in an optional field, device will work improperly.

- 4. The optional values of the drive strength (A1,A0) are only targets and can be determined by the DRAM vendor.

- 5. WR\_A (write recovery time for autoprecharge) in clock cycles is calculated by dividing tWR (in nS) and rounding up to the next integer (WR[cycles] = tWR(ns)/tCK(ns)). The mode register must be programmed to this value.

- 6. Default value in C/A Termination is determined by CKE status at the rising edge of RESET during power-up.

#### **DLL Enable/Disable**

The DLL must be enabled for normal operation. DLL enable is required during power-up initialization and upon returning to normal operation after disabling the DLL for debugging or evaluation. (When the device exits self refresh mode, the DLL is enabled automatically.) Any time the DLL is enabled, 5K clock cycles must occur before a READ command can be issued.

# tWR(WR\_A)

The value of tWR in the AC parametrics table on page 49 of this specification is loaded into register bits 5 and 4. The WR\_A (write recovery time for autoprecharge) in clock cycles is calculated by dividing tWR (in ns) and rounding up to the next integer (WR[cycles] = tWR(ns)/tCK(ns)). The mode register must be programmed to this value.

#### **Data Termination**

The data termination value is used to define the value for the on die termination for the DQ, DM, and WDQS pins. The GDDR3 device supports one-quarter ZQ and one-half ZQ termination for a nominal 60 or 120 set with bit A3 and A2 during an EMRS command for a single- or dual-loaded system.

#### **Data Driver Impedance**

The Data Driver Impedance, DZ, is used to determine the value of the data drivers impedance. When auto calibration is used the data driver impedance is set to 1/6 ZQ and it's tolerance is determined by the calibration accuracy of the device. When any other value is selected the target impedance is set nominally to the selected impedance. However, the accuracy is now determined by the device's specific process corner, applied voltage and operating temperature.

# **Manufacturers Vendor Code Identifi- cation**

The Manufacturers Vendor Code, V, is selected by issuing an EXTENDED MODE REGISTER SET command with bits A10 set to 1, and bits A0-A9 and A11 set to the desired values. When the V function is enabled the GDDR3 SDRAM will provide its manufacturers vendor code on DQ[3:0] and revision identification on DQ[7:4]. The code will be driven onto the DQ bus after tIDON with respect to the EMRS that set A10 to 1. The DQ bus will be continuously driven until an EMRS write sets A10 back to 0. The DQ bus will be in a Hi-Z state after tIDOFF. The code can be sampled by the controller after waiting tIDON max and before tIDOFF min.

Table 5: Vendor IDs

| VENDOR   | DQ(3:0) |

|----------|---------|

| Reserved | 0       |

| Samsung  | 1       |

| Infineon | 2       |

| Elpida   | 3       |

| Etron    | 4       |

| Nanya    | 5       |

| Hynix    | 6       |

| Mosel    | 7       |

| Winbond  | 8       |

| ESMT     | 9       |

| Reserved | Α       |

| Reserved | В       |

| Reserved | С       |

| Reserved | D       |

| Reserved | E       |

| Micron   | F       |

# Clock frequency change sequence during the device operation Not only Clock frequency but also VDD change sequence as below

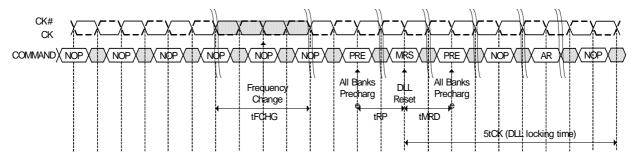

#### Both existing tCK and desired tCK are in DLL-On mode

- Change frequency from existing frequency to desired frequency

- Issue Precharge All Banks command

- Issue MRS command to reset the DLL while other fields are valid and required 5K tCK to lock the DLL

- Issue Precharge All Banks command. Issue at least Auto-Refresh command

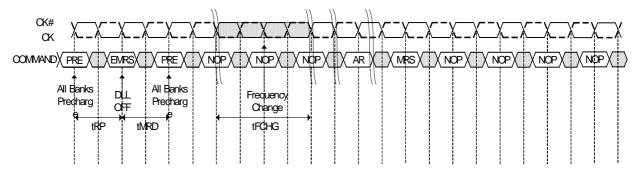

#### Existing tCK is in DLL-on mode while desired tCK is in DLL-off mode

- Issue Precharge All Banks command

- Issue EMRS command to disable the DLL

- Issue Precharge All Banks command

- Change the frequency from existing to desired.

- Issue Auto-Refresh command at least two. Issue MRS command

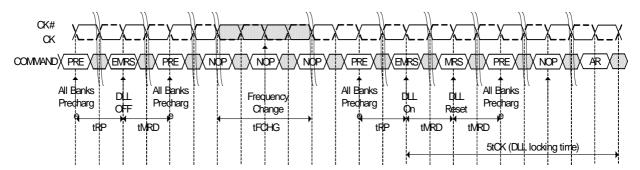

#### Clock frequency change in case existing tCK is in DLL-off mode while desired tCK is in DLL-on mode

- Issue Precharge All Banks command and issue EMRS command to disable the DLL.

- Issue Precharge All Banks command.

- Change the clock frequency from existing to desired

- Issue Precharge All Banks command.

- Issue EMRS command to enable the DLL

- Issue MRS command to reset the DLL and required 5K tCK to lock the DLL.

- Issue Precharge All Banks command.

- Issue Auto-Refresh command at least two

#### Commands

Table6 provides a quick reference of available commands, followed by a description of each command. Two additional truth tables appear following the Operation section; these tables provide current state/next state information.

#### Table 6: Truth Table - Commands

Note: 1

| NAME (FUNCTION)                                        | CS# | RAS# | CAS# | WE# | ADDR     | NOTES |

|--------------------------------------------------------|-----|------|------|-----|----------|-------|

| DESELECT (NOP)                                         | Н   | Х    | Х    | Х   | Х        | 8     |

| NO OPERATION (NOP)                                     | L   | Н    | Н    | Н   | Х        | 8     |

| ACTIVE (Select bank and activate row)                  | L   | L    | Н    | Н   | Bank/Row | 3     |

| READ (Select bank and column, and start READ burst)    | L   | Н    | L    | Н   | Bank/Col | 4     |

| WRITE (Select bank and column, and start WRITE burst)  | L   | Н    | L    | L   | Bank/Col | 4     |

| PRECHARGE (Deactivate row in bank or banks)            | L   | L    | Н    | L   | Code     | 5     |

| AUTO REFRESH or SELF REFRESH (Enter self refresh mode) | L   | L    | L    | Н   | Х        | 6, 7  |

| LOAD MODE REGISTER                                     | L   | L    | L    | L   | Op-Code  | 2     |

| DATA TERMINATOR DISABLE                                | Х   | Н    | L    | Н   | Х        | 10    |

# Table 7: Truth Table 2 - DM Operation

| NAME (FUNCTION) | DM | DQS   | NOTES |

|-----------------|----|-------|-------|

| Write Enable    | L  | Valid | 9     |

| Write Inhibit   | Н  | Χ     | 8     |

#### NOTE:

- 1. CKE is HIGH for all commands shown except SELF REFRESH.

- 2. BA0-BA1 select either the mode register or the extended mode register (BA0 = 0, BA1 = 0 select the mode register; BA0 = 1, BA1 = 0 select extended mode register; other combinations of BA0.BA1 are reserved). A0-A11 provide the opcode to be written to the selected mode register.

- 3. BAO-BA2 provide bank address and AO-A11 provide row address.

- 4. BA0-BA2 provide bank address; A0-A7 and A9 provide column address; A8 HIGH enables the auto precharge feature (non-persistent), and A8 LOW disables the auto precharge feature.

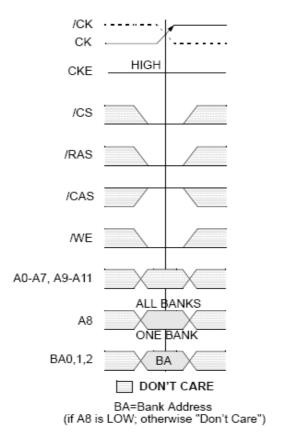

- 5. A8 LOW: BA0-BA2 determine which bank is precharged. A8 HIGH: all banks are precharged and BA0-BA2 are "Don't Care."

- 6. This command is AUTO REFRESH if CKE is HIGH, SELF REFRESH if CKE is LOW.

- 7. Internal refresh counter controls row addressing; all inputs and I/Os are Don't Care except for CKE.

- 8. DESELECT and NOP are functionally interchangeable.

- 9. Used to mask write data; provided coincident with the corresponding data.

- 10. Used for bus snooping when the DQ termination is set to 120 ohms in the EMR and cannot be used during power-down or self refresh.

#### **Deselect**

The DESELECT function (CS# HIGH) prevents new commands from being executed by the GDDR3 SDRAM. The GDDR3 SDRAM is effectively deselected. Operations already in progress are not affected.

### **NO Operation (NOP)**

The NO OPERATION (NOP) command is used to instruct the selected GDDR3 SDRAM to perform a NOP(CS# LOW). This prevents unwanted commands from being registered during idle or wait states. Operations already in progress are not affected.

#### LOAD MODE REGISTER

The mode registers are loaded via inputs A0~A11. See mode register descriptions in the Register Definition section. The LOAD MODE REGISTER command can only be issued when all banks are idle, and a subsequent executable command cannot be issued until tMRD is met.

#### **ACTIVE**

The ACTIVE command is used to open (or activate) a row in a particular bank for a subsequent access. The value on the BAO~BA2 inputs selects the bank, and the address provided on inputs AO~A11 selects the row. This row remains active (or open) for accesses until a precharge command is issued to that bank. A precharge command must be issued before opening a different row in the same bank.

#### **READ**

The READ command is used to initiate a burst read access to an active row. The value on the BAO~BA2 inputs selects the bank, and the address provided on inputs AO~A7, A9 selects the starting column location. The value on input A8 determines whether or not auto precharge is used. If auto precharge is selected, the row being accessed will be precharged at the end of the read burst; if auto precharge is not selected, the row will remain open for subsequent accesses.

#### WRITE

The WRITE command is used to initiate a burst write access to an active row. The value on the BAO~BA2 inputs selects the bank, and the address provided on inputs AO~A7, A9 selects the starting column location. The value on input A8 determines whether or not auto precharge is used. If auto precharge is selected, the row being accessed will be precharged at the end of the write burst; if auto precharge is not selected, the row will remain open for subsequent accesses. Input data appearing on the DQs is written to the memory array subject to the DM input logic level appearing coincident with the data. If a given DM signal is registered LOW, the corresponding data will be written to memory; if the DM signal is registered HIGH, the corresponding data inputs will be ignored and a write will not be executed to that byte/column location.

#### **PRECHARGE**

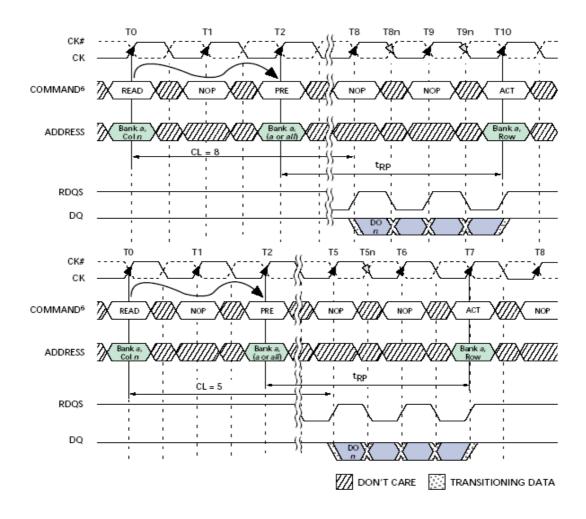

The PRECHARGE command is used to deactivate the open row in a particular bank or the open row in all banks. The bank(s) will be available for a subsequent row access a specified time (tRP) after the precharge command is issued. Input A8 determines whether one or all banks are to be precharged, and in the case where only one bank is to be precharged, inputs BA0.BA2 select the bank. Otherwise, BA0. BA2 are treated as "Don't Care." Once a bank has been precharged, it is in the idle state and must be activated prior to any READ or WRITE commands being issued to that bank.

A PRECHARGE command will be treated as a NOP if there is no open row in that bank (idle state) or if the previously open row is already in the process of precharging.

#### **Auto Precharge**

Auto precharge is a feature that performs the same individual-bank precharge function described above but without requiring an explicit command. This is accomplished by using A8 to enable auto precharge in conjunction with a specific READ or WRITE command. A precharge of the bank/row that is addressed with the READ or WRITE command is automatically performed upon completion of the READ or WRITE burst. Auto precharge is nonpersistent in that it is either enabled or disabled for each individual Read or Write command. Auto precharge ensures that the precharge is initiated at the earliest valid stage within a burst. This "earliest valid stage" is determined as if an explicit PRECHARGE command was issued at the earliest possible time, without violating tRAS min, as described for each burst type in the Operation section of this data sheet. The user must not issue another command to the same bank until the precharge time (tRP) is completed.

#### **AUTO REFRESH**

The addressing is generated by the internal refresh controller. This makes the address bits a Don't Care during an AUTO REFRESH command. The 512Mb x32 GDDR3 SDRAM requires AUTO REFRESH cycles at an average interval of 3.9us (maximum). A maximum of eight AUTO REFRESH commands can be posted to any given GDDR3 SDRAM, meaning that the maximum absolute interval between any AUTO REFRESH command and the next AUTO REFRESH command is 9 x 3.9us (35.1us). This maximum absolute interval allows GDDR3 SDRAM output drivers to automatically recalibrate to compensate for voltage and temperature changes. AUTO REFRESH is used during normal operation of the GDDR3 SDRAM and is analogous to CAS#-BEFORE-RAS# (CBR) refresh in FPM/EDO DRAMs.This command is nonpersistent, so it must be issued each time a refresh is required.

#### **SELF REFRESH**

The SELF REFRESH command can be used to retain data in the GDDR3 SDRAM, even if the rest of the system is powered down. When in the self refresh mode, the GDDR3 SDRAM retains data without external clocking. The SELF REFRESH command is initiated like an AUTO REFRESH command except CKE is disabled(LOW). The DLL is automatically disabled upon entering SELF REFRESH and is automatically enabled and reset upon exiting SELF REFRESH. The on-die termination is also disabled upon entering Self Refresh except for CKE and enabled upon exiting Self Refresh. (5K clock cycles must then occur before a READ command can be issued). Input signals except CKE are "Don't Care" during SELF REFRESH. The procedure for exiting self refresh requires a sequence of commands. First, CK and CK# must be stable prior to CKE going back HIGH. Once CKE is HIGH, the GDDR3 SDRAM must have NOP commands issued for tXSNR because time is required for the completion of any internal refresh in progress. A simple algorithm for meeting both refresh and DLL requirements and output calibration is to apply NOPs for 1000 clock cycles before applying any other command to allow the DLL to lock and the output drivers to recalibrate. If the GDDR3 device enters SELF REFRESH with the DLL disabled the GDDR3 device will exit SELF REFRESH with the DLL disabled.

# DATA TERMINATOR DISABLE (BUS SNOOPING FOR READ COMMANDS)

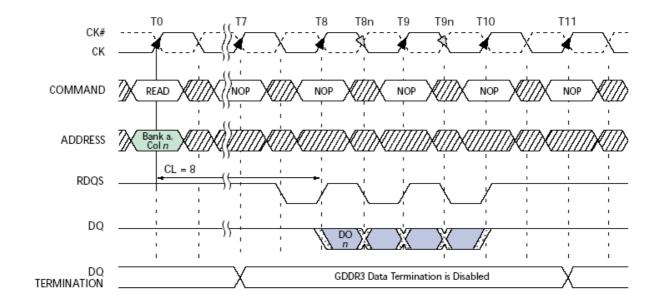

Bus snooping for READ commands other than CS# is used to control the on-die termination in the dual load configuration. The GDDR3 SDRAM will disable the on-die termination when a READ command is detected, regardless of the state of CS#, when the ODT for the DQ pins are set for dual loads (120 ). The on-die termination is disabled x clocks after the READ command where x equals CL-1 and stay off for a duration of BL/2 +2CK, as shown in Figure8, Data Termination Disable Timing on page15. In a two-rank system, both DRAM devices snoop the bus for READ commands to either device and both will disable the on-die termination if a READ command is detected. The on-die termination for all other pins on the device are always turned-on for both a single-rank system and a dual-rank system.

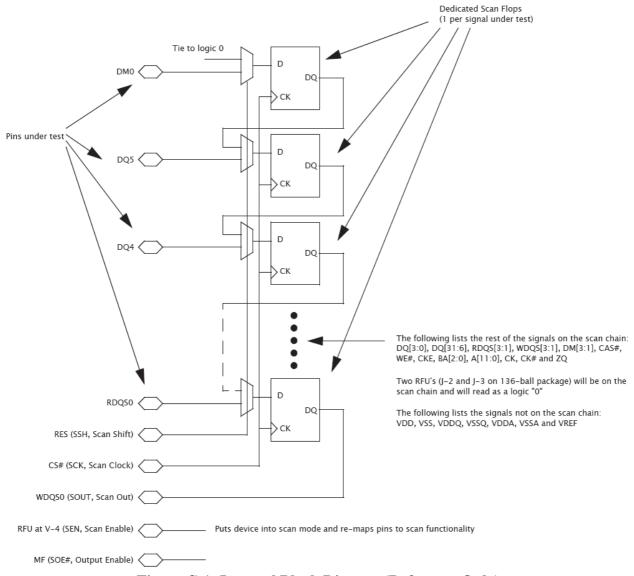

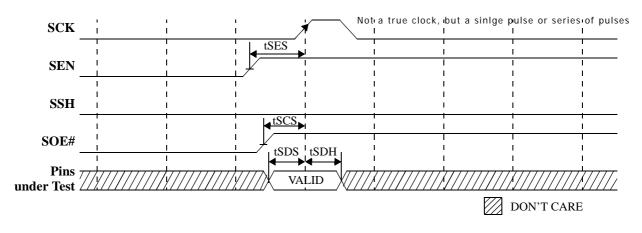

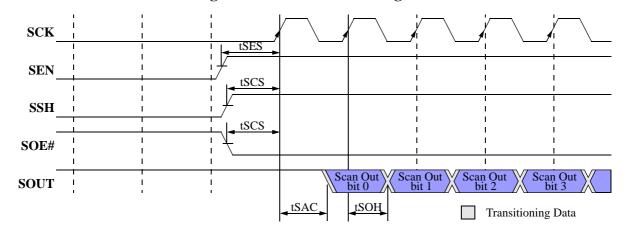

# **Boundary Scan Test Mode**

The 512Mb GDDR3 incorporates a modified boundary scan test mode as an optional feature. This mode doesn't operate in accordance with IEEE Standard 1149.11990. To save the current GDDR3 ballout, this mode will scan the parallel data input and output the scanned data through WDQS0 pin controlled by an addon pin, SEN which is located at U4 of 136 ball package. You can find the detailed descriptions of this feature on Appendix C (page 62).

**Figure 8: Data Termination Disable Timing**

DON'T CARE TRANSITIONING DATA

#### NOTE:

- 1. DO n = data-out from column n.

- 2. Burst length = 4.

- 3. Three subsequent elements of data-out appear in the specified order following DO n.

- 4. Shown with nominal tAC and tDQSQ.

- 5. RDQS will start driving high one-half clock cycle prior to the first falling edge.

- 6. The Data Terminators are disabled starting at CL 1 and the duration is BL/2 + 2CK.

- 7. READS to either rank disable both ranks' termination regardless of the logic level of CS#.

# **Operations**

#### **Bank/Row Activation**

Before any READ or WRITE commands can be issued to a bank within the GDDR3 device, a row in that bank must be "opened."

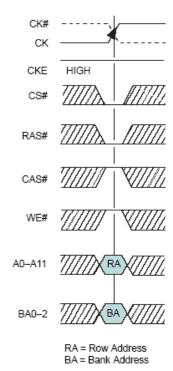

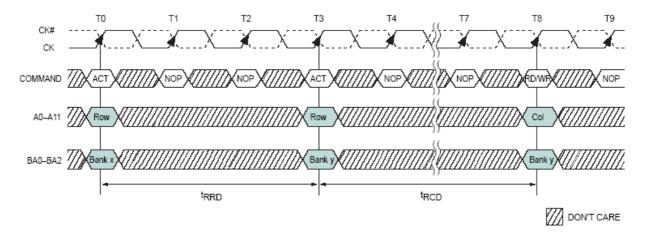

This is accomplished via the ACTIVE command, which selects both the bank and the row to be activated, as shown in Figure 9, Activating a Specific Row in a Specific Bank. After a row is opened with an ACTIVE command, a READ or WRITE command may be issued to that row, subject to the tRCD specification. tRCD min should be divided by the clock period and rounded up to the next whole number to determine the earliest clock edge after the ACTIVE command on which a READ or WRITE command can be entered. For example, a tRCD specification of 15ns with a 550 MHz clock(1.8ns period) results in 7.5 clocks rounded to 8.

This is reflected in Figure 10, Example: Meeting tRCD, which overs any cases where 7 < tRCDMIN/tCK <= 8. The same procedure is used to convert other specification limits from time units to clock cycles. A subsequent ACTIVE command to a different row in the same bank can only be issued after the previous active row has been "closed" (precharged). The minimum time interval between successive ACTIVE commands to the same bank is defined by tRC. A subsequent ACTIVE command to another bank can be issued while the first bank is being accessed, which results in a reduction of total row-access overhead. The minimum time interval between successive ACTIVE commands to different banks is defined by

# Figure 9: Activating a Specific Row in a Specific Bank

Figure 10: Example: Meeting tRCD

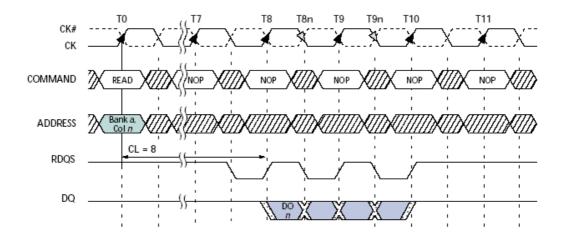

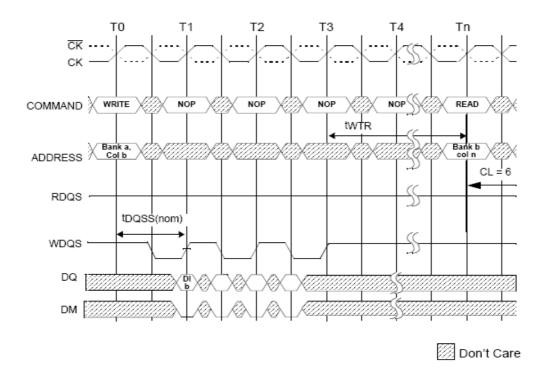

# **READ Timing**

#### READ burst is initiated with a READ command.

The starting column and bank addresses are provided with the READ command and auto precharge is either enabled or disabled for that burst access with the A8 pin. If auto precharge is enabled, the row being accessed is precharged at the completion of the burst after tRAS min has been met.

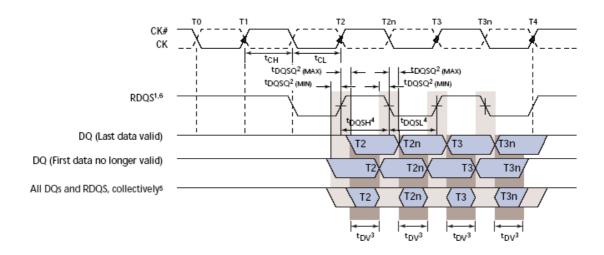

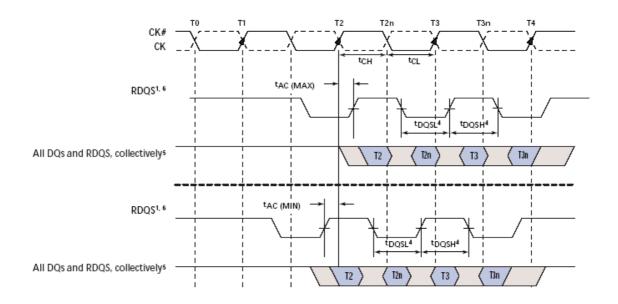

During READ bursts, the first valid data-out element from the starting column address will be available following the CAS latency after the READ command. Each subsequent data-out element will be valid nominally at the next positive or negative RDQS edges. The GDDR3 SDRAM drives the output data edge aligned to RDQS. And all outputs, i.e. DQs and RDQS, are also edge aligned to the clock. Prior to the first valid RDQS rising edge, a cycle is driven and specified as the READ preamble. The preamble consists of a half cycle High followed by a half cycle Low driven by the GDDR3 SDRAM. The cycle on RDQS consisting of a half cycle Low coincident with the last data-out element followed by a half cycle High is known as the read postamble, and it will be driven by the SDRAM. The SDRAM toggles RDQS only when it is driving valid data out onto on the bus.

Upon completion of a burst, assuming no other command has been initiated; the DQs and RDQS will go to be in Hi-Z state. VDDQ due to the on die termination. long as the bus turn around time is met. READ data cannot be terminated or truncated.

A PRECHARGE can also be issued to the SDRAM with the same timing restriction as the new READ command if tRAS is met as shown in Figure 17, READ to Precharge, on page 29. A WRITE can be issued any time after a READ command as long as the bus turn around time is met as shown in Figure 16, READ to WRITE, on page 28. READ data cannot be terminated or truncated

# Figure 12: READ Burst

#### NOTE:

- 1. DO n = data-out from column n.

- 2. Burst length = 4.

- 3. Three subsequent elements of data-out appear in the specified order following DO n.

- 4. Shown with nominal tAC and tDQSQ.

- 5. RDQS will start driving high one-half clock cycle prior to the first falling edge.

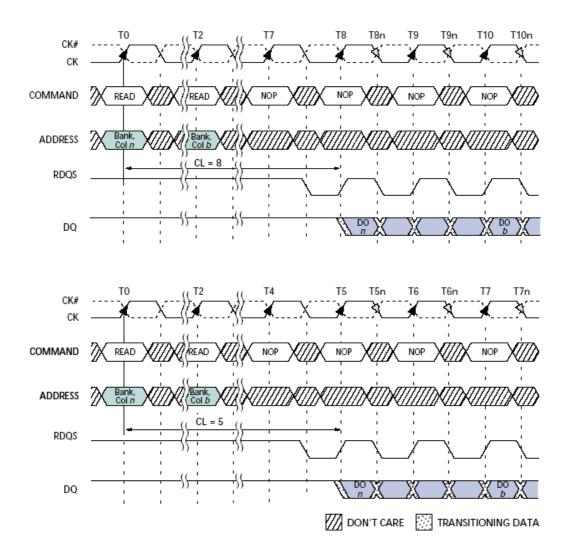

**Figure 13: Consecutive READ Bursts**

- 1. DO n (or b) = data-out from column n (or column b).

- 2. Burst length = 4

- 3. Three subsequent elements of data-out appear in the programmed order following DO n.

- 4. Three subsequent elements of data-out appear in the programmed order following DO b.

- 5. Shown with nominal tAC, and tDQSQ.

- 6. Example applies only when READ commands are issued to same device.

- 7. RDQS will start driving high one half clock cycle prior to the first falling edge of RDQS.

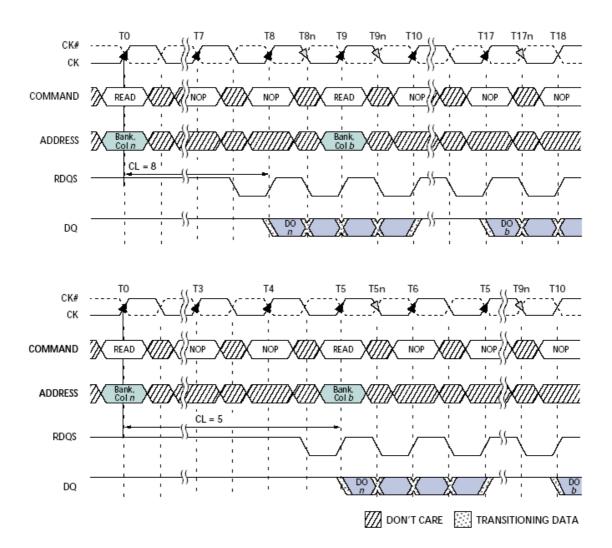

Figure 14: Non-Consecutive READ Bursts

- 1. DO n (or b) = data-out from column n (or column b).

- 2. Burst length = 4.

- 3. Three subsequent elements of data-out appear in the programmed order following DO  $\ensuremath{\text{n}}$ .

- 4. Three subsequent elements of data-out appear in the programmed order following DO b.

- 5. Shown with nominal tAC and tDQSQ.

- 6. Example applies when READ commands are issued to different devices or nonconsecutive READs.

- 7. RDQS will start driving high one-half clock cycle prior to the first falling edge of RDQS.

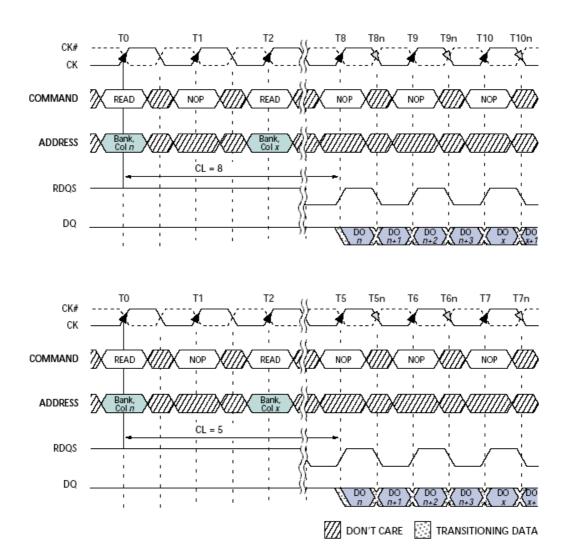

Figure 15: Random Read Accesses

- 1. DO n (or x or b or g) = data-out from column n (or column x or column b or column g).

- 2. Burst length = 4.

- 3. READs are to an active row in any banks.

- 4. Shown with nominal tAC and tDQSQ.

- 5. RDQS will start driving high one-half clock cycle prior to the first falling edge of RDQS.

Figure 16: Read to Write

- 1. DQ n = Data-out from column n.

- 2. DI b = Data-in from column b.

- 3. Shown with nominal tAC, tDQSQ and tDQSS.

- 4. Read Preamble consists of a half cycle High followed by a half cycle Low driven by device

- 5. Write Data cannot be driven onto the DQ bus for 2 clocks after the READ data is off the bus.

- 6. The timing diagram covers a READ to a WRITE command from different device, different bank or the same row in the same bank.

Figure 17: READ to Precharge

- 1. DO n = data-out from column n.

- 2. Burst length = 4.

- 3. Three subsequent elements of data-out appear in the programmed order following DO n.

- 4. Shown with nominal tAC and tDQSQ.

- 5. READ to PRECHARGE equals two clocks, which enables two data pairs of data-out.

- 6. PRE = PRECHARGE command; ACT = ACTIVE command.

- 7. RDQS will start driving high one-half clock cycle prior to the first falling edge of RDQS.

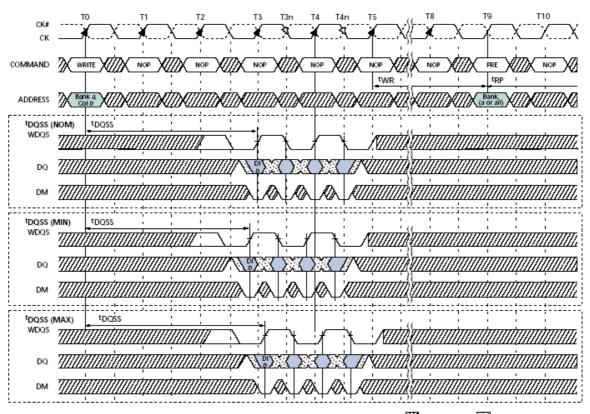

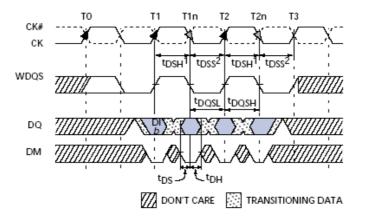

# **WRITE Timing**

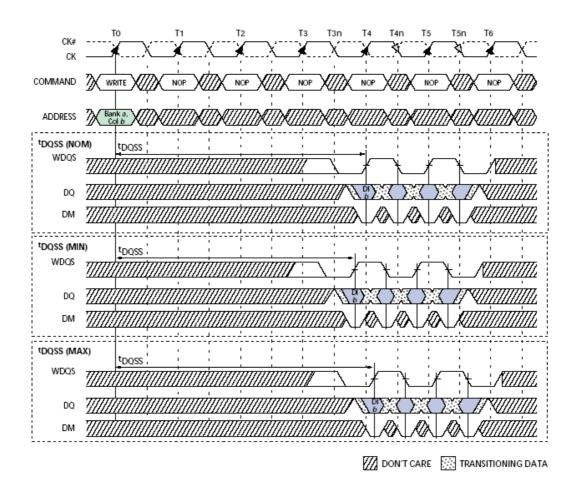

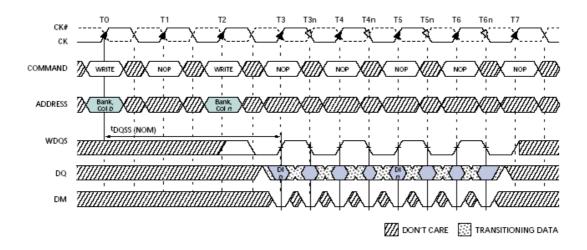

#### WRITE burst is initiated with a WRITE command.

The starting column and bank addresses are provided with the WRITE command, and auto precharge is either enabled or disabled for that access with the A8 pin. If auto precharge is enabled, the row being accessed is precharged at the completion of the burst.

During WRITE bursts, the first valid data-in element will be registered on the rising edge of WDQS following the write latency set in the mode register and subsequent data elements will be registered on successive edges of WDQS. Prior to the first valid WDQS rising edge, a cycle is needed and specified as the WRITE Preamble. The preamble consists of a half cycle High followed by a half cycle Low driven by the controller. The cycle on WDQS following the last data-in element is known as the write postamble and must be driven High by the controller, it can not be left to float High using the on die termination. The WDQS should only toggle on data transfers.

The time between the WRITE command and the first valid rising edge of WDQS (tDQSS) is specified relative to the write latency (WL - 0.25tCK and WL + 0.25tCK). All of the WRITE diagrams show the nominal case, and where the two extreme cases (i.e., tDQSS [MIN] and tDQSS [MAX]) might not be intuitive, they have also been included. Upon completion of a burst, assuming no other command has been initiated, the DQs should remain Hi-Z and any additional input data will be ignored.

Data for any WRITE burst may not be truncated with any subsequent command. A subsequent WRITE command can be issued on any positive edge of clock following the previous WRITE command assuming the previous burst has completed. The subsequent WRITE command can be issued x cycles after the previous WRITE command, where x equals the number of desired nibbles x2 (nibbles are required by 4n-prefetch architecture) i.e. BL/2. A subsequent READ command can be issued once tWTR is met or a subsequent PRECHARGE command can be issued once tWR is met. After the PRECHARGE command, a subsequent command to the same bank cannot be issued until tRP is met.

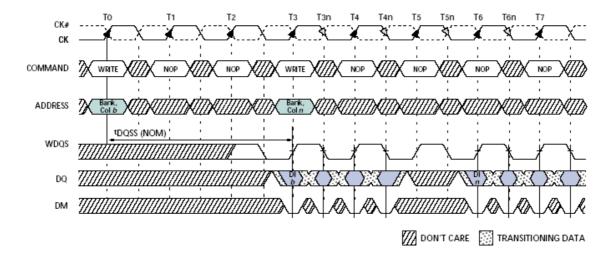

Figure 19: WRITE Burst

- 1. DI b = data-in for column b.

- 2. Three subsequent elements of data-in are applied in the specified order following DI b.

- 3. A burst of 4 is shown.

- 4. A8 is LOW with the WRITE command (auto precharge is disabled).

- 5. Write latency is set to 4.

Figure 20: Consecutive WRITE to WRITE

- 1. DI b, etc. = data-in for column b, etc.

- 2. Three subsequent elements of data-in are applied in the specified order following DI b.

- 3. Three subsequent elements of data-in are applied in the specified order following DI n.

- 4. Burst of 4 is shown.

- 5. Each WRITE command may be to any bank of the same device.

- 6. WRITE latency is set to 3.

Figure 21: NonConsecutive WRITE to WRITE

- 1. DI b, etc. = data-in for column b, etc.

- 2. Three subsequent elements of data-in are applied in the specified order following DI b.

- 3. Three subsequent elements of data-in are applied in the specified order following DI n.

- 4. A burst of 4 is shown.

- 5. Each WRITE command may be to any banks.

- 6. WRITE latency set to 3.

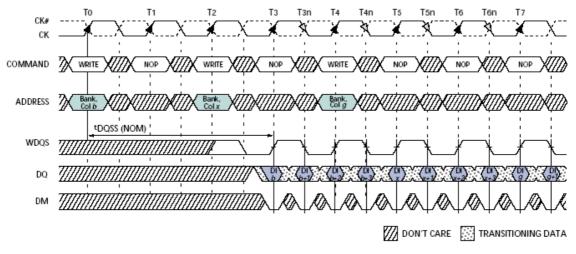

Figure 22: Random WRITE Cycles

- 1. DI b, etc. = data-in for column b, etc.

- 2. b', etc. = the next data-in following DI b, etc., according to the specified burst order.

- 3. Programmed burst length = 4 case is shown.

- 4. Each WRITE command may be to any banks.

- 5. Last write command will have the rest of the nibble on T8 and T8n.

- 6. WRITE latency is set to 3.

# Figure 23: WRITE to READ Timing

# NOTE:

- 1. DI b = Data In for column b

- 2. Three subsequent elements of Data In are applied following D1 b

- 3. tWTR is referenced from the first positive CK edge after the last  $\operatorname{Data}$  In

- 4. The READ and WRITE commands may be to any bank.

- 5. WRITE Latency is set to 1

- 6. The 4n prefetch architecture requires a 2-clock WRITE-to-READ turn around time (tWTR).

Figure 24: WRITE to PRECHARGE

DON'T CARE TRANSITIONING DATA

### NOTE:

- 1. DI b = data-in for column b.

- 2. Three subsequent elements of data-in are applied in the specified order following DI b.

- 3. A burst of 4 is shown.

- 4. A8 is LOW with the WRITE command (auto precharge is disabled).

- 5. WRITE latency is set to 3.

### **PRECHARGE**

The PRECHARGE command (shown in Figure 25) issued to deactivate the open row in a particular bank or the open row in all banks. The bank(s) will be available for a subsequent row access some specified time (tRP) after the precharge command is issued. Input A8 determines whether one or all banks are to be precharged, and in the case where only one bank is to be precharged, inputs BA0-BA2 select the bank. When all banks are to be precharged, inputs BA0-BA2 are treated as "Don't Care." Once a bank has been precharged, it is in the idle state and must be activated prior to any READ or WRITE commands being issued to that bank.

Figure 25: PRECHARGE Command

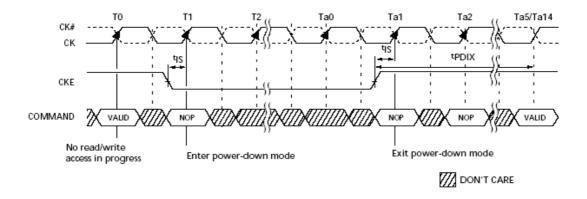

### **POWER-DOWN (CKE Not Active)**

Unlike SDR SDRAMs, GDDR3 SDRAMs require CKE to be active at all times that an access is in progress: from the issuing of a READ or WRITE command until completion of the burst. For READs, a burst completion is defined when the Read Postamble is satisfied; For WRITEs, a burst completion is defined when the write postamble is satisfied. Power-down (shown in Figure26, Power-Down, on page38) is entered when CKE is registered low. If power-down occurs when all banks are idle, this mode is referred to as precharge power-down; if power-down occurs when there is a row active in any banks, this mode is referred to as active power-down. Entering power-down deactivates the input and output buffers, excluding CK, CK# and CKE. For maximum power savings, the user also has the option of disabling the DLL prior to entering power-down. In that case, the DLL must be enabled and reset after exiting power-down, and 5K clock cycles must occur before a READ command can be issued. However, power-down duration is limited by the refresh requirements of the device, so in most applications, the self refresh mode is preferred over the DLL-disabled power-down mode. While in power-down, CKE LOW and a stable clock signal must be maintained at the inputs of the GDDR3 SDRAM, while all other input signals are "Don't Care." The power-down state is synchronously exited when CKE is registered HIGH (in conjunction with a NOP or DESELECT command). A valid executable command may be applied four clock cycles later.

## Figure 26: Power-Down

Table 8: Truth Table - CKE

Notes: 1~4; notes appear below table

| CKEn-1 | CKEn | CURRENT STATE  | COMMANDn          | ACTIONn                    | NOTES |

|--------|------|----------------|-------------------|----------------------------|-------|

| L      | L    | Power-Down     | Х                 | Maintain Power-Down        |       |

| L      | L    | Self Refresh   | Х                 | Maintain Self Refresh      |       |

| L      | Н    | Power-Down     | DESELECT or NOP   | Exit Power-Down            |       |

| L      | Н    | Self Refresh   | DESELECT or NOP   | Exit Self Refresh          | 5     |

| Н      | L    | All Banks Idle | DESELECT or NOP   | Precharge Power-Dwon Entry |       |

| Н      | L    | Bank(s) Active | DESELECT or NOP   | Active Power-Down Entry    |       |

| Н      | L    | All Banks Idle | AUTO REFRESH      | Self Refresh Entry         |       |

| Н      | Н    |                | See Truth Table 3 |                            |       |

#### NOTE:

- 1. CKEn is the logic state of CKE at clock edge n; CKEn-1 was the state of CKE at the previous clock edge.

- 2. Current state is the state of the GDDR3 SDRAM immediately prior to clock edge n.

- 3. COMMANDn is the command registered at clock edge n, and ACTIONn is a result of COMMANDn.

- 4. All states and sequences not shown are illegal or reserved.

- 5. DESELECT or NOP commands should be issued on any clock edges occurring during the tXSR period. A minimum of 5K clock cycles is needed for the DLL to lock before applying a READ command if the DLL was disabled.

### Table 9: Truth Table 3 - Current State Bank n - Command to Bank n

Notes: 1~3; notes appear below table

| CURRENT<br>STATE    | CS# | RAS# | CAS# | WE# | COMMAND/ACTION                                    | NOTES |

|---------------------|-----|------|------|-----|---------------------------------------------------|-------|

| Any                 | Н   | Х    | Х    | Х   | DESELECT (NOP/continue previous operation)        |       |

|                     | L   | Н    | Н    | Н   | NO OPERATION (NOP/continue previous operation)    |       |

|                     | L   | L    | Н    | Н   | ACTIVE (select and activate row)                  |       |

| Idle                | L   | L    | L    | Н   | AUTO REFRESH                                      | 4     |

|                     | L   | L    | L    | L   | LOAD MODE REGISTER                                | 4     |

| Row Active          | L   | Н    | L    | Н   | READ (select column and start READ burst)         | 6     |

|                     | L   | Н    | L    | L   | WRITE (select column and start WRITE burst)       | 6     |

|                     | L   | L    | Н    | L   | PRECHARGE (deactivate row in bank or banks)       | 5     |

| Read                | L   | Н    | L    | Н   | READ (select column and start new READ burst)     | 6     |

| (Auto Pre-          | L   | Н    | L    | L   | WRITE (select column and start WRITE burst)       | 6, 8  |

| charge<br>Disabled) | L   | L    | Н    | L   | PRECHARGE (truncate READ burst , start Precharge) | 5     |

| Write               | L   | Н    | L    | Н   | READ (select column and start READ burst)         | 6, 7  |

| (Auto Pre-          | L   | Н    | L    | L   | WRITE (select column and start new WRITE burst)   | 6     |

| charge<br>Disabled) | L   | L    | Н    | L   | PRECHARGE (truncate WRITE burst, start Precharge) | 5, 7  |

#### NOTE:

- 1. This table applies when CKEn-1 was HIGH and CKEn is HIGH (see Truth Table 2) and after tXSNR has been met (if the previous state was self refresh).

- 2. This table is bank-specific, except where noted (i.e., the current state is for a specific bank and the commands shown are those allowed to be issued to that bank when in that state). Exceptions are covered in the notes below.

- 3. Current state definitions:

- Idle: The bank has been precharged, and tRP has been met.

Row Active: A row in the bank has been activated, and tRCD has been met. No data bursts/accesses and no register accesses are in progress.

Read: A READ burst has been initiated, with auto precharge disabled.

Write: A WRITE burst has been initiated, with auto precharge disabled.

4. The following states must not be interrupted by a command issued to the same bank. COMMAND INHIBIT or NOP commands, or allowable commands to the other bank should be issued on any clock edge occurring during these states. Allowable commands to the other bank are determined by its current state and Table9, and according to Table10. Precharging: Starts with registration of a PRECHARGE command and ends when tRP is met. Once tRP is met, the bank will be in the idle state.

Row Activating: Starts with registration of an ACTIVE command and ends when tRCD is met. Once tRCD is met, the bank will be in the "row active" state.

Read w/Auto-Precharge Enabled: Starts with registration of a READ command with auto precharge enabled and ends when tRP has been met. Once tRP is met, the bank will be in the idle state.

Write w/Auto-Precharge Enabled: Starts with registration of a WRITE command with auto precharge enabled and ends when tRP has been met. Once tRP is met, the bank will be in the idle state.

5. The following states must not be interrupted by any executable command; COMMAND INHIBIT or NOP commands must be applied on each positive clock edge during these states.

Refreshing: Starts with registration of an AUTO REFRESH command and ends when tRC is met. Once tRC is met, the GDDR3 x32 will be in the all banks idle state.

Accessing Mode Register: Starts with registration of a LOAD MODE REGISTER command and ends when tMRD has been met. Once tMRD is met, the GDDR3 x32 will be in the all banks idle state.

Precharging All: Starts with registration of a PRECHARGE ALL command and ends when tRP is met. Once tRP is met, all banks will be in the idle state. READ or WRITE: Starts with the registation of the ACTIVE command and ends the last valid data nibble.

- 6. All states and sequences not shown are illegal or reserved.

- 7. Not bank-specific; requires that all banks are idle, and bursts are not in progress.

- 8. May or may not be bank-specific; if multiple banks are to be precharged, each must be in a valid state for precharging.

- 9. Reads or Writes listed in the Command/Action column include Reads or Writes with auto precharge enabled and Reads or Writes with auto precharge disabled.

- 10. Requires appropriate DM masking.

- 11. A WRITE command may be applied after the completion of the READ burst

Table 10: Truth Table - Current State Bank n - Command to Bank m

Notes: 1~5; notes appear below table

| CURRENT<br>STATE | CS# | RAS# | CAS# | WE# | COMMAND/ACTION                                  | NOTES |

|------------------|-----|------|------|-----|-------------------------------------------------|-------|

| Any              | Н   | Х    | Х    | Х   | DESELECT (NOP/continue previous operation)      |       |

|                  | L   | Н    | Н    | Н   | NO OPERATION (NOP/continue previous operation)  |       |

| Idle             | Х   | Х    | Х    | Х   | Any Command Otherwise Allowed to Bank m         |       |

| Row Activat-     | L   | L    | Н    | Н   | ACTIVE (select and activate row)                |       |

| ing, Active, or  | L   | Н    | L    | Н   | READ (select column and start READ burst)       | 6     |

| Precharging      | L   | Н    | L    | L   | WRITE (select column and start WRITE burst)     | 6     |

|                  | L   | L    | Н    | L   | PRECHARGE                                       |       |

| Read (Auto       | L   | L    | Н    | Н   | ACTIVE (select and activate row)                |       |

| Precharge Dis-   | L   | Н    | L    | Н   | READ (select column and start new READ burst)   | 6     |

| abled)           | L   | Н    | L    | L   | WRITE (select column and start WRITE burst)     | 6     |

|                  | L   | L    | Н    | L   | PRECHARGE                                       |       |

| Write (Auto      | L   | L    | Н    | Н   | ACTIVE (select and activate row)                |       |

| Precharge Dis-   | L   | Н    | L    | Н   | READ (select column and start READ burst)       | 6, 7  |

| abled)           | L   | Н    | L    | L   | WRITE (select column and start new WRITE burst) | 6     |

|                  | L   | L    | Н    | L   | PRECHARGE                                       |       |

| Read(With        | L   | L    | Н    | Н   | ACTIVE (select and activate row)                |       |

| Auto Pre-        | L   | Н    | L    | Н   | READ (select column and start new READ burst)   | 6     |

| charge)          | L   | Н    | L    | L   | WRITE (select column and start WRITE burst)     | 6     |

|                  | L   | L    | Н    | L   | PRECHARGE                                       |       |

| Write(With       | L   | L    | Н    | Н   | ACTIVE (select and activate row)                |       |

| Auto Pre-        | L   | Н    | L    | Н   | READ (select column and start READ burst)       | 6     |

| charge)          | L   | Н    | L    | L   | WRITE (select column and start new WRITE burst) | 6     |

|                  | L   | L    | Н    | L   | PRECHARGE                                       |       |

#### NOTE:

- 1. This table applies when CKEn-1 was HIGH and CKEn is HIGH (see Table9) and after tXSNR has been met (if the previous state was self refresh).

- 2. This table describes alternate bank operation, except where noted (i.e., the current state is for bank n and the commands shown are those allowed to be issued to bank m, assuming that bank m is in such a state that the given command is allowable).

Exceptions are covered in the notes below.

- 3. Current state definitions:

Idle: The bank has been precharged, and tRP has been met.