MT9E001: 1/2.5-Inch 8-Mp Digital Image Sensor

# 1/2.5-Inch CMOS Digital Image Sensor

### MT9E001

Refer to the latest MT9E001 data sheet on Micron's Web site: www.mircon.com/imaging

### **Features**

- DigitalClarity<sup>®</sup> CMOS imaging technology

- Superior low-light performance

- · Low dark current

- Simple two-wire serial interface

- Auto black level calibration

- Support for external mechanical shutter

- Support for external LED or Xenon flash

- High frame rate preview mode with arbitrary downsize scaling from maximum resolution

- Programmable controls: gain, frame size/rate, exposure, left-right and top-bottom image reversal, window size, and panning

- Data interface: parallel

- On-chip phase-locked loop (PLL)

- Bayer pattern down-size scaler

- Four channel shading correction (SC)

## **Applications**

- Digital still cameras

- Cellular phones

**Table 1: Key Performance Parameters**

| Parar                | neter           | Value                                                                  |  |  |  |

|----------------------|-----------------|------------------------------------------------------------------------|--|--|--|

| Optical format       |                 | 1/2.5-inch (4:3)                                                       |  |  |  |

| Full resolution      |                 | 3,264 x 2,448 pixels                                                   |  |  |  |

| Pixel size           |                 | 1.75µm x 1.75µm                                                        |  |  |  |

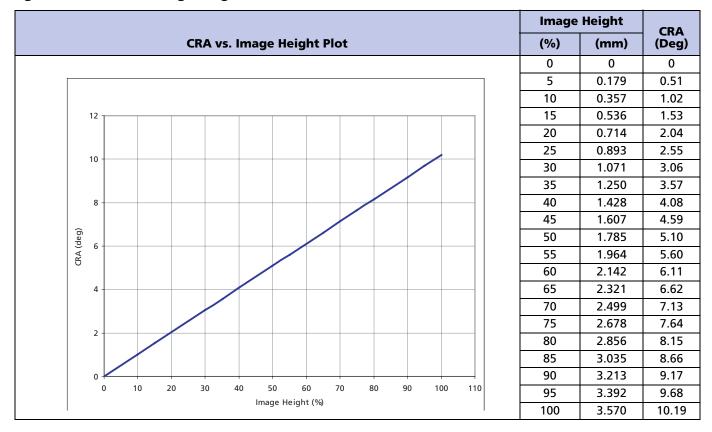

| Chief ray ang        | le              | 10.19 maximum                                                          |  |  |  |

| Color filter ar      | ray             | RGB Bayer pattern                                                      |  |  |  |

| Shutter type         |                 | Electronic rolling shutter<br>(ERS) with global reset<br>release (GRR) |  |  |  |

| Input clock from     |                 | 6–48 MHz                                                               |  |  |  |

| Maximum dat<br>clock | a rate/master   | 96 Mbps                                                                |  |  |  |

| Frame rate           | Full resolution | 11 fps                                                                 |  |  |  |

|                      | Video mode      | 30 fps                                                                 |  |  |  |

|                      | Analog          | 2.4–3.1V (2.8V nominal)                                                |  |  |  |

| Supply               | Digital         | 1.7–1.9V (1.8V nominal)                                                |  |  |  |

| voltage              | I/O             | 1.8 or 2.8V                                                            |  |  |  |

|                      | PLL             | 2.4–3.1V (2.8V nominal)                                                |  |  |  |

| ADC resolution       | n               | 12-bit                                                                 |  |  |  |

| Responsivity         |                 | 0.3 V/lux-sec (at 550nm)                                               |  |  |  |

|                      |                 | (preliminary)                                                          |  |  |  |

| Dynamic rang         | je              | 70dB (preliminary)                                                     |  |  |  |

| SNRMAX               |                 | 38.9dB (preliminary)                                                   |  |  |  |

|                      | Full            | 650mW (typical)                                                        |  |  |  |

| Power resolution     |                 |                                                                        |  |  |  |

| consumption          |                 | 594mW (typical)                                                        |  |  |  |

|                      | Standby         | 45μW (typical, EXTCLK disabled)                                        |  |  |  |

| Operating ter        | nperature       | -30°C to +70°C (at junction)                                           |  |  |  |

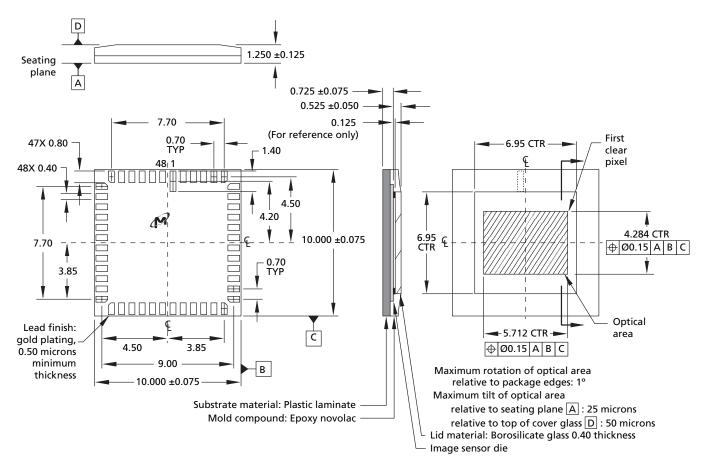

| Package              |                 | 48-pin iLCC                                                            |  |  |  |

## **Ordering Information**

**Table 2: Available Part Numbers**

| Part Number   | Description |  |

|---------------|-------------|--|

| MT9E001I12STC | 48-pin iLCC |  |

## MT9E001: 1/2.5-Inch 8-Mp Digital Image Sensor Table of Contents

## **Table of Contents**

| Features                                           | 1  |

|----------------------------------------------------|----|

| Applications                                       |    |

| Ordering Information                               |    |

| General Description                                |    |

| Signal Description                                 |    |

| Typical Connections                                |    |

| Architecture Overview                              |    |

| Sensor Core Description                            |    |

| Pixel Array                                        |    |

| Default Readout Order                              |    |

| Analog Processing                                  |    |

| Analog Readout Channel                             |    |

| Timing and Control                                 |    |

| Analog Gain Options                                |    |

| Using Per-color or Global Gain Control             |    |

| SMIA Gain Model                                    |    |

|                                                    |    |

| Micron Imaging Gain Model                          |    |

| Gain Code Mapping                                  |    |

| Digital Gain                                       |    |

| Pedestal                                           |    |

| Integration Time                                   |    |

| PLL                                                |    |

| PLL Generated Master Clock.                        |    |

| PLL Setup                                          |    |

| Readout Options                                    |    |

| Window Size                                        |    |

| Pixel Border                                       |    |

| Column Readout Limitation                          |    |

| Readout Modes                                      |    |

| Horizontal Mirror                                  |    |

| Vertical Flip                                      |    |

| Column and Row Skip                                |    |

| Programming Restrictions when Subsampling          |    |

| Binning                                            |    |

| Binning Limitations                                | 25 |

| Shading Correction (SC)                            |    |

| The Correction Function                            |    |

| Output Data Format (Parallel Pixel Data Interface) | 26 |

| Output Data Timing (Parallel Pixel Data Interface) | 27 |

| General Purpose Inputs                             | 29 |

| Parallel Pixel Data Interface                      | 29 |

| Output Enable Control                              |    |

| Trigger Control                                    | 29 |

| Streaming/Standby Control                          | 30 |

| Operational Modes                                  |    |

| Snapshot and Flash                                 |    |

| Low Power Mode                                     |    |

| Test Patterns                                      |    |

| Fwo-Wire Serial Interface                          |    |

| Protocol                                           |    |

| Start Condition.                                   |    |

## MT9E001: 1/2.5-Inch 8-Mp Digital Image Sensor Table of Contents

| Stop Condition                               | 33 |

|----------------------------------------------|----|

| Data Transfer                                | 33 |

| Slave Address/Data Direction Byte            | 33 |

| Message Byte                                 | 34 |

| Acknowledge Bit                              | 34 |

| No-Acknowledge Bit                           | 34 |

| Typical Serial Transfer                      | 34 |

| Single Read from Random Location             |    |

| Single Read from Current Location            |    |

| Sequential Read, Start from Random Location  | 35 |

| Sequential Read, Start from Current Location | 36 |

| Single Write to Random Location              | 36 |

| Sequential Write, Start at Random Location   | 36 |

| Registers                                    | 37 |

| Register Notation                            | 37 |

| Register Aliases                             | 37 |

| Bit Fields                                   | 37 |

| Bit Field Aliases                            | 38 |

| Byte Ordering                                | 38 |

| Address Alignment                            | 38 |

| Bit Representation                           | 38 |

| Data Format                                  | 38 |

| Register Behavior                            | 38 |

| Double-Buffered Registers                    | 39 |

| Using grouped_parameter_hold                 | 39 |

| Bad Frames                                   |    |

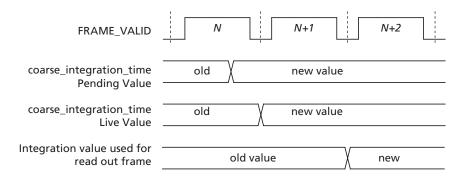

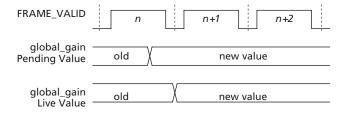

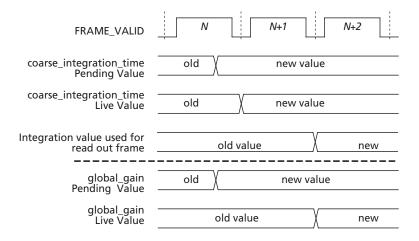

| Changes to Integration Time                  | 40 |

| Changes to Gain Settings                     | 40 |

| Embedded Data                                | 41 |

| Register List and Default Value              | 42 |

| Register Description                         | 55 |

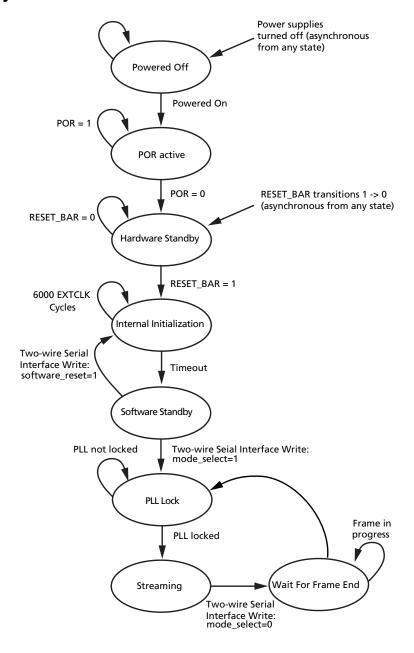

| System States                                | 85 |

| Spectral Characteristics                     | 87 |

| Fiming Specifications                        | 88 |

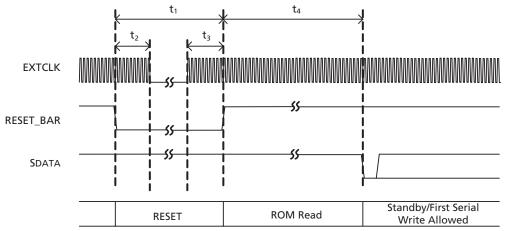

| Power-up                                     | 88 |

| Reset                                        | 88 |

| Hard Reset                                   |    |

| Soft Reset                                   | 88 |

| Signal State during Reset                    | 88 |

| Electrical Specifications                    |    |

| I/O Timing                                   |    |

| Power on Reset (POR)                         |    |

| Package Dimensions                           | 95 |

| Revision History.                            | 96 |

## MT9E001: 1/2.5-Inch 8-Mp Digital Image Sensor List of Figures

## **List of Figures**

| Figure 1:  | 48-Pin ILCC 10x10 Package Pinout Diagram (Top View)   |    |

|------------|-------------------------------------------------------|----|

| Figure 2:  | Typical Configuration (connection)                    | .9 |

| Figure 3:  | Block Diagram                                         |    |

| Figure 4:  | Pixel Color Pattern Detail (Top Right Corner)         | 12 |

| Figure 5:  | Imaging a Scene                                       | 12 |

| Figure 6:  | Clocking Structure                                    | 15 |

| Figure 7:  | 8 Pixels in Normal and Column Mirror Readout Modes    | 18 |

| Figure 8:  | 6 Rows in Normal and Row Mirror Readout Modes         | 19 |

| Figure 9:  | Effect of x_odd_inc=3 on Readout Sequence             |    |

| Figure 10: | Effect of x_odd_inc=7 on Readout Sequence             | 19 |

| Figure 11: | Pixel Readout (no skipping, x_odd_inc=1, y_odd_inc=1) | 20 |

| Figure 12: | Pixel Readout (x_odd_inc=3, y_odd_inc=1)              | 20 |

| Figure 13: | Pixel Readout (x_odd_inc=1, y_odd_inc=3)              |    |

| Figure 14: | Pixel Readout (x_odd_inc=3, y_odd_inc=3)              | 21 |

| Figure 15: | Pixel Readout (x_odd_inc=3, y_odd_inc=1, x_bin=1)     | 24 |

| Figure 16: | Pixel Readout (x_odd_inc=3, y_odd_inc=3, x_ybin=1)    |    |

| Figure 17: | Pixel Readout (x_odd_inc=7, y_odd_inc=7, x_ybin=1)    | 25 |

| Figure 18: | Pixel Data Timing Example                             | 27 |

| Figure 19: | Pixel Data Timing Example                             | 27 |

| Figure 20: | Row Timing and FRAME_VALID/LINE_VALID Signals         | 28 |

| Figure 21: | Xenon Flash Enabled                                   | 31 |

| Figure 22: | LED Flash Enabled                                     |    |

| Figure 23: | LED Flash Enabled Following Forced Restart            |    |

| Figure 24: | Single Read from Random Location                      |    |

| Figure 25: | Single Read from Current Location                     | 35 |

| Figure 26: | Sequential Read, Start from Random Location           |    |

| Figure 27: | Sequential Read, Start from Current Location          | 36 |

| Figure 28: | Single Write to Random Location                       |    |

| Figure 29: | Sequential Write, Start at Random Location            |    |

| Figure 30: | Changes to Integration Time                           | 40 |

| Figure 31: | Changes to Gain                                       |    |

| Figure 32: | Changes to Gain and Integration Time                  |    |

| Figure 33: | Sensor System States                                  |    |

| Figure 34: | CRA vs. Image Height                                  |    |

| Figure 35: | Hard Reset                                            | 88 |

| Figure 36: | I/O TIming                                            | 93 |

| Figure 37: | Power On Reset                                        |    |

| Figure 38: | 48-Pin ILCC Package Outline Drawing                   | 95 |

## MT9E001: 1/2.5-Inch 8-Mp Digital Image Sensor List of Tables

## **List of Tables**

| Table 1:  | Key Performance Parameters                          | 1  |

|-----------|-----------------------------------------------------|----|

| Table 2:  | Available Part Numbers                              | 1  |

| Table 3:  | Signal Description                                  | 7  |

| Table 4:  | Recommended Gain Settings                           | 14 |

| Table 5:  | Frequency Parameters                                | 17 |

| Table 6:  | Row Address Sequencing                              | 23 |

| Table 7:  | Register Adjustments Required for Binning Mode      | 25 |

| Table 8:  | Row Timing Parameters                               | 28 |

| Table 9:  | Output Enable Control                               |    |

| Table 10: | Trigger Control                                     | 30 |

| Table 11: | Streaming/STANDBY                                   | 30 |

| Table 12: | Test Patterns                                       | 32 |

| Table 13: | Address Space Regions                               | 37 |

| Table 14: | Data Formats                                        | 38 |

| Table 15: | SMIA Configuration                                  | 42 |

| Table 16: | 1: SMIA Parameter Limits                            | 44 |

| Table 17: | 3: Manufacturer Specific                            | 46 |

| Table 18: | 0: SMIA Configuration                               | 55 |

| Table 19: | 1: SMIA Parameter Limits                            | 60 |

| Table 20: | 3: Manufacturer Specific                            | 64 |

| Table 21: | RESET_BAR and PLL in System States                  | 86 |

| Table 22: | Signal State During Reset                           | 89 |

| Table 23: | Electrical Characteristics and Operating Conditions | 90 |

| Table 24: | I/O Parameters                                      | 92 |

| Table 25: | Typical Power                                       | 92 |

| Table 26: | I/O Timing                                          | 93 |

| Table 27: | POR Characterization                                | 94 |

## **General Description**

The Micron  $^{\circledR}$  Imaging MT9E001 is a 1/2.5-inch format CMOS active-pixel digital image sensor with a pixel array of 3,264H x 2,448V. It incorporates sophisticated on-chip camera functions such as windowing, mirroring, binning and skip modes, and snapshot mode. It is programmable through a simple two-wire serial interface and has very low power consumption.

The MT9E001 digital image sensor features DigitalClarity<sup>®</sup> technology—Micron's breakthrough low-noise CMOS imaging technology that achieves near CCD image quality (based on signal-to-noise ratio and low-light sensitivity) while maintaining the inherent size, cost, power consumption, and integration advantages of CMOS.

## **Signal Description**

Table 3 provides the signal descriptions for the MT9E001.

## **Table 3: Signal Description**

| Name        | Туре   | Description                                                                                                                                                                                                                              |  |  |  |  |  |

|-------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| SCLK        | Input  | Serial clock for access to control and status registers.                                                                                                                                                                                 |  |  |  |  |  |

| TEST2       | Input  | eserved for factory use. Tie to digital ground during normal operation.                                                                                                                                                                  |  |  |  |  |  |

| RESET_BAR   | Input  | synchronous active LOW reset. When asserted, data output stops and all internal egister are restored to their factory default settings.                                                                                                  |  |  |  |  |  |

| EXTCLK      | Input  | Master clock input; PLL input clock, 6–48 MHz.                                                                                                                                                                                           |  |  |  |  |  |

| TEST        | Input  | Reserved for factory use. Tie to digital ground during normal operation.                                                                                                                                                                 |  |  |  |  |  |

| GPI[3:0]    | Input  | General purpose inputs. After reset, these pads are powered down by default (it is not secessary to bond to these pads). Any of these pads can be configured for hardware ontrol of SADDR, output enable, and shutter trigger functions. |  |  |  |  |  |

| PIXCLK      | Output | Pixel clock. Used to qualify the LINE_VALID, FRAME_VALID and DOUT[11:0] outputs.                                                                                                                                                         |  |  |  |  |  |

| FRAME_VALID | Output | FRAME_VALID output. Qualified by PIXCLK.                                                                                                                                                                                                 |  |  |  |  |  |

| LINE_VALID  | Output | INE_VALID output. Qualified by PIXCLK.                                                                                                                                                                                                   |  |  |  |  |  |

| SHUTTER     | Output | ontrol for external mechanical shutter.                                                                                                                                                                                                  |  |  |  |  |  |

| FLASH       | Output | lash output. Synchronization pulse for external light source.                                                                                                                                                                            |  |  |  |  |  |

| Douт[11:0]  | Output | welve-bit image data output.                                                                                                                                                                                                             |  |  |  |  |  |

| Sdata       | I/O    | Serial data.                                                                                                                                                                                                                             |  |  |  |  |  |

| VDD         | Supply | Digital power (1.8V).                                                                                                                                                                                                                    |  |  |  |  |  |

| VAAPIX      | Supply | Pixel array power (2.8V).                                                                                                                                                                                                                |  |  |  |  |  |

| Vaa         | Supply | Analog power (2.8V).                                                                                                                                                                                                                     |  |  |  |  |  |

| VddPLL      | Supply | PLL power (2.8V).                                                                                                                                                                                                                        |  |  |  |  |  |

| VDDIO       | Supply | I/O power supply (1.8V or 2.8V).                                                                                                                                                                                                         |  |  |  |  |  |

| DGND        | Supply | Digital, I/O, and PLL ground.                                                                                                                                                                                                            |  |  |  |  |  |

| AGND        | Supply | Analog ground.                                                                                                                                                                                                                           |  |  |  |  |  |

## MT9E001: 1/2.5-Inch 8-Mp Digital Image Sensor Signal Description

Figure 1: 48-Pin ILCC 10x10 Package Pinout Diagram (Top View)

### MT9E001: 1/2.5-Inch 8-Mp Digital Image Sensor Typical Connections

## **Typical Connections**

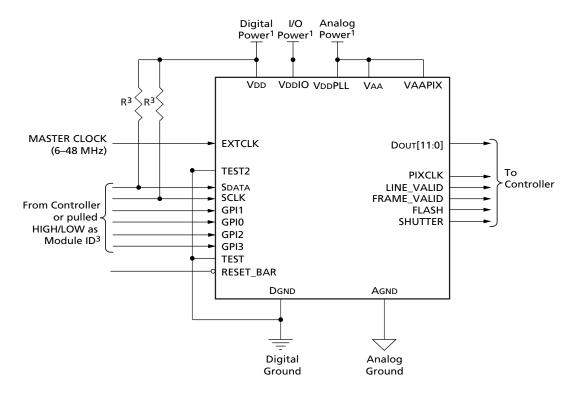

Figure 2 shows typical MT9E001 device connections. For low-noise operation, the MT9E001 requires separate power supplies for analog and digital. Incoming digital and analog ground conductors can be tied together next to the die. Both power supply rails should be decoupled to ground using capacitors as close as possible to the die. The use of inductance filters is not recommended on the power supplies or output signals.

The MT9E001 also supports different digital core (VDD/DGND) and I/O power (VDDIO/DGND) power domains that can be at different voltages. The PLL requires a clean power source (VDDPLL).

Figure 2: Typical Configuration (connection)

Notes: 1. Connection diagram shows only one of many possible variations for this sensor.

- 2. The GPI pads can configure multiple features for the sensor.

- 3. Recommended resistor value is  $1.5 \text{K}\Omega$  for the two-wire serial interface RPULL-UP; however, greater value may be used for slower transmission speed.

- 4. All inputs must be configured with VDDIO.

- 5. VAA and VAAPIX must be tied together.

## MT9E001: 1/2.5-Inch 8-Mp Digital Image Sensor Architecture Overview

## **Architecture Overview**

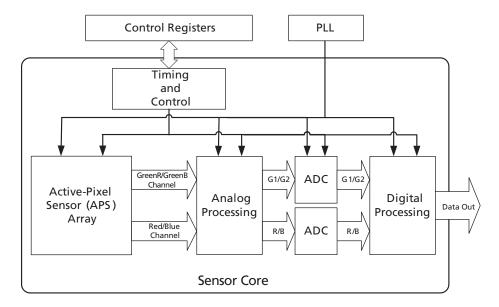

The MT9E001 is a progressive-scan sensor that generates a stream of pixel data at a constant frame rate. It uses an on-chip PLL to generate all internal clocks from a single master input clock running between 6 MHz and 48 MHz. The maximum pixel rate is 96 Mbps, corresponding to a physical pixel clock rate of 96 MHz. Figure 3 shows a block diagram of the sensor.

Figure 3: Block Diagram

## **Sensor Core Description**

The core of the sensor is an active-pixel array. The timing and control circuitry sequences through the rows of the array, resetting and then reading each row in turn. In the time interval between resetting a row and reading that row, the pixels in the row integrate incident light. The exposure is controlled by varying the integration. Once a row has been read, the data from the columns is sequenced through an analog signal chain (providing offset correction and gain), and then through an ADC. The output from the ADC is a 12-bit value for each pixel in the array. The ADC output passes through a digital processing signal chain (providing further data path corrections and applying digital gain).

The pixel array contains optically active and light-shielded (black) pixels. The black pixels are used to provide data for on-chip offset-correction algorithms (black level control).

The sensor contains a set of control and status registers that can be used to control many aspects of the sensor behavior including the frame size, exposure, and gain setting. These registers can be accessed through a two-wire serial interface.

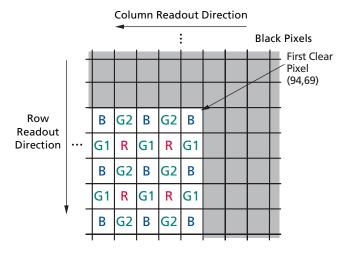

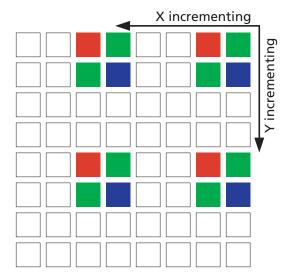

The output from the sensor is a Bayer pattern: alternate rows are a sequence of either green/red pixels or blue/green pixels. The offset and gain stages of the analog signal chain provide per-color control of the pixel data.

The control registers, timing and control and digital processing functions shown in Figure 3 on page 10 are partitioned into two logical parts:

- A sensor core which provides array control and data path corrections. The output of the sensor core is 12-bit parallel pixel data stream qualified by an output data clock (PIXCLK), together with LINE VALID and FRAME VALID signals.

- Additional functionality is required to support the SMIA standard. This includes a horizontal and vertical image scaler, a limiter, a data compressor, an output FIFO.

A flash output strobe is provided to allow an external Xenon or LED light source to synchronize with the sensor exposure time. Additional I/O signals support the provision of an external mechanical shutter.

## **Pixel Array**

The MT9E001 image sensor array consists of a 3,382-column by 2,540-row matrix of pixels addressed by column and row. The address (column 0, row 0) represents the upper-left corner of the entire array as oriented in the output image, which is the upper-right pixel, when looking at the chip.

The active region in the center of the array consists of a 3,264-columns by 2,448-rows representing the default output image. It is surrounded by a boundary region (also active), and a border of shielded dark pixels. The boundary region can be used to avoid edge effects when doing color processing to achieve a 3,264 x 2,448 result image.

The 4-pixel border on each edge can be enabled by reprogramming the x\_addr\_start, y\_addr\_start, x\_addr\_end and y\_addr\_end registers.

Figure 4: Pixel Color Pattern Detail (Top Right Corner)

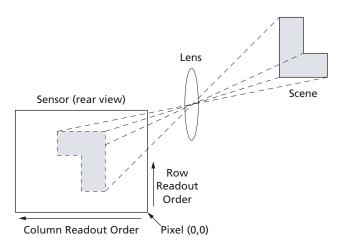

## **Default Readout Order**

Figure 5: Imaging a Scene

## **Analog Processing**

### **Analog Readout Channel**

The sensor core features two identical analog readout channels, as shown in Figure 3 on page 10. The readout channel consists of two gain stages, a sample-and-hold stage with black level calibration capability, and two12-bit ADCs.

## **Timing and Control**

### **Analog Gain Options**

The MT9E001 provides two mechanisms for setting the analog gain. The first uses the SMIA gain model; the second uses the traditional Micron Imaging gain model. The following sections describe both models, the mapping between the models, and the operation of the per-color and global gain control. Use of high gains can result in reduced image quality by introducing noise and by amplifying image defects or artifacts.

### **Using Per-color or Global Gain Control**

The read-only analogue\_gain\_capability register returns a value of "1," indicating that the MT9E001 provides per-color gain control. However, the MT9E001 also provides the option of global gain control. Per-color and global gain control can be used interchangeably. A write to a global gain register is aliased as a write of the same data to the four associated color-dependent gain registers. A read from a global gain register is aliased to a read of the associated color-dependent gain registers.

The read/write gain\_mode register required by SMIA has no defined function in the SMIA specification. In the MT9E001 this register has no side-effects on the operation of the gain; per-color and global gain control can be used interchangeably regardless of the state of the gain\_mode register.

#### **SMIA Gain Model**

The SMIA gain model uses the following registers to set the analog gain:

- · analogue\_gain\_code\_global

- analogue\_gain\_code\_green1

- analogue\_gain\_code\_red

- · analogue\_gain\_code\_blue

- analogue\_gain\_code\_green2

The SMIA gain model requires a uniform step size between all gain settings. The analog gain is given by:

$$gain = \frac{analogue\_gain\_m0 \ x \ analogue\_gain\_code}{analogue\_gain\_c1} = \frac{analogue\_gain\_code\_ < color >}{8} \tag{EQ 1}$$

### **Micron Imaging Gain Model**

The Micron Imaging gain model uses the following registers to set the analog gain:

- · global\_gain

- · greenR gain

- red\_gain

- · blue gain

- greenB\_gain

This gain model maps directly to the control settings applied to the gain stages of the analog signal chain. This provides a 7-bit gain stage and two2X gain stages. As a result, the step size varies depending upon whether the 2X gain stages are enabled. The analog gain is given by:

$$gain = (\langle color \rangle \_gain[8] + 1) \times (\langle color \rangle \_gain[7] + 1) \times \frac{\langle color \rangle \_gain[6:0]}{32}$$

(EQ 2)

As a result of the 2X gain stages, many of the possible gain settings can be achieved in two different ways. For example, red\_gain=0x02A0 provides the same gain as red\_gain=0x0240 and red\_gain=0x0320. The first example uses the first 2X gain stage, the second example uses no 2X gain stage and the third example uses the second 2X gain stage. In all cases, the preferred setting is the setting that enables the first 2X gain stage and not the last 2X gain stage, since this will result in lower noise. The recommended sequence is shown in Table 4.

### **Table 4: Recommended Gain Settings**

| Desired Gain | Recommended Gain Register Setting |

|--------------|-----------------------------------|

| 1–1.969      | 0x0220–0x023F                     |

| 2–7.9375     | 0x02A0-0x02FF                     |

| 8–15.875     | 0x03C0-0x03FF                     |

### **Gain Code Mapping**

The Micron Imaging gain model maps directly to the underlying structure of the gain stages in the analog signal chain. When the SMIA gain model is used, gain codes are translated into equivalent settings in the Micron Imaging gain model.

When the SMIA gain model is in use and values have been written to the analogue\_gain\_code\_<color> registers, the associated value in the Micron Imaging gain model can be read from the SMIA associated <color>\_gain register. In cases where there is more than one possible mapping, the recommended gain register setting is followed, in order to provide the mapping with the lowest noise.

When the Micron Imaging gain model is in use and values have been written to the gain\_<color> registers, data read from the associated analogue\_gain\_code\_<color> register is UNDEFINED. The reason for this is that many of the gain codes available in the Micron Imaging gain model have no corresponding value in the SMIA gain model.

The result of this is that the two gain models can be used interchangeably but, having written gains through one set of registers, those gains should be read back through the same set of registers.

## **Digital Gain**

Integer digital gains in the range 1–7 can be programmed.

As gain is increased, image quality degrades due to the amplification of image defects.

### **Pedestal**

This block adds the value from R0x301E (data\_pedestal\_) to the incoming pixel value. The data\_pedestal register is read-only by default but can be configured to be read/write by clearing the lock\_reg bit in R0x301A-B. The only way to disable the effect of the pedestal is to set the register to "0."

## **Integration Time**

The integration (exposure) time of the sensor is controlled by the fine\_integration\_time and coarse\_integration\_time registers.

The limits for the fine integration time are defined by:

(EQ 3)

$fine\_integration\_time\_min \le fine\_integration\_time \le (line\_length\_pck-fine\_integration\_time\_max\_margin)$

The limits for the coarse integration time are defined by:

(EQ 4)

$coarse\_integration\_time\_min \le coarse\_integration\_time \le (frame\_length\_lines-coarse\_integration\_time\_max\_margin)$

The actual integration time is given by:

(EQ 5)

$$integration\_time = \frac{\left(\left(coarse\_integration\_time \times line\_length\_pck\right) + fine\_integration\_time\right)}{vt\_pix\_clk\_freq\_mhz/10^6}$$

If the integration time is set larger than the frame time, the frame time will automatically be extended to accommodate the larger integration time.

When the coarse\_integration\_time and fine\_integration\_time are changed simultaneously, and the change to coarse integration time has been an increase, the first output frame will be non uniformly integrated.

### **PLL**

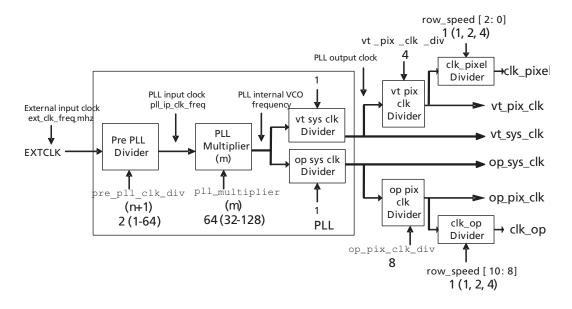

The sensor contains a PLL for timing generation and control. The PLL contains a prescaler to divide the input clock applied on EXTCLK, a VCO to multiply the prescaler output, and a set of dividers to generate the output clocks. The clocking structure is shown in Figure 6.

Figure 6: Clocking Structure

Figure 6 on page 15 shows the different clocks and (in courier font) the names of the registers that contain or are used to control their values. It also shows the default setting for each divider/multiplier control register, and the range of legal values for each divider/multiplier control register. The vt and op sys clk Divider is hardwired in the design.

From the diagram, the clock frequencies can be calculated as follows:

Internal pixel clock used to readout the pixel array:

(EQ 6)

$$clk\_pixel\_freq\_mhz = \frac{ext\_clk\_freq\_mhz \ x \ pll\_multiplier}{pre\_pll\_clk\_div \ x \ vt\_pix\_clk\_div \ x \ row\_speed \ [2:0]} = \frac{24 \ MHz \ x \ 64}{2x4x1} = 192 \ MHz$$

External pixel clock used to output the data:

(EQ 7)

$$clk\_op\_freq\_mhz = \frac{ext\_clk\_freq\_mhz \ x \ pll\_multiplier}{pre\_pll\_clk\_div \ x \ op\_pix\_clk\_div \ x \ row\_speed \ [10:8]} = \frac{24 \ MHz \ x \ 64}{2x8x1} = 96 \ MHz$$

Internal master clock:

$$op\_pix\_clk\_freq\_mhz = \frac{ext\_clk\_freq\_mhz \times pll\_multiplier}{pre\_pll\_clk\_div \times 8} = \frac{24 \text{ MHz } \times 64}{2 \times 8} = 96 \text{ MHz}$$

(EQ 8)

The parameter limit register space contains registers that declare the minimum and maximum allowable values for:

- The frequency allowable on each clock.

- The divisors that are used to control each clock.

The following factors determine what are valid values, or combinations of valid values, for the divider/multiplier control registers:

- The minimum/maximum frequency limits for the associated clock must be met. pll\_ip\_clk\_freq must be in the range 2–24 MHz. Higher frequencies are preferred. PLL internal VCO frequency must be in the range 384–768 MHz.

- The minimum/maximum value for the divider/multiplier must be met.

Range for m: 32–128.

Range for n: 0-63. Range for (n + 1): 1-64.

- The op\_pix\_clk must never run faster than the vt\_pix\_clk to ensure that the output data stream is contiguous.

- Given the maximum programmed line length, the minimum blanking time, the maximum image width, the available PLL divisor/multiplier values, and the require-

ment that the output line time (including the necessary blanking) must be output in a time equal to or less than the time defined by line\_length\_pck.

Although the PLL VCO input frequency range is advertised as 6 MHz–48 MHz, superior performance is obtained by keeping the VCO input frequency as high as possible.

The usage of the output clocks is shown below:

- clk\_pixel is used by the sensor core to control the timing of the pixel array. The sensor core produces one 12-bit pixel each vt\_pix\_clk period. The line length (line\_length\_pck) and fine integration time (fine\_integration\_time) are controlled in increments of the clk\_pixel period.

- clk\_op is used to load parallel pixel data from the output FIFO. The output FIFO generates one pixel each op\_pix\_clk period.

#### **PLL Generated Master Clock**

#### **PLL Setup**

The PLL divisors should be programmed while the sensor is in the software standby state. The PLL is enabled by entering the STREAMING state. STREAMING state will be entered after the VCO lock time.

The VCO lock time is 100µs (typical), 1ms (maximum).

The effect of programming the PLL divisors whilst the sensor is in the streaming state is UNDEFINED.

**Table 5: Frequency Parameters**

| Frequency        | Equation                              | Min (MHz) | Max (MHz) |

|------------------|---------------------------------------|-----------|-----------|

| †IN              | _                                     | 6         | 48        |

| <sup>f</sup> PFD | <sup>f</sup> extclk /(pll_n+1)        | 2         | 24        |

| †VCO             | <sup>†</sup> extclk * pll_m/(pll_n+1) | 384       | 768       |

### **Readout Options**

The sensor core supports different readout options to modify the output image. The readout can be limited to a specific window of the original pixel array.

For preview modes, the sensor core supports both skipping and pixel binning in x and y directions.

By changing the readout direction, the image can be flipped in the vertical and/or mirrored in the horizontal direction.

#### **Window Size**

The sequencing of the pixel array is controlled by the x\_addr\_start, y\_addr\_start, x\_addr\_end and y\_addr\_end registers. The image output from the sensor core data path is controlled by these registers. The output image size is controlled by the x\_output\_size and y\_output\_size registers.

### **Pixel Border**

The default settings of the sensor provide a 3264 x 2448 image. A border of up to 4 pixels on each edge can be enabled by reprogramming the x\_addr\_start, y\_addr\_start, x\_addr\_end and y\_addr\_end registers and then adjusting the x\_output\_size and y\_output\_size registers accordingly.

#### **Column Readout Limitation**

The MT9E001 has limitations on the allowed values of x addr start and x addr end.

x\_addr\_start needs to be a multiple of 8 in normal mode, 16 in 2X skip or binning mode and 32 in 4X skip or binning mode. Similarly x\_addr\_end needs to be set so the width of the window read out after taking subsampling mode into account is a multiple of 8.

#### **Readout Modes**

#### **Horizontal Mirror**

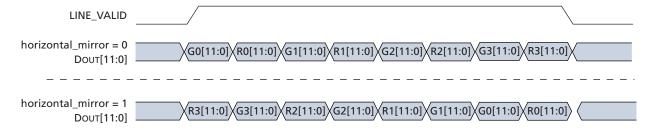

When the horizontal\_mirror bit (R0x3040[0]) is set in the read mode register, the order of pixel readout within a row is reversed, so that readout starts from x\_addr\_end and ends at x\_addr\_start. Figure 7 shows a sequence of 6 pixels being read out with horizontal\_mirror=0 and horizontal\_mirror=1. Changing horizontal\_mirror causes the Bayer order of the output image to change; the new Bayer order is reflected in the value of the pixel\_order register.

Figure 7: 8 Pixels in Normal and Column Mirror Readout Modes

### **Vertical Flip**

When the vertical\_flip bit is set in the image\_orientation register, the order in which pixel rows are read out is reversed, so that row readout starts from y\_addr\_end and ends at y\_addr\_start. Figure 8 on page 19 shows a sequence of six rows being read out with vertical\_flip= 0 and vertical\_flip=1. Changing vertical\_flip causes the Bayer order of the output image to change; the new order is reflected in the value of the pixel\_order register.

Figure 8: 6 Rows in Normal and Row Mirror Readout Modes

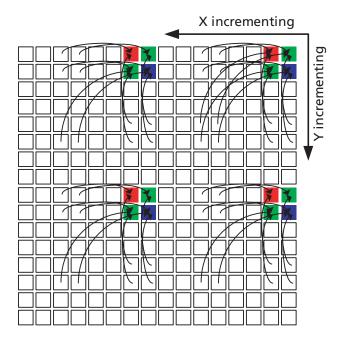

### **Column and Row Skip**

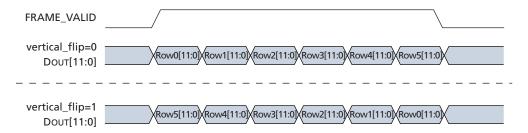

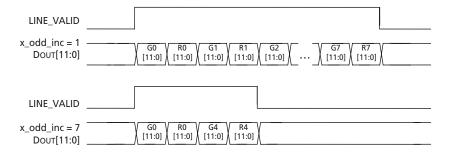

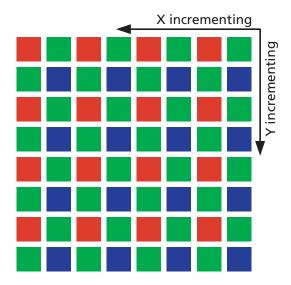

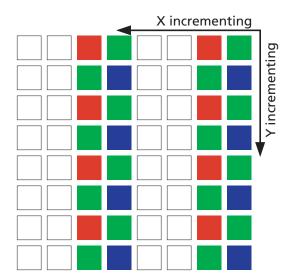

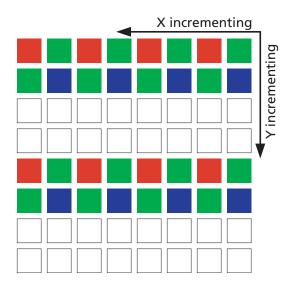

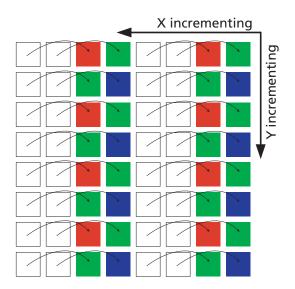

The sensor supports subsampling. Subsampling reduces the amount of data processed by the analogue signal chain in the sensor and thereby allows the frame rate to be increased. Subsampling is enabled by changing x\_odd\_inc and/or y\_odd\_inc. Values of 1, 3 and 7 are supported. Setting both of these variables to 3 reduces the amount of row and column data processed and is equivalent to the skip2 readout mode provided by earlier Micron Imaging sensors. The following figure shows a sequence of 8 columns being read out with x\_odd\_inc=3 and y\_odd\_inc=1.

Figure 9: Effect of x\_odd\_inc=3 on Readout Sequence

Figure 10: Effect of x odd inc=7 on Readout Sequence

A 1/16 reduction in resolution is achieved by setting both x\_odd\_inc and y\_odd\_inc to 7. This is equivalent to skip4 readout mode provided by earlier Micron Imaging sensors. Figure 10 on page 19 shows a sequence of 16 columns being read out with x\_odd\_inc=7 and y\_odd\_inc=1.

The following waveform shows a sequence of data being read out with x\_odd\_inc=3 and y\_odd\_inc=1. The effect of the different subsampling settings on the pixel array readout is shown in Figures 11 through Figure 13 on page 21.

Figure 11: Pixel Readout (no skipping, x\_odd\_inc=1, y\_odd\_inc=1)

Figure 12: Pixel Readout (x\_odd\_inc=3, y\_odd\_inc=1)

Figure 13: Pixel Readout (x\_odd\_inc=1, y\_odd\_inc=3)

Figure 14: Pixel Readout (x\_odd\_inc=3, y\_odd\_inc=3)

### **Programming Restrictions when Subsampling**

When subsampling is enabled as a viewfinder mode, and the sensor is switched back and forth between full resolution and subsampling, it is recommended that line\_length\_pck be kept constant between the two modes. This allows the same integration times to be used in each mode to maintain the same brightness.

When subsampling is enabled, it may be necessary to adjust the x\_addr\_end, x\_addr\_start and y\_addr\_end settings: the values for these registers are required to correspond with rows/columns that form part of the subsampling sequence. The adjustment should be made in accordance with the following rules:

```

x_skip_factor = (x_odd_inc + 1) / 2

y_skip_factor = (y_odd_inc + 1) / 2

```

- x\_addr\_start should be a multiple of x\_skip\_factor\*8

- (x addr end x addr start 1) should be a multiple of x skip factor\*8

- (y\_addr\_end y\_addr\_start 1) should be a multiple of y\_skip\_factor\*8

The number of columns/rows read out with subsampling can be found from the equation below:

• columns/rows = (addr\_end - addr\_start + odd\_inc) / skip\_factor

### Example:

The sensor is set up to give out a 640 x 480 image:

- x\_addr\_start = 8

- x addr end = 647

- y\_addr\_start = 8

- y addr end = 487

To half the resolution in each direction the registers need to be reprogrammed as follows:

- x addr start = 0 (8 is not read out in subsampling mode)

- x\_addr\_end = 637 (adjust for new start address and end requirement)

- y addr start = 8 (no restrictions on row starting address)

- y\_addr\_end = 485 (adjust for end requirement)

To quarter the resolution in each direction the registers need to be reprogrammed as follows:

- x addr start = 0

- x\_addr\_end = 633 (adjust for new start address and end requirement)

- y\_addr\_start = 8 (no restrictions on row starting address)

- y\_addr\_end = 481 (adjust for end requirement)

Table 6 shows the row address sequencing for normal and subsampled readout. The same sequencing applies to column addresses for subsampled readout. There are two possible subsampling sequences for the rows (because the subsampling sequence only read half of the rows) depending upon the alignment of the start address. The row address sequencing during binning is also shown. Due to the restrictions in column readout, only one subsampling sequence that meets the required x\_addr\_start is supported. This corresponds to the columns for start=0 in Table 6.

### **Table 6: Row Address Sequencing**

| odd_inc=1 | odd_inc=3 |         |         | odd_inc=7 |         |         |         |         |

|-----------|-----------|---------|---------|-----------|---------|---------|---------|---------|

| Normal    | Norr      | nal     | Binned  |           | Normal  |         | Binned  |         |

| start=0   | start=0   | start=2 | start=0 | start=2   | start=0 | start=2 | start=0 | start=2 |

| 0         | 0         |         | 0,2     |           | 0       |         | 0,2     |         |

| 1         | 1         |         | 1,3     |           | 1       |         | 1,3     |         |

| 2         |           | 2       |         | 2,4       |         | 2       |         | 2,4     |

| 3         |           | 3       |         | 3,5       |         | 3       |         | 3,5     |

| 4         | 4         |         | 4,6     |           |         |         |         |         |

| 5         | 5         |         | 5,7     |           |         |         |         |         |

| 6         |           | 6       |         | 6,8       |         |         |         |         |

| 7         |           | 7       |         | 7,9       |         |         |         |         |

| 8         | 8         |         | 8,10    |           | 8       |         | 8,10    |         |

| 9         | 9         |         | 9,11    |           | 9       |         | 9,11    |         |

| 10        |           | 10      |         | 10,12     |         | 10      |         | 10,12   |

| 11        |           | 11      |         | 11,13     |         | 11      |         | 11,13   |

| 12        | 12        |         | 12,14   |           |         |         |         |         |

| 13        | 13        |         | 13,15   |           |         |         |         |         |

| 14        |           | 14      |         | 14,16     |         |         |         |         |

| 15        |           | 15      |         | 15,17     |         |         |         |         |

#### **Binning**

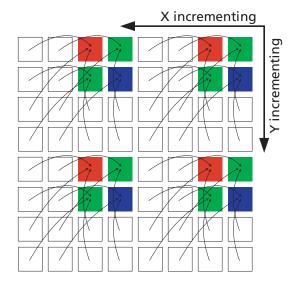

The sensor supports  $2 \times 1$  and  $2 \times 2$  analog binning which includes column binning (x-binning), and row/column binning (xy-binning). Binning has many of the same characteristics as subsampling, however:

- It gathers image data from all pixels in the active window (rather than a subset of them).

- It achieves superior image quality.

- It avoids the aliasing artifacts that can be a characteristic side effect of subsampling.

Binning is enabled by selecting the appropriate subsampling settings (x\_odd\_inc=3 and y\_odd\_inc=1 for x-binning, x\_odd\_inc=3 and y\_odd\_inc=3 for xy-binning) and setting the appropriate binning bit in read\_mode (R0x3040-1). In subsampling, x\_addr\_end and y\_addr\_end may require adjustment when binning is enabled. It is the first of the two columns/rows binned together that should be the end column/row in binning, so the requirements for the end address is exactly the same as in nonbinning subsampling mode.

Binning can also be enabled when the 4X subsampling mode is enabled (x\_odd\_inc=7 and y\_odd\_inc=1 for x-binning, x\_odd\_inc=7 and y\_odd\_inc=7 for xy-binning). In this mode, however, not all pixels will be used so this is not a 4X binning implementation. An implementation providing a combination of skip2 and bin2 is used to achieve 4X subsampling with better image quality.

The effect of the different subsampling settings is shown in Figure 15 on page 24 and Figure 16 on page 24.

Figure 15: Pixel Readout (x\_odd\_inc=3, y\_odd\_inc=1, x\_bin=1)

Figure 16: Pixel Readout (x\_odd\_inc=3, y\_odd\_inc=3, x\_ybin=1)

Figure 17: Pixel Readout (x\_odd\_inc=7, y\_odd\_inc=7, x\_ybin=1)

### **Binning Limitations**

Binning requires different sequencing of the pixel array and imposes different timing limits on the operation of the sensor. In particular, xy-binning requires two read operations from the pixel array for each line of output data, which has the effect of increasing the minimum line blanking time. The SMIA specification cannot accommodate this variation because its parameter limit registers are defined as being static.

As a result, when xy-binning is enabled, some of the programming limits declared in the parameter limit registers are no longer valid. In addition, the default values for some of the manufacturer specific registers need to be reprogrammed. The recommended settings are shown in Table 7. None of these adjustments are required for x-binning.

**Table 7: Register Adjustments Required for Binning Mode**

| Register                         | Туре      | Default<br>(Normal<br>Readout) | Recommended<br>Setting During<br>Binning | Notes                                                                         |

|----------------------------------|-----------|--------------------------------|------------------------------------------|-------------------------------------------------------------------------------|

| min_line_blanking_pck            | Read-only | 0x06AC                         | 0x0C40                                   | Read-only register for control software; does not affect operation of sensor. |

| min_line_length_pck              | Read-only | 0x0914                         | 0x1200                                   | Read-only register for control software; does not affect operation of sensor. |

| fine_integration_time_min        | Read-only | 0x056A                         | 0x0B1A                                   | Read-only register for control software; does not affect operation of sensor. |

| fine_integration_time_max_margin | Read-only | 0x03AA                         | 0x06E6                                   | Read-only register for control software; does not affect operation of sensor. |

Table 7: Register Adjustments Required for Binning Mode (continued)

| Register              | Туре       |        | Recommended<br>Setting During<br>Binning |                                 |

|-----------------------|------------|--------|------------------------------------------|---------------------------------|

| fine_correction       | Read/write | 0x0100 | 0x0238                                   | Affects operation of sensor     |

| fine_integration_time | Read/write | 0x056A | 0x0B1A                                   | Normal default is minimum value |

Since binning also requires subsampling to be enabled, the same restrictions apply to the setting of x\_addr\_end and y\_addr\_end ("Programming Restrictions when Subsampling" on page 21).

A given row n will always be binned with row n + 2 for 2X subsampling mode and row n+4 for 4X subsampling mode. Therefore, there are two candidate rows that a row can be binned with, depending upon the alignment of  $y_addr_start$ .

For a given column n, there is only one other column, n\_bin, that is can be binned with. Since the x\_addr\_start is restricted to multiple of 8 a column n will also always we binned with column n + 2 for 2X subsampling mode and column n + 4 for 4X subsampling mode.

## **Shading Correction (SC)**

Lenses tend to produce images whose brightness is significantly attenuated near the edges. There are also other factors causing fixed pattern signal gradients in images captured by image sensors. The cumulative result of all these factors is known as image shading. The MT9E001 has an embedded shading correction module that can be programmed to counter the shading effects on each individual Red, GreenR, GreenB, and Blue color signal.

#### **The Correction Function**

Color dependent solutions are calibrated using the sensor, lens system, and an image of an evenly illuminated, featureless gray calibration field. From the resulting image the color correction functions can be derived.

The correction functions can then be applied to each pixel value to equalize the response across the image as follows:

$$P_{corrected}(row,col) = P_{sensor}(row,col) *f(row,col)$$

(EQ 9)

where P are the pixel values and f is the color dependent correction functions for each color channel.

Each function includes a set of color dependent coefficients defined by registers R0x3600–3726. The function's origin is the center point of the function used in the calculation of the coefficients. Using an origin near the central point of symmetry of the sensor response provides the best results. The center point of the function is determined by ORIGIN\_C (R0x3782) and ORIGIN\_R (R0x3784) and can be used to counter an offset in the system lens from the center of the sensor array.

## **Output Data Format (Parallel Pixel Data Interface)**

The sensor image data is read out in a progressive scan. Valid image data is surrounded by horizontal blanking and vertical blanking as shown in Figure 18. The amount of horizontal blanking and vertical blanking is programmable. LINE\_VALID is HIGH during the shaded region of the figure. FRAME\_VALID timing is described in the next section.

Figure 18: Pixel Data Timing Example

| P <sub>0,0</sub> P <sub>0,1</sub> P <sub>0,2</sub>                                                                                                  | 00 00 00 00 00 00<br>00 00 00 00 00 00 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| VALID IMAGE                                                                                                                                         | HORIZONTAL<br>BLANKING                 |

| P <sub>m-1,0</sub> P <sub>m-1,1</sub> P <sub>m-1,n-1</sub> P <sub>m-1,n</sub> P <sub>m,0</sub> P <sub>m,1</sub> P <sub>m,n-1</sub> P <sub>m,n</sub> | 00 00 00 00 00 00<br>00 00 00 00 00 00 |

| 00 00 00 00 00 00<br>00 00 00 00 00 00                                                                                                              | 00 00 00 00 00 00<br>00 00 00 00 00 00 |

| VERTICAL BLANKING                                                                                                                                   | VERTICAL/HORIZONTAL<br>BLANKING        |

| 00 00 00                                                                                                                                            | 00 00 00 00 00 00 00 00 00 00 00 0     |

## **Output Data Timing (Parallel Pixel Data Interface)**

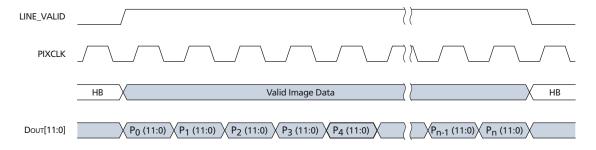

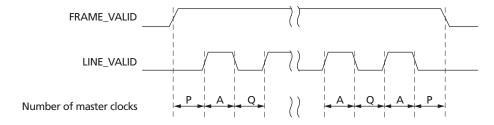

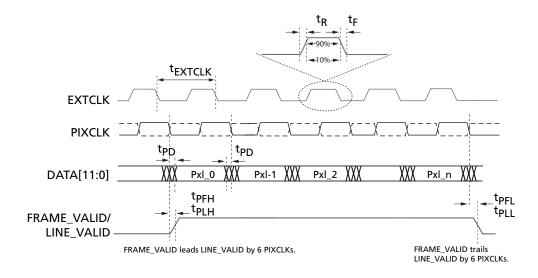

The sensor core output data is synchronized with the PIXCLK output. When LINE\_VALID is HIGH, one pixel data is output on the 12-bit Dout output every PIXCLK period. By default, the sensor master input clock (vt\_pix\_clk\_mhz) is set up as the virtual 192 MHz clock. Hence, the output clock (op\_pix\_clk\_mhz) is set up as half the sensor master input clock (vt\_pix\_clk\_mhz). The rising edges on the PIXCLK signal occur one-half of a pixel clock period after transitions on LINE\_VALID, FRAME\_VALID, and Dout (Figure 19). This allows PIXCLK to be used as a clock to sample the data. PIXCLK is continuously enabled, even during the blanking periods. The sensor can be programmed to delay the PIXCLK edge relative to the Dout transitions. This can be achieved by programming the corresponding bits in the row\_speed register. The parameters P, A, and Q in Figure 20 are defined inTable 8.

Figure 19: Pixel Data Timing Example

Figure 20: Row Timing and FRAME\_VALID/LINE\_VALID Signals

**Table 8: Row Timing Parameters**

| Parameter     | Name                      | Equation                                                                   | Default Timing                        |

|---------------|---------------------------|----------------------------------------------------------------------------|---------------------------------------|

| PIXCLK_PERIOD | Pixel clock period        | R0x3016-7[2:0] / vt_pix_clk_freq_mhz                                       | 1 pixel clock<br>= 5.2ns              |

| S             | Skip (subsampling) factor | x_odd_inc=y_odd_inc=3, S=2<br>x_odd_inc=y_odd_inc=7, S=4<br>otherwise, S=1 | 1                                     |

| А             | Active data time          | (x_addr_end - x_addr_start + 1) * PIXCLK_PERIOD/S                          | 3264 pixel clocks<br>= 17.0µs         |

| P             | Frame start/end blanking  | 12 * PIXCLK_PERIOD                                                         | 12 pixel clocks<br>= 62.5ns           |

| Q             | Horizontal blanking       | (line_length_pck - A) * PIXCLK_PERIOD                                      | 6558 - 3264 pixel clocks<br>= 17.16µs |

| A + Q         | Row time                  | line_length_pck * PIXCLK_PERIOD                                            | 6558 pixel clocks<br>= 34.16µs        |

| N             | Number of rows            | (y_addr_end - y_addr_start + y_odd_inc)/S                                  | 2448 rows                             |

| V             | Vertical blanking         | ((frame_length_lines - N) * (A+Q)) + Q - (2*P)                             | 737,766 pixel clocks<br>= 3.84ms      |

| N * (A+Q)     | Frame valid time          | (N * (A + Q)) - Q + (2*P)                                                  | 16,050,714 pixel clocks<br>= 83.60ms  |

| F             | Total frame time          | line_length_pck * frame_length_lines * PIXCLK_PERIOD                       | 16,788,480 pixel clocks<br>= 87.44ms  |

Note:

This sensor has two internal data paths. The pixel clock used in the calculations (192 MHz) will, therefore, be twice the physical pixel clock frequency (96 MHz). The parameter P is measured in physical pixel clocks, and will therefore change for sensors with two data paths as described in Table 8.

The sensor timing (Table 8) is shown in terms of pixel clock and master clock cycles (Figure 18 on page 27). The default settings for the on-chip PLL generate a 9 6MHz master input clock and pixel clock given a 24 MHz input clock to the sensor.

## **General Purpose Inputs**

The sensor provides four general purpose inputs; before reset they are in an unknown state. After reset, the input pads associated with these signals are powered-down by default, allowing the pads to be left disconnected/floating.

The general purpose inputs are enabled by setting reset\_register[8] (0x301A-B[8]). Once enabled, all four inputs must be driven to valid logic levels by external signals. The state of the general purpose inputs can be read through gpi\_status (0x3026[3:0]).

In addition, each of the following functions can be associated with none, one or more of the general-purpose inputs so that the function can be directly controlled by a hardware input:

- output enable (see "Output Enable Control" on page 29)

- SADDR (selects device address for the two-wire serial interface)

- trigger (see the sections below)

- standby functions (see the sections below)

The gpi\_status register (0x3026) is used to associate a function with a general purpose input.

### **Parallel Pixel Data Interface**

The parallel pixel data interface uses the following output-only signals:

- FRAME VALID

- LINE VALID

- PIXCLK

- Dout[11:0]

The parallel pixel data interface is disabled by default at power-up and after reset. It can be enabled by programming R0x301A.

#### **Output Enable Control**

When the parallel pixel data interface is enabled, its signals can be switched asynchronously between the driven and High-Z—this is controlled either by pin or register control, as shown in Table 9.

### **Table 9: Output Enable Control**

| GPI Configured<br>OE_N Pin | Drive Signals<br>R0x301A-B[6] | Description      |

|----------------------------|-------------------------------|------------------|

| disabled                   | 0                             | Interface High-Z |

| disabled                   | 1                             | Interface driven |

| 1                          | 0                             | Interface High-Z |

| X                          | 1                             | Interface driven |

| 0                          | X                             | Interface driven |

## **Trigger Control**

When the global reset feature is in use, the trigger for the sequence can be initiated either under pin or register control, as shown in Table 10 on page 30.

**Table 10: Trigger Control**

| GPI Configured<br>TRIGGER in | Global Trigger R0x3160–1[0] | Description |

|------------------------------|-----------------------------|-------------|

| Disabled                     | 0                           | Idle        |

| Disabled                     | 1                           | Trigger     |

| 0                            | 0                           | Idle        |

| X                            | 1                           | Trigger     |

| 1                            | X                           | Trigger     |

## **Streaming/Standby Control**

The sensor can be switched between its soft standby and streaming states under pin or register control, as shown in the Table 11 above. Selection of a pin to use for the STANDBY function is described in "General Purpose Inputs" on page 29. The state diagram for transitions between soft standby and streaming states is shown in the Figure 33 on page 85.

**Table 11: Streaming/STANDBY**

| GPI Configured STANDBY Pin | Streaming R0x301A-B[2] | Description  |

|----------------------------|------------------------|--------------|

| Disabled                   | 0                      | Soft Standby |

| Disabled                   | 1                      | Streaming    |

| X                          | 0                      | Soft Standby |

| 0                          | 1                      | Streaming    |

| 1                          | X                      | Soft Standby |

## **Operational Modes**

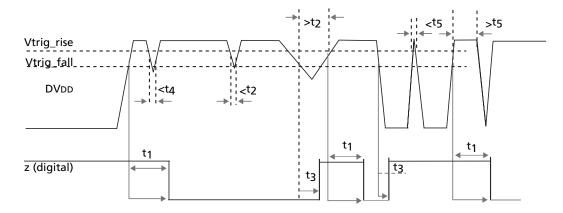

### **Snapshot and Flash**

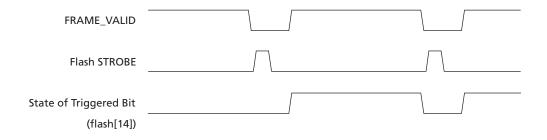

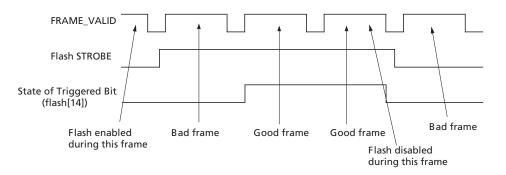

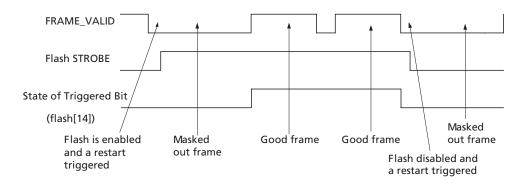

The sensor supports both Xenon and LED flash through the FLASH output signal. The timing of the FLASH signal with the default settings is shown in Figure 21 on page 31 through Figure 23 on page 31. The flash and flash\_count registers allow the timing of the flash to be changed. The flash can be programmed to fire only once, to be delayed by a few frames when asserted, and (for Xenon flash) to program the flash duration.

Enabling the LED flash will cause one bad frame, where several of the rows only have the flash on for part of their integration time. This can be avoided by forcing a restart of the frame (write reset\_register[1] = 1) immediately after enabling the flash; the first bad frame will then be masked out as shown in Figure 23 on page 31. Read-only bit flash[14] is set during frames that are correctly integrated; the state of this bit is shown in Figures 21 through Figure 23 on page 31.

Figure 21: Xenon Flash Enabled

Figure 22: LED Flash Enabled

Figure 23: LED Flash Enabled Following Forced Restart

### **Low Power Mode**

The sensor supports a low-power mode by programming register bit read\_mode[9]. Setting this bit will result in the following:

• Double the value of pc\_speed[2:0] internally. This means halving the internal pixel clock frequency.

The slower pixel clock provides more time for settling in the analog domain, thus, the low power DAC values can be approximately half the full power DAC values.

Enabling the low power mode will not put the sensor in subsampling mode; this has to be programmed separately as described earlier in this document. Low power is independent of the readout mode, and can also be enabled in full resolution mode. However, since the pixel clock speed is halved, the frame rates that can be achieved with low power mode are lower than in full power mode.

Only internal pixel clock speeds of 1, 2 and 4 are supported; therefore, low power mode combined with pc\_speed[2:0]=4 is an illegal combination.

Any limitations related to changing the internal pixel clock speed will also apply to low power mode since it automatically changes the pixel clock speed. SMIA limiter registers therefore needs to be reprogram to match the new internal pixel clock frequency.

#### **Test Patterns**

For test purposes, pixel data can be replaced with a fixed image generated by a special test module in the pipeline. The module provides a selection of test patterns sufficient for basic testing of the signal chain.

Test patterns are accessible using R0x0600 and are shown in Table 12.

#### **Table 12: Test Patterns**

| Test Pattern                      | Register Value |

|-----------------------------------|----------------|

| Normal Operation: no test pattern | 0              |

| Flat Field                        | 1              |

| Color Bar                         | 2              |

| Fade-to-Gray Color Bar            | 3              |

| Marching 1's                      | 256            |

## **Two-Wire Serial Interface**

The two-wire serial interface bus enables read/write access to control and status registers within the sensor. This interface is designed to be compatible with the "SMIA 1.0 Part2: CCP2 Specification Camera Control Interface (CCI)," that uses the electrical characteristics and transfer protocols of the two-wire serial interface specification.

The interface protocol uses a master/slave model in which a master controls one or more slave devices. The sensor acts as a slave device. The master generates a clock (SCLK) that is an input to the sensor and used to synchronize transfers. Data is transferred between the master and the slave on a bidirectional signal (SDATA). SDATA is pulled up to VDD off-chip by a  $1.5 {\rm K}\Omega$  resistor. Either the slave or master device can drive SDATA LOW—the interface protocol determines which device is allowed to drive SDATA at any given time.

The protocols described in the two-wire serial interface specification allow the slave device to drive SCLK LOW; the sensor uses SCLK as an input only; therefore, never drives it LOW.

#### **Protocol**

Data transfers on the two-wire serial interface bus are performed by a sequence of low-level protocol elements, as follows:

- a (repeated) start condition

- · a slave address/data direction byte

- a(an) (not) acknowledge bit

- · a message byte

- · a stop condition

The bus is idle when both SCLK and SDATA are HIGH. Control of the bus is initiated with a start condition, and the bus is released with a stop condition. Only the master can generate the start and stop conditions.

#### **Start Condition**

A start condition is defined as a HIGH-to-LOW transition on SDATA while SCLK is HIGH. At the end of a transfer, the master can generate a start condition without previously generating a stop condition; this is known as a repeated start or restart condition.

### **Stop Condition**

A stop condition is defined as a LOW -to-HIGH transition on SDATA while SCLK is HIGH.

#### **Data Transfer**

Data is transferred serially, 8 bits at a time, with the MSB transmitted first. Each byte of data is followed by an acknowledge bit or a no-acknowledge bit. This data transfer mechanism is used for the slave address/data direction byte and for message bytes.

One data bit is transferred during each SCLK clock period. SDATA can change when SCLK is LOW and must be stable while SCLK is HIGH.

#### **Slave Address/Data Direction Byte**

Bits [7:1] of this byte represent the device slave address and bit [0] indicates the data transfer direction. A "0" in bit [0] indicates a write, and a "1" indicates a read. The default slave addresses used by the sensor are 0x20 (write address) and 0x21 (read address), in accordance with the SMIA specification. Alternate slave addresses of 0x30 (write

address) and 0x31 (read address) can be selected. The GPI pins can be configured for SADDR functionality through register bit fields 0x3026[6:4], and enabled by setting 0x301A[8].

These default slave addresses are also fully programmable through the I<sup>2</sup>C address registers (0x31FC–0x31FD). Before this register can be written to, it needs to be unlocked through reset\_register 0x301A[3].

#### **Message Byte**

Message bytes are used for sending register addresses and register write data to the slave device and for retrieving register read data. The protocol used is outside the scope of the two-wire serial interface specification and is defined as part of the SMIA CCI.

### **Acknowledge Bit**

Each 8-bit data transfer is followed by an acknowledge bit or a no-acknowledge bit in the SCLK clock period following the data transfer. The transmitter (which is the master when writing, or the slave when reading) releases SDATA. The receiver indicates an acknowledge bit by driving SDATA LOW. As for data transfers, SDATA can change when SCLK is LOW and must be stable while SCLK is HIGH.

## **No-Acknowledge Bit**

The no-acknowledge bit is generated when the receiver does not drive SDATA LOW during the SCLK clock period following a data transfer. A no-acknowledge bit is used to terminate a read sequence.

## **Typical Serial Transfer**

A typical read or write sequence begins by the master generating a start condition on the bus. After the start condition, the master sends the 8-bit slave address/data direction byte. The last bit indicates whether the request is for a read or a write, where a "0" indicates a write and a "1" indicates a read. If the address matches the address of the slave device, the slave device acknowledges receipt of the address by generating an acknowledge bit on the bus.

If the request was a write, the master then transfers the 16-bit register address to which the write should take place. This transfer takes place as two, 8-bit sequences and the slave sends an acknowledge bit after each sequence to indicate that the byte has been received. The master then transfers the data as an 8-bit sequence; the slave sends an acknowledge bit at the end of the sequence. After 8 bits have been transferred, the slave's internal register address is incremented automatically, so that the next 8 bits are written to the next register address. The master stops writing by generating a (re)start or stop condition.

If the request was a read, the master sends the 8-bit write slave address/data direction byte and 16-bit register address, the same way as with a write request. The master then generates a (re)start condition and the 8-bit read slave address/data direction byte, and clocks out the register data, 8 bits at a time. The master generates an acknowledge bit after each 8-bit transfer. The slave's internal register address is auto-incremented after every 8 bits are transferred. The data transfer is stopped when the master sends a no-acknowledge bit.

## **Single Read from Random Location**

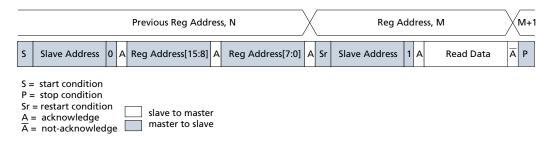

This sequence (Figure 24) starts with a dummy write to the 16-bit address that is to be used for the read. The master terminates the write by generating a restart condition. The master then sends the 8-bit read slave address/data direction byte and clocks out one byte of register data. The master terminates the read by generating a no-acknowledge bit followed by a stop condition. Figure 24 shows how the internal register address maintained by the sensor is loaded and incremented as the sequence proceeds.

Figure 24: Single Read from Random Location

## **Single Read from Current Location**

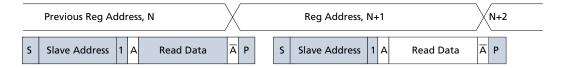

This sequence (Figure 25) performs a read using the current value of the sensor internal register address. The master terminates the read by generating a no-acknowledge bit followed by a stop condition. The figure shows two independent read sequences.

Figure 25: Single Read from Current Location

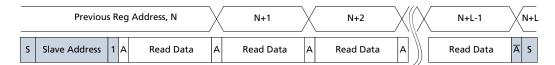

## **Sequential Read, Start from Random Location**

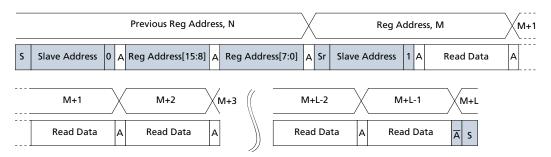

This sequence (Figure 26) starts in the same way as the single read from random location (Figure 24). Instead of generating a no-acknowledge bit after the first byte of data has been transferred, the master generates an acknowledge bit, and continues to perform byte reads until "L" bytes have been read.

Figure 26: Sequential Read, Start from Random Location

### **Sequential Read, Start from Current Location**

This sequence (Figure 27) starts in the same way as the single read from current location (Figure 25 on page 35). Instead of generating a no-acknowledge bit after the first byte of data has been transferred, the master generates an acknowledge bit, and continues to perform byte reads until "L" bytes have been read.

Figure 27: Sequential Read, Start from Current Location

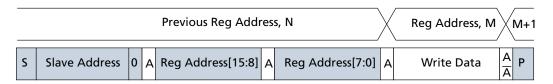

## **Single Write to Random Location**

This sequence (Figure 28) begins with the master generating a start condition. The slave address/data direction byte signals a write and is followed by the high then low bytes of the register address that is to be written. The master follows this with the byte of write data. The write is terminated by the master generating a stop condition.

Figure 28: Single Write to Random Location

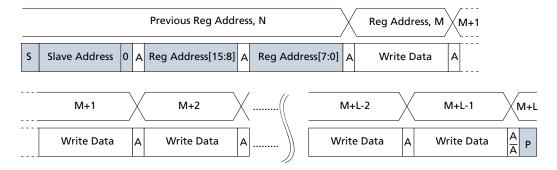

## **Sequential Write, Start at Random Location**

This sequence (Figure 29) starts in the same way as the single write to random location (Figure 28). Instead of generating a no-acknowledge bit after the first byte of data has been transferred, the master generates an acknowledge bit, and continues to perform byte writes until "L" bytes have been written. The write is terminated by the master generating a stop condition.

Figure 29: Sequential Write, Start at Random Location

# MT9E001: 1/2.5-Inch 8-Mp Digital Image Sensor Registers

# Registers

The sensor provides a 16-bit register address space accessed through a serial interface. Each register location is 8 bits in size.

The address space is divided into the five major regions shown in Table 13.

#### **Table 13: Address Space Regions**

| Address Regions | Description                                                                  |

|-----------------|------------------------------------------------------------------------------|

| 0x0000-0x0FFF   | Configuration registers (Read-only and read-write dynamic registers)         |

| 0x1000-0x1FFF   | Parameter limit registers<br>(Read-only static registers)                    |

| 0x2000-0x2FFF   | Reserved<br>(Undefined)                                                      |

| 0x3000-0x3FFF   | Manufacturer specific registers (Read-only and read-write dynamic registers) |

| 0x4000-0xFFFF   | Reserved<br>(Undefined)                                                      |

#### **Register Notation**

The underlying mechanism for reading and writing registers provides byte write capability. However, it is convenient to consider some registers as multiple adjacent bytes. The sensor uses 8-bit, 16-bit, and 32-bit registers; all implemented as 1 or more bytes at naturally aligned, contiguous locations in the address space.

Registers are described either by address or by name. When registers are described by address, the size of the registers is explicit. For example, R0x3024 is an 8-bit register at address 0x3024, and R0x3000–1 is a 16-bit register at address 0x3000–0x3001. When registers are described by name, the size of the register is not implicit. For example, it is necessary to refer to the register table to determine that model\_id is a 16-bit register.

#### **Register Aliases**

A consequence of the internal architecture of the sensor is that some registers are decoded at multiple addresses: some registers in configuration space are also decoded in manufacturing specific space. In order to provide unique names for all registers, the name of the register within manufacturer specific register space has a trailing underscore. For example, R0x0000–1 is model\_id, and R0x3000–1 is model\_id\_ (see the register tables for more examples). The effect of reading or writing a register to itself or through any of its aliases is identical.

#### **Bit Fields**

Some registers provide control of several different pieces of related functionality and this makes it necessary to refer to bit fields within registers. As an example of the notation used for this, the least significant 4 bits of the model\_id register are referred to as model id[3:0] or R0x0000–1[3:0].

# MT9E001: 1/2.5-Inch 8-Mp Digital Image Sensor Registers

#### **Bit Field Aliases**