### **General Description**

The DS4560 is a self-contained hot-plug switch intended to be used on +12V power buses to limit through current and to control the power-up output-voltage ramp. The device contains an on-board  $25m\Omega$  n-channel power MOSFET that is actively closed-loop controlled to ensure that an adjustable current limit is not exceeded. The maximum allowable current through the device is determined by an external resistor connected to the ILIM pin.

The DS4560 also contains the ability to control the power-up output-voltage ramp. A capacitor connected to the VRAMP pin sets the desired voltage ramp rate. The output voltage is unconditionally clamped to keep input overvoltage stresses from harming the load. The DS4560 also contains an adjustable power-up timer. A capacitor connected to the TIMER pin determines how long after power-on reset the DS4560 should wait before starting to apply power to the load. The TIMER pin can also be driven with a digital logic output to create a device-enable function.

The DS4560 contains an on-board temperature sensor with hysteresis. If operating conditions cause the device to exceed an internal thermal limit, the DS4560 either unconditionally shuts down and latches off awaiting a power-on reset (DS4560S-LO), or it waits until the device has cooled by the hysteresis amount and then restarts (DS4560S-AR).

### **Applications**

**RAID/Hard Drives**

InfiniBand<sup>SM</sup> **Base Stations**

Servers/Routers PCI/PCI Express®

# **Ordering Information**

| PART         | THERMAL<br>SHUTDOWN | PIN-PACKAGE |

|--------------|---------------------|-------------|

| DS4560S-LO+  | Latchoff            | 8 SO        |

| DS4560S-LO+T | Latchoff            | 8 SO        |

| DS4560S-AR+  | Autoretry           | 8 SO        |

| DS4560S-AR+T | Autoretry           | 8 SO        |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

# **Features**

- ♦ On-Board 25mΩ Power MOSFET

- ♦ Adjustable Short-Circuit Current and Overload **Current Limit**

- **♦ Adjustable Output-Voltage Slew Rate**

- ♦ Adjustable Power-Up Timer with External Enable Capability

- **♦ Output Overvoltage Limiting**

- ♦ On-Board Thermal Protection

- ♦ On-Board Charge Pump

- **♦ Latchoff and Autoretry Versions Available**

- ♦ 9.0V to 13.2V Supply Operation

- ♦ 8-Pin SO (150 mils) Pb-Free Package

- ♦ UL Certification Record E211395

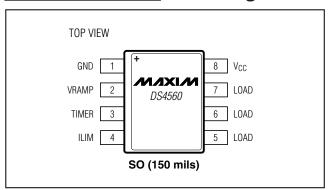

### Pin Configuration

## **Pin Description**

| PIN     | NAME            | FUNCTION                                         |

|---------|-----------------|--------------------------------------------------|

| 1       | GND             | Ground. This is also a heat sink for the device. |

| 2       | VRAMP           | Output-Voltage Ramp Adjustment                   |

| 3       | TIMER           | Power-Up Timer/Enable                            |

| 4       | ILIM            | Current-Limit Adjustment                         |

| 5, 6, 7 | LOAD            | Output Load Connection (MOSFET Source)           |

| 8       | V <sub>CC</sub> | Input Supply Voltage (MOSFET Drain)              |

PCI Express is a registered trademark of PCI-SIG Corp. InfiniBand is a trademark and service mark of the InfiniBand Trade Association.

MIXIM

T = Tape and reel.

### **ABSOLUTE MAXIMUM RATINGS**

| Voltage Range on VCC and LOAD Relative to GND |                                |  |  |  |

|-----------------------------------------------|--------------------------------|--|--|--|

| Continuous                                    | 0.3V to +18V                   |  |  |  |

| 1ms Maximum                                   | 0.3V to +22V                   |  |  |  |

| Voltage Range on ILIM and VRAMP               |                                |  |  |  |

| Relative to GND                               | $-0.3V$ to $(V_{CC} + 0.3V)$ , |  |  |  |

| b                                             | out not to exceed +18V         |  |  |  |

| Voltage Range on TIMER Relative to GND        | 00.3V to +5.0V                 |  |  |  |

| Drain Current                     |                          |

|-----------------------------------|--------------------------|

| Continuous                        | 4A                       |

| Peak                              | 15A                      |

| Operating Junction Temperature Ra | nge40°C to +135°C        |

| Storage Temperature Range         | 55°C to +135°C           |

| Soldering Temperature             |                          |

|                                   | J-STD-020 Specification. |

|                                   |                          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### RECOMMENDED OPERATING CONDITIONS

$(T_J = -40^{\circ}C \text{ to } +135^{\circ}C.)$

| PARAMETER                | SYMBOL           | CONDITIONS   | MIN  | TYP | MAX  | UNITS |

|--------------------------|------------------|--------------|------|-----|------|-------|

| Supply Voltage           | Vcc              | (Notes 1, 2) | 9.0  |     | 13.2 | V     |

| R <sub>ILIM</sub> Value  | RILIM            |              | 20   |     | 400  | Ω     |

| C <sub>VRAMP</sub> Value | CVRAMP           |              | 0.04 |     | 5.00 | μF    |

| C <sub>TIMER</sub> Value | CTIMER           |              | 0.04 |     | 5.00 | μF    |

| TIMER Turn-On Voltage    | Von              |              | 2.6  |     | 5    | V     |

| TIMER Turn-Off Voltage   | V <sub>OFF</sub> |              | -0.3 |     | +2.0 | V     |

### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +12V, T_J = +25^{\circ}C, unless otherwise noted.)$

| PARAMETER                                            | SYMBOL           | CONDITIONS                   | MIN  | TYP  | MAX  | UNITS |

|------------------------------------------------------|------------------|------------------------------|------|------|------|-------|

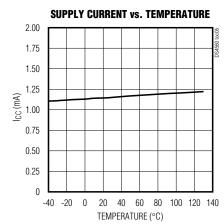

| Supply Current                                       | Icc              | (Note 3)                     |      | 1.1  | 2.00 | mA    |

| UVLO Rising                                          | Vuvlor           |                              | 7.5  | 8.0  | 8.5  | V     |

| UVLO Falling                                         | Vuvlof           |                              | 6.5  | 7.0  | 7.5  | V     |

| UVLO Hysteresis                                      | Vuvloh           |                              |      | 1    |      | V     |

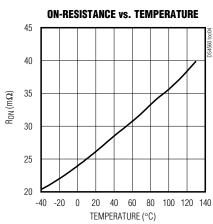

| On-Resistance                                        | Ron              |                              |      | 25   | 32   | mΩ    |

| MOSFET Output Capacitance                            | Cout             |                              |      | 500  |      | pF    |

| LOAD Voltage During Off State                        | VLOFF            | (Note 4)                     |      |      | 200  | mV    |

| Delay Time from Enable to<br>Beginning of Conduction | tpond            | CVRAMP = 1µF                 |      | 5    |      | ms    |

| Gate-Charging Time from Conduction to 90% of VOUT    | tgct             | CVRAMP = 1µF, CLOAD = 1000µF | 48   | 66   | 80   | ms    |

| Shutdown Junction Temperature                        | TSHDN            | (Note 5)                     | 120  | 135  | 150  | °C    |

| Thermal Hysteresis                                   | T <sub>HYS</sub> | (Note 5)                     |      | 40   |      | °C    |

| TIMER Charging Current                               | ITIMER           |                              | 70   | 80   | 92   | μΑ    |

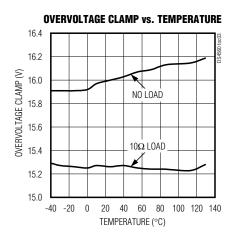

| Overvoltage Clamp                                    | V <sub>OVC</sub> |                              | 13.5 | 15.0 | 16.5 | V     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +12V, T_J = +25^{\circ}C, \text{ unless otherwise noted.})$

| PARAMETER              | SYMBOL           | CONDITIONS                                | MIN  | TYP  | MAX  | UNITS |

|------------------------|------------------|-------------------------------------------|------|------|------|-------|

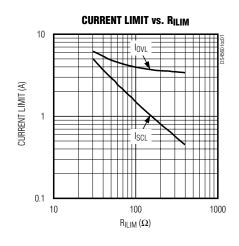

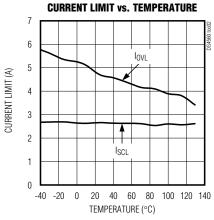

| Short-Circuit Limit    | I <sub>SCL</sub> | $R_{ILIM} = 56\Omega \text{ (Note 6)}$    | 2.0  | 2.5  | 3.0  | Α     |

| Overload Limit         | lovL             | $R_{\rm ILIM} = 56\Omega  ({ m Note}  7)$ | 3.5  | 4.4  | 5.9  | Α     |

| LOAD Voltage Slew Rate | SRLOAD           | CVRAMP = 1µF                              | 0.13 | 0.15 | 0.18 | V/ms  |

| VRAMP Charging Current | IVRAMP           |                                           | 70   | 80   | 92   | μΑ    |

Note 1: All voltages are referenced to ground. Currents entering the IC are specified positive and currents exiting the IC are negative.

Note 2: This supply range guarantees that the LOAD voltage is not clamped by the overvoltage limit.

Note 3: Supply current specified with no load on the LOAD pin.

**Note 4:** V<sub>I OFF</sub> voltage specified with a 2.5mA load applied to LOAD.

Note 5: Not production tested. Guaranteed by design.

Note 6: ISCL is the current limit when the output voltage is initially ramping up.

Note 7: IOVL is the current limit after the output voltage ramping is complete.

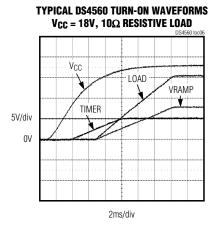

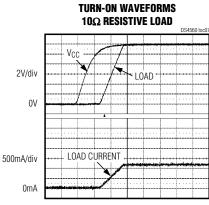

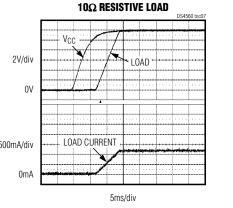

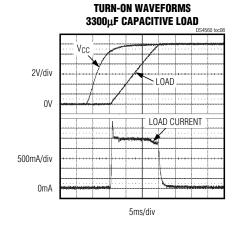

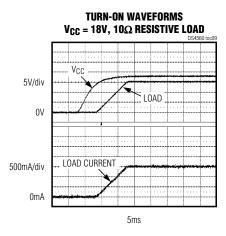

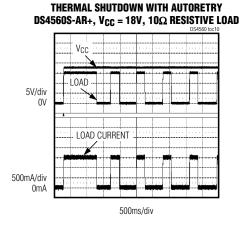

## Typical Operating Characteristics

$(V_{CC} = 12V, T_A = +25^{\circ}C, R_{ILIM} = 56\Omega, V_{CC} = 12V, C_{TIMER} = 0.1\mu F, C_{VRAMP} = 0.1\mu F, unless otherwise noted.)$

## Typical Operating Characteristics (continued)

$(V_{CC} = 12V, T_A = +25^{\circ}C, R_{ILIM} = 56\Omega, V_{CC} = 12V, C_{TIMER} = 0.1\mu\text{F}, C_{VRAMP} = 0.1\mu\text{F}, unless otherwise noted.})$

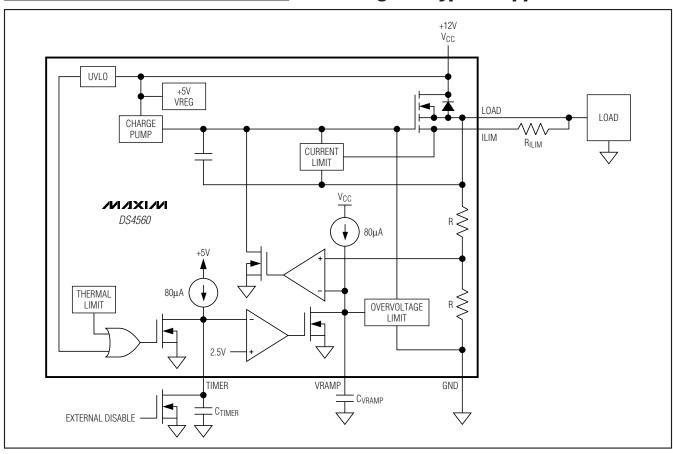

### Block Diagram/Typical Application Circuit

## Detailed Description

The DS4560 begins to operate when VCC exceeds the undervoltage lockout level,  $V_{UVLOR}$ . At this level, the enable circuit and TIMER pin become active. Once the device has been enabled, a gate voltage is applied to the power MOSFET, allowing current to begin flowing from VCC to LOAD. The speed of the output-voltage ramp is controlled by the capacitance placed at the VRAMP pin. The load current is continuously monitored during the initial voltage ramping (ISCL) and during normal operation (IOVL). If the current exceeds the current limit that is set by the external resistance at ILIM, the gate voltage of the power MOSFET is decreased, reducing the output current to the set current limit.

Current is limited by the DS4560 comparing the voltage difference between the LOAD and ILIM pins to an internal reference voltage. If the output current exceeds the limit that is set by the R<sub>ILIM</sub> resistor, the gate voltage of the power MOSFET is decreased, which reduces the output current to the load.

When the output power is initially ramping up, the current limit is I<sub>SCL</sub>. Once the voltage ramping is complete, the current limit is I<sub>OVL</sub>. The lower I<sub>SCL</sub> current limit protects the source if there is a dead short on initial power-up.

The DS4560 acts as a fuse and automatically disables the current flowing to the load when the temperature of the power MOSFET has exceeded the shutdown junction temperature, T<sub>SHDN</sub>.

#### Enable/Timer

The voltage level of the TIMER pin is compared to an internal source (see the *Block Diagram*). When the level on the pin exceeds VON, the comparator outputs a low level. This then turns on the voltage ramp circuit, enabling the device's output. This TIMER pin can be configured into one of four different modes of operation listed in Table 1. The TIMER pin was designed to work with most logic families. The TIMER pin will have at least 250mV of hysteresis between VON and VOFF. It is recommended that any logic gate used to drive the TIMER pin be tested to ensure proper operation.

Once the device has been enabled, there is a delay  $(t_{POND})$  until conduction begins from  $V_{CC}$  to LOAD. This delay is the time required for the charge pump to bring the gate voltage of the power MOSFET above its threshold level. Once the gate is above the threshold level, conduction begins and the output voltage begins ramping.

#### Automatic Enable Mode

When  $V_{\rm CC}$  exceeds  $V_{\rm UVLOR}$ , the gate holding the TIMER node low is released. The internal current source brings the node to a level greater than  $V_{\rm ON}$ , enabling the device.

#### Delayed Automatic Enable Mode

When VCC exceeds VUVLOR, the gate holding the TIMER node low is released. The internal current source (ITIMER) then begins charging CTIMER. When CTIMER is charged to a level greater than VON, the device turns on. The equation for the delay time is:

tdelay = (Ctimer x Von)/Itimer

#### Enable/Disable Mode

A logic gate or open-collector device can be connected to the TIMER pin to enable or disable the device. When the TIMER pin is held low, the device is disabled. When an open-collector device is used to drive the TIMER pin, the DS4560 is enabled when the open collector is in its high-impedance state by the internal current source bringing the TIMER node high. The TIMER pin is also compatible with most logic families if the out-

put high voltage level of the gate exceeds the VoN level, and the gate can sink the ITIMER current.

#### Enable with Delay/Disable Mode

An open-collector device is connected in parallel with CTIMER. When the pin is held low, the DS4560 is disabled. When the open-collector driver is high impedance, the internal current source begins to charge CTIMER as in the delayed mode.

### **Output-Voltage Ramp**

The voltage ramp circuit uses an operational amplifier to control the gate bias of the n-channel power MOSFET. When the timer/enable circuit is disabled, a FET is used to keep CVRAMP discharged, which forces the output voltage to GND. Once the enable/timer circuit has been enabled, an internal current source, IVRAMP, begins to charge the external capacitor, CVRAMP, connected to the VRAMP pin. The amplifier controls the gate of the power MOSFET so that the LOAD output voltage divided by two tracks the rising voltage level of CVRAMP. The output voltage continues to ramp until it reaches either the input VCC level or the overvoltage clamp limits. The equation for the output-voltage ramp function is:

$dV_{LOAD}/dt = 2 \times (I_{VRAMP}/C_{VRAMP})$

#### **Thermal Shutdown**

The DS4560 enters a thermal shutdown state when the temperature of the power MOSFET reaches or exceeds T<sub>SHDN</sub>, approximately +135°C. When T<sub>SHDN</sub> is exceeded, the thermal-limiting circuitry disables the DS4560 using the enable circuitry. The DS4560 is offered in two different versions: an autoretry version and a latchoff version.

#### Autoretry Version (DS4560S-AR)

The autoretry verson continually monitors the temperature once it has entered thermal shutdown. If the junction temperature falls below approximately +95°C (TSHDN - THYS), the power MOSFET is re-enabled. See the Thermal Shutdown with Autoretry graph for details.

**Table 1. TIMER Pin Modes**

| MODE OF OPERATION         | TIMER PIN SETUP                                  |

|---------------------------|--------------------------------------------------|

| Automatic Enable          | No connection to TIMER pin.                      |

| Delayed Automatic Enable  | Capacitor C <sub>TIMER</sub> connected to TIMER. |

| Enable/Disable            | Open-collector device.                           |

| Enable with Delay/Disable | Open-collector device and CTIMER.                |

#### Latchoff Version (DS4560S-LO)

Once the latchoff version has entered thermal shutdown, it does not attempt to turn back on. The only way to turn this device back on is to cycle the power to the device. When power is reapplied to V<sub>CC</sub>, the junction temperature needs to be less than T<sub>SHDN</sub> for the device to be enabled.

#### **Overvoltage Limit**

The overvoltage-limiting clamp monitors the VRAMP level compared to an internal voltage reference. When the voltage on VRAMP exceeds Vovc/2, the gate voltage of the n-channel power MOSFET is reduced, limiting the voltage on LOAD to Vovc even as Vcc increases. If the device is in overvoltage for an extended period of time, the device may overheat and enter thermal shutdown. This is caused by the power created by the voltage drop across the power MOSFET and the load current. See the Thermal Shutdown with Autoretry graph for details.

## **Applications Information**

The GND pin of the DS4560 is also a heat sink for the device. This pin should be connected to a large trace or plane capable of dissipating heat from the device.

## Package Information

For the latest package outline information and land patterns, go to **www.maxim-ic.com/packages**.

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO. |

|--------------|--------------|--------------|

| 8 SO         | _            | 21-0041      |

## **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                                                                                        | PAGES<br>CHANGED |

|--------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 0                  | 6/08             | Initial release.                                                                                                                                                   | _                |

| 1                  | 9/08             | In the <i>Recommended Operating Conditions</i> , changed the TIMER Turn-On Voltage (V <sub>ON</sub> ) maximum specification from "V <sub>CC</sub> + 0.3V" to "5V." | 2                |

| 2                  | 5/09             | Added the UL certification number to the Features section.                                                                                                         | 1                |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.