### HT77S10/HT77S11

### High Efficiency Synchronous Step-Up DC/DC Converter

#### **Features**

• Low start-up voltage: 0.7V (Typ.)

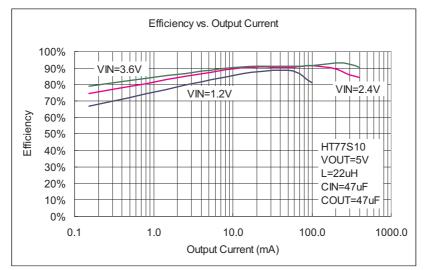

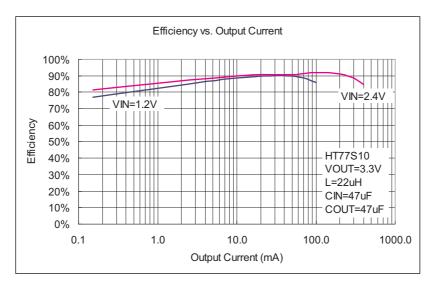

High efficiency: HT77S10: 91% (Typ.) at I<sub>OUT</sub>=200mA, V<sub>IN</sub>=2.4V, V<sub>OUT</sub>=3.3V

• High output voltage accuracy: ±4%

• Output voltage: 3.3V, 5.0V or Adjustable

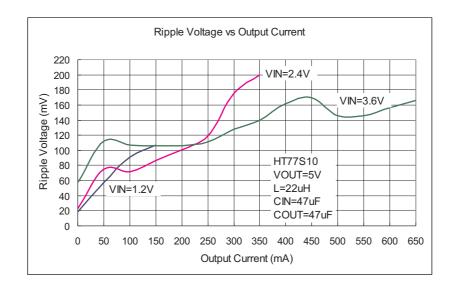

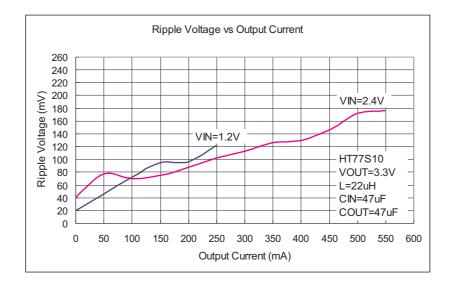

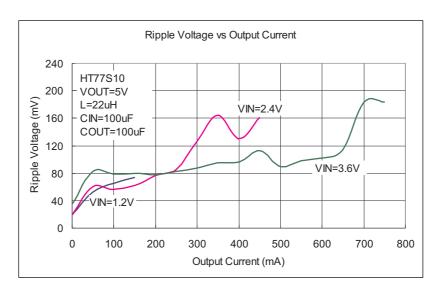

· Low ripple and low noise

• Ultra low supply current: 20μA (Typ.)

Low shutdown current: 1μA (Max.)

· Built-in voltage detector

• 8-pin MSOP/SOP packages

#### **Applications**

• Battery-powered equipment power source

Power source for cameras, camcorders, VCRs, PDAs, pagers, electronic data banks, and hand-held communication equipment  Power source for appliances, which require a higher operating voltage than that of the application batteries

### **General Description**

The HT77S11 and HT77S10 are high efficiency PFM synchronous step-up DC-DC converters. The two devices although functionally similar are different in their output drive current capabilities. Synchronous rectification operation is used to increase device efficiency and to reduce the external component resulting in reduced product costs. The converter switching frequency, which can have a value up to 500KHz, will vary according to the load demands and according to the input voltage to keep the output voltage at the required level.

The HT77S11 and HT77S10 have 0.7V start-up voltage, and will consume a typical quiescent current of  $20\mu A.$  A shutdown mode is provided whereby the operating current will be reduced a very low value. The output voltage has two fixed voltages of 3.3V by setting FB to OUT pin and 5V by setting FB to GND pin, but can also be adjusted between a value of 1.8V~5.5V using two external resistors. With internal voltage detector function, the detected voltage can be set by using dividing resistor.

#### **Selection Table**

| Part No. | Current Limit | Package   |  |

|----------|---------------|-----------|--|

| HT77S10  | 1.0A          | 8MSOP/SOP |  |

| HT77S11  | 0.55A         |           |  |

Rev. 1.10 1 March 11, 2010

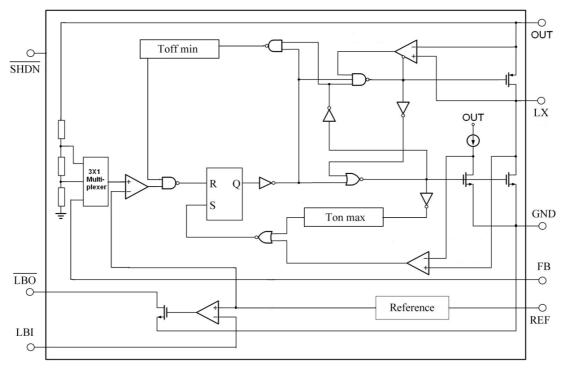

## **Block Diagram**

Note: \* The FB pin is connected to an external resistive divider, OUT or GND pins to set the output voltage.

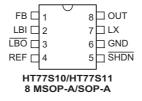

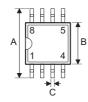

## **Pin Assignment**

## **Pin Descriptions**

| Pin No. | Pin Name | Description                                                                                                                                                                                                                                                                                                                                         |

|---------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | FB       | Feedback Input Pin. This pin is used to select the required output voltage. It can be connected to an external resistor divider for a user selected voltage or to either the OUT or GND pins for a fixed voltage. GND: 5V output OUT: 3.3V output Resistor Divider: 1.8V~5.5V range output                                                          |

| 2       | LBI      | Low-Battery Comparator Input Pin.  This pin is connected to the internal low battery voltage comparator. If the voltage on this pin is less than the REF voltage - nominally 1.3V - then the LBO output will be low.                                                                                                                                |

| 3       | ĪBO      | Open-Drain Low Battery Comparator Output.  This pin is used to indicate a low battery condition and is connected to the low battery voltage comparator output. Note that the pin will be in a high impedence condition when the device is in the shutdown mode.  High Z: V <sub>LBI</sub> > V <sub>REF</sub> 0: V <sub>LBI</sub> < V <sub>REF</sub> |

| 4       | REF      | Reference Voltage Output Pin.  This pin is the output from the voltage reference generator and should be connected to a 0.1µF bypass capacitor.                                                                                                                                                                                                     |

| 5       | SHDN     | Shutdown Input Pin.  This pin is used to power down the device and place it into the shutdown mode.  High: Device in normal operating mode  Low: Device in shutdown mode                                                                                                                                                                            |

| 6       | GND      | Ground Pin.                                                                                                                                                                                                                                                                                                                                         |

| 7       | LX       | Switching Output Pin.  This pin is the device switching output pin which is connected to the internal N-channel and P-channel switching power MOSFET drain pins.                                                                                                                                                                                    |

| 8       | OUT      | Power Output Pin. This pin is the converter output pin. It also supplies bootstrap power to the device.                                                                                                                                                                                                                                             |

## **Absolute Maximum Ratings**

| Supply Voltage0.3V to 7.0V        | Storage Temperature50°C to 125°C |

|-----------------------------------|----------------------------------|

| Operating Temperature40°C to 85°C |                                  |

Note: These are stress ratings only. Stresses exceeding the range specified under "Absolute Maximum Ratings" may cause substantial damage to the device. Functional operation of this device at other conditions beyond those listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability.

Rev. 1.10 3 March 11, 2010

### **Electrical Characteristics**

$V_{IN}\text{=}2V, \, \overline{\text{SHDN}}\text{=}\text{FB=OUT}, \, V_{OUT}\text{=}3.3V, \, \text{refer to figure 1 unless otherwise specified,} \, \, \text{Ta=}25^{\circ}\text{C}$

| Symbol                | Parameter                             | Test C                                                               | onditions | Min.  | Тур.  | Max.  | Unit |

|-----------------------|---------------------------------------|----------------------------------------------------------------------|-----------|-------|-------|-------|------|

| V <sub>IN</sub>       | Operating Input Voltage               | _                                                                    |           |       | _     | 5.5   | V    |

| V <sub>IN-MIN</sub>   | Minimum Input Voltage                 | _                                                                    |           | _     | 0.7   | _     | V    |

| V <sub>IN-START</sub> | Start-up Input Voltage                | R <sub>L</sub> =3kΩ                                                  |           | _     | 0.7   | 0.9   | V    |

|                       |                                       | FB=OUT                                                               |           | 3.17  | 3.30  | 3.43  | V    |

| V <sub>OUT</sub>      | Output Voltage                        | FB=GND                                                               |           | 4.80  | 5.00  | 5.20  | V    |

| 001                   | - Carpan Canaga                       | V <sub>IN</sub> < V <sub>OUT</sub> , FB using two external resistors |           | 1.80  | _     | 5.50  | V    |

| V <sub>REF</sub>      | Reference Voltage                     | I <sub>REF</sub> =0                                                  |           | 1.268 | 1.300 | 1.333 | V    |

| V <sub>REF-LOAD</sub> | Reference Load Regulation             | I <sub>REF</sub> =0 to 1                                             | 50μΑ      | _     | 10    | 30    | mV   |

| V <sub>REF-LINE</sub> | Reference Line Regulation             | V <sub>OUT</sub> = 2V                                                | to 5.5V   | -     | 5     | 10    | mV/V |

| R <sub>DS(ON)</sub>   | Internal PMOS and N-MOS On Resistance | I <sub>L</sub> =100mA                                                |           | _     | 0.3   | _     | Ω    |

| 1                     | Internal NMOS Switch                  | HT77S10                                                              |           | 0.80  | 1.00  | 1.20  | Α    |

| I <sub>LIM</sub>      | Current Limit                         | HT77S11                                                              |           | 0.40  | 0.55  | 0.75  | Α    |

| I <sub>LEAK</sub>     | Internal N-MOS Leakage Current        | V <sub>LX</sub> =4V, V                                               | OUT=5.5V  | _     | 0.05  | 1.00  | μΑ   |

|                       |                                       | FB=OUT                                                               | HT77S10   | 300   | 350   |       | mA   |

| 1                     | Standy State Output Comment           |                                                                      | HT77S11   | 150   | 300   | _     | mA   |

| Гоит                  | Steady-State Output Current           | FB=GND                                                               | HT77S10   | 180   | 230   |       | mA   |

|                       |                                       |                                                                      | HT77S11   | 90    | 160   |       | mA   |

| IQ                    | Quiescent Current                     | V <sub>FB</sub> =1.4V, V <sub>OUT</sub> =3.3V                        |           | 1     | 20    | 35    | μΑ   |

| V <sub>FB</sub>       | FB Input Threshold                    | _                                                                    |           | 1.268 | 1.300 | 1.333 | V    |

| $V_{LBI}$             | LBI Input Threshold                   | _                                                                    |           | 1.268 | 1.300 | 1.333 | V    |

| $V_{\overline{LBO}}$  | LBO Low Output Voltage                | V <sub>LBI</sub> =0, I <sub>SINK</sub> =1mA                          |           | _     | 0.2   | 0.4   | V    |

| I <sub>LBO</sub>      | LBO Off Leakage Current               | V <sub>LBO</sub> =5.5V, V <sub>LBI</sub> =5.5V                       |           | _     | 0.07  | 1.00  | μА   |

| I <sub>SHDN</sub>     | Shutdown Current                      | SHDN=GND                                                             |           | _     | 0.1   | 1     | μА   |

| V <sub>IH</sub>       | SHDN Pin Voltage High                 | _                                                                    |           | 1.5   | _     | _     | V    |

| V <sub>IL</sub>       | SHDN Pin Voltage Low                  | _                                                                    |           | _     |       | 0.4   | V    |

| t <sub>ON(MAX)</sub>  | LX Switch On Time                     | V <sub>FB</sub> =1V, V <sub>OUT</sub> =3.3V                          |           | 2     | 4     | 7     | μS   |

| t <sub>OFF(MIN)</sub> | LX Switch Off Time                    | V <sub>FB</sub> =1V, V <sub>OUT</sub> =3.3V                          |           | 0.6   | 0.9   | 1.4   | μS   |

|                       |                                       | V <sub>OUT</sub> =3.3V, I <sub>O</sub> =200mA                        |           | _     | 90    | _     | %    |

| η                     | Efficiency                            | V <sub>IN</sub> =1.1V,V <sub>OUT</sub> =2.0V,<br>I <sub>O</sub> =1mA |           | _     | 85    | _     | %    |

Note: Absolute maximum ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but do not guarantee specific performance limits. The guaranteed specifications apply only for the test conditions listed.

Specifications are production tested at Ta=25 degree. Specifications over -40 to 85 degree operating temperature range are assured by design.

Rev. 1.10 4 March 11, 2010

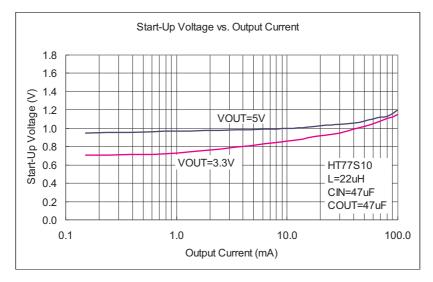

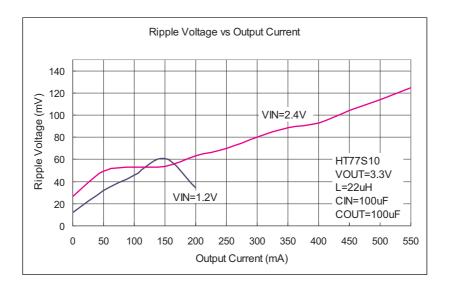

## **Typical Performance Characteristics**

Rev. 1.10 5 March 11, 2010

Rev. 1.10 6 March 11, 2010

#### **Functional Description**

These devices use minimum off-time, current limited pulse-frequency modulation, PFM, techniques for output voltage regulation. The PFM control circuitry acts to control the energy stored in an external inductor to regulate the output voltage to the correct level. Using PFM for control offers the advantages of very low quiescent currents.

The device output voltage is continuously monitored using an internal comparator. The output status of the comparator is then used to determine what action the control logic should take to correct any differences between the actual output voltage and the required voltage. The variable switching frequency depends upon the input voltage and the load demands but can have a frequency of up to 500kHz. The maximum current of the internal NMOS power switching transistor is fixed at 1A for the HT77S10 and 0.55A for the HT77S11.

The switching frequency is controlled by two internal single shot circuits that generate pulses of  $0.9\mu s$  typical minimum off-time and  $4\mu s$  typical maximum on-time. If the circuitry detects that the output voltage is lower than the required voltage, the control circuitry will ensure that more inductor energy is transferred to the load. Refer to the block diagram to see how this regulation is implemented using the following two ON and OFF steps:

#### ON Step

During this step, the NMOS transistor will be switched on which effectively connects the LX pin to ground, and allows energy to build up in the inductor as supplied by VIN. Inductor energy build up is allowed to continue until the inductor current reaches a maximum of 1A for the HT77S10 and 0.55A for the HT77S11 or if the on time exceeds  $4\mu s.$

#### · OFF Step

The energy stored in the inductor during the ON Step is now transferred to the load via the synchronous switch for a minimum time of  $0.9\mu s$ . When the output voltage is less than the required regulated voltage the synchronous switch will switch off which will reduce the inductor current to zero. It is during this cycle that the PMOS power transistor is switched on which shunts its body diode, resulting in enhanced conversion efficiency.

As the design of these devices uses an internal synchronous rectifier, there is no requirement to provide the usual external Schottky diode. This gives users the advantage of smaller circuit board areas and reduced costs.

#### Low Voltage Start-up

These devices can provide a very low start up voltage down to 0.7V. When power is first applied, the synchronous switch will be initially off but energy will be transferred to the load through its intrinsic body diode.

### Voltage Reference

The internal voltage reference circuit supplies a nominal voltage of 1.3V on the REF pin. Up to  $150\mu A$  can be sourced on this pin for use by external circuits. The reference voltage provided here offers excellent load regulation characteristics, however a bypass capacitor of  $0.1\mu F$  should be connected for proper operation.

#### Shutdown

During normal device operation, the SHDN pin should be either high or connected to the OUT pin. When the device is in the shutdown mode, that is when the SHDN pin is pulled low, the internal circuitry will be switched off, thus reducing the current demands on the VIN power source. During shutdown, the PMOS power transistor body diode will allow current to flow from VIN to VOUT, therefore VOUT falls to a value of approximately VIN - 0.6V

#### **Low Battery Detection**

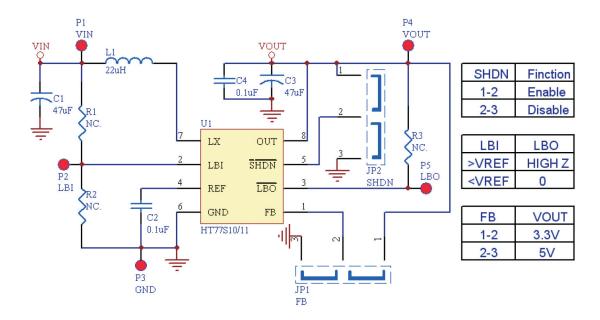

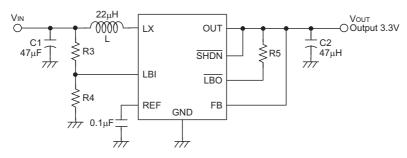

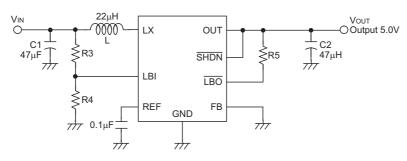

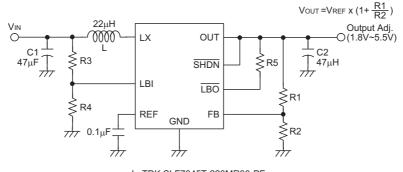

A low battery detector function is provided in the device using an internal comparator. The output pin LBO is the output and input pin LBI is the input for this function. As this is an open-drain NMOS type output, it is usually necessary to connect an external pull-high resistor for proper use. This pin can be pulled-high up to a voltage of 6V independently of the OUT pin voltage. When the voltage on LBI is higher than the threshold voltage, the LBO output will be high impedance. If the low battery detection function is not used, the LBI and LBO pins should be grounded. The LBI threshold voltage is set using two external resistors, R3 and R4. The R3 and R4 ratio can be calculated using the following equation. See Figure 1, Figure 2 and Figure 3:

$$\frac{R3}{R4} = \frac{V_{IN}}{V_{REF}} - 1$$

Where

V<sub>IN</sub> = Input Voltage, V<sub>IN</sub> > V<sub>REF</sub> Reference Voltage V<sub>REF</sub> = 1.3V

### **Application Information**

#### **Output Voltage Selection**

The required output voltage is controlled using the FB pin. Two fixed voltages of 3.3V and 5V are available or an adjustable output voltage which is set using an external resistor divider.

| VOUT           | FB pin                                                                                     |

|----------------|--------------------------------------------------------------------------------------------|

| 3.3V           | Connect OUT                                                                                |

| 5.0V           | Connect to GND                                                                             |

| 1.8V≤VOUT≤5.5V | Connect to resistive divider (Figure.3) $V_{OUT} = V_{REF} \left(1 + \frac{R1}{R2}\right)$ |

#### Where

V<sub>REF</sub>= Reference Voltage is 1.3V

A recommended value for R2 is 240kΩ.

#### Inductor Selection

Selecting a suitable inductor is an important consideration as it is usually a compromise situation between the output current requirements, the inductor saturation limit and the acceptable output voltage ripple. Lower values of inductor values can provide higher output currents but will suffer from higher ripple voltages and reduced efficiencies. Higher inductor values can provide reduced output ripple voltages and better efficiencies, but will be limited in their output current capabilities. For all inductors it must be noted however that lower core losses and lower DC resistance values will always provide higher efficiencies.

The peak inductor current can be calculated using the following equation:

$$IL(\textit{PEAK}) = \frac{\textit{Vout} \times \textit{Io}}{\textit{Vin} \times \eta} + \frac{\textit{Vin} \times (\textit{Vout} - \textit{Vin}) \times \textit{Ts}}{2 \times \textit{Vout} \times L}$$

Where

$V_{IN}$  = Input Voltage  $V_{OUT}$  = Output Voltage  $I_{O}$  = Output Current  $\eta$  = Efficiency Ts = Period L = Inductor

### **Capacitor Selection**

As the output capacitor selected affects both efficiency and output ripple voltage, it must be chosen with care to achieve best results from the converter. Output voltage ripple is the product of the peak inductor current and the output capacitor equivalent series resistance or ESR for short. It is important that low ESR value capacitors are used to achieve optimum performance. One method to achieve low ESR values is to connect two or more filter capacitors in parallel. The capacitors values and rated voltages are only suggested values.

### **Layout Guidelines**

Good PCB layout is an extremely important factor is ensuring the optimum performance from switching regulator converters. Poorly thought out circuit layout can result in related noise problems. In order to minimise both EMI and switching noise, the follow guidelines should be followed:

- All tracks should be as short and wide as possible

- All components must be located as close to the IC as possible

- A star ground connection should be used to connect the input capacitor, C1, output capacitors, C3 and C4, and the IC GND pin

- Feedback resistors must be kept close as close to the FB pin as possible to limit the possibility of noise injection onto the PCB track connected to the FB pin

- A full ground plane will do much to enhance EMI performance

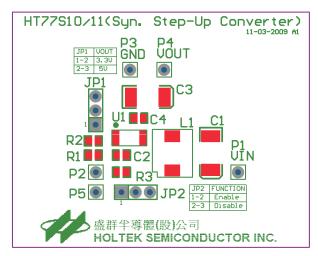

A demo board schematic and layout is provided for consultation below:

Rev. 1.10 9 March 11, 2010

**TopOverlay View**

**TopLayer View**

**BottomLayer View**

### **Application Circuits**

### V<sub>OUT</sub>=3.3V

L: TDK SLF7045T-220MR90-PF C1, C2: Vishay 593D476X9016C2

Figure 1

## V<sub>OUT</sub>=5.0V

L: TDK SLF7045T-220MR90-PF C1, C2: Vishay 593D476X9016C2

Figure 2

### V<sub>OUT</sub>=1.8V~5.5V

L: TDK SLF7045T-220MR90-PF C1, C2: Vishay 593D476X9016C2

Figure 3

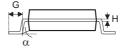

# Package Information

## 8-pin SOP (150mil) Outline Dimensions

## • MS-012

| Compleal | Dimensions in inch |       |       |  |

|----------|--------------------|-------|-------|--|

| Symbol   | Min.               | Nom.  | Max.  |  |

| Α        | 0.228              | _     | 0.244 |  |

| В        | 0.150              | _     | 0.157 |  |

| С        | 0.012              | _     | 0.020 |  |

| C'       | 0.188              | _     | 0.197 |  |

| D        | _                  | _     | 0.069 |  |

| E        | _                  | 0.050 | _     |  |

| F        | 0.004              |       | 0.010 |  |

| G        | 0.016              | _     | 0.050 |  |

| Н        | 0.007              | _     | 0.010 |  |

| α        | 0°                 | _     | 8°    |  |

| Cumb al | Dimensions in mm |          |      |  |

|---------|------------------|----------|------|--|

| Symbol  | Min.             | Nom.     | Max. |  |

| A       | 5.79             | _        | 6.20 |  |

| В       | 3.81             | _        | 3.99 |  |

| С       | 0.30             |          | 0.51 |  |

| C'      | 4.78             | _        | 5.00 |  |

| D       | _                |          | 1.75 |  |

| Е       | _                | 1.27     | _    |  |

| F       | 0.10             | _        | 0.25 |  |

| G       | 0.41             |          | 1.27 |  |

| Н       | 0.18             | _        | 0.25 |  |

| α       | 0°               | <u> </u> | 8°   |  |

Rev. 1.10 12 March 11, 2010

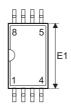

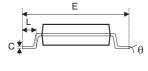

## 8-pin MSOP Outline Dimensions

### • MO-187

| Complete | Dimensions in inch |       |       |

|----------|--------------------|-------|-------|

| Symbol   | Min.               | Nom.  | Max.  |

| А        | _                  | _     | 0.043 |

| A1       | 0.000              | _     | 0.006 |

| A2       | 0.030              | _     | 0.037 |

| В        | 0.009              | _     | 0.013 |

| С        | 0.003              | _     | 0.009 |

| D        | _                  | 0.012 | _     |

| E        | _                  | 0.193 | _     |

| E1       | _                  | 0.118 | _     |

| е        | _                  | 0.026 | _     |

| L        | 0.016              | _     | 0.031 |

| L1       | _                  | 0.037 | _     |

| у        | _                  | _     | 0.004 |

| θ        | 0°                 | _     | 8°    |

| Comple al | Dimensions in mm |      |      |  |

|-----------|------------------|------|------|--|

| Symbol    | Min.             | Nom. | Max. |  |

| Α         | _                | _    | 1.10 |  |

| A1        | 0.00             | _    | 0.15 |  |

| A2        | 0.75             | _    | 0.95 |  |

| В         | 0.22             | _    | 0.33 |  |

| С         | 0.08             | _    | 0.23 |  |

| D         | _                | 3.00 | _    |  |

| E         | _                | 4.90 | _    |  |

| E1        | _                | 3.00 | _    |  |

| е         | _                | 0.65 | _    |  |

| L         | 0.40             | _    | 0.80 |  |

| L1        | _                | 0.95 | _    |  |

| у         | _                | _    | 0.10 |  |

| θ         | 0°               | _    | 8°   |  |

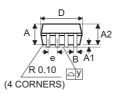

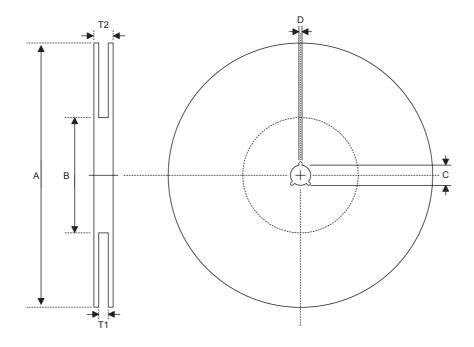

# **Product Tape and Reel Specifications**

## **Reel Dimensions**

## SOP 8N

| Symbol | Description           | Dimensions in mm |

|--------|-----------------------|------------------|

| Α      | Reel Outer Diameter   | 330.0±1.0        |

| В      | Reel Inner Diameter   | 100.0±1.5        |

| С      | Spindle Hole Diameter | 13.0 +0.5/-0.2   |

| D      | Key Slit Width        | 2.0±0.5          |

| T1     | Space Between Flange  | 12.8 +0.3/-0.2   |

| T2     | Reel Thickness        | 18.2±0.2         |

Rev. 1.10 14 March 11, 2010

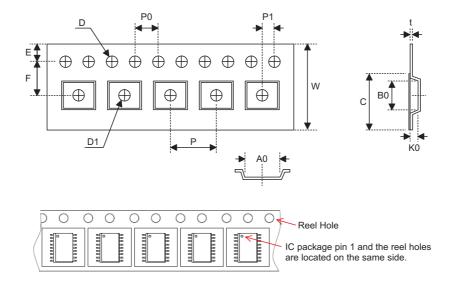

## **Carrier Tape Dimensions**

SOP 8N

| Symbol | Description                              | Dimensions in mm |

|--------|------------------------------------------|------------------|

| W      | Carrier Tape Width                       | 12.0 +0.3/-0.1   |

| Р      | Cavity Pitch                             | 8.0±0.1          |

| E      | Perforation Position                     | 1.75±0.1         |

| F      | Cavity to Perforation (Width Direction)  | 5.5±0.1          |

| D      | Perforation Diameter                     | 1.55±0.1         |

| D1     | Cavity Hole Diameter                     | 1.50 +0.25/-0.00 |

| P0     | Perforation Pitch                        | 4.0±0.1          |

| P1     | Cavity to Perforation (Length Direction) | 2.0±0.1          |

| A0     | Cavity Length                            | 6.4±0.1          |

| В0     | Cavity Width                             | 5.2±0.1          |

| K0     | Cavity Depth                             | 2.1±0.1          |

| t      | Carrier Tape Thickness                   | 0.30±0.05        |

| С      | Cover Tape Width                         | 9.3±0.1          |

Rev. 1.10 15 March 11, 2010

Holtek Semiconductor Inc. (Headquarters)

No.3, Creation Rd. II, Science Park, Hsinchu, Taiwan Tel: 886-3-563-1999 Fax: 886-3-563-1189 http://www.holtek.com.tw

### Holtek Semiconductor Inc. (Taipei Sales Office)

4F-2, No. 3-2, YuanQu St., Nankang Software Park, Taipei 115, Taiwan

Tel: 886-2-2655-7070 Fax: 886-2-2655-7373

Fax: 886-2-2655-7383 (International sales hotline)

#### Holtek Semiconductor Inc. (Shenzhen Sales Office)

5F, Unit A, Productivity Building, No.5 Gaoxin M 2nd Road, Nanshan District, Shenzhen, China 518057 Tel: 86-755-8616-9908, 86-755-8616-9308

Fax: 86-755-8616-9722

### Holtek Semiconductor (USA), Inc. (North America Sales Office)

46729 Fremont Blvd., Fremont, CA 94538

Tel: 1-510-252-9880 Fax: 1-510-252-9885 http://www.holtek.com

### Copyright © 2010 by HOLTEK SEMICONDUCTOR INC.

The information appearing in this Data Sheet is believed to be accurate at the time of publication. However, Holtek assumes no responsibility arising from the use of the specifications described. The applications mentioned herein are used solely for the purpose of illustration and Holtek makes no warranty or representation that such applications will be suitable without further modification, nor recommends the use of its products for application that may present a risk to human life due to malfunction or otherwise. Holtek's products are not authorized for use as critical components in life support devices or systems. Holtek reserves the right to alter its products without prior notification. For the most up-to-date information, please visit our web site at http://www.holtek.com.tw.

Rev. 1.10 March 11, 2010