## IXZ4DF18N50 RF Power MOSFET & DRIVER

# Driver / MOSFET Combination DEIC-515 Driver combined with IXZ318N50 MOSFET Gate driver matched to MOSFET

#### **Features**

- · Isolated substrate

- high isolation voltage (>2500V)

- excellent thermal transfer

- Increased temperature and power cycling capability

- IXYS advanced Z-MOS process

- Low R<sub>ds(ON)</sub>

- Very low insertion inductance(<2nH)</li>

- No beryllium oxide (BeO) or other hazardous materials

- Built using the advantages and compatibility of CMOS and IXYS HDMOS™ processes

- · Latch-up protected

- · Low quiescent supply current

#### **Advantages**

- · Optimized for RF and high speed

- · Easy to mount—no insulators needed

- · High power density

- Single package reduces size and heat sink area

#### 500 Volts 19 A 0.29 Ohms

#### **Applications**

- Class D or E Switching Amplifier

- Multi MHz Switch Mode Power Supplies (SMPS)

#### **Description**

The IXZ4DF18N50 is a CMOS high speed high current gate driver and ZMOS MOSFET combination specifically designed Class D and E HF RF applications at up to 40MHz, as well as other applications. The IXZ4DF18N50 in pulse mode can provide 95A of peak current while producing voltage rise and fall times of less than 4ns, and minimum pulse widths of 8ns. The input of the driver is fully immune to latch up over the entire operating range. Designed with small internal delays, the IXZ4DF18N50 is suitable for higher power operation where combiners are used. Its features and wide safety margin in operating voltage and power make the IXZ4DF18N50 unmatched in performance and value.

The IXZ4DF18N50 is packaged in DEI's low inductance RF package incorporating DEI's RF layout techniques to minimize stray lead inductances for optimum switching performance. The IXZ4DF18N50 is a surface-mountable device.

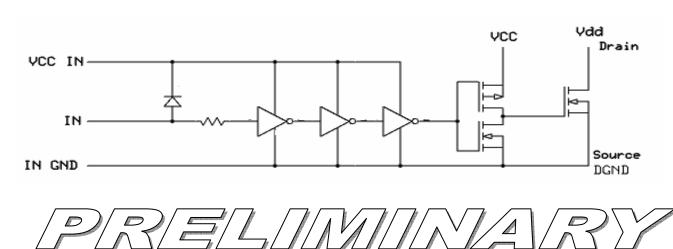

Figure 1. Functional Diagram

## **Device Specifications**

| Parameter                    | Value          |

|------------------------------|----------------|

| Maximum Junction Temperature | 150°C          |

| Operating Temperature Range  | - 40°C to 85°C |

| Weight                       | 5.5g           |

| Symbol                 | Test Conditions                 | Maximum<br>Ratings |

|------------------------|---------------------------------|--------------------|

| fmax                   | ID = 0.5IDM25                   | 40MHz              |

| VDSS                   |                                 | 500V               |

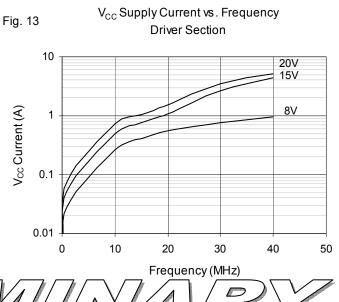

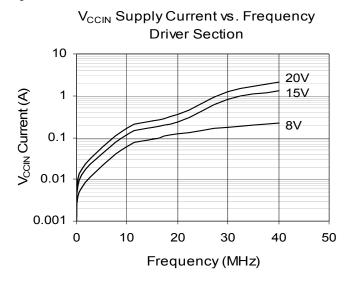

| Vcc, Vccin             |                                 | 20V                |

| lace                   | Vps = 0.8Vpss                   | 50uA               |

| IDSS                   | VGS = 0V $TJ = 125C$            | 1mA                |

| IDM25                  | Tc = 25°C                       | 19A                |

| Ірм                    | Tc = 25°C, Pulse limited by Тлм | 95A                |

| lar                    | Tc = 25°C                       | 19A                |

| PT (MOSFET and Driver) | Tc = 25°C                       | 500 W              |

| RthJC                  |                                 | 0.25 °C/W          |

| RthJHS                 |                                 | TBD °C/W           |

#### **Device Performance**

| Symbol                   | Test Condition                                                                          | Minimum               | Typical | Maximum    |

|--------------------------|-----------------------------------------------------------------------------------------|-----------------------|---------|------------|

| Rds(ON)                  | $V_{CC}$ = 15 V, $I_D$ = 0.5 $I_{DM25}$<br>Pulse Test, t ≤ 300 $\mu$ S, Duty Cycle ≤ 2% |                       | 0.29 Ω  |            |

| Vcc, Vccin               |                                                                                         | 8V                    | 15V     | 20V        |

| IN (Signal Input)        |                                                                                         | - 5V                  |         | Vccin+0.3V |

| VIH (High Input Voltage) |                                                                                         | V <sub>CCIN</sub> -2V |         | Vccin+0.3V |

| VIL (Low Input Voltage)  |                                                                                         |                       | 0.8V    |            |

| ZIN                      | f = 1MHz                                                                                |                       | 7960 Ω  |            |

| Cstray                   | f = 1MHz Any one pin to the back plane metal                                            |                       | 46pf    |            |

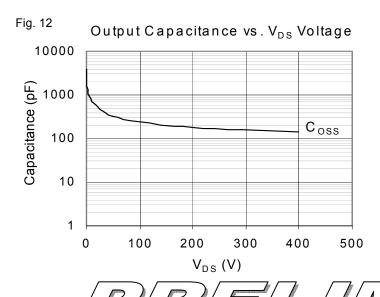

| Coss                     | $V_{GS} = 0V$ , $V_{DS} = 0.8V_{DSS}(max)$ , $f = 1MHz$                                 |                       | 139pf   |            |

| tondly                   | T <sub>C</sub> = 25°C                                                                   |                       | 17 nS   |            |

| <b>t</b> offdly          | $V_{CC}$ , $V_{CCIN}$ , $V_{IN}$ = 15V, 1μS Pulse, $V_{DS}$ = 50V, $R_L$ = 5.0Ω         |                       | 26 nS   |            |

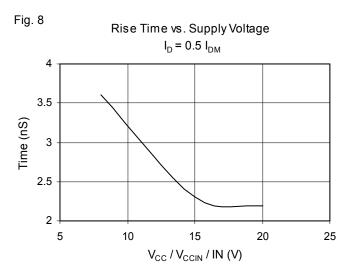

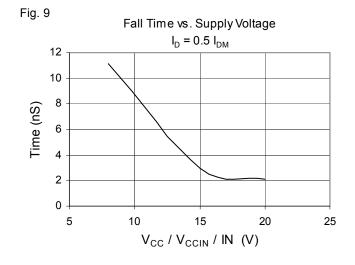

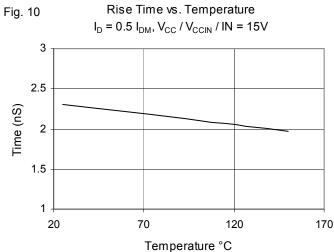

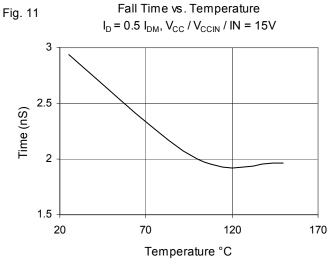

| <b>t</b> R               | T <sub>C</sub> = 25°C                                                                   |                       | 3 nS    |            |

| tr                       | $V_{CC}$ , $V_{CCIN}$ , $V_{IN}$ = 15V,1μS Pulse,<br>$V_{DS}$ = 50V, $R_L$ = 5.0Ω       |                       | 3 nS    |            |

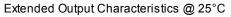

Fig. 2

Fig. 3

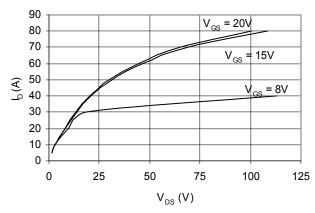

$R_{DS(ON)}$  vs. Temperature  $I_D = 0.5 I_{DM}$

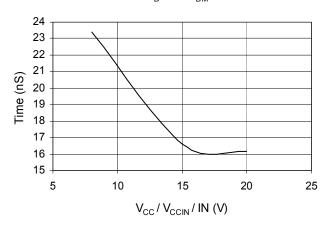

Fig. 4 Propagation Delay ON vs. Supply Voltage  $I_D = 0.5 I_{DM}$

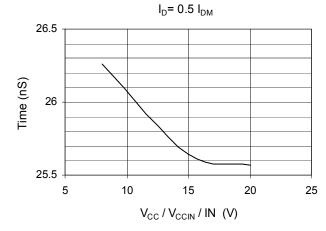

Fig. 5 Propagation Delay OFF vs. Supply Voltage

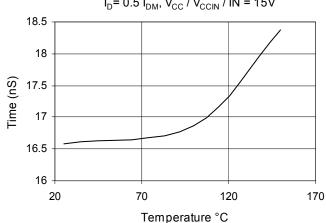

Fig. 6 Propagation Delay ON vs. Temperature  $I_D = 0.5 I_{DM}, V_{CC} / V_{CCIN} / IN = 15V$

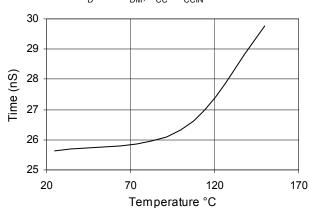

Fig. 7 Propagation Delay OFF vs. Temperature  $I_D = 0.5 I_{DM}, V_{CC} / V_{CCIN} / IN = 15V$

Fig. 14

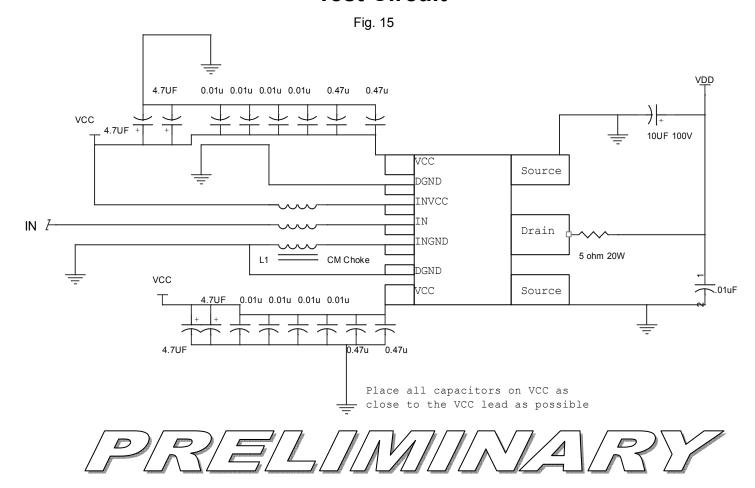

## **Test Circuit**

#### **Lead Description**

| SYMBOL | FUNCTION      | DESCRIPTION                                                                                                                                                                                                           |

|--------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Drain  | MOSFET Drain  | Drain of Power MOSFET.                                                                                                                                                                                                |

| Source | MOSFET Source | Source of Power MOSFET. This connection is common to DGND.                                                                                                                                                            |

| VCC    |               | Power supply input for the driver output section. These leads provide power to the output section of the DEIC515 driver. Both leads must be connected.                                                                |

| VCCIN  |               | Input for the positive input section power-supply voltage. This lead provide power to the input section of the DEIC515 driver. This lead should not be directly connected to VCC.                                     |

| IN     | Input         | Input signal.                                                                                                                                                                                                         |

| DGND   | Power Driver  | The system ground leads. Internally connected to all circuitry, these leads provide ground reference for the entire chip. These leads should be connected to a low noise analog ground plane for optimum performance. |

| INGND  |               | The input section ground lead. This lead is a Kelvin connection internally connected to DGND. This lead must not be connected to DGND as excessive current can damage this lead.                                      |

IXYS RF reserves the right to change limits, test conditions and dimensions without notice. IXYS RF MOSFETS are covered by one or more of the following U.S. patents:

4,835,592 4,860,072 4,881,106 4,891,686 4,931,844 5,017,508 5,034,796 5,049,961 5,063,307 5,187,117 5,237,481 5,486,715 5,381,025 5,640,045 6,404,065 6,583,505 6,710,463 6,727,585 6,731,002

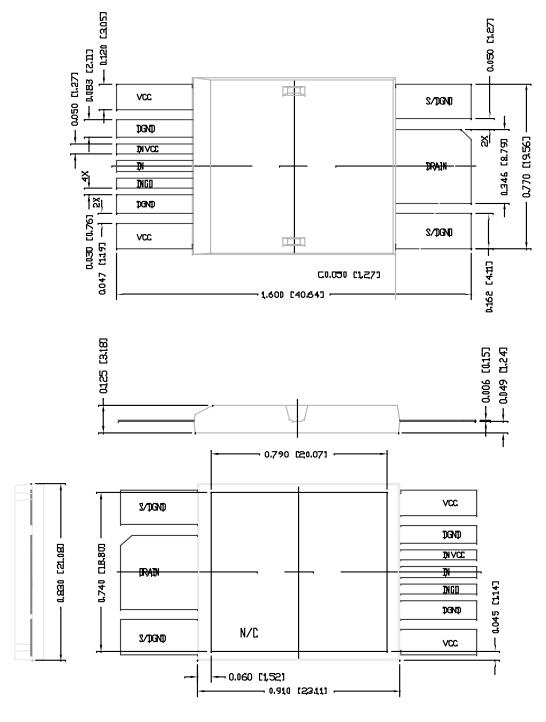

Fig. 16 IXZ4DF18N50 Package Outline

IXYS RF An IXYS Company 2401 Research Blvd. Ste. 108, Ft. Collins, CO 80526 Tel: 970-493-1901; Fax: 970-493-1903 e-mail: deiinfo@directedenergy.com www.directedenergy.com