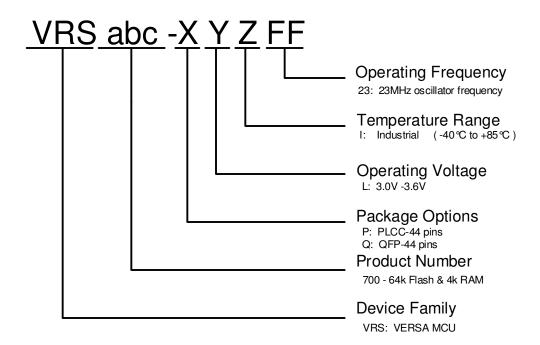

# VERSA 700: 64kB FLASH, 4kB RAM 23MHz, 3V, 8-Bit MCU

**Datasheet Rev 1.3**

# Overview

The VRS700 is a 3V, 8-bit microcontroller with 64kB of Flash memory and 4K RAM that is based on the architecture of the standard 80C51 microcontroller family. It is pin compatible with these devices.

Among the VRS700's features are 8 PWM outputs, a Watch Dog Timer, bank mapping to permit direct addressing of the 4096 bytes of RAM and a serial port.

The VRS700's hardware features and powerful instruction set make it a versatile and cost-effective controller for a wide range of applications requiring a microcontroller running at 3V.

The Flash memory can be programmed using programmers available from Goal Semiconductor or other 3<sup>rd</sup> party commercial programmers.

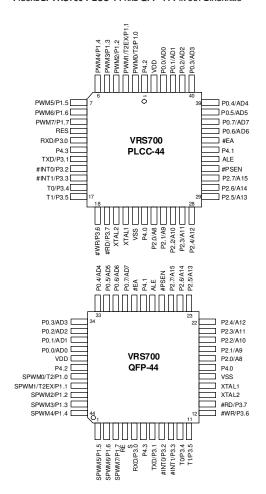

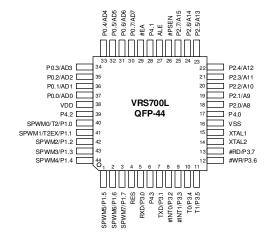

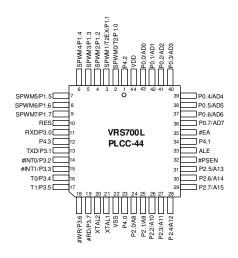

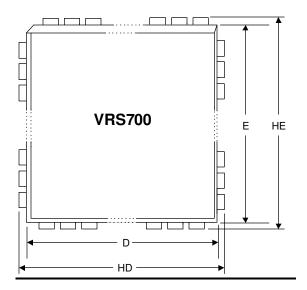

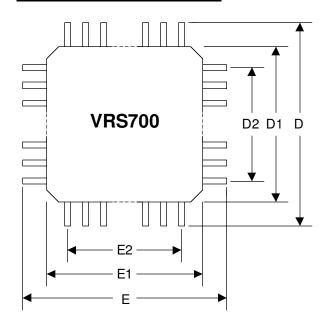

The VRS700 is available in PLCC-44 and QFP-44 packages in the Industrial Temperature Range.

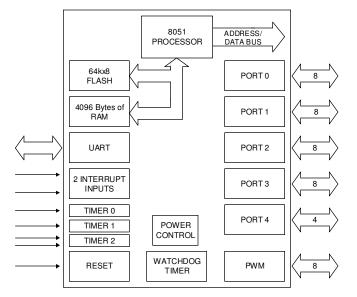

FIGURE 1: VRS700 BLOCK DIAGRAM

## **Features**

- Operating voltage: 3.0V ~ 3.6V

- General 80C51/80C52 family compatible

- 64kB on-chip Flash memory

- 4096 bytes on-chip data RAM

- Bank mapping direct addressing mode to access RAM

- Four 8-bit I/O ports + one 4-bit I/O port

- 8-Channel PWM on P1.0~P1.7

- Full duplex serial port (UART)

- Three 16-bit Timers/Counters

- Watch Dog Timer

- 8-bit Unsigned Multiply and Division Instructions

- BCD arithmetic

- Direct and Indirect Addressing

- Two levels of Interrupt Priority and Nested Interrupts

- Power saving modes

- Code protection functions

- Operates at a clock frequency from 3MHz to 23MHz

- Low EMI (inhibit ALE)

- Industrial Temperature Range (-40°C to +85°C)

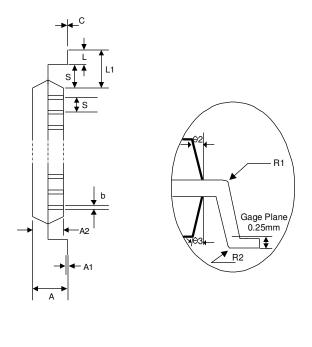

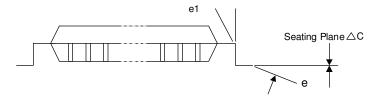

FIGURE 2: VRS700 PLCC-44 AND QFP-44 PIN OUT DIAGRAMS

Datasheet Rev 1.3

# Pin Descriptions for QFP-44/PLCC-44

TABLE 1: PIN DESCRIPTIONS FOR QFP-44/PLCC-44

| QFP<br>- 44 | PLCC<br>- 44 | Name  | I/O | Function                          |

|-------------|--------------|-------|-----|-----------------------------------|

| 1           | 7            | SPWM5 | 0   | SPWM Channel 5                    |

| ļ           | /            | P1.5  | l/O | Bit 5 of Port 1                   |

| 2           | 8            | SPWM6 | 0   | SPWM Channel 6                    |

| 2           | 0            | P1.6  | VO. | Bit 6 of Port 1                   |

| 3           | 9            | SPWM7 | 0   | SPWM Channel 7                    |

| 3           | 9            | P1.7  | 1/0 | Bit 7 of Port 1                   |

| 4           | 10           | RES   | 1   | Reset                             |

| 5           | 11           | RXD   | ı   | Receive Data                      |

| 3           | - ' '        | P3.0  | I/O | Bit 0 of Port 3                   |

| 6           | 12           | P4.3  | I/O | Bit 3 of Port 4                   |

| 7           | 13           | TXD   | 0   | Transmit Data &                   |

| ,           | 13           | P3.1  | VO. | Bit 1 of Port 3                   |

| 8           | 14           | #INT0 | I   | Low True Interrupt 0              |

| O .         | 17           | P3.2  | I/O | Bit 2 of Port 3                   |

| 9           | 15           | #INT1 | 1   | Low True Interrupt 1              |

| 9           | 13           | P3.3  | I/O | Bit 3 of Port 3                   |

| 10          | 16           | T0    | I   | Timer 0                           |

| 10          | 10 10        | P3.4  | VO. | Bit 4 of Port 3                   |

| 11          | 17           | T1    | 1   | Timer 1 & 3                       |

| 11          | 1 17         | P3.5  | I/O | Bit 5 of Port 3                   |

| 12          | 18           | #WR   | 0   | Ext. Memory Write                 |

| 12          | 10           | P3.6  | I/O | Bit 6 of Port 3                   |

| 13          | 19           | #RD   | 0   | Ext. Memory Read                  |

| 13          | 19           | P3.7  | VO. | Bit 7 of Port 3                   |

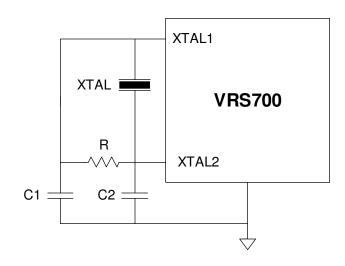

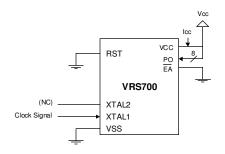

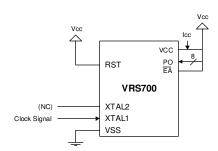

| 14          | 20           | XTAL2 | 0   | Oscillator/Crystal Output         |

| 15          | 21           | XTAL1 | 1   | Oscillator/Crystal In             |

| 16          | 22           | VSS   | -   | Ground                            |

| 17          | 23           | P4.0  | I/O | Bit 0 of Port 4                   |

| 18          | 24           | P2.0  | I/O | Bit 0 of Port 2                   |

| 10          | 24           | A8    | 0   | Bit 8 of External Memory Address  |

| 19          | 25           | P2.1  | I/O | Bit 1 of Port 2                   |

| 13          | 20           | A9    | 0   | Bit 9 of External Memory Address  |

| 20          | 26           | P2.2  | I/O | Bit 2 of Port 2                   |

| 20          | 20           | A10   | 0   | Bit 10 of External Memory Address |

| 21          | 27           | P2.3  | I/O | Bit 3 of Port 2 &                 |

| <u> </u>    | 21           | A11   | 0   | Bit 11 of External Memory Address |

| 22          | 28           | P2.4  | I/O | Bit 4 of Port 2                   |

| 22          | 20           | A12   | 0   | Bit 12 of External Memory Address |

| 23          | 29           | P2.5  | I/O | Bit 5 of Port 2                   |

| 23          | 29           | A13   | 0   | Bit 13 of External Memory Address |

| QFP<br>- 44 | PLCC<br>- 44 | Name  | I/O | Function                              |

|-------------|--------------|-------|-----|---------------------------------------|

|             |              | P2.6  | VO. | Bit 6 of Port 2                       |

| 24          | 30           | A14   | 0   | Bit 14 of External Memory Address     |

| 25          | 31           | P2.7  | VO. | Bit 7 of Port 2                       |

| 25          | 31           | A15   | 0   | Bit 15 of External Memory Address     |

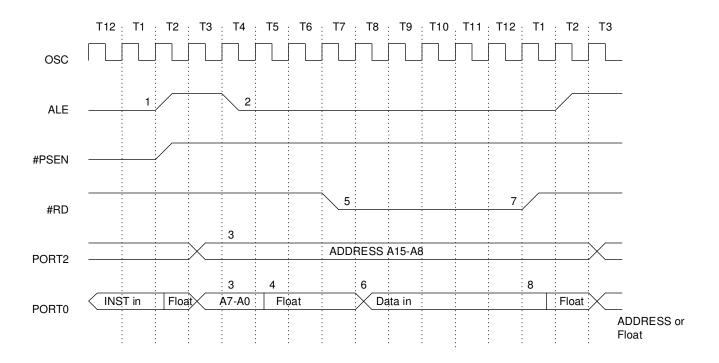

| 26          | 32           | #PSEN | 0   | Program Store Enable                  |

| 27          | 33           | ALE   | 0   | Address Latch Enable                  |

| 28          | 34           | P4.1  | VO. | Bit 1 of Port 4                       |

| 29          | 35           | #EA   | 1   | External Access                       |

| 30          | 36           | P0.7  | VO  | Bit 7 Of Port 0                       |

| 30          | 36           | AD7   | I/O | Data/Address Bit 7 of External Memory |

| 31          | 37           | P0.6  | 1/0 | Bit 6 of Port 0                       |

| 31          | 37           | AD6   | I/O | Data/Address Bit 6 of External Memory |

| 32          | 38           | P0.5  | 1/0 | Bit 5 of Port 0                       |

| 32          | 30           | AD5   | 1/0 | Data/Address Bit 5 of External Memory |

| 33          | 39           | P0.4  | VO  | Bit 4 of Port 0                       |

| 33          | 39           | AD4   | I/O | Data/Address Bit 4 of External Memory |

| 24          | 34 40        | P0.3  | VO  | Bit 3 Of Port 0                       |

| 34          |              | AD3   | I/O | Data/Address Bit 3 of External Memory |

| 35          | 41           | P0.2  | VO  | Bit 2 of Port 0                       |

| 33          | 41           | AD2   | I/O | Data/Address Bit 2 of External Memory |

| 36          | 42           | P0. 1 | VO  | Bit 1 of Port 0 & Data                |

| 30          | 42           | AD1   | 1/0 | Address Bit 1 of External Memory      |

| 37          | 43           | P0.0  | VO  | Bit 0 Of Port 0 & Data                |

| 37          | 43           | AD0   | I/O | Address Bit 0 of External Memory      |

| 38          | 44           | VDD   | -   | VCC                                   |

| 39          | 1            | P4.2  | VO  | Bit 2 of Port 4                       |

|             |              | T2    | 1   | Timer 2 Clock Out                     |

| 40          | 2            | P1.0  | VO. | Bit 0 of Port 1                       |

|             |              | SPWM0 | 0   | SPWM Channel 0                        |

|             |              | T2EX  | I   | Timer 2 Control                       |

| 41          | 3            | P1.1  | VO  | Bit 1 of Port 1                       |

|             |              | SPWM1 | 0   | SPWM Channel 1                        |

| 42          | 4            | P1.2  | 1/0 | Bit 2 of Port 1                       |

| 42          | 4            | SPWM2 | 0   | SPWM Channel 2                        |

|             |              | P1.3  | VO  | Bit 3 of Port 1                       |

| 43          | 5            | SPWM3 | 0   | SPWM Channel 3                        |

| 44          | 6            | P1.4  | VO  | Bit 4 of Port 1                       |

| 44          | U            | SPWM4 | 0   | SPWM Channel 4                        |

Datasheet Rev 1.3

# **Instruction Set**

All VRS700 instructions are binary code compatible and perform the same functions as the industry standard 8051. The following two tables describe the instruction set of the VRS700.

TABLE 2: LEGEND FOR INSTRUCTION SET TABLE

| Symbol   | Function                                               |

|----------|--------------------------------------------------------|

| A        | Accumulator                                            |

| Rn       | Register R0-R7                                         |

| Direct   | Internal register address                              |

| @Ri      | Internal register pointed to by R0 or R1 (except MOVX) |

| rel      | Two's complement offset byte                           |

| bit      | Direct bit address                                     |

| #data    | 8-bit constant                                         |

| #data 16 | 16-bit constant                                        |

| addr 16  | 16-bit destination address                             |

| addr 11  | 11-bit destination address                             |

TABLE 3: VERSA 700 INSTRUCTION SET

| Mnemonic                       | Description                              | Size<br>(bytes) | Instr. Cycles |

|--------------------------------|------------------------------------------|-----------------|---------------|

| Arithmetic instruction         |                                          |                 |               |

| ADD A, Rn                      | Add register to A                        | 1               | 1             |

| ADD A, direct                  | Add direct byte to A                     | 2               | 1             |

| ADD A, @Ri                     | Add data memory to A                     | 1               | 1             |

| ADD A, #data                   | Add immediate to A                       | 2               | 1             |

| ADDC A, Rn                     | Add register to A with carry             | 1               | 1             |

| ADDC A, direct                 | Add direct byte to A with carry          | 2               | 1             |

| ADDC A, @Ri                    | Add data memory to A with carry          | 1               | 1             |

| ADDC A, #data                  | Add immediate to A with carry            | 2               | 1             |

| SUBB A, Rn                     | Subtract register from A with borrow     | 1               | 1             |

| SUBB A, direct                 | Subtract direct byte from A w ith borrow | 2               | 1             |

| SUBB A, @Ri                    | Subtract data mem from A with borrow     | 1               | 11            |

| SUBB A, #data                  | Subtract immediate from A with borrow    | 2               | 1             |

| INC A                          | Increment A                              | 1               | 1             |

| INC Rn                         | Increment register                       | 1               | 1             |

| INC direct                     | Increment direct byte                    | 2               | 1             |

| INC@Ri                         | Increment data memory                    | 1               | 1             |

| DEC A                          | Decrement A                              | 1               | 1             |

| DEC Rn                         | Decrement register                       | 1               | 1             |

| DEC direct                     | Decrement direct byte                    | 2               | 1             |

| DEC @Ri                        | Decrement data memory                    | 1               | 1             |

| INC DPTR                       | Increment data pointer                   | 1               | 2             |

| MUL AB                         | Multiply A by B Divide A by B            | 1               | 4             |

| DIV AB                         |                                          | 1               | 4             |

|                                | Decimal adjust A                         | 1               | 1             |

| Logical Instructions ANL A, Rn | AND register to A                        | 1               | 1             |

| ANL A, direct                  | AND direct byte to A                     | 2               | 1             |

| ANL A, @Ri                     | AND data memory to A                     | 1               | 1             |

| ANL A, @ Al                    | AND immediate to A                       | 2               | 1             |

| ANL direct, A                  | AND A to direct byte                     | 2               | 1             |

| ANL direct, #data              | AND immediate data to direct byte        | 3               | 2             |

| ORL A, Rn                      | OR register to A                         | 1               | 1             |

| ORL A, direct                  | OR direct byte to A                      | 2               | <u> </u>      |

| ORL A, @Ri                     | OR data memory to A                      | 1               | <u>·</u>      |

| ORL A, #data                   | OR immediate to A                        | 2               | 1             |

| ORL direct, A                  | ORA to direct byte                       | 2               | 1             |

| ORL direct, #data              | OR immediate data to direct byte         | 3               | 2             |

| XRL A, Rn                      | Exclusive-OR register to A               | 1               | 1             |

| XRL A, direct                  | Exclusive-OR direct byte to A            | 2               | 1             |

| XRL A, @Ri                     | Exclusive-OR data memory to A            | 1               | 1             |

| XRL A, #data                   | Exclusive-OR immediate to A              | 2               | 1             |

| XRL direct, A                  | Exclusive-OR A to direct byte            | 2               | 1             |

| XRL direct, #data              | Exclusive-OR immediate to direct byte    | 3               | 2             |

| CLR A                          | Clear A                                  | 1               | 1             |

| Mnemonic                             | Description                                                   | Size<br>(bytes)                              | Instr. Cycles                         |

|--------------------------------------|---------------------------------------------------------------|----------------------------------------------|---------------------------------------|

| CPL A                                | Compliment A                                                  | 1                                            | 1                                     |

| SWAP A                               | Sw ap nibbles of A                                            | 1                                            | 1                                     |

| RL A                                 | Rotate A left                                                 | 1                                            | 1                                     |

| RLC A                                | Rotate A left through carry                                   | 1                                            | <u>·</u><br>1                         |

| RR A                                 | Rotate A right                                                | 1                                            | <br>1                                 |

| RRC A                                | Rotate A right through carry                                  | 1                                            | 1                                     |

| Data Transfer Instruc                |                                                               | <u> </u>                                     | · · · · · · · · · · · · · · · · · · · |

| MOV A, Rn                            | Move register to A                                            | 1                                            | 1                                     |

| MOV A, direct                        | Move direct byte to A                                         | 2                                            | <u> </u>                              |

| MOV A, @Ri                           | Move data memory to A                                         | 1                                            | <u>.</u><br>1                         |

| MOV A, #data                         | Move immediate to A                                           | 2                                            | <u>·</u>                              |

| MOV Rn, A                            | Move A to register                                            | 1                                            | <u> </u>                              |

| MOV Rn, direct                       | Move direct byte to register                                  | 2                                            | 2                                     |

| MOV Rn, #data                        | Move immediate to register                                    | 2                                            | 1                                     |

| MOV direct, A                        | Move A to direct byte                                         | 2                                            | 1                                     |

|                                      |                                                               | 2                                            | 2                                     |

| MOV direct, Rn<br>MOV direct, direct | Move register to direct byte  Move direct byte to direct byte | 3                                            | 2                                     |

| ·                                    |                                                               |                                              |                                       |

| MOV direct, @Ri                      | Move data memory to direct byte                               | 3                                            | 2                                     |

| MOV @R: A                            | Move immediate to direct byte                                 |                                              |                                       |

| MOV @Ri, A                           | Move A to data memory                                         | 1                                            | 1 2                                   |

| MOV @Ri, direct                      | Move direct byte to data memory                               | 2                                            | 2                                     |

| MOV @Ri, #data                       | Move immediate to data memory                                 | 2                                            | 1                                     |

| MOV DPTR, #data                      | Move immediate to data pointer                                | 3                                            | 2                                     |

| MOVC A, @A+DPTR                      | Move code byte relative DPTR to A                             | 1                                            | 2                                     |

| MOVC A, @A+PC                        | Move code byte relative PC to A                               | 1                                            | 2                                     |

| MOVX A, @Ri                          | Move external data (A8) to A                                  | 1                                            | 2                                     |

| MOVX A, @DPTR                        | Move external data (A16) to A                                 | 1                                            | 2                                     |

| MOVX @Ri, A                          | Move A to external data (A8)                                  | 1                                            | 2                                     |

| MOVX @DPTR, A                        | Move A to external data (A16)                                 | 1                                            | 2                                     |

| PUSH direct                          | Push direct byte onto stack                                   | 2                                            | 2                                     |

| POP direct                           | Pop direct byte from stack                                    | 2                                            | 2                                     |

| XCH A, Rn                            | Exchange A and register                                       | 1                                            | 1                                     |

| XCH A, direct                        | Exchange A and direct byte                                    | 2                                            | 1                                     |

| XCH A, @Ri                           | Exchange A and data memory                                    | 1                                            | 1                                     |

| XCHD A, @Ri                          | Exchange A and data memory nibble                             | 1                                            | 1                                     |

| Branching Instructio                 | ns                                                            |                                              |                                       |

| ACALL addr 11                        | Absolute call to subroutine                                   | 2                                            | 2                                     |

| LCALL addr 16                        | Long call to subroutine                                       | 3                                            | 2                                     |

| RET                                  | Return from subroutine                                        | 1                                            | 2                                     |

| RETI                                 | Return from interrupt                                         | 1                                            | 2                                     |

| AJMP addr 11                         | Absolute jump unconditional                                   | 2                                            | 2                                     |

| LJMP addr 16                         | Long jump unconditional                                       | 3                                            | 2                                     |

| SJMP rel                             | Short jump (relative address)                                 | 2                                            | 2                                     |

| JC rel                               | Jump on carry = 1                                             | 2                                            | 2                                     |

| JNC rel                              | Jump on carry = 0                                             | 2                                            | 2                                     |

| JB bit, rel                          | Jump on direct bit = 1                                        | 3                                            | 2                                     |

| JNB bit, rel                         | Jump on direct bit = 0                                        | 3                                            | 2                                     |

| JBC bit, rel                         | Jump on direct bit = 1 and clear                              | 3                                            | 2                                     |

| JMP @A+DPTR                          | Jump indirect relative DPTR                                   | 1                                            | 2                                     |

| JZ rel                               | Jump on accumulator = 0                                       | 2                                            | 2                                     |

| JNZ rel                              | Jump on accumulator 1 = 0                                     | 2                                            | 2                                     |

| CJNE A, direct, rel                  | Compare A, direct JNE relative                                | 3                                            | 2                                     |

| CJNE A, #d, rel                      | Compare A, immediate JNE relative                             | 3                                            | 2                                     |

| CJNE Rn, #d, rel                     | Compare reg, immediate JNE relative                           | 3                                            | 2                                     |

| CJNE @ Ri, #d, rel                   | Compare ind, immediate JNE relative                           | 3                                            | 2                                     |

| DJNZ Rn, rel                         | Decrement register, JNZ relative                              | 2                                            | 2                                     |

| DJNZ direct, rel                     | Decrement direct byte, JNZ relative                           | 3                                            | 2                                     |

| Miscellaneous Instru                 | • '                                                           | Ü                                            | -                                     |

| NOP                                  | No operation                                                  | 1                                            | 1                                     |

| .101                                 | - vp=:=:::                                                    | <u>'                                    </u> |                                       |

# **Special Function Registers (SFR)**

Addresses 80h to FFh of the SFR address space can be accessed in direct addressing mode only. The following table lists the VRS700 Special Function Registers.

TABLE 4: SPECIAL FUNCTION REGISTERS (SFR)

| SFR            | SFR         | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Reset     |

|----------------|-------------|---------|---------|---------|---------|---------|---------|---------|---------|-----------|

| Register<br>P0 | Adrs<br>80h |         | _       | _       | -       | _       | _       | _       | _       | Value     |

| SP             | 81h         | -       | -       | -       | -       | -       | -       | -       | _       |           |

| DPL            | 82h         | _       | -       | _       | -       | -       | -       | -       | _       |           |

| DPH            | 83h         | _       | _       | _       | _       | _       | _       | _       | _       |           |

| (Reserved)     | 84h         |         |         |         |         |         |         |         |         |           |

| RCON           | 85h         | _       | _       | -       | -       | RAMS3   | RAMS2   | RAMS1   | RAMS0   | 0000000b  |

| DBANK          | 86h         | BSE     | -       | BS5     | BS4     | BS3     | BS2     | BS1     | BS0     | 0***0001b |

| PCON           | 87h         | SMOD    | -       | -       | -       | GF1     | GF0     | PDOWN   | IDLE    | 0000000b  |

| TCON           | 88h         | TF1     | TR1     | TF0     | TR0     | IE1     | IT1     | IE0     | IT0     | 0000000b  |

| TMOD           | 89h         | GATE1   | C/T1    | M1.1    | M0.1    | GATE0   | C/T0    | M1.0    | M0.0    | 0000000b  |

| TL0            | 8Ah         | -       | -       | -       | -       | -       | -       | -       | -       |           |

| TL1            | 8Bh         | -       | -       | -       | -       | -       | -       | -       | -       |           |

| TH0            | 8Ch         | -       | -       | -       | -       | -       | -       | -       | -       |           |

| TH1            | 8Dh         | -       | -       | -       | -       | -       | -       | -       | -       |           |

| P1             | 90h         | -       | -       | -       | -       | -       | -       | -       | -       |           |

| WDTKEY         | 97h         | WDTKEY7 | WDTKEY6 | WDTKEY5 | WDTKEY4 | WDTKEY3 | WDTKEY2 | WDTKEY1 | WDTKEY0 | ******b   |

| SCON           | 98h         | SM0     | SM1     | SM2     | REN     | TB8     | RB8     | TI      | RI      | 0000000b  |

| SBUF           | 99h         | -       | -       | -       | -       | -       | -       | -       | -       |           |

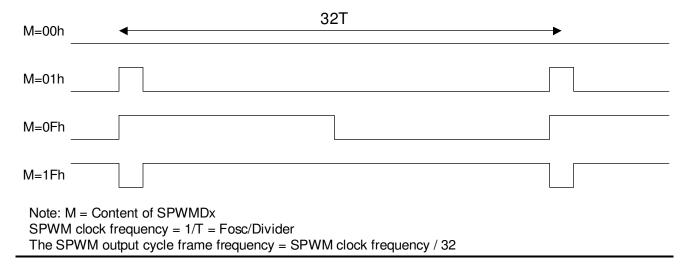

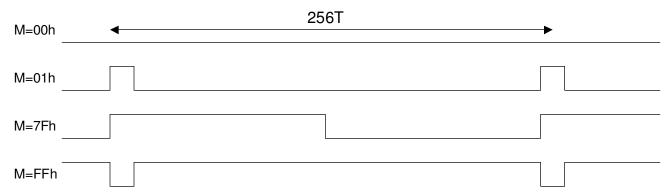

| SPWME          | 9Bh         | SPWM7E  | SPWM6E  | SPWM5E  | SPWM4E  | SPWM3E  | SPWM2E  | SPWM1E  | SPWM0E  | 00000000b |

| WDTC           | 9Fh         | WDTE    | -       | CLEAR   | -       | -       | PS2     | PS1     | PS0     | 0*0**000b |

| P2             | A0h         | -       | -       | -       | -       | -       | -       | -       | -       |           |

| ΙΕ             | A8h         | EA      | -       | ET2     | ES      | ET1     | EX1     | ET0     | EX0     | 00000000b |

| P3             | B0h         | -       | -       | -       | -       | -       | -       | -       | -       |           |

| SPWMD0         | B3h         | -       | -       | -       | -       | -       | -       | -       | -       | 00000000b |

| SPWMD1         | B4h         | -       | -       | -       | -       | -       | -       | -       | -       | 00000000b |

| SPWMD2         | B5h         | -       | -       | -       | -       | -       | -       | -       | -       | 00000000b |

| SPWMD3         | B6h         | -       | -       | -       | -       | -       | -       | -       | -       | 00000000b |

| IP             | B8h         | -       | -       | PT2     | PS      | PT1     | PX1     | PT0     | PX0     | 00000000b |

| SPWMD4         | BBh         | -       | -       | -       | -       | -       | -       | -       | -       | 00000000b |

| SPWMD5         | BCh         | -       | -       | -       | -       | -       | -       | -       | -       | 00000000b |

| SPWMD6         | BDh         | -       | -       | -       | -       | -       | -       | -       | -       | 00000000b |

| SPWMD7         | BEh         | -       | -       | -       | -       | -       | -       | -       | -       | 00000000b |

| SCONF          | BFh         | WDR     | -       | -       | -       | -       |         | OME     | ALEI    | 0****00b  |

| T2CON          | C8h         | TF2     | EXF2    | RCLK    | TCLK    | EXEN2   | TR2     | C/T2    | CP/RL2  | 0000000b  |

| T2MOD          | C9h         | -       | -       | -       | -       | -       | =       | T2OE    | DCEN    | 0000000b  |

| RCAP2L         | CAh         | -       | -       | -       | =       | -       | =       | =       | =       |           |

| RCAP2H         | CBh         | -       | -       | -       | -       | -       | -       | -       | -       |           |

| TL2            | CCh         | -       | -       | -       | -       | -       | -       | -       | -       |           |

| TH2            | CDh         |         |         |         |         |         |         | -       |         |           |

| PSW            | D0h         | CY      | AC      | F0      | RS1     | RS0     | OV      | -       | Р       |           |

| SPWMC0         | D3h         | -       | -       | i       | -       | i       | PBS0    | PFS01   | PFS00   | ******00b |

| SPWMC1         | D4h         | -       | -       | -       | -       | -       | PBS1    | PFS11   | PFS10   | ******00b |

| SPWMC2         | D5h         | -       | -       | -       | -       | -       | PBS2    | PFS21   | PFS20   | ******00b |

| SPWMC3         | D6h         | -       | -       | -       | -       | -       | PBS3    | PFS31   | PFS30   | ******00b |

| P4             | D8h         | -       | -       | -       | -       | P4.3    | P4.2    | P4.1    | P4.0    | ****1111b |

| SPWMC4         | DBh         |         |         |         |         |         | PBS4    | PFS41   | PFS40   | ******00b |

| SPWMC5         | DCh         |         |         |         |         |         | PBS5    | PFS51   | PFS50   | ******00b |

| SPWMC6         | DDh         |         |         |         |         |         | PBS6    | PFS61   | PFS60   | ******00b |

| SPWMC7         | DEh         |         |         |         |         |         | PBS7    | PFS71   | PFS70   | ******00b |

| ACC            | E0h         | -       | -       | -       | -       | -       | -       | -       | -       |           |

| В              | F0h         | -       | -       | -       | -       | -       | -       | -       | -       |           |

# Program Memory Structure

# **Program Memory**

The VRS700 includes 64K of on-chip Flash memory that can be used as general program memory. The address range for the 64KB of Flash memory is 0000h to FFFFh.

# **Program Status Word Register**

The register below contains the program state flags. These flags may be read or written to by the user.

TABLE 5: PROGRAM STATUS WORD REGISTER (PSW) - SFR DOH

| 7  | 6  | 5  | 4   | 3   | 2  | 1 | 0 |

|----|----|----|-----|-----|----|---|---|

| CY | AC | F0 | RS1 | RS0 | OV | - | Р |

| Bit | Mnemonic | Description                          |  |

|-----|----------|--------------------------------------|--|

| 7   | CY       | Carry Bit                            |  |

| 6   | AC       | Auxiliary Carry Bit from bit 3 to 4. |  |

| 5   | F0       | User definer flag                    |  |

| 4   | RS1      | R0-R7 Registers bank select bit 0    |  |

| 3   | RS0      | R0-R7 Registers bank select bit 1    |  |

| 2   | OV       | Overflow flag                        |  |

| 1   | -        | -                                    |  |

| 0   | Р        | Parity flag                          |  |

| RS1 | RS0 | Active Bank | Address |

|-----|-----|-------------|---------|

| 0   | 0   | 0           | 00h-07h |

| 0   | 1   | 1           | 08h-0Fh |

| 1   | 0   | 2           | 10h-17h |

| 1   | 1   | 3           | 18-1Fh  |

#### **Data Pointer**

The VRS 700 has one 16-bit data pointer. The DPTR is accessed through two SFR addresses: DPL located at address 82h and DPH located at address 83h.

#### **Data Memory**

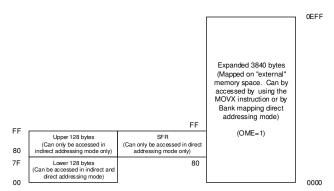

The VRS700 has 4K of on-chip SRAM: 256 bytes are configured like the internal memory structure of a standard 80C52, while the expanded 3840 bytes can be accessed using external memory addressing (MOVX) or in bank mapping direct addressing mode.

**Note:** By default, the expanded RAM memory is disabled. To use it, users must first set the bit OME (2) of the System Control Register (SFR BFh).

FIGURE 3: VRS700 DATA MEMORY

By default, the expanded RAM area is active. It is possible to disable it by clearing the OME bit of the SCONF register located at address BFh in the SFR.

#### Lower 128 bytes (00h to 7Fh, Bank 0 & Bank 1)

The lower 128 bytes (Figure 3) of data memory (from 00h to 7Fh) can be summarized in the following points:

- Address range 00h to 7Fh can be accessed in direct and indirect addressing modes.

- Address range 00h to 1Fh includes R0-R7 registers area.

- Address range 20h to 2Fh is bit addressable.

- Address range 30h to 7Fh is not bit addressable and can be used as general purposes storage.

- Range 40h-7Fh can be configured as a window to access the whole 4K of RAM memory.

#### Upper 128 bytes (80h to FFh)

The upper 128 bytes of the data memory ranging from 80h to FFh can be accessed using indirect addressing or by using the bank mapping in direct addressing mode (see Table 8).

Datasheet Rev 1.3

# Expanded RAM Access Using the MOVX @DPTR Instruction (0000-0EFF, Bank4-Bank63)

The 3840 bytes of the expanded RAM data memory occupy addresses 0000h to 0EFFh mapped on the "external" memory bus.

These bytes can be accessed using the MOVX instruction.

Note that in the case of indirect addressing using the *MOVX @DPTR* instruction, if the address exceeds 0EFFh, the VRS700 will generate the external memory control signal automatically.

# Internal RAM Access using MOVX @Rn instruction and the IRAM Control Register

The 3840 bytes of expanded RAM of the VRS700 can also be accessed using the MOVX @Rn instruction (where n=0,1). Since this instruction can only address 256 bytes of data, it must be used in conjunction with the internal RAM RCON register that serves to select which part of the expanded RAM will be targeted by the instruction.

TABLE 6: INTERNAL RAM CONTROL REGISTER (RCON) - SFR 85H

| 7      | 6 | 5 | 4     | 3     | 2     | 1     | 0 |

|--------|---|---|-------|-------|-------|-------|---|

| Unused |   |   | RAMS3 | RAMS2 | RAMS1 | RAMS0 |   |

| Bit | Mnemonic | Description             |  |  |  |

|-----|----------|-------------------------|--|--|--|

| 7   | Unused   | -                       |  |  |  |

| 6   | Unused   | -                       |  |  |  |

| 5   | Unused   | -                       |  |  |  |

| 4   | Unused   | -                       |  |  |  |

| 3   | RAMS3    | See Table 8 for details |  |  |  |

| 2   | RAMS2    | See Table 8 for details |  |  |  |

| 1   | RAMS1    | See Table 8 for details |  |  |  |

| 0   | RAMS0    | See Table 8 for details |  |  |  |

The value of the RAMS0, RAMS1, RAMS2, RAMS3 bits define the page of the expanded RAM that will be accessed by the MOVX @Rn instruction.

The default setting of the RAMS0, RAMS1, RAMS2 and RAMS3 bits is 0000 (page 0). Each page has 256 bytes.

TABLE 7: MAPPING OF EXPANDED RAM PAGE ACCESS

| RAMS3 | RAMS2 | RAMS1 | RAMS0 | MOVX@Ri I=0, 1 mapping to expanded RAM address |

|-------|-------|-------|-------|------------------------------------------------|

| 0     | 0     | 0     | 0     | 0000h-00FFh                                    |

| 0     | 0     | 0     | 1     | 0100h-01FFh                                    |

| 0     | 0     | 1     | 0     | 0200h-02FFh                                    |

| 0     | 0     | 1     | 1     | 0300h-03FFh                                    |

| 0     | 1     | 0     | 0     | 0400h-04FFh                                    |

| 0     | 1     | 0     | 1     | 0500h-05FFh                                    |

| 0     | 1     | 1     | 0     | 0600h-06FFh                                    |

| 0     | 1     | 1     | 1     | 0700h-07FFh                                    |

| 1     | 0     | 0     | 0     | 0800h-08FFh                                    |

| 1     | 0     | 0     | 1     | 0900h-09FFh                                    |

| 1     | 0     | 1     | 0     | 0A00h-0AFFh                                    |

| 1     | 0     | 1     | 1     | 0B00h-0BFFh                                    |

| 1     | 1     | 0     | 0     | 0C00h-0CFFh                                    |

| 1     | 1     | 0     | 1     | 0D00h-0DFFh                                    |

| 1     | 1     | 1     | 0     | 0E00h-0EFFh                                    |

# VRS700 **VERSA**

#### **Data Bank Control Register**

The DBANK register allows the user to map the entire content of the RAM memory in the 64 bytes RAM memory window ranging from 40h to 7Fh. This allows for faster direct addressing of the entire RAM content. The Data Bank Control Register permits this feature to be activated and selects which 64-byte-block of RAM will be mapped into the 40h to 7Fh window.

The Data Bank Select function is activated by setting the Data Bank Select enable bit (BSE) to 1. Setting this bit to zero disables this function. The 6 least significant bits of this register control the mapping of the entire 4K bytes on-chip RAM space into the 040h-07Fh range. See tables 8 and 9.

TABLE 8: DATA BANK CONTROL REGISTER (DBANK) - SFR 86H

| 7   | 6      | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|--------|-----|-----|-----|-----|-----|-----|

| BSE | unused | BS5 | BS4 | BS3 | BS2 | BS1 | BS0 |

| Bit | Mnemonic | Description                               |

|-----|----------|-------------------------------------------|

| 7   | BSE      | Data Bank Select Enable Bit               |

|     |          | BSE=1, Data Bank Select enabled           |

|     |          | BSE=0, Data Bank Select disabled          |

| 6   | Unused   | -                                         |

| 5   | BS5      | Allows the mapping of the 4K RAM into the |

| 4   | BS4      | 040h - 07Fh RAM space. See Table 8 for a  |

| 3   | BS3      | complete description.                     |

| 2   | BS2      |                                           |

| 1   | BS1      |                                           |

| 0   | BS0      |                                           |

Example: User writes #30h to 101h address:

MOV DBANK, #88H ;Set bank mapping 40h-07Fh to 0100h-013Fh

MOV A, #30H ;Store #30H to A MOV 41H, A ;Write #30 to 0101h

;address

TABLE 9:BANK MAPPING DIRECT ADDRESSING MODE

| B        | S5 | BS4 | BS3 | BS2   | BS1    | BSO        | 040h~07fh<br>mapping<br>address | Note                                   |

|----------|----|-----|-----|-------|--------|------------|---------------------------------|----------------------------------------|

| (        | 0  | 0   | 0   | 0     | 0      | 0          | 000h-<br>03Fh                   | Lower 128<br>byte RAM                  |

| (        | 0  | 0   | 0   | 0     | 0      | 1          | 040h-<br>07Fh                   | Lower 128<br>byte RAM                  |

| (        | 0  | 0   | 0   | 0     | 1      | 0          | 080h-<br>0BFh                   | Upper 128<br>byte RAM                  |

|          | 0  | 0   | 0   | 0     | 1      | 1          | 0C0h-                           | Upper 128                              |

| (        | 0  | 0   | 0   | 1     | 0      | 0          | 0FFh<br>0000h-<br>003Fh         | byte RAM On-chip expanded 768 byte RAM |

| (        | 0  | 0   | 0   | 1     | 0      | 1          | 0040h-<br>007Fh                 | ű                                      |

| (        | 0  | 0   | 0   | 1     | 1      | 0          | 0080h-<br>00BFh                 | ű                                      |

| (        | 0  | 0   | 0   | 1     | 1      | 1          | 00C0h-<br>00FFh                 | "                                      |

| (        | 0  | 0   | 1   | 0     | 0      | 0          | 0100h-<br>013Fh                 | ű                                      |

| (        | 0  | 0   | 1   | 0     | 0      | 1          | 0140h-<br>017Fh                 | íí.                                    |

| (        | 0  | 0   | 1   | 0     | 1      | 0          | 0180h-<br>01BFh                 | ıı                                     |

| (        | 0  | 0   | 1   | 0     | 1      | 1          | 01C0h-<br>01FFh                 | ű                                      |

| (        | 0  | 0   | 1   | 1     | 0      | 0          | 0200h-<br>023Fh                 | ű                                      |

|          | 0  | 0   | 1   | 1     | 0      | 1          | 0240h-<br>027Fh                 | ű                                      |

| (        | 0  | 0   | 1   | 1     | 1      | 0          | 0280h-<br>02BFh                 | ű                                      |

| (        | 0  | 0   | 1   | 1     | 1      | 1          | 02C0h-<br>02FFh                 | ű                                      |

| (        | 0  | 1   | 0   | 0     | 0      | 0          | 0300h-<br>033Fh                 | ű                                      |

| (        | 0  | 1   | 0   | 0     | 0      | 1          | 0340h-<br>037Fh                 | ű                                      |

| (        | 0  | 1   | 0   | 0     | 1      | 0          | 0380h-<br>03BFh                 | ű                                      |

| (        | 0  | 1   | 0   | 0     | 1      | 1          | 03C0h-<br>03FFh                 | ű                                      |

| (        | 0  | 1   | 0   | 1     | 0      | 0          | 0400-<br>043Fh                  | и                                      |

| (        | 0  | 1   | 0   | 1     | 0      | 1          | 0440h-<br>047Fh                 | ű                                      |

|          | 0  | 1   | 0   | 1     | 1      | 0          | 0480h-<br>04BFh                 | íí                                     |

|          |    |     |     | (Foll | ow the | <br>same p |                                 | //                                     |

|          | 1  | 1   | 1   | 0     | 1      | 0          | 0D80h-                          | íí.                                    |

| -        | 1  | 1   | 1   | 0     | 1      | 1          | 0DBFh<br>0DC0h-                 | íí                                     |

| -        | 1  | 1   | 1   | 1     | 0      | 0          | 0DFFh<br>0E00h-                 | ű                                      |

|          | 1  | 1   | 1   | 1     | 0      | 1          | 0E3Fh<br>0E40h-                 | "                                      |

| -        | 1  | 1   | 1   | 1     | 1      | 0          | 0E7Fh<br>0E80-                  | íí                                     |

| <u> </u> | 1  | 1   | 1   | 1     | 1      | 1          | 0EBFh<br>0EC0h-                 | «                                      |

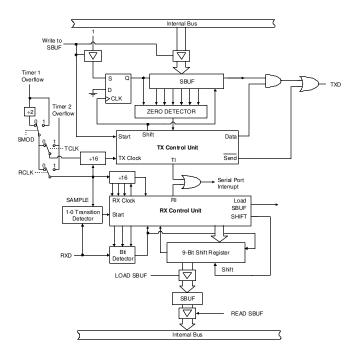

# **Description of Peripherals**

# **System Control Register**

The System control Register serves the following functions:

- Flag that shows Watch Dog Timer reset has occurred.

- Controls the activation of the expanded RAM Memory.

- Controls the ALE output.

The Table 10 shows the structure of the System Control Register.

The WDR bit is a flag that indicates whether the Watch Dog Timer has caused the system reset. When the WDT is enabled, users should check the WDR bit whenever an unpredicted reset occurs.

The OME bit allows the user to enable or disable the on-chip expanded 3840 bytes of RAM. By default, after reset, the expanded RAM memory is disabled (OME=0). This bit must be set to 1 to activate the expanded RAM memory.

The ALE bit controls the ALE output activity.

By default, the ALE pin is active. In applications where the program is executed from the internal flash memory of the VRS700, the ALE pin is usually of no use, so it is advisable to inhibit the ALE output in order to reduce the EMI generated by the device.

By default, the ALE pin is active and emits a signal of a frequency of Fosc/6. Setting the ALE bit of the System Control Register inhibits the ALE output.

TABLE 10: SYSTEM CONTROL REGISTER (SCONF) - SFR BFH

| 7   | 6 | 5 | 4     | 3 | 2 | 1   | 0    |

|-----|---|---|-------|---|---|-----|------|

| WDR |   |   | Unuse | d |   | OME | ALEI |

| Bit | Mnemonic | Description                                                   |

|-----|----------|---------------------------------------------------------------|

| 7   | WDR      | This is the Watch Dog Timer reset bit. It will                |

|     |          | be set to 1 when the reset signal generated by WDT overflows. |

| 6   | Unused   | -                                                             |

| 5   | Unused   | -                                                             |

| 4   | Unused   | -                                                             |

| 3   | Unused   | -                                                             |

| 2   | Unused   | -                                                             |

| 1   | OME      | 3840 bytes of on-chip enable bit                              |

| 0   | ALEI     | ALE output inhibit bit, which is used to reduce EMI.          |

#### **Power Control Register**

The VRS700 provides two power saving modes: Idle and Power Down. These two modes serve to reduce the power consumption of the device.

In Idle mode, the processor is stopped but the oscillator is still running. The content of the RAM, I/O state and SFR registers are maintained. Timer operation is maintained, as well as the external interrupts.

This mode is useful for applications in which stopping the processor to save power is required. The processor will be woken up when an external event, triggering an interrupt, occurs.

In Power Down mode, the oscillator of the VRS700 is stopped. This means that all the peripherals are disabled. The content of the RAM and the SFR registers, however, is maintained.

These power saving modes are controlled by the PDOWN and IDLE bits of the PCON register (Table 11) at address 87h.

TABLE 11: POWER CONTROL REGISTER (PCON) - SFR 87H

| 7 | 6 | 5   | 4    | 3 | 2 | 1     | 0     |

|---|---|-----|------|---|---|-------|-------|

|   |   | Unı | ısed |   |   | RAMS1 | RAMS0 |

| Bit | Mnemonic | Description                                           |

|-----|----------|-------------------------------------------------------|

| 7   | SMOD     | 1: Double the baud rate of the serial port            |

|     |          | frequency that was generated by Timer 1.              |

|     |          | 0: Normal serial port baud rate generated by Timer 1. |

| 6   | Unused   | -                                                     |

| 5   | Unused   | -                                                     |

| 4   | Unused   | -                                                     |

| 3   | GF1      | General Purpose Flag                                  |

| 2   | GF0      | General Purpose Flag                                  |

| 1   | PDOWN    | Power down mode control bit                           |

| 0   | IDLE     | Idle mode control bit                                 |

# **Input/Output Ports**

The VRS700 has 36 bi-directional lines grouped into four 8-bit I/O ports and one 4-bit I/O port. These I/Os can be individually configured as input or output.

Except for the P0 I/Os, which are of the open drain type, each I/O is made of a transistor connected to ground and a dynamic pull-up resistor made of a combination of transistors.

Writing a 0 in a given I/O port bit register will activate the transistor connected to ground, this will bring the I/O to a LOW level.

Writing a 1 into a given I/O port bit register deactivates the transistor between the pin and ground. In this case, the pull-up resistor will bring the Pin to a HIGH level.

To use a given I/O as an input, one must write a 1 into its associated port register bit.

By default, upon reset all the I/Os are configured as input.

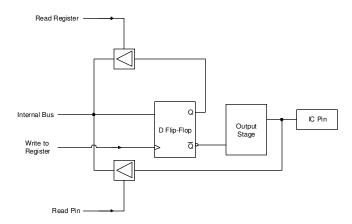

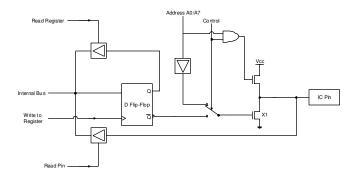

### General Structure of an I/O Port

The following elements establish the link between the core unit and the pins of the microcontroller:

- Special Function Register (same name as port)

- Output Stage Amplifier (the structure of this element varies with its auxiliary function)

From Figure 4, one may see that the D flip-flop stores the value received from the internal bus after receiving a write signal from the core. Also, notice that the Q output of the flip-flop can be linked to the internal bus by executing a read instruction.

This is how one would read the content of the register. It is also possible to link the value of the pin to the internal bus. This is done by the "read pin" instruction. In short, the user may read the value of the register or the pin.

FIGURE 4: INTERNAL STRUCTURE OF ONE OF THE FIGHT I/O PORT LINES

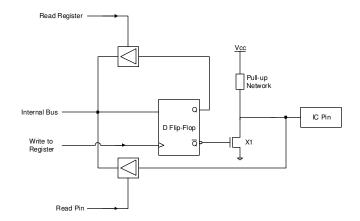

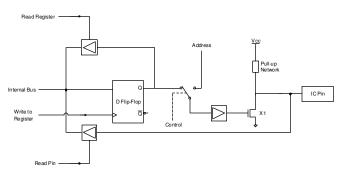

#### Structure of the P1, P2, P3 and P4 Ports

The following figure (Figure 5) gives a general idea of the structure of one of the lines of the P1, P2 and P3 ports. For each port, the output stage is composed of a transistor (X1) and 3 other pull-up transistors. It is important to note that the figure below does not show the intermediary logic that connects the output of the register and the output stage together because this logic varies with the auxiliary function of each port.

FIGURE 5: GENERAL STRUCTURE OF THE OUTPUT STAGE OF P1, P2 AND P3

Each line may be used independently as a logical input or output. When used as an input, as mentioned earlier, the corresponding bit register must be high.

Datasheet Rev 1.3

The transistor would be off and the pull-up will maintain the output at a high level. Also, note that if an external device with a logical low value is connected to the pin, the current will flow out of the pin. In order to have a real bi-directional output, the input should be in a high impedance state. It is for this reason that we call ports P1, P2, P3 and P4 "quasi bi-directional".

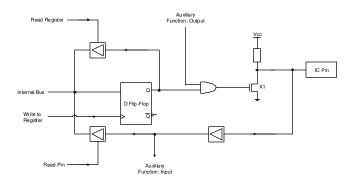

#### Structure of Port 0

The internal structure of P0 is shown in Figure 6. The auxiliary function of this port requires a particular logic. As opposed to the other ports, P0 is truly bi-directional. In other words, when used as an input, it is considered to be in a floating logical state (high impedance state). This arises from the absence of the internal pull-up resistance. The pull-up resistance is actually replaced by a transistor that is only used when the port is used to access external memory/data bus (EA=0).

When used as an I/O port, P0 acts as an open drain port and the use of an external pull-up resistor is likely to be required for most applications.

FIGURE 6: PORT PO'S PARTICULAR STRUCTURE

When P0 is used as an external memory bus input (for a MOVX instruction, for example), the outputs of the register are automatically forced to 1.

#### Port P0 and P2 as Address and Data Bus

The output stage may receive data from two sources (Figure 7):

- The outputs of register P0 or the bus address itself multiplexed with the data bus for P0.

- The outputs of the P2 register or the high part (A8/A15) of the bus address for the P2 port.

FIGURE 7: P2 PORT STRUCTURE

When the ports are used as an address or data bus, the special function registers P0 and P2 are disconnected from the output stage. The 8 bits of the P0 register are forced to 1 and the content of the P2 register remains constant.

### **Auxiliary Port 1 Functions**

The port 1 I/O pins are shared with the SPWM outputs, Timer 2 EXT and T2 input as shown below:

| Pin   | Mnemonic | Function               |

|-------|----------|------------------------|

| P1.0  | T2       | Timer 2 counter input  |

| 1 1.0 | SPWM0    | SPWM0 output           |

| P1.1  | T2EX     | Timer2 Auxiliary input |

| 1 1.1 | SPWM1    | SPWM1 output           |

| P1.2  | SPWM2    | SPWM2 output           |

| P1.3  | SPWM3    | SPWM3 output           |

| P1.4  | SPWM4    | SPWM4output            |

| P1.5  | SPWM5    | SPWM5 output           |

| P1.6  | SPWM6    | SPWM6 output           |

| P1.7  | SPWM7    | SPWM7 output           |

Datasheet Rev 1.3

#### **Auxiliary P3 Port Functions**

The Port 3 I/O pins are shared with the UART interface, INTO and INT1 interrupts, Timer 0 and Timer 1 inputs and finally the #WR and #RD lines, when external memory access is performed.

To maintain the correct functionality of the line in auxiliary function mode, it is necessary that the Q output of the register is held stable at 1. Conversely, if the pull-down transistor continues conducting, it will set the IC pin at a voltage of approximately 0 (Figure 8).

FIGURE 8: P3 PORT STRUCTURE

The following table describes the auxiliary function of the port 3 I/O pins.

TABLE 12: P3 AUXILIARY FUNCTION TABLE

| Pin  | Mnemonic | Function                         |

|------|----------|----------------------------------|

| P3.0 | RXD      | Serial Port:                     |

|      |          | Receive data in asynchronous     |

|      |          | mode. Input and output data in   |

|      |          | synchronous mode.                |

| P3.1 | TXD      | Serial Port:                     |

|      |          | Transmit data in asynchronous    |

|      |          | mode. Output clock value in      |

|      |          | synchronous mode.                |

| P3.2 | ĪNT0     | External Interrupt 0             |

|      | 11410    | Timer 0 Control Input            |

| P3.3 | ĪNT1     | External Interrupt 1             |

|      | 11111    | Timer 1 Control Input            |

| P3.4 | T0       | Timer 0 Counter Input            |

| P3.5 | T1       | Timer 1 Counter Input            |

| P3.6 | WR       | Write signal for external memory |

| P3.7 | RD       | Read signal for external memory  |

#### Port 4

Port 4 (Table 13) has four pins and its port address is located at 0D8H. The functionality of Port 4 is identical to that of Port 1, Port 2 Port 3.

TABLE 13: PORT 4 (P4) - SFR D8H

|        |   | , |   |      |      |      |      |

|--------|---|---|---|------|------|------|------|

| 7      | 6 | 5 | 4 | 3    | 2    | 1    | 0    |

| Unused |   |   |   | P4.3 | P4.2 | P4.1 | P4.0 |

| Bit | Mnemonic | Description                              |

|-----|----------|------------------------------------------|

| 7   | Unused   | -                                        |

| 6   | Unused   | -                                        |

| 5   | Unused   | -                                        |

| 4   | Unused   | -                                        |

| 3   | P4.3     | Used to output the setting to pins P4.3, |

| 2   | P4.2     | P4.2, P4.1, P4.0 respectively.           |

| 1   | P4.1     |                                          |

| 0   | P4.0     |                                          |

#### **Software Particularities Concerning the Ports**

Some instructions allow the user to read the logic state of the output pin, while others allow the user to read the content of the associated port register. These instructions are called *read-modify-write* instructions. A list of these instructions is found in the table below.

Upon execution of these instructions, the content of the port register (at least 1 bit) is modified. The other read instructions take the present state of the input into account. For example, the instruction ANL P3,#01h obtains the value in the P3 register, performs the desired logic operation with the constant 01h and recopies the result into the P3 register. When users want to take the present state of the inputs into account, they must first read these states and perform an AND operation between the reading and the constant.

MOV A, P3; State of the inputs in the accumulator ANL A, #01; AND operation between P3 and 01h

When the port is used as an output, the register contains information on the state of the output pins. Measuring the state of an output directly on the pin is inaccurate because the electrical level depends mostly on the type of charge that is applied to it. The functions shown below (Table 14) take the value of the register rather than that of the pin.

Table 14: List of Instructions that Read and Modify the Port Using Register Values

| Instruction | Function                                |

|-------------|-----------------------------------------|

| ANL         | Logical AND ex: ANL P0, A               |

| ORL         | Logical OR ex: ORL P2, #01110000B       |

| XRL         | Exclusive OR ex: XRL P1, A              |

| JBC         | Jump if the bit of the port is set to 0 |

| CPL         | Complement one bit of the port          |

| INC         | Increment the port register by 1        |

| DEC         | Decrement the port register by 1        |

| DJNZ        | Decrement by 1 and jump if the result   |

|             | is not equal to 0                       |

| MOV P.,C    | Copy the held bit C to the port         |

| CLR P.x     | Set the port bit to 0                   |

| SETB P.x    | Set the port bit to 1                   |

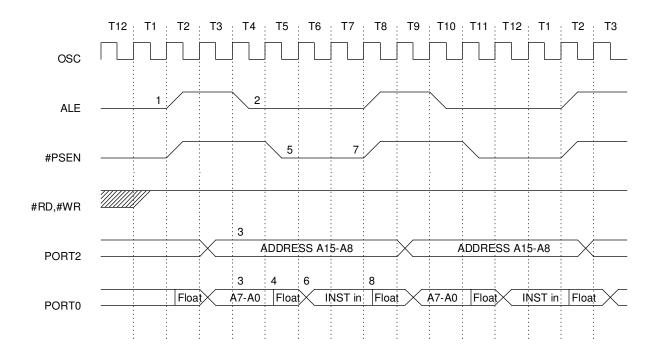

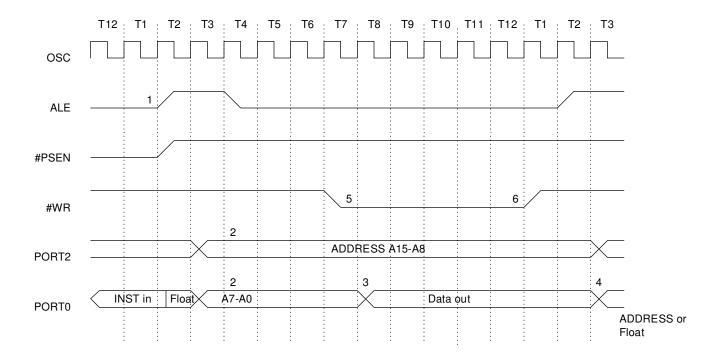

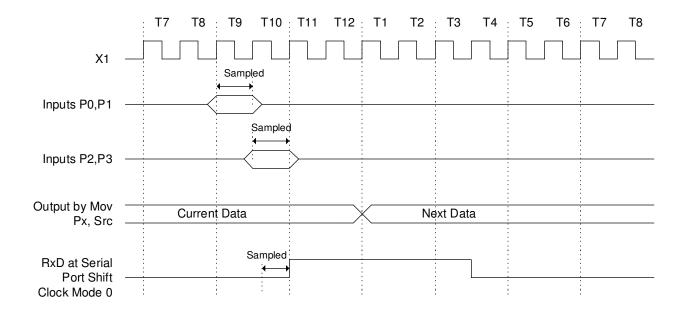

## **Port Operation Timing**

#### Writing to a Port (Output)

When an operation induces a modification of the content in a port register, the new value is placed at the output of the D flip-flop during the T12 period of the last machine cycle that the instruction needed to execute.

It is important to note, however, that the output stage only samples the output of the registers on the P1 phase of each period. It follows that the new value only appears at the output after the T12 period of the following machine cycle (see Figure 24).

### Reading a Port (Input)

The reading of an I/O pin takes place:

- During T9 cycle for P0, P1

- During T10 cycle for P2, P3

- When the ports are configured as I/Os (see Figure 24).

In order to get sampled, the signal duration present on the I/O configured input must have a duration longer than Fosc/12.

Dalasheel nev 1.3

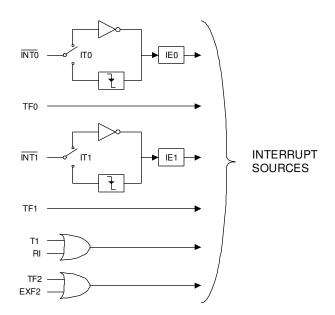

# **Timers**

The VRS700 includes three 16-bit timers: T0, T1 and T2. The timers can operate in two specific modes:

- Event counting mode

- Timer mode

When operating in counting mode, the counter is incremented each time an external event, such as a transition in the logical state of the timer input (T0, T1, T2 input), is detected. When operating in timer mode, the counter is incremented by the microcontroller's direct clock pulse or by a divided version of it.

#### Timer 0 and Timer 1

Timers 0 and 1 have four modes of operation. These modes allow the user to change the size of the counting register or to authorize an automatic reload when provided with a specific value. Timer 1 can even be used as a baud rate generator to generate communication frequencies for the serial interface.

Timer 1 and Timer 0 are configured by the TMOD (Table 15) and TCON (Table 16) registers.

TABLE 15: TIMER MODE CONTROL REGISTER (TMOD) - SFR 89H

| TABLE TO: TIME! MODE CONTINUE TIEGICIE! (TIMOS) |     |    |    |      |     |      |      |  |

|-------------------------------------------------|-----|----|----|------|-----|------|------|--|

| 7                                               | 6   | 5  | 4  | 3    | 2   | 1    | 0    |  |

| GATE                                            | С/Т | M1 | MO | GATE | С/Т | M1.0 | MO 0 |  |

| Bit | Mnemonic | Description                                                                                                                                                                                   |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | GATE1    | 1: Enables external gate control (pin INT1 for Counter 1). When INT1 is high, and TRx bit is set (see TCON register), a counter is incremented every falling edge on the T1 IN input pin.     |

| 6   | C/T1     | Selects timer or counter operation (Timer1).  1 = A counter operation is performed  0 = The corresponding register will function as a timer.                                                  |

| 5   | M1.1     | Selects mode for Timer/Counter 1, as shown in Table 16.                                                                                                                                       |

| 4   | M0.1     | Selects mode for Timer/Counter 1, as shown in Table 16.                                                                                                                                       |

| 3   | GATE0    | If set, enables external gate control (pin INT0 for Counter 0). When INT0 is high, and TRx bit is set (see TCON register), a counter is incremented every falling edge on the T0IN input pin. |

| 2   | C/T0     | Selects timer or counter operation (Timer 0).  1 = A counter operation is performed  0 = The corresponding register will function as a timer.                                                 |

| 1   | M1.0     | Selects mode for Timer/Counter 0.                                                                                                                                                             |

| 0   | M0.0     | Selects mode for Timer/Counter 0.                                                                                                                                                             |

The table below (Table 16) summarizes the four modes of operation of timers 0 and 1. The timer operating mode is selected by the bits M1 and M0 of the TMOD register.

TABLE 16: TIMER/COUNTER MODE DESCRIPTION SUMMARY

| M1 | MO | Mode   | Function                                                                                                                                                                             |

|----|----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0  | 0  | Mode 0 | 13-bit Counter                                                                                                                                                                       |

| 0  | 1  | Mode 1 | 16-bit Counter                                                                                                                                                                       |

| 1  | 0  | Mode 2 | 8-bit auto-reload Counter/Timer. The reload value is kept in TH0 or TH1, while TL0 or TL1 is incremented every machine cycle. When TLx overflows, the value of THx is copied to TLx. |

| 1  | 1  | Mode 3 | If Timer 1 M1 and M0 bits are set to 1, Timer 1 stops.                                                                                                                               |

#### **Counter and Timer Functions**

#### **Timing Function**

When operating as a timer, the counter is automatically incremented at every machine cycle.

When a timer overflow condition occurs an associated overflow flag, TF0 or TF1 flag is set to 1.

These flags are part of the TCON register.

TABLE 17:TIMER 0 AND 1 CONTROL REGISTER (TCON) -SFR 88H

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| TF1 | TR1 | TF0 | TR0 | IE1 | IT1 | IE0 | IT0 |

| Bit | Mnemonic | Description                                                                                                                                                                       |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TF1      | Timer 1 Overflow Flag. Set by hardware on Timer/Counter overflow. Cleared by hardware on Timer/Counter overflow. Cleared by hardware when processor vectors to interrupt routine. |

| 6   | TR1      | Timer 1 Run Control Bit. Set/cleared by software to turn Timer/Counter on or off.                                                                                                 |

| 5   | TF0      | Timer 0 Overflow Flag. Set by hardware on<br>Timer/Counter overflow. Cleared by<br>hardware when processor vectors to<br>interrupt routine.                                       |

| 4   | TR0      | Timer 0 Run Control Bit. Set/cleared by software to turn Timer/Counter on or off.                                                                                                 |

| 3   | IE1      | Interrupt Edge Flag. Set by hardware when external interrupt edge is detected. Cleared when interrupt processed.                                                                  |

| 2   | IT1      | Interrupt 1 Type Control Bit. Set/cleared by software to specify falling edge/low level triggered external interrupts.                                                            |

| 1   | IE0      | Interrupt 0 Edge Flag. Set by hardware when external interrupt edge is detected. Cleared when interrupt processed.                                                                |

| 0   | IT0      | Interrupt 0 Type control bit. Set/cleared by software to specify falling edge/low level triggered external interrupts.                                                            |

#### **Counting Function**

When operating as a counter, the timer's register is incremented at every falling edge of the T0, T1 and T2 signals located at the input of the timer. In this case, the signal is sampled at the T10 phase of each machine cycle for Timer 0, Timer 1 and T9 for Timer 2.

When a high to low transition is detected at the timer input pin, the counter is incremented. Two machine cycles are required to detect and record an event. This means that the event duration must be greater than  $(Fosc/24)^{-1}$ .

#### **Operating Modes**

The user may change the operating mode by varying the M1 and M0 bits of the TMOD SFR.

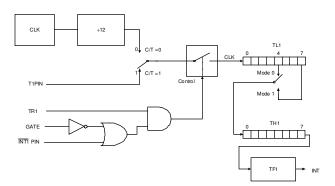

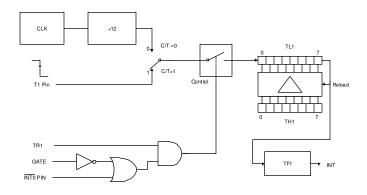

#### Mode 0

In Mode 0, the timer operates as an 8-bit counter preceded by a divide-by-32 prescaler made of the 5 LSB of TL1. The register of the counter is configured to be 13 bits long. When an overflow causes the value of the register to roll over to 0, the TFx interrupt signal goes to 1. The count value is validated as soon as TRx goes to 1 and the GATE bit is 0, or when INTx is 1. The figure below shows this mode of operation.

FIGURE 9: TIMER/COUNTER 1 MODE 0: 13-BIT COUNTER

#### Mode 1

Mode 1 is almost identical to Mode 0. They differ in that, in Mode 1, the counter is 16 bits wide and has no prescaler.

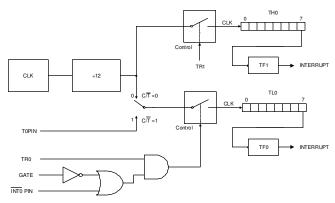

#### Mode 2

In this mode, the timer is configured as an 8-bit counter with auto-reload. The lower byte of the timer, TLx is used as the counter and the upper byte serves to store the timer reload value which will be automatically copied into the TLx portion of the timer when TFx flag is set in response to the overflow. The value of THx remains unchanged.

FIGURE 10: TIMER/COUNTER 1 MODE 2: 8-BIT AUTOMATIC RELOAD

#### Mode 3

In Mode 3 (Figure 11), Timer 1 is blocked as if its control bit, TR1, was set to 0. In this mode, Timer 0's registers TL0 and TH0 are configured as two separate 8-bit counters. Also, the TL0 counter uses Timer 0's control bits C/T, GATE, TR0, INT0, TF0, and the TH0 counter is held in Timer Mode (counting machine cycles) and gains control over TR1 and TF1 from Timer 1. At this point, TH0 controls the Timer 1 interrupt.

FIGURE 11: TIMER/COUNTER 0 MODE 3

#### Timer 2

Timer 2 of the VRS700 is a 16-bit Timer/Counter. Similar to timers 0 and 1, Timer 2 can operate either as an event counter or as a timer. The user may switch functions by writing to the C/T2 bit located in the T2CON Special Function Register. Timer 2 has three operating modes: "Auto-Load", "Capture" and "Baud Rate Generator". The T2CON SFR configures the modes of operation of Timer 2. Table 18 describes each bit in the T2CON Special Function Register.

TABLE 18: TIMER 2 CONTROL REGISTER (T2CON) - SFR C8H

| 7   | 6    | 5    | 4    | 3     | 2   | 1    | 0      |

|-----|------|------|------|-------|-----|------|--------|

| TF2 | EXF2 | RCLK | TCLK | EXEN2 | TR2 | C/T2 | CP/RL2 |

| Bit | Mnemonic | Description                                                                                                                                                                                                                                                                    |

|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TF2      | Timer 2 Overflow Flag. Set by an overflow of Timer 2 and must be cleared by software. TF2 will not be set when either RCLK =1 or TCLK =1.                                                                                                                                      |

| 6   | EXF2     | Timer 2 external flag change in state occurs when either a capture or reload is caused by a negative transition on T2EX and EXEN2=1. When Timer 2 is enabled, EXF=1 will cause the CPU to vector to the Timer 2 interrupt routine. Note that EXF2 must be cleared by software. |

| 5   | RCLK     | Serial Port Receive Clock Source.  1: Causes serial port to use Timer 2 overflow pulses for its receive clock in modes 1 and 3.  0: Causes Timer 1 overflow to be used for the Serial Port receive clock.                                                                      |

| 4   | TCLK     | Serial Port Transmit Clock.  1: Causes serial port to use Timer 2 overflow pulses for its transmit clock in modes 1 and 3.  0: Causes Timer 1 overflow to be used for                                                                                                          |

|     |          | the serial port transmit clock.                                                                                                                                                                                                                                                |

| 3   | EXEN2    | Timer 2 External Mode Enable.  1: Allows a capture or reload to occur as a result of a negative transition on T2EX if Timer 2 is not being used to clock the serial port.  0: Causes Timer 2 to ignore events at T2EX.                                                         |

| 2   | TR2      | Start/Stop Control for Timer 2. 1: Start Timer 2 0: Stop Timer 2                                                                                                                                                                                                               |

| 1   | C/T2     | Timer or Counter Select (Timer 2)  1: External event counter falling edge triggered.  0: Internal Timer (OSC/12)                                                                                                                                                               |

| 0 | CP/RL2 | Capture/Reload Select.  1: Capture of Timer 2 value into RCAP2H. RCAP2L is performed if EXEN2=1 and a negative transitions occurs on the T2EX pin. The capture mode requires RCLK and TCLK to be 0.                          |

|---|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |        | 0: Auto-reload reloads will occur either with Timer 2 overflows or negative transitions at T2EX when EXEN2=1. When either RCK =1 or TCLK =1, this bit is ignored and the timer is forced to auto-reload on Timer 2 overflow. |

Table 19 enumerates the possible combinations of control bits that may be used for the mode selection of Timer 2.

TABLE 19: TIMER 2 MODE SELECTION BITS

| RCLK + TCLK | CP/RL2 | TR2 | MODE                        |

|-------------|--------|-----|-----------------------------|

| 0           | 0      | 1   | 16-bit Auto-<br>Reload Mode |

| 0           | 1      | 1   | 16-bit Capture<br>Mode      |

| 1           | Х      | 1   | Baud Rate<br>Generator Mode |

| Χ           | Χ      | 0   | Off                         |

The details of each mode are described below.

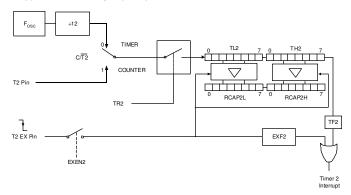

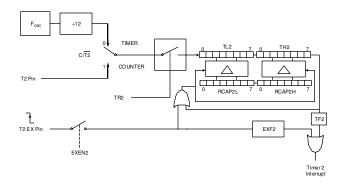

#### **Capture Mode**

In Capture Mode the EXEN2 bit value defines whether the external transition on the T2EX pin will trigger the capture of the timer value.

When EXEN2=0, Timer 2 acts as a 16-bit timer or counter, which, when an overflow occurs, will set bit TF2 (Timer 2 overflow bit). This overflow can be used to generate an interrupt.

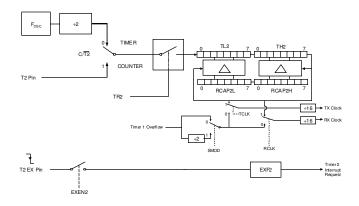

FIGURE 12: TIMER 2 IN CAPTURE MODE