## **General Description**

The MAX1441 proximity and touch sensor IC is designed for capacitive proximity sensing in automotive passive remote keyless entry (PRKE) and other applications. This device provides signal processing to support two independent touch/proximity sensor channels. The device features two open-drain output pins with highvoltage capability up to 28V, as well as five digital I/Os to indicate sensing events. During manufacturing, JTAG programming uses four digital I/Os.

The device uses grounded electrode capacitive sensing to measure capacitance between one of the two sense pins and the ground. A hand approaching a sense electrode attached to these sense pins causes a change in measured capacitance indicating the presence (touch or proximity) of the object. Activeguard outputs shield the sense electrode from unwanted sources without adding parasitic capacitance. Spread-spectrum techniques in the sensor excitation circuit reduce both electromagnetic emissions and susceptibility to interfering signals. In addition, the sensing excitation frequency is programmable from 100kHz to 500kHz in 10kHz steps to avoid interference.

The sensor input signals are converted to a 12-bit digital data and are available to an on-chip microcontroller (µC). The device provides independent offset compensation of up to 63pF for each input channel. Each channel can be programmed to 5pF, 10pF, or 20pF full-scale range.

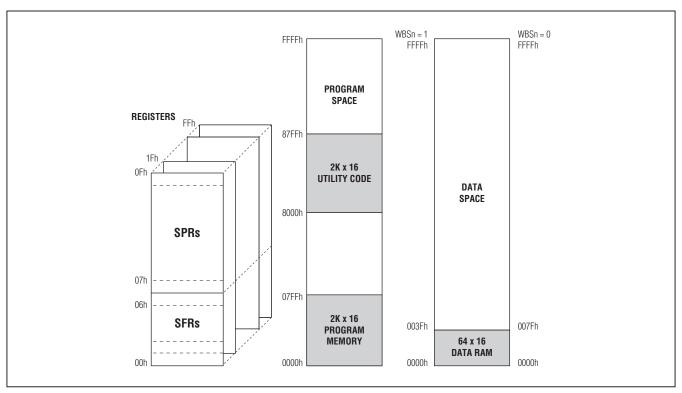

The device features an internal MAXQ® microcontroller with 2kword of flash for user programs and 128 bytes of SRAM. This feature provides the ability to implement customized signal processing and discrimination algorithms that optimize performance in the systems.

The device offers user-configurable general-purpose digital I/O lines. Power-on-reset (POR) circuitry provides consistent startup of the device, and a watchdog timer ensures long-term reliable operation of the user's software.

The device is available in a 20-pin TSSOP package and is specified over the -40°C to +105°C automotive temperature range.

#### **Features**

- ◆ Low Average Operating Current (100µA at 14V)

- ♦ 1.2.fF LSB Capacitance-to-Digital Resolution (5pF Range)

- ♦ 5V to 28V Operation

- **♦ 45V Overvoltage Protection**

- ♦ Sinusoidal Excitation for Reduced EMI Emissions

- Frequency Spreading Operation for Reduced EMI **Susceptibility and Emissions**

- ♦ Active-Guard-Sense Architecture Provides Increased Flexibility in System Packaging

- ♦ CMOS/LVCMOS-Compatible Outputs

- ♦ Embedded µC Supports User-Specified Adaptive Sense Algorithms

- ♦ 2kwords Flash Memory

- ♦ 128-Byte SRAM

- ♦ ±2kV ESD Immunity on Sensor I/O Lines

- JTAG Serial Interface

- Supports Two Independent Grounded Capacitor **Sensor Inputs**

- ◆ -12V Reverse Voltage Protection with External Diode

## **Applications**

PRKE System Proximity Sensing Object Detection Systems

## **Ordering Information**

| PART          | TEMP RANGE      | PIN-PACKAGE |  |  |

|---------------|-----------------|-------------|--|--|

| MAX1441GUP/V+ | -40°C to +105°C | 20 TSSOP    |  |  |

+Denotes a lead(Pb)-free/RoHS-compliant package. /V Denotes an automotive qualified part.

MAXQ is a registered trademark of Maxim Integrated Products, Inc.

### **ABSOLUTE MAXIMUM RATINGS**

| (VDD = VAA, AGND = DGND, unless otherwise noted.)     |

|-------------------------------------------------------|

| VBATT to AGND0.3V to +45V                             |

| VAA, VDD to AGND0.3V to +4V                           |

| SINPUT1, SINPUT2, AGUD1,                              |

| AGUD2 to AGND0.3V to (VAA + 0.3V)                     |

| RESET, PO, I.C. to DGND0.3V to (VDD + 0.3V)           |

| AGND to DGND0.3V to +0.3V                             |

| OUT1, OUT2, to AGND0.3V to +28V                       |

| OUT_, P0, Continuous Output Current   20mA            |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) |

| Single-Layer PCB                                      |

| 20-Lead TSSOP (derate 11mW/°C above +70°C)879mW       |

| Multilayer PCB                                        |

| 20-Lead TSSOP (derate 13.6mW/°C above +70°C)1084mW    |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> ) (Note 1 20-Lead TSSOP | +20°C/W     |

|------------------------------------------------------------------------------|-------------|

| 20-Lead TSSOP                                                                | +91°C/W     |

| 20-Lead TSSOP                                                                | +73.8°C/W   |

| Operating Temperature Range40°C                                              | C to +105°C |

| Junction Temperature                                                         | +150°C      |

| Storage Temperature Range65°C                                                | C to +150°C |

| Lead Temperature (soldering, 10s)                                            |             |

| Soldering Temperature (reflow)                                               | +260°C      |

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maxim-ic.com/thermal-tutorial.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

(VBATT = 5V to 28V, VAA = VDD, TA = -40°C to +105°C. Typical values are at VBATT = 14V,  $f_{EX}$  = 300kHz,  $T_{A}$  = +25°C, unless otherwise noted.) (Note 2)

| PARAMETER                           | SYMBOL                 | CONDITIONS                                                                                | MIN TYP MA |     | MAX  | UNITS            |  |

|-------------------------------------|------------------------|-------------------------------------------------------------------------------------------|------------|-----|------|------------------|--|

| Average Power-Supply Current        |                        | 16ms capacitance-to-digital (C2D) conversion time, two active channels; CPU in sleep mode |            | 100 | 120  | μА               |  |

| CAPACITANCE-TO-DIGITAL CO           | NVERTER                |                                                                                           |            |     |      |                  |  |

| Bit Resolution                      |                        |                                                                                           |            | 12  |      | Bits             |  |

|                                     |                        | CRNG_[1:0] = 10                                                                           |            | 20  |      |                  |  |

| Input Capacitance Range             |                        | CRNG_[1:0] = 01                                                                           |            | 10  |      | рF               |  |

|                                     |                        | CRNG_[1:0] = 00                                                                           |            | 5   |      |                  |  |

| Lauret Caracitanas I CD             |                        | 20pF capacitance range                                                                    |            | 4.8 |      |                  |  |

| Input Capacitance LSB Resolution    | 10pF capacitance range |                                                                                           |            | 2.4 |      | fF               |  |

| riesolution                         |                        | 5pF capacitance range                                                                     |            | 1.2 |      |                  |  |

| Integral Nonlinearity               | INL                    |                                                                                           |            | 1   |      | %FS              |  |

| Differential Nonlinearity           | DNL                    |                                                                                           |            | 0.5 |      | LSB              |  |

| Sampling Time                       |                        | f <sub>EX</sub> = 300kHz (Note 3)                                                         | 584        | 600 | 624  | μs               |  |

| Number of Effective Bits            |                        |                                                                                           |            | 11  |      | Bits             |  |

| DC Input Current of SIN1, SIN2      |                        |                                                                                           |            | 300 |      | nA               |  |

| INPUT CAPACITANCE EXCITATION SOURCE |                        |                                                                                           |            |     |      |                  |  |

| Source Peak-to-Peak Voltage 3       |                        | 300kHz excitation frequency                                                               | 0.96       | 1.0 | 1.21 | V <sub>P-P</sub> |  |

| Minimum Excitation Frequency        | fEXMIN                 | Frequency Control register = 0x0A (Note 3)                                                |            | 100 |      | kHz              |  |

| Maximum Excitation Frequency        | fEXMAX                 | Frequency Control register = 0x32 (Note 3)                                                | 500 kH     |     | kHz  |                  |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

(VBATT = 5V to 28V, VAA = VDD, TA = -40°C to +105°C. Typical values are at VBATT = 14V, fEX = 300kHz, TA = +25°C, unless otherwise noted.) (Note 2)

| PARAMETER                               | SYMBOL     | CONDITIONS                                  | MIN                      | TYP   | MAX  | UNITS  |

|-----------------------------------------|------------|---------------------------------------------|--------------------------|-------|------|--------|

| CAPACITIVE OFFSET DACS                  |            |                                             |                          |       |      |        |

| Offset Adjustment Range 6 bits          |            | 6 bits                                      |                          | 63    |      | pF     |

| Offset Adjustment Resolution            |            |                                             |                          | 1     |      | рF     |

| LOGIC INPUTS/OUTPUTS (P0                | RESET)     |                                             |                          |       |      |        |

| Output Logic Low                        | Vol        | ISINK = 2mA                                 |                          |       | 0.4  | V      |

| Output Logic High                       | Voн        | ISOURCE = 2mA                               | V <sub>DD</sub><br>- 0.5 |       |      | V      |

| Input Logic Low                         | VIL        | 3.0V < V <sub>DD</sub> < 3.6V               |                          |       | 0.8  | V      |

| Input Logic High                        | VIH        | 3.0V < V <sub>DD</sub> < 3.6V               | 2.4                      |       |      | V      |

| Leakage Current                         | IL         | I/O = high impedance                        |                          | 0.01  | 1    | μΑ     |

| Port 0 Interrupt Minimum Pulse<br>Width |            | 3.0V < V <sub>DD</sub> < 3.6V               |                          | 20    |      | ns     |

| HIGH-VOLTAGE OPEN-DRAIN (               | OUTPUTS (O | UT1, OUT2)                                  |                          |       |      |        |

| Output Logic Low                        | VOL2       | ISINK = 2mA                                 |                          |       | 0.5  | V      |

| Leakage Current                         | IL         | V <sub>OUT1</sub> = V <sub>OUT2</sub> = 25V |                          |       | 1    | μΑ     |

| MICROCONTROLLER                         |            |                                             |                          |       |      |        |

| Flash Program Memory Size               |            | 16 bits wide                                |                          | 2k    |      | Words  |

| Program Memory Clear Time               | tCPM       |                                             |                          | 38    |      | ms     |

| Page Write Time                         | t₩         |                                             |                          | 10    |      | ms     |

| Maximum Flash Erase/Write Cycles        | nCYC       |                                             |                          | 100k  |      | Cycles |

| SRAM Size                               |            |                                             |                          | 128   |      | Bytes  |

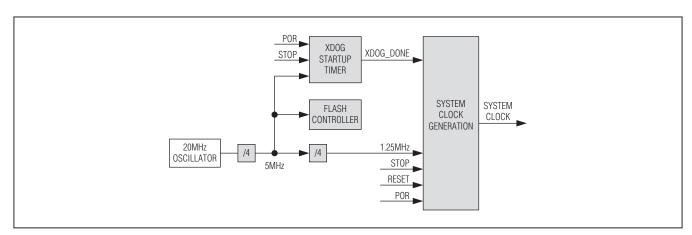

| CPU Clock Frequency                     | fCPU       |                                             |                          | 1.25  |      | MHz    |

| INTERNAL OSCILLATOR                     |            |                                             |                          |       |      |        |

| Ossillator Fraguenov                    |            | Master oscillator                           | 19.8                     | 20.48 | 21.2 | MHz    |

| Oscillator Frequency                    |            | RC oscillator                               | 31.7                     | 32    | 32.2 | kHz    |

| VOLTAGE REGULATOR                       |            |                                             |                          |       |      |        |

| Input Voltage                           | VBATT      |                                             | 5                        | 14    | 28   | V      |

| Maximum Dropout Voltage                 | VDROP      | IAA = 10mA                                  |                          | 0.6   |      | V      |

| Quiescent Current                       | IQ         |                                             |                          | 8     |      | μΑ     |

| Output Voltage                          | VAA        | 5V < VBATT < 28V, 0 < IAA < 10mA            | 3.2                      | 3.4   | 3.6  | V      |

**Note 2:** All units are production tested at  $T_A = +25^{\circ}C$  and  $T_A = +105^{\circ}C$ . Limits over the operating temperature range are guaranteed by design and characterization.

**Note 3:** Measured indirectly by testing the excitation signal frequency. The excitation signal frequency is determined by the master oscillator frequency, which in turn determines the sample time.

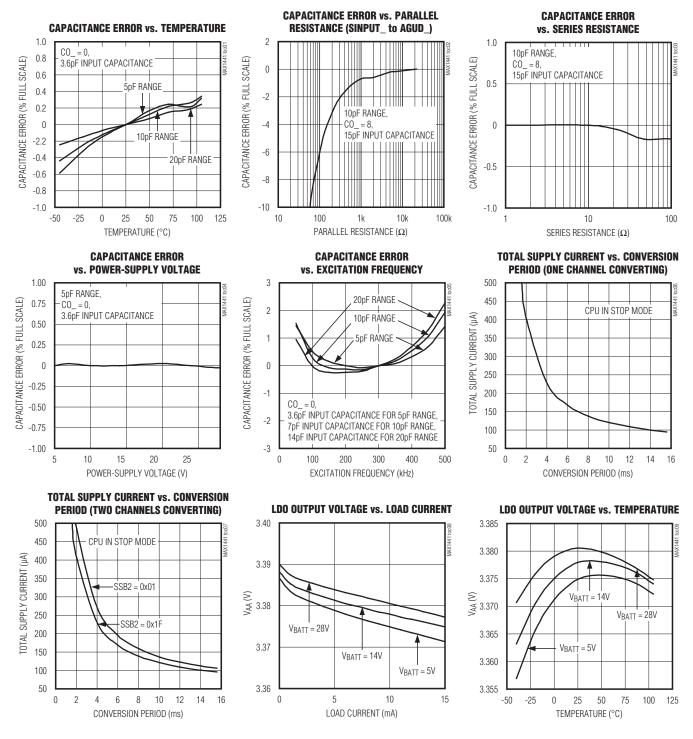

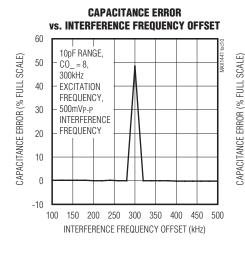

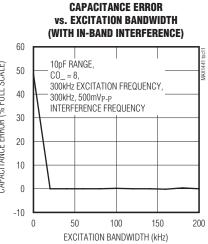

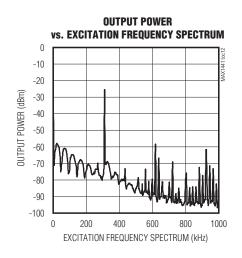

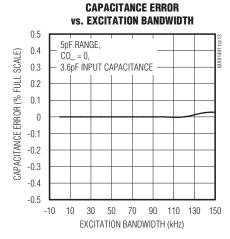

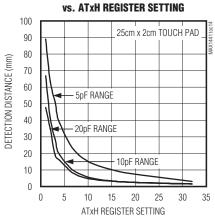

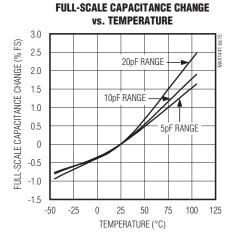

## **Typical Operating Characteristics**

(VBATT = 14V, VAA = VDD = 3.4V, TA = +25°C, unless otherwise noted.)

## Typical Operating Characteristics (continued)

(VBATT = 14V, VAA = VDD = 3.4V, TA = +25°C, unless otherwise noted.)

**DETECTION DISTANCE**

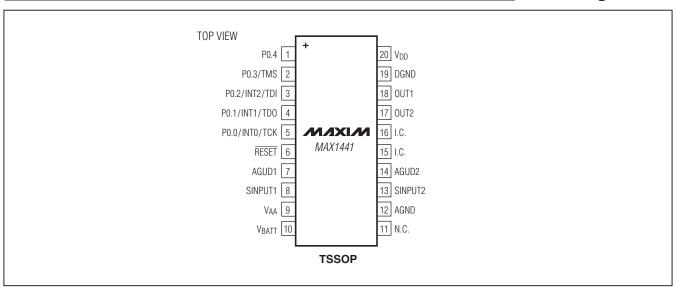

## **Pin Configuration**

## **Pin Description**

| PIN    | NAME                                                                                                                                                                          | FUNCTION                                                                                                                                                           |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | P0.4                                                                                                                                                                          | CPU Port 0 Bit 4. Digital input/output.                                                                                                                            |

| 2      | P0.3/TMS                                                                                                                                                                      | CPU Port 0 Bit 3/TMS. Digital input/output.                                                                                                                        |

| 3      | P0.2/INT2/TDI                                                                                                                                                                 | CPU Port 0 Bit 2/TDI. Digital input/output with configurable edge-triggered interrupt.                                                                             |

| 4      | P0.1/INT1/TDO                                                                                                                                                                 | CPU Port 0 Bit 1/TDO. Digital input/output with configurable edge-triggered interrupt.                                                                             |

| 5      | P0.0/INT0/TCK                                                                                                                                                                 | CPU Port 0 Bit 0/TCK. Digital input/output with configurable edge-triggered interrupt.                                                                             |

| 6      | RESET                                                                                                                                                                         | Active-Low Reset Input. RESET requires an external pullup to VDD.                                                                                                  |

| 7      | AGUD1                                                                                                                                                                         | Active Guard 1. Driven guard (active shield) output for channel 1.                                                                                                 |

| 8      | SINPUT1                                                                                                                                                                       | Sensor Input 1. Capacitive sensor electrode input for channel 1.                                                                                                   |

| 9      | VAA  Analog Power Supply. VAA is internally connected to the output of an on-chip 3.4V line Connect VAA to VDD. Bypass VAA with a 0.47µF capacitor to AGND as close to VAA as |                                                                                                                                                                    |

| 10     | VBATT                                                                                                                                                                         | Power-Supply Voltage. Input to the 3.4V on-chip linear regulator. Bypass VBATT to AGND with a 0.1µF capacitor as close to VBATT as possible.                       |

| 11     | N.C.                                                                                                                                                                          | No Connection. Not internally connected. Leave N.C. unconnected.                                                                                                   |

| 12     | AGND                                                                                                                                                                          | Analog Ground. Connect AGND to DGND.                                                                                                                               |

| 13     | SINPUT2                                                                                                                                                                       | Sensor Input 2. Capacitive sensor electrode input for channel 2.                                                                                                   |

| 14     | AGUD2                                                                                                                                                                         | Active Guard 2. Driven guard (active shield) output for channel 2.                                                                                                 |

| 15, 16 | I.C.                                                                                                                                                                          | Internally Connected. Leave unconnected.                                                                                                                           |

| 17     | OUT2                                                                                                                                                                          | Open-Drain Output 2. CPU port 0 bit 6.                                                                                                                             |

| 18     | OUT1                                                                                                                                                                          | Open-Drain Output 1. CPU port 0 bit 5.                                                                                                                             |

| 19     | DGND                                                                                                                                                                          | Digital Ground. Connect DGND to AGND.                                                                                                                              |

| 20     | V <sub>DD</sub>                                                                                                                                                               | Digital Power Supply. Connect V <sub>DD</sub> to V <sub>AA</sub> . Bypass V <sub>DD</sub> with a 0.47µF capacitor to DGND as close to V <sub>DD</sub> as possible. |

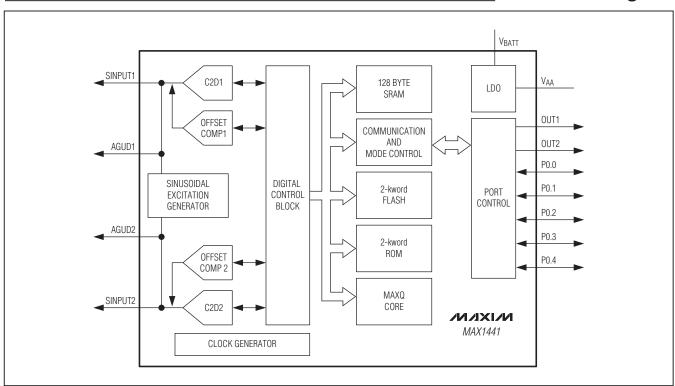

## **Functional Diagram**

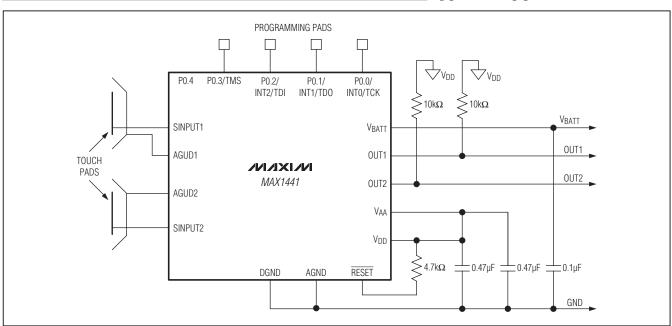

# **Typical Application Circuit**

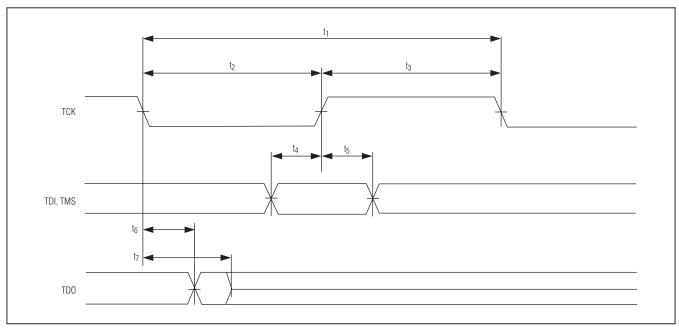

Figure 1. JTAG Timing Diagram

## **Detailed Description**

The MAX1441 is a 2-channel proximity and touch sensor that contains all the functions necessary to implement a proximity/touch detection system for vehicle PRKE systems and other applications. There are four principal architectural components to the device: the capacitive sensing analog front-end (AFE), a programmable CPU system, vehicle power, and I/O interface. Figure 1 shows the JTAG timing diagram.

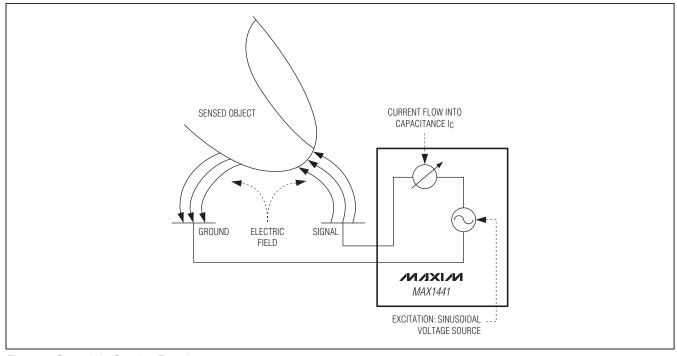

The AFE uses a 2-channel C2D converter to measure the capacitance present between sensor inputs SINPUT1 and SINPUT2 and the ambient ground (Figure 2). The AFE-sensing architecture converts approaching hand motion to 12-bit digital words that are operated by an algorithm in the CPU to ensure detection of positive events and minimizing false detections. The C2D converters can measure the input capacitance in three different ranges: 20pF, 10pF, and 5pF. Additionally, the C2Ds compensate up to 63pF of parasitic capacitance programmable in 1pF steps.

In addition to capacitive proximity and touch detection, the AFE contains POR and a watchdog timer for monitoring CPU operations. The CPU runs the input capacitive data through an algorithm to ensure detection of positive events and minimizing false detections. The CPU system includes Flash-based program memory, SRAM, clocks,

and communications. The power input and signal outputs provide a complete interface to the vehicle power system and a robust communication signal to remote electronic control modules (ECUs).

#### **Technical Function**

Each C2D converter produces an AC excitation voltage at inputs SINPUT1 and SINPUT2. The excitation voltage forces current through the capacitance connected to the sensor input. The current amplitude is proportional to the measured capacitance. The circuit measures the input capacitance by measuring the current flowing through the sensor inputs. This excitation signal is a sine wave with a frequency programmable from 100kHz to 500kHz in10kHz steps. The sinusoidal excitation allows for much lower EMI emissions compared to architectures that utilize simple square-wave excitation.

The device drives the guard outputs AGUD1 and AUGD2 with the same signal from the sinusoidal excitation and shields the sense electrodes without adding parasitic capacitance. The converter measures the amplitude of the current and converts it to 12-bit digital data by a 12-bit C2D. The maximum conversion rate in each of the sensor channels is 1.66kHz.

The microcontroller reads the input capacitance values and uses a user-supplied custom algorithm to detect the object proximity. Once the proximity is detected,

Figure 2. Capacitive-Sensing Function

the microcontroller can use the OUT1 or OUT2 pins to signal the event to external modules. The GPIOs can also provide system or configuration inputs to the microcontroller.

The device has a power-saving standby mode for power-sensitive applications. In the standby mode, the microcontroller is powered down (CPU stop mode) and the analog front-end runs conversions at a reduced and programmable rate. A programmable hardware discriminator monitors the C2D converters outputs and brings the device out of standby mode when a potential object-proximity event is detected. The microcontroller can then analyze the capacitance data and validate the object-proximity event.

The on-chip watchdog timer requires periodic servicing from the microcontroller to ensure proper and continuous operation. The watchdog timer resets the microcontroller if it is not serviced. This prevents the microcontroller from permanently hanging up due to unpredicted code behavior.

The device features an on-chip voltage regulator allowing the part to operate with a wide range of power-supply voltage inputs: 5V to 28V with protection up to 45V. The regulator provides power for all the circuits making the device a very compact single-chip solution.

#### **Control Registers**

The device's analog front-end is controlled by a number of control registers. The C2D conversion results and the AFE status are accessible through status and result registers. All AFE registers are available in the microcontroller data space. The control registers support read and write operations. The status and result registers are read-only registers.

Communication between the CPU and the external interface and AFE registers is performed using read/write operations to CPU special-function registers (SFRs).

The SFRs are organized in three sections (Section I–Section III); each section consists of six modules (M0–M5). Table 1 shows the location of each SFR within the SFR sections (see the *Detailed Description* for more details).

#### **Sensed Capacitance Range**

The sensed capacitance range can be set independently for both channels. After power-up, the range is set to 20pF in both channels.

**Table 1. Important AFE Function Registers**

| _                                                                                    |

|--------------------------------------------------------------------------------------|

| FUNCTION                                                                             |

| Adjust the capacitance range                                                         |

| Set the frequency of excitation                                                      |

| Set the bandwidth of the spread-<br>spectrum modulation                              |

| Set the capacitance offset                                                           |

| Put the device in single-conversion mode                                             |

| Set the standby conversion rate                                                      |

| Set the channel 2 standby conversion rate subdivider                                 |

| Put the AFE in power-down mode (does not affect CPU operation)                       |

| Select the wakeup criteria (rate-of-<br>change and/or absolute capacitive<br>change) |

| Set the absolute wake-up threshold                                                   |

| Set the capacitance rate-of-<br>change threshold                                     |

| Channel 1 conversion result                                                          |

| Channel 2 conversion result                                                          |

| Interrupt status of the AFE                                                          |

|                                                                                      |

#### **Excitation Frequency**

To avoid interference, the excitation frequency can be adjusted to automatically spread within a frequency range. The lower frequency bound and spread-spectrum bandwidth registers determine this range. Spread spectrum continuously changes the excitation frequency so that the radiated power is distributed over a frequency range rather than a single frequency. This lowers the radiated energy density and thus leads to a cleaner spectrum. In addition, by changing the excitation frequency, the capacitance measurement becomes more immune against interference signals.

### Offset Capacitance

In case the capacitance measurement permanently reaches the upper or lower limit, there is a likelihood of a parasitic capacitance on top of the touch pads. This could be an ice coating on the door handle for example. In this case, the offset capacitance is adjusted so that the capacitance reenters the measurement range. A parasitic capacitance up to 63pF is compensated for each channel independently by properly setting the offset registers, CO1/CO2.

#### **Single Conversion Mode**

The C2D converter can be placed into a single conversion mode. In the single conversion mode, the microcontroller triggers a single conversion by setting bit SCT. If the single conversion mode is enabled, the analog front-end powers up only during the conversion. SCEN controls the single conversion mode. SCEN = 1 enables the single conversion mode and SCEN = 0 disables the single conversion mode. When single conversion mode is enabled, set bit SCT to trigger a conversion. SCT bit automatically clears after the conversion is completed.

### **Standby Control**

To save power, the analog front-end can be put in the standby state. During standby, the conversion rate is determined by the standby state conversion rate divider. SB controls the standby mode. SB = 1 enables the standby mode and SB = 0 disables the standby mode. There is only 1 SB bit common to both channels, so the channels cannot be placed in the standby state independently.

The following sequence of control register writes to the PD register is recommended for entering standby mode:

- 1) Set PD to 06h to put both AFE channels into reset state.

- 2) Write DSB and SSB2 registers to set standby rate (if not already set).

- 3) Set PD to 00h to release AFE reset.

- 4) Set PD to 01h to enter standby mode.

### Standby State Conversion-Rate Divider

The maximum C2D conversion rate is 1.66kHz. Standby state uses conversion-rate reduction to save power. The conversion rate divider and conversion rate subdivider determine the final conversion rate. The DSB divider DSB[4:0] is common to both sensor channels. The conversion rate for channel 2 can be further reduced by the SSB2[4:0] divider. The conversion rate in kHz is determined by the equation:

$$f_{conv,channel1} = \frac{1}{D} \times 1.66kHz$$

$$f_{conv,channel2} = \frac{1}{D \times S} \times 1.66kHz$$

where D is an integer number determined by a 5-bit word DSB[4:0] and S is an integer number determined by a 5-bit word SSB2[4:0]. The default value of D and S is one. D > 1 when SSB2 > 1.

#### **Power-Down Control**

Each sensor channel independently powers down through the PD register. Bit value 1 powers down the channel and bit value 0 powers up the channel. The excitation source circuitry powers down if both channels are powered down. Powering down both channels also resets all AFE internal circuits except for the AFE's control registers.

#### Wake-Up Event Thresholds

The sensor wakes up when the measured capacitance exceeds a set capacitance threshold and/or a predefined rate of change in the capacitance. When an object approaches the sensor, the sensed capacitance starts changing. Once the capacitance value crosses the absolute value threshold and/or the capacitance rate of change crosses the rate-of-change threshold, the analog front-end is automatically put in the wake-up state and the SB bit is cleared. At the same time, the wake-up interrupt is sent to the microcontroller. The 8-bit word ATx[11:4] determines the absolute wake-up threshold and 8-bit word RTx[11:4] determines the rate-of-change threshold. Only the upper 8 bits are used in the threshold comparisons. Bit AOx determines if logical AND or OR operation is performed on the absolute and the rate-of-change threshold crossing events to produce the wake-up event. Bit value 1 sets the AND operation and bit value 0 sets OR operation. Both absolute and rateof-change threshold crossing detection can be enabled or disabled using bits AEx and REx. AEx bit value 1 enables absolute value detection and REx bit value 1 enables rate-of-change detection. The thresholds can be independently programmed in channels 1 and 2.

### **Conversion Result Word**

The 12-bit result of the C2D conversion is available in CRSLT1L and CRSLT1H for channel 1 and in CRSLT2L

and CRSLT2H for channel 2. Bit OVRx is set to 1 if the current conversion caused overranging in the C2D converter.

### **Data Ready in Channel 1**

The interrupt status bit IDR1 is set to 1 when a new conversion result is available in channel 1. If the microcontroller does not read the conversion result before the next conversion is completed, the old conversion result is overwritten.

### **Data Ready in Channel 2**

The interrupt status bit IDR2 is set to 1 when a the new conversion result is available in channel 2. If the microcontroller does not read the conversion result before the next conversion is completed, the old conversion result is overwritten.

### Wake-Up Event in Channel 1

The interrupt status bit IWUP1 is set to 1 when channel 1 detects a wake-up condition.

#### Wake-Up Event in Channel 2

The interrupt status bit IWUP2 is set to 1 when channel 2 detects a wake-up condition.

## \_Detailed Controller Specification

#### **Architecture**

The device is based on the MAXQ RISC processor with Harvard memory architecture.

# Specific MAXQ Special-Purpose Register Implementation

The device implements all other standard MAXQ special-purpose registers (SPRs). For details, see the SPR bit description in Table 5.

#### **Special-Purpose Registers**

Table 2 summarizes the SPRs and their address indexes. These registers can be accessed by user software.

Table 2. Special-Purpose Register Map

| МО     | DULE      |       | INDEX OF SPECIAL-PURPOSE REGISTER |       |       |       |       |       |       |       |       |       |       |       |       |       |       |

|--------|-----------|-------|-----------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| MODULE | SPECIFIER | 00000 | 00001                             | 00010 | 00011 | 00100 | 00101 | 00110 | 00111 | 01000 | 01001 | 01010 | 01011 | 01100 | 01101 | 01110 | 01111 |

| AP     | 01000     | AP    | APC                               | _     | _     | PSF   | IC    | IMR   | _     | SC    | _     | _     | IIR   | _     | _     | CKCN  | WDCN  |

| А      | 01001     | A0    | A1                                | A2    | АЗ    | _     | _     | _     | _     | _     | _     | _     | _     | _     | _     | _     | _     |

| PFX    | 01011     | PFX   | _                                 | _     | _     | _     | _     | _     | _     | _     | _     | _     | _     | _     | _     | _     | _     |

| IP     | 01100     | IP    | _                                 | _     | _     | _     | _     | _     | _     | _     | _     | _     | _     | _     | _     | _     | _     |

| SP     | 01101     | _     | SP                                | IV    | _     | _     | _     | LC0   | LC1   | _     | _     | _     | _     | _     | _     | _     | _     |

| DPC    | 01110     | _     | _                                 | _     | Offs  | DPC   | GR    | GRL   | BP    | GRS   | GRH   | GRXL  | FP    | _     | _     | _     | _     |

| DP     | 01111     | _     | _                                 | _     | DP0   | _     | _     | _     | DP1   | _     | _     | _     | CP    | _     | _     | _     | _     |

Indexes not specified in this table are either reserved for hardware functional use or for future expansion; access to these locations has deterministic behavior that may not be the intention of the user. Register addresses highlighted in the table are reserved.

Table 3 lists the SPR registers' functional bits and their bit positions. Table 4 specifies the default reset condition for all SPR bits. The default value for unused SPR

bit locations is 0. For registers in the accumulator and Loop module, all 16 bits are undetermined after a reset. Undetermined values are labeled as "i" in the table. Special default values are labeled as "s" in the table.

Table 5 details all SPRs and their bit description. Registers are also identified by their address in the form of (xxh, yyh), where xxh is the register index in hex and yyh is the module specifier in hex.

Table 3. Special-Purpose Register Bit Function

| REGIS | TER    | MSB       |      |      |      |      |      |      | LSB  |

|-------|--------|-----------|------|------|------|------|------|------|------|

| AP    | [7:0]  | _         | _    | _    | _    | _    | _    | AP1  | AP0  |

| APC   | [7:0]  | CLR       | IDS  | _    | _    | _    | _    | MOD1 | MOD0 |

| PSF   | [7:0]  | Z         | S    | _    | GPF1 | GPF0 | OV   | С    | E    |

| IC    | [7:0]  | _         | _    | _    | _    | _    | _    | INS  | IGE  |

| IMR   | [7:0]  | IMS       | _    | _    | _    | _    | _    | IM1  | IMO  |

| SC    | [7:0]  | TAP       | _    | _    | _    | _    | ROD  | PWL  | _    |

| IIR   | [7:0]  | IIS       | _    | _    | _    | _    | _    | _    | _    |

| CKCN  | [7:0]  | IDLE      | _    | _    | _    | _    | _    | _    | _    |

| WDCN  | [7:0]  | POR       | EWDI | WD1  | WD0  | WDIF | WTRF | EWT  | RWT  |

| A0    | [15:0] | A0[15:0]  |      |      |      |      |      |      |      |

| A1    | [15:0] | A1[15:0]  |      |      |      |      |      |      |      |

| A2    | [15:0] | A2[15:0]  |      |      |      |      |      |      |      |

| A3    | [15:0] | A2[15:0]  |      |      |      |      |      |      |      |

| PFX   | [15:0] | PFX[15:0] |      |      |      |      |      |      |      |

| IP    | [15:0] | IP[15:0]  |      |      |      |      |      |      |      |

| SP    | [15:0] | SP[15:0]  |      |      |      |      |      |      |      |

| IV    | [15:0] | IV[15:0]  |      |      |      |      |      |      |      |

| LC0   | [15:0] | LC0[15:0] |      |      |      |      |      |      |      |

| LC1   | [15:0] | LC1[15:0] |      |      |      |      |      |      |      |

| DPC   | [7:0]  | _         | _    | _    | _    | _    | WBS0 | _    | _    |

| GR    | [15:0] | GR[15:0]  |      |      |      |      |      |      |      |

| GRL   | [7:0]  | GRL[7:0]  |      |      |      |      |      |      |      |

| GRS   | [15:8] | GR7       | GR6  | GR5  | GR4  | GR3  | GR2  | GR1  | GR0  |

| Gno   | [7:0]  | GR15      | GR14 | GR13 | GR12 | GR11 | GR10 | GR9  | GR8  |

| GRH   | [7:0]  | GRH[7:0]  |      |      |      |      |      |      |      |

| GRXL  | [15:8] | GR7       | GR7  | GR7  | GR7  | GR7  | GR7  | GR7  | GR7  |

| GIAL  | [7:0]  | GR7       | GR6  | GR5  | GR4  | GR3  | GR2  | GR1  | GR0  |

| DP0   | [15:0] | DP0[15:0] |      |      |      |      |      |      |      |

**Table 4. Special-Purpose Registers' Reset Values**

| REGISTER | MSB  |      |      | LSB  |

|----------|------|------|------|------|

| AP       | _    | _    | 0000 | 0000 |

| APC      | _    | _    | 0000 | 0000 |

| PSF      | _    | _    | 1000 | 0000 |

| IC       | _    | _    | 0000 | 0000 |

| IMR      | _    | _    | 0000 | 0000 |

| SC       | _    | _    | 1000 | 00s0 |

| IIR      | _    | _    | 0000 | 0000 |

| CKCN     | _    | _    | 1110 | 0000 |

| WDCN     | _    | _    | ss11 | 0ss0 |

| A0       | 0000 | 0000 | 0000 | 0000 |

| A1       | 0000 | 0000 | 0000 | 0000 |

| A2       | 0000 | 0000 | 0000 | 0000 |

| A3       | 0000 | 0000 | 0000 | 0000 |

| REGISTER | MSB  |      |      | LSB  |

|----------|------|------|------|------|

| PFX      | 0000 | 0000 | 0000 | 0000 |

| IP       | 1000 | 0000 | 0000 | 0000 |

| SP       | 0000 | 0000 | 0010 | 1111 |

| IV       | 0000 | 0111 | 1111 | 1101 |

| LC0      | 0000 | 0000 | 0000 | 0000 |

| LC1      | 0000 | 0000 | 0000 | 0000 |

| DPC      | 0000 | 0000 | 0000 | 0100 |

| GR       | 0000 | 0000 | 0000 | 0000 |

| GRL      | _    | _    | 0000 | 0000 |

| GRS      | 0000 | 0000 | 0000 | 0000 |

| GRH      | _    | _    | 0000 | 0000 |

| GRXL     | 0000 | 0000 | 0000 | 0000 |

| DP0      | 0000 | 0000 | 0000 | 0000 |

Table 5. Special-Purpose Register Bit Description

| REGISTER          |                                                                                                                                                                                                                                                                                                                                                            | DESCRIPTION                                                                                                                                  |  |  |  |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| AP (00h, 08h)     | Accumulator Pointer (8-Bit Register)                                                                                                                                                                                                                                                                                                                       |                                                                                                                                              |  |  |  |  |

| Initialization    | This register is cleared to 00h on                                                                                                                                                                                                                                                                                                                         | all forms of reset.                                                                                                                          |  |  |  |  |

| Read/Write Access | Unrestricted read/write.                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                              |  |  |  |  |

| AP[1:0]           | Active Accumulator Select Bits [1:0]. The setting of these bits activates one of the four accumulators in the accumulator module (A) to function as the active accumulator for arithmetic and logical operations. The setting of these bits can be automatically incremented/decremented in a modulo fashion according to the setting to the APC register. |                                                                                                                                              |  |  |  |  |

| AP[7:2]           | Reserved. Read returns 0.                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                              |  |  |  |  |

| APC (01h, 08h)    | Accumulator Pointer Control (8                                                                                                                                                                                                                                                                                                                             | 3-Bit Register)                                                                                                                              |  |  |  |  |

| Initialization    | This register is cleared to 00h on                                                                                                                                                                                                                                                                                                                         | all forms of reset.                                                                                                                          |  |  |  |  |

| Read/Write Access | Unrestricted read/write.                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                              |  |  |  |  |

|                   | bits are set to a value other than ment/decrement is active.                                                                                                                                                                                                                                                                                               | ator pointer autoincrement/decrement function is activated when these 00b. The modulo is selected accordingly when active pointer autoincre- |  |  |  |  |

| APC[1:0]-MOD[1:0] | MOD[1:0]                                                                                                                                                                                                                                                                                                                                                   | MODULO                                                                                                                                       |  |  |  |  |

| / o[o]oz[o]       | 00                                                                                                                                                                                                                                                                                                                                                         | Default, no AP autoincrement/decrement                                                                                                       |  |  |  |  |

|                   | 01                                                                                                                                                                                                                                                                                                                                                         | Modulo 2                                                                                                                                     |  |  |  |  |

|                   | 10                                                                                                                                                                                                                                                                                                                                                         | Modulo 4                                                                                                                                     |  |  |  |  |

|                   | 11                                                                                                                                                                                                                                                                                                                                                         | Reserved (modulo 4 if set)                                                                                                                   |  |  |  |  |

| APC[5:2]          | Reserved. Read returns 0.                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                              |  |  |  |  |

| APC.6-IDS         | <b>Increment/Decrement Select.</b> When this bit is cleared to 0, the content of AP increments after an arithmetic or logical operation. When this bit is set to 1, the content of AP is decremented after arithmetic or logical operation.                                                                                                                |                                                                                                                                              |  |  |  |  |

| APC.7-CLR         | AP Clear. When this bit is set to 1, the content of AP is cleared to 0. This bit automatically resets to 0 after clearing the AP register. Note if the MOVE APC, Acc instruction (980Ah) causes the CLR bit to set, the clear operation overrides other functions (i.e., the AP autoincrement/decrement does not happen).                                  |                                                                                                                                              |  |  |  |  |

# Table 5. Special-Purpose Register Bit Description (continued)

| REGISTER          | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PSF (04h, 08h)    | Processor Status Flags Register (8-Bit Register)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Initialization    | This register is set to 80h on all forms of reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Read/Write Access | Unrestricted direct read. Write access to OV, E, C, GPF1, and GPF0 bits only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| PSF.0-E           | <b>Equal Flag.</b> This flag reflects the state of the Equal bit of a compare operation. It is 1 when the two values are equal. It is 0 when the two values are different. Writing a 1 to this bit by software is effectively set by the Equal flag.                                                                                                                                                                                                                                                                                                                                                                                                  |

| PSF.1-C           | <b>Carry Flag.</b> This flag reflects the state of the Carry bit of the active accumulator. Its state may change after an arithmetic and logical operation. This flag is set to 1 if the last operation resulted in a carry/borrow. Otherwise, it is cleared to 0. Writing a 1 to this bit by software is effectively set by the Carry flag.                                                                                                                                                                                                                                                                                                          |

| PSF.2-OV          | <b>Overflow Flag.</b> This flag is set to 1 if there is a carry out of bit 14 but not out of bit 15, or a carry out of bit 15 bit not out of bit 14 from the last arithmetic operation; otherwise, the OV remains as 0. When adding signed numbers, OV indicates a negative number resulted as the sum of two positive operands, or a positive sum resulted from two negative operands. For subtraction, OV is set if a borrow is needed into bit 14 but not into bit 15, or into bit 15 but not into bit 14.  This bit can be read and written by software to allow it to be restored after events such as interrupt servicing and debug operations. |

| PSF.3-GPF0        | General-Purpose Flag 0. This is a general-purpose flag for software control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PSF.4-GPF1        | General-Purpose Flag 1. This is a general-purpose flag for software control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PSF.5             | Reserved. Read returns 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| PSF.6-S           | <b>Sign Flag.</b> This flag reflects the state of the Sign bit of the active accumulator (the most significant bit of the active accumulator). Its state may change after an arithmetic and logical operation or after the switch of the active accumulator. When it is set to 1, it indicates a negative value in the active accumulator from the last operation. When it is cleared to 0, it indicates a positive value.                                                                                                                                                                                                                            |

| PSF.7–Z           | <b>Zero Flag.</b> This flag reflects the state of the Zero bit of the active accumulator (bit-wise NOR of the active accumulator). Its state may change after an arithmetic and logical operation or after the switch of the active accumulator. When it is set to 1, it indicates a zero value as a result of the last operation. When it is cleared to 0, it indicates a nonzero value.                                                                                                                                                                                                                                                             |

| IC (05h, 08h)     | Interrupt and Control Register (8-Bit Register)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Initialization    | This register is cleared to 00h on all forms of reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Read/Write Access | Unrestricted read/write.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| IC.0-IGE          | <b>Interrupt Global Enable.</b> The IGE bit enables the interrupt handler if set to 1. No interrupt to the CPU is allowed if this bit is cleared to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| IC.1-INS          | Interrupt In Service. The INS is set by the interrupt handler automatically when an interrupt is acknowledged. No further interrupt occurs as long as the INS remains set. The interrupt service routine can clear the INS to allow interrupt nesting. Otherwise, at the execution of an RETI/POPI instruction, the INS is cleared automatically by the interrupt handler.                                                                                                                                                                                                                                                                            |

| IC[7:2]           | Reserved. Read returns 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| IMR (06h, 08h)    | Interrupt Mask Register (8-Bit Register)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Initialization    | This register is cleared 80h on all forms of reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Read/Write Access | Unrestricted read. All bits have unrestricted write access, unless otherwise stated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| IMR.0-IM0         | <b>Interrupt Mask 0.</b> This bit is the module level interrupt enable for register module 0. To activate the interrupt request from module 0, the IGE and IM0 must be set and the INS is not set. Clearing this bit to 0 disables all interrupt sources in module 0.                                                                                                                                                                                                                                                                                                                                                                                 |

**Table 5. Special-Purpose Register Bit Description (continued)**

| REGISTER                                                                                                     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| IMR.1-IM1                                                                                                    | <b>Interrupt Mask 1.</b> This bit is the module level interrupt enable for register module 1. To activate the interrupt request from module 1, the IGE and IM1 must be set and the INS is not set. Clearing this bit to 0 disables all interrupt sources in module 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

| IMR[6:2]                                                                                                     | Reserved. Read returns 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |

| IMR.7-IMS                                                                                                    | Interrupt Mask 7. This bit is the module level interrupt enable for SPR modules. To activate the interrupt request from any SPR modules, the IGE and IMS must be set and the INS is not set. Clearing this bit to 0 disables all interrupt sources in all SPR modules.  This bit is read only and defaults to 1 on all forms of reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| SC (08h, 08h)                                                                                                | System Control Register (8-Bit Register)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |