a leap ahead

**20** austria**micro**systems

## AS1526, AS1527 10-Bit, Single Supply, Low-Power, 73ksps A/D Converters

# **1** General Description

The AS1526/AS1527 are low-power, 10-bit, 73ksps analog-to-digital (A/D) converters specifically designed for single-supply A/D applications. Superior AC characteristics, very low power consumption, and robust packaging make these ultra-small devices perfect for battery-powered analog-data collection devices.

The integrated successive-approximation register (SAR) and a fast (1.5µs) sampling track/hold time provide an economic and highly-reliable A/D conversion solution.

The AS1526/AS1527 operate from a single 2.7 to 3.6V supply. The AS1527 requires an external reference. using less power than the AS1526, however, the AS1526 features an internal 2.5V reference.

As with the AS1527, the AS1526 can also be used with an external reference, which uses the input range 0V to VREF, including the positive supply range.

The AS1527 consumes only 3mW (VDD = 3V) at the 73ksps maximum sampling speed. Both devices feature a low-current (0.3µA) shutdown mode, which reduces power consumption at slower throughput rates.

Data accesses are made via the standard, high-speed 3-wire serial interface, which is SPI-, QSPI-, and Microwire-compatible. Both devices contain an internal clock, however, both devices also support an external clock for increased flexibility.

The AS1526/AS1527 are available in an 8-pin SOIC-150 package.

## 2 Key Features

- 10-Bit Resolution with 7.5µs Conversion Time

- Sampling Rate: 73ksps

- Straight Binary (Unipolar) Data Format

- Single-Supply Operation:+2.7 to +3.6V

- Internal 2.5V Reference (AS1526)

- Low Power-Consumption:

- 4mW (73ksps, AS1526)

- 3mW (73ksps, AS1527)

- 66µW (1ksps, AS1527)

- 1µW (Shutdown Mode)

- Integrated Track/Hold Amplifier

- Internal Clock

- SPI/QSPI/Microwire 3-Wire Serial Interface

- Operating Temperature Range: -40 to +85°C

- 8-pin SOIC-150 Package

# **3** Applications

The devices are ideal for remote sensors, data-acquisition, data logging devices, lab instruments, or for any other space-limited A/D devices with low power consumption and single-supply requirements.

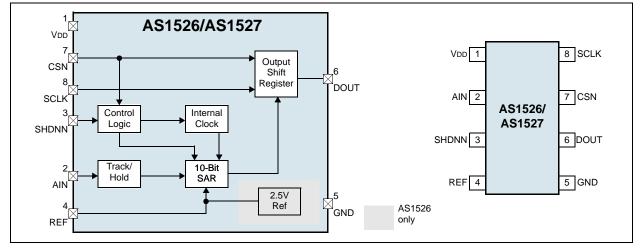

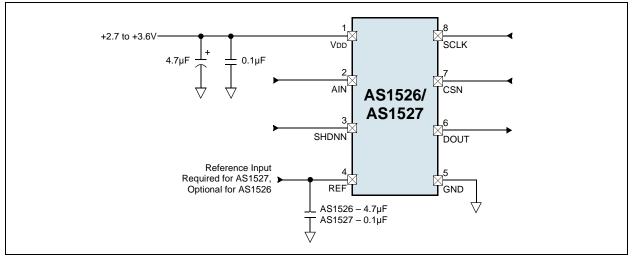

#### Figure 1. Block Diagram and Pin Assignments

**DataSheet**

## Contents

| 1  | General Description                  | 1   |

|----|--------------------------------------|-----|

| 2  | Key Features                         | 1   |

| 3  | Applications                         | 1   |

| 4  | Pinout and Packaging                 | 3   |

|    | Pin Assignments                      | 3   |

|    | Pin Descriptions                     | 3   |

| 5  | Absolute Maximum Ratings             | 4   |

| 6  | Electrical Characteristics           | 5   |

|    | Timing Characteristics               | 7   |

| 7  | Typical Operating Characteristics    | 8   |

| 8  | Detailed Description                 | 11  |

|    | Analog Input                         |     |

|    | Input Protection                     |     |

|    | Track/Hold                           |     |

|    | External Clock                       |     |

|    | Timing and Control                   |     |

|    | Transfer Function                    |     |

|    | Reducing Supply Current              |     |

|    | Internal 2.5V Reference (AS1526)     |     |

| _  | External Reference                   |     |

| 9  | Application Information              |     |

|    | Initialization                       |     |

|    | Serial Interface                     |     |

|    | Serial Interface Configuration       |     |

|    | SPI and Microwire Interfaces QSPI 17 | .16 |

|    | Layout Considerations                | .18 |

|    | Package Drawings and Markings        | .19 |

| 10 | Ordering Information                 | 20  |

# 4 Pinout and Packaging

## **Pin Assignments**

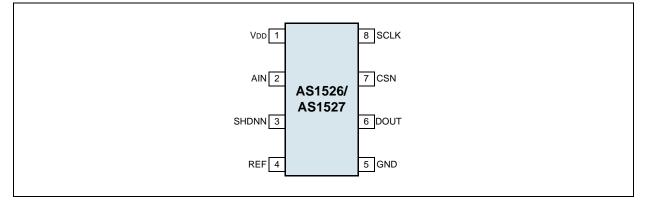

Figure 2. Pin Assignments (Top View)

## **Pin Descriptions**

Table 1. Pin Descriptions

| Pin Number | Pin Name | Description                                                                                                                                                                                                                                                                                                                                                                                     |

|------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | Vdd      | Positive Supply Voltage. +2.7 to +3.6V                                                                                                                                                                                                                                                                                                                                                          |

| 2          | AIN      | Sampling Analog Input. 0V to VREF range.                                                                                                                                                                                                                                                                                                                                                        |

| 3          | SHDNN    | <b>Three-Level Shutdown Input</b> . Pulling this pin low puts the AS1526/AS1527 in shutdown mode, down to $4\mu$ A (max) supply current. The devices are fully operational with this pin high or floating.                                                                                                                                                                                      |

|            | Childran | <b>Note:</b> For the AS1526, pulling this pin high enables the internal reference; letting this pin float disables the internal reference allowing for the use of an external reference. See also pin 4.                                                                                                                                                                                        |

| 4          | REF      | <b>A/D Conversion Reference Voltage</b> . This pin serves as the internal 2.5V reference output for the AS1526; bypass this pin with a 4.7 $\mu$ F capacitor. This pin also serves as the external reference voltage input for the AS1527, or for AS1526 if the internal reference is disabled. Bypass this pin with a minimum of 0.1 $\mu$ F when using an external reference. See also pin 3. |

| 5          | GND      | Analog and Digital Ground                                                                                                                                                                                                                                                                                                                                                                       |

| 6 DOUL     |          | Serial Data Output. Data changes state at SCLK's falling edge.<br>Note: This pin is high-impedance when pin CSN is high.                                                                                                                                                                                                                                                                        |

| 7          | CSN      | Active-Low Chip Select. The falling edge of this pin initiates a conversion.<br>Note: When this pin is high, DOUT is high-impedance.                                                                                                                                                                                                                                                            |

| 8          | SCLK     | Serial Clock Input. This pin clocks data out at rates up to 2.1MHz.                                                                                                                                                                                                                                                                                                                             |

# **5** Absolute Maximum Ratings

Stresses beyond those listed in Table 2 may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in Section 6 Electrical Characteristics on page 5 is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table 2. Absolute Maximum Ratings

| Parameter                                      | Min  | Max           | Units | Comments                                                                                                                                                                                                               |

|------------------------------------------------|------|---------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD to GND                                     | 0.3  | +5            | V     |                                                                                                                                                                                                                        |

| AIN to GND                                     | -0.3 | VDD +<br>0.3V | V     |                                                                                                                                                                                                                        |

| REF to GND                                     | -0.3 | VDD +<br>0.3V | V     |                                                                                                                                                                                                                        |

| Digital Inputs to GND                          | -0.3 | VDD +<br>0.3V | V     |                                                                                                                                                                                                                        |

| DOUT to GND                                    | -0.3 | VDD +<br>0.3V | V     |                                                                                                                                                                                                                        |

| DOUT Current                                   | -25  | +25           | mA    |                                                                                                                                                                                                                        |

| Continuous Power Dissipation<br>(ТАМВ = +70°С) |      | 471           | mW    | Derate 5.88mW/ºC above +70ºC                                                                                                                                                                                           |

| Operating Temperature Range                    | -40  | +85           | ٥C    |                                                                                                                                                                                                                        |

| Storage Temperature Range                      | -60  | +150          | ٥C    |                                                                                                                                                                                                                        |

| Package-Body Peak Temperature                  |      | 260           | °C    | The reflow peak soldering temperature (body temperature) specified is in accordance with <i>IPC/JEDEC J-STD-020C "Moisture/Reflow Sensitivity Classification for non-hermetic Solid State Surface Mount Devices"</i> . |

# **6 Electrical Characteristics**

$V_{DD} = +2.7$  to +3.6V, 73ksps, fscLK = 2.1MHz (50% duty cycle); AS1526:4.7 $\mu$ F capacitor at REF, AS1527: external reference;  $V_{REF} = 2.5V$  applied to REF; TAMB = TMIN to TMAX (unless otherwise specified).

Table 3. Electrical Characteristics

| Symbol     | Parameter                             | Conditions                               | Min    | Тур   | Max           | Units    |

|------------|---------------------------------------|------------------------------------------|--------|-------|---------------|----------|

| DC Accu    | racy <sup>1</sup>                     |                                          |        |       |               |          |

|            | Resolution                            |                                          | 10     |       |               | Bits     |

|            | Relative Accuracy <sup>2</sup>        |                                          |        |       | ±0.5          | LSB      |

| DNL        | Differential Non-Linearity            | No missing codes over temperature        |        |       | ±1            | LSB      |

|            | Offset Error                          |                                          |        |       | ±2            | LSB      |

|            | Gain Error <sup>3</sup>               |                                          |        |       | ±2            | LSB      |

|            | Gain Temperature Coefficient          |                                          |        | ±1    |               | ppm/°C   |

| Dynamic    | Specifications (10kHz sine-wave       | e input, 0V to 2.5Vp-p, 73ksps, fscLκ =2 | .1MHz) |       | 1             | <u> </u> |

| SINAD      | Signal-to-Noise + Distortion<br>Ratio |                                          |        | 61    |               | dB       |

| THD        | Total Harmonic Distortion             | Up to the 5th harmonic                   |        | -70   |               | dB       |

| SFDR       | Spurious-Free Dynamic Range           |                                          |        | 70    |               | dB       |

|            | Small-Signal Bandwidth                | -3dB rolloff                             |        | 2.5   |               | MHz      |

|            | Full-Power Bandwidth                  |                                          |        | 2.5   |               | MHz      |

| Conversi   | ion Rate                              |                                          | -      |       |               |          |

| tCONV      | Conversion Time                       |                                          | 5.5    |       | 7.5           | μs       |

| tACQ       | Track/Hold Acquisition Time           |                                          |        |       | 1.5           | μs       |

|            | Throughput Rate <sup>4</sup>          | fsclk = 2.1MHz                           |        |       | 73            | ksps     |

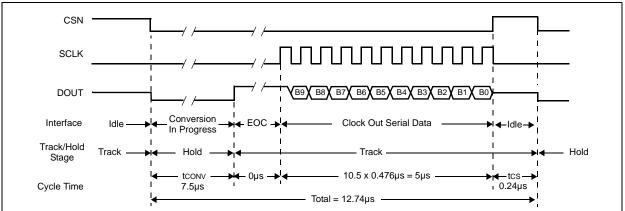

| tAP        | Aperture Delay                        | Figure 27 on page 13                     |        | 7     |               | ns       |

|            | Aperture Jitter                       |                                          |        | <50   |               | ps       |

| Analog li  | nput                                  |                                          |        |       |               |          |

|            | Input Voltage Range                   |                                          | 0      |       | Vref          | V        |

|            | Input Capacitance                     |                                          |        | 21    |               | pF       |

| Internal I | Reference (AS1526 only)               |                                          |        |       |               |          |

|            | REF Output Voltage                    | TAMB = +25°C <sup>5</sup>                | 2.47   | 2.50  | 2.53          | V        |

|            | REF Short-Circuit Current             |                                          |        |       | 45            | mA       |

|            | REF Temperature Coefficient           | AS1526                                   |        | ±30   |               | ppm/°C   |

|            | Load Regulation <sup>6</sup>          | 0 to 0.2mA output load                   |        | 0.35  |               | mV       |

| CREFBYP    | Capacitive Bypass at REF              |                                          | 4.7    |       |               | μF       |

| External   | <b>Reference</b> (VREF = 2.5V)        |                                          |        |       |               |          |

|            | Input Voltage Range                   |                                          | 1.00   |       | Vdd +<br>50mV | V        |

|            | Input Current                         |                                          |        | 100   | 150           | μA       |

|            | Input Resistance                      |                                          | 18     | 25    |               | kΩ       |

|            | REF Input Current in Shutdown         | SHDNN = 0V                               |        | ±0.01 | 10            | μA       |

| CREFBYP    | Capacitive Bypass at REF              |                                          | 0.1    |       |               | μF       |

| Symbol     | Parameter                               | Conditions                                  | Min          | Тур   | Max          | Units |

|------------|-----------------------------------------|---------------------------------------------|--------------|-------|--------------|-------|

| Digital In | puts: SCLK, SHDNN, CSN                  |                                             |              |       |              |       |

| Vін        | SCLK, CSN Input High Voltage            |                                             | 0.7x<br>Vdd  |       |              | V     |

| VIL        | SCLK, CSN Input Low Voltage             |                                             |              |       | 0.3x<br>Vdd  | V     |

| VHYST      | SCLK, CSN Input Hysteresis              |                                             |              | 0.2   |              | V     |

| lin        | SCLK, CSN Input Leakage                 | VIN = 0V or VDD                             |              | ±0.01 | ±1           | μΑ    |

| CIN        | SCLK, CSN Input Capacitance 7           |                                             |              |       | 15           | pF    |

| Vsн        | SHDNN Input High Voltage                |                                             | Vdd -<br>0.4 |       |              | V     |

| Vsl        | SHDNN Input Low Voltage                 |                                             |              |       | 0.4          | V     |

|            | SHDNN Input Current                     | SHDNN = 0V or VDD                           |              |       | ±4.0         | μA    |

| Vsм        | SHDNN Input Mid Voltage                 |                                             | 1.1          |       | Vdd -<br>1.1 | V     |

| VFLT       | SHDNN Voltage, Floating                 | SHDNN = float                               |              | Vdd/2 |              | V     |

|            | SHDNN Max Allowed Leakage,<br>Mid Input | SHDNN = float                               |              |       | ±50          | nA    |

| Digital O  | utput: DOUT                             |                                             |              |       |              |       |

| Mai        | Output Voltage Low                      | ISINK = 5mA                                 |              |       | 0.4          | V     |

| Vol        |                                         | ISINK = 16mA                                |              |       | 0.8          | V     |

| Vон        | Output Voltage High                     | ISOURCE = 0.5mA                             | Vdd -<br>0.5 |       |              | V     |

| ΙL         | Tri-State Leakage Current               | CSN = VDD                                   |              | ±0.01 | ±10          | μA    |

| Соит       | Tri-State Output Capacitance            | $CSN = VDD^{7}$                             |              |       | 15           | pF    |

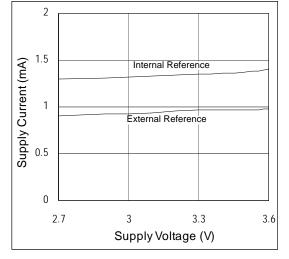

| Power R    | equirements                             |                                             |              |       |              |       |

| Vdd        | Supply Voltage                          |                                             | 2.7          |       | 3.6          | V     |

|            | Supply Current                          | Int. Reference (AS1526), VDD = 3.6V         |              | 1.4   | 2.0          | mA    |

| Idd        |                                         | External Reference, VDD = 3.6V              |              | 1.0   | 1.4          | 111/4 |

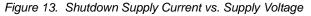

|            |                                         | Shutdown mode, VDD = 3.6V                   |              | 0.3   | 2            | μA    |

| PSR        | Power-Supply Rejection <sup>8</sup>     | VDD = VDDMIN to VDDMAX,<br>full-scale input |              | ±1    |              | mV    |

#### Table 3. Electrical Characteristics (Continued)

1. Tested at VDD = +2.7V.

2. Relative accuracy is the deviation of the analog value at any code from its theoretical value after the full-scale range and offset have been calibrated.

- 3. Offset nulled.

- 4. Achievable with standard timing (see Figure 25 on page 13).

- 5. Sample tested at 0.1% AQL.

- 6. External load should not change during conversion for specified accuracy.

- 7. Guaranteed by design; not subject to production testing.

- 8. Measured as [VFs(VDDMIN) VFs(VDDMAX)] with external reference.

## **Timing Characteristics**

VDD = +2.7 to +3.6V, TAMB = TMIN to TMAX (unless otherwise specified).

#### Table 4. Timing Characteristics

| Parameter                               | Symbol        | Conditions             | Min | Тур | Max | Units |

|-----------------------------------------|---------------|------------------------|-----|-----|-----|-------|

| Acquisition Time <sup>1</sup>           | tacq          |                        | 1.5 |     |     | μs    |

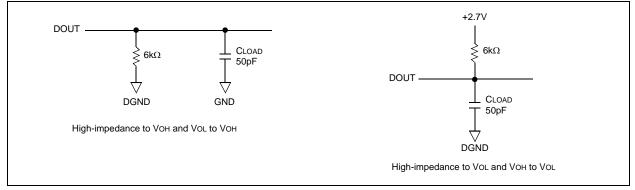

| SCLK Falling-to-DOUT Valid              | tDO           | Figure 3, CLOAD = 50pF | 20  |     | 200 | ns    |

| CSN Falling-to-Output Enable            | tDV           | Figure 3, CLOAD = 50pF |     |     | 240 | ns    |

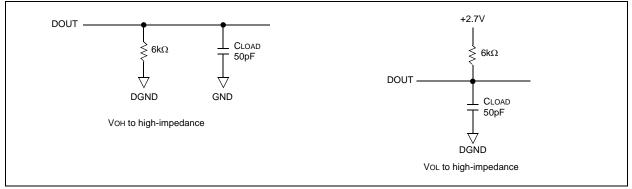

| CSN Rising-to-Output Disable            | ttr           | Figure 4, CLOAD = 50pF |     |     | 240 | ns    |

| SCLK Clock Frequency                    | <b>f</b> SCLK |                        | 0   |     | 2.1 | MHz   |

| SCLK Pulse Width High                   | tCH           |                        | 200 |     |     | ns    |

| SCLK Pulse Width Low                    | tCL           |                        | 200 |     |     | ns    |

| SCLK Low-to-CSN Falling Setup<br>Time   | tCS0          |                        | 50  |     |     | ns    |

| DOUT Rising-to-SCLK Rising <sup>2</sup> | tSTR          |                        | 0   |     |     | ns    |

| CSN Pulse Width                         | tcs           |                        | 240 |     |     | ns    |

1. To guarantee acquisition time, tACQ is the maximum time the device takes to acquire the signal, and is also the minimum time needed for the signal to be acquired

2. Guaranteed by design; not subject to production testing.

Figure 3. DOUT Enable-Time Load Circuits

#### Figure 4. DOUT Disable-Time Load Circuits

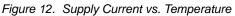

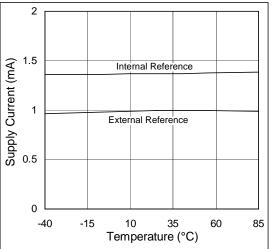

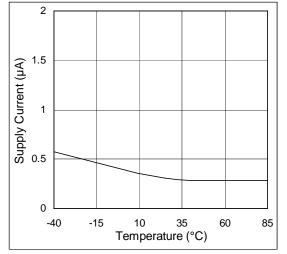

# 7 Typical Operating Characteristics

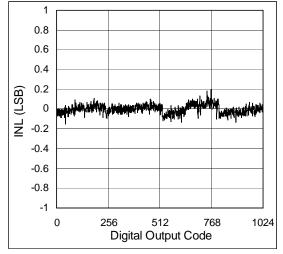

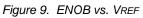

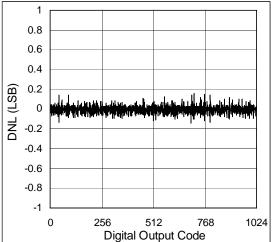

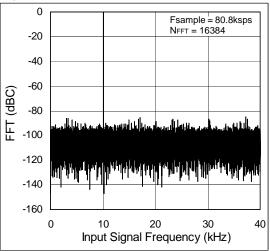

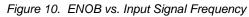

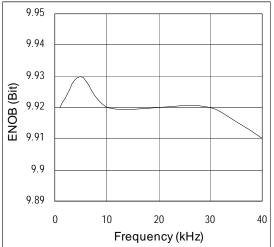

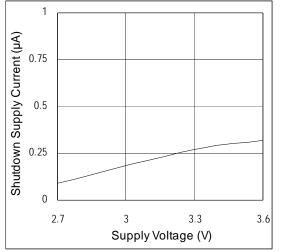

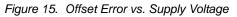

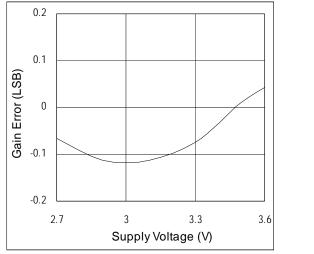

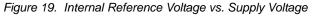

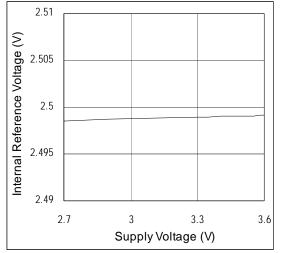

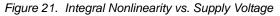

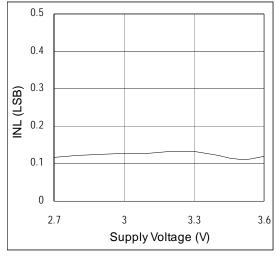

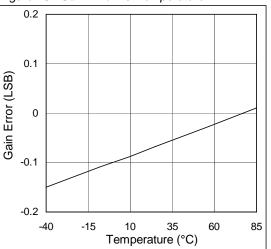

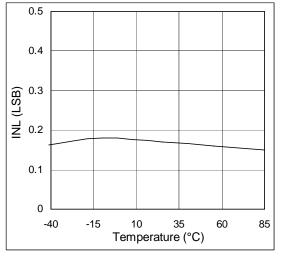

VDD = 3.0V, VREF = 2.5V, fSCLK = 2.1MHz, CLOAD = 50pF, TAMB = +25°C (unless otherwise specified). Figure 5. Integral Nonlinearity vs. Digital Output Code Figure 6. Differential Nonlinearity vs. Digital Output Code

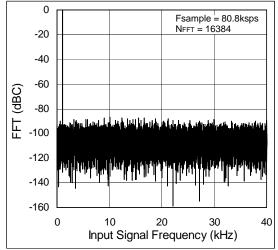

Figure 7. FFT @ 1kHz

Figure 8. FFT @ 10kHz

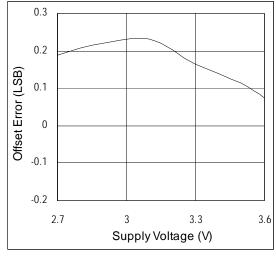

#### Figure 11. Supply Current vs. Supply Voltage

Figure 14. Shutdown Supply Current vs. Temperature

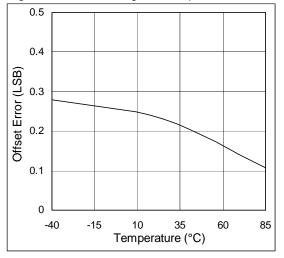

Figure 16. Offset Voltage vs. Temperature

#### Figure 17. Gain Error vs. Supply Voltage

Figure 20. Internal Reference Voltage vs. Temperature

Figure 22. Integral Nonlinearity vs. Temperature

# 8 Detailed Description

The AS1526/AS1527 analog-to-digital converters have two modes of operation:

- Normal A/D Conversion Mode Pulling pin SHDNN high or leaving it open puts the device into normal A/D conversion mode.

- Shutdown Mode Pulling pin SHDNN low shuts the device down and reduces supply current below 2µA (VDD ≤ 3.6V).

- **Note:** Pulling pin CSN low starts a conversion. The conversion result is available at pin DOUT in unipolar serial format (see Timing and Control on page 12).

Figure 23 shows a basic configuration for the AS1526/AS1527. The integrated input track/hold circuitry and a successive-approximation register (SAR) circuitry convert analog input signals to a digital 10-bit output. No external-hold capacitor is needed for the track/hold circuit.

The devices convert analog input signals in the 0V to VREF range in 13µs (includes track/hold acquisition time).

The AS1526 internal reference is trimmed to 2.5V; the AS1527 requires an external reference. Both devices can accept external reference voltages from 1.0V to VDD. The serial interface requires only three digital lines (at pins SCLK, CSN, and DOUT) and provides a simple microprocessor interface.

Figure 23. Operational Diagram

### **Analog Input**

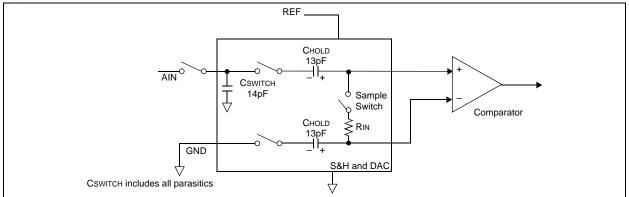

Figure 24 illustrates the integrated comparator sampling architecture. The full scale input voltage is set by the voltage at pin REF.

Figure 24. Equivalent Input Circuit

The devices' input tracking circuitry has a 2.5MHz small-signal bandwidth, thus it is possible to under-sample (digitize high-speed transient events) and measure periodic signals with bandwidths exceeding the devices' sampling rate.

Note: Anti-aliasing filtering should be used to avoid aliasing of unwanted high-frequency signals into the bandwidth of interest.

#### **Input Protection**

Internal protection diodes clamp the analog input to VDD and GND, allowing the input to swing from (GND - 0.3V) to (VDD + 0.3V) without damage. However, for accurate conversions near full scale, the input must not exceed VDD by more than 50mV, or be lower than GND by 50mV.

Note: If the analog input exceeds the supply by 50mV, limit the input current to 2mA.

#### Track/Hold

In track mode, the analog signal is acquired and stored in the internal hold capacitors. During acquisition, the analog input at pin AIN charges capacitor CHOLD (see Figure 24 on page 11). Bringing CSN low ends the acquisition interval and the charge on CHOLD represent the sampled input voltage.

In hold mode, the T/H switches are opened thus the input is disconnected from the capacitor CHOLD. During this mode the successive approximation is performed which in turn forms a digital representation of the analog input signal. At the end of the conversion, the input side of the in meantime discharged CHOLD switches back to AIN, and CHOLD charges to the input signal again.

The maximum time for the T/H to acquire a signal (tACQ) is a function of how quickly its input capacitance is charged. tACQ increases proportionally to the input signal's impedance, and at higher impedances more time must be allowed between conversions. tACQ is also the minimum time needed for the signal to be acquired, and is calculated by:

$$tACQ = 7(Rs + RiN) \times 21pF$$

(EQ 1)

#### Where:

$R_{IN} = 4.5 k\Omega$

Rs = the input signal's source impedance.

tAcQ is never less than 1.5 $\mu$ s. Source impedances < 1k $\Omega$  do not significantly affect the AC performance of the devices.

**Note:** Higher source impedances can be used if a 0.01µF capacitor is connected to the analog input. Note that the input capacitor forms an RC filter with the input source impedance, limiting the devices' input signal bandwidth.

### **External Clock**

The AS1526/AS1527 do not require an external clock for analog-to-digital data conversion. This allows the microprocessor to read back the conversion results at any clock rate from up to 2.1MHz at any time. The clock duty cycle is unrestricted if each clock phase is at least 200ns.

Note: The external clock must not be run while a conversion is in progress.

### **Timing and Control**

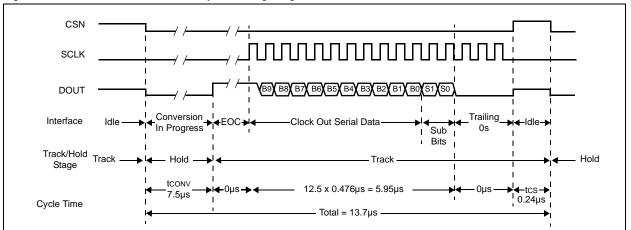

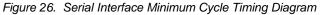

Conversion-start and data-read operations are controlled by digital inputs CSN and SCLK. Refer to Figures 25 - 27 (see page 13) for graphical timing and control information.

The falling edge on pin CSN initiates a conversion sequence:

- 1. The T/H stage holds the voltage at pin AIN, and the A/D conversion begins.

- 2. Pin DOUT changes from high-impedance to logic-low. SCLK must be kept low during the conversion.

- 3. The internal SAR stores the data during the conversion process.

- 4. Pin DOUT going high indicates the conversion process has completed.

- 5. The rising edge of pin DOUT can be used as a framing signal.

- 6. SCLK shifts the data out of this register any time after the conversion is complete.

- 7. DOUT transitions on the falling edge of pin SCLK.

- 8. The next falling clock edge produces the MSB of the conversion at DOUT, followed by the remaining bits. Since there are 10 data bits and one leading high-bit or 10 data bits, two sub bits, and one leading high-bit, at least 11 or 13 falling clock edges are needed to shift out these bits, respectively.

- 9. Extra clock pulses occurring after the conversion result has been clocked out, and prior to a rising edge of CSN, produce trailing zeros at DOUT and have no effect on the conversion process.

- 10. For minimum cycle time, clock out the data with 10.5 clock cycles at full speed using the rising edge of DOUT as the EOC signal. Pull CSN high after reading the conversion's LSB. After the specified minimum time (tcs) CSN can be pulled low to initiate the next conversion.

Figure 25. Serial Interface Standard Cycle Timing Diagram

## **Transfer Function**

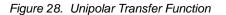

The data output from the AS1526/AS1527 is binary (unipolar), and Figure 28 depicts the nominal transfer function. Code transitions occur midway between successive integer LSB values.

Note: If VREF = +2.50V, then 1 LSB = 2.44mV (2.50V/1024).

### **Reducing Supply Current**

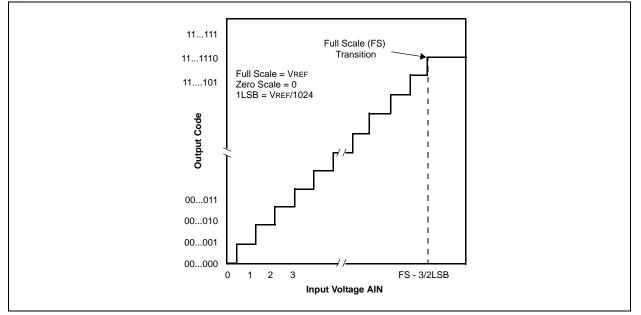

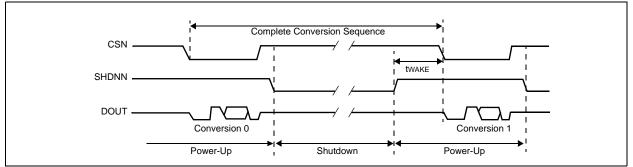

Power consumption can be reduced significantly by powering down the devices between conversions. Figure 30 shows a plot of an average supply current versus sampling rate.

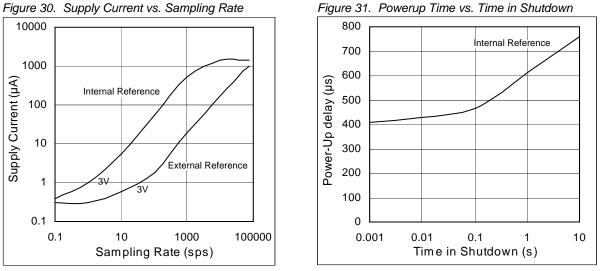

Wake-up time (tWAKE) can also factor into reduced power consumption. tWAKE is defined as the time from when pin SHDNN is deasserted to the time when a conversion may be initiated (see Figure 29).

Figure 29. Shutdown Sequence Timing Diagram

For the AS1526 using the internal reference, tWAKE depends on the time in shutdown mode (see Figure 31) since the external 4.7µF reference bypass capacitor slowly loses charge during shutdown. The wakeup time for AS1526 and AS1527 using an internal reference are largely dependent on the external reference's power-up time. The wakeup time for the ADC itself from shutdown mode is approximately 4µs.

Figure 30. Supply Current vs. Sampling Rate

### Internal 2.5V Reference (AS1526)

The AS1526 internal 2.5V reference output is connected to pin REF and also drives the internal DAC (see Figure 24 on page 11). REF output can be used as a reference voltage source for other components and can source up to 400µA.

The internal reference is enabled by pulling pin SHDNN high. Letting SHDNN float disables the internal reference, which allows the use of an external reference (see External Reference on page 15).

Pin REF should be bypassed with a 4.7µF capacitor as shown in Figure 23 on page 11. Larger capacitors increase wake-up time when the devices exit shutdown mode (see Layout Considerations on page 18)

### **External Reference**

Both devices can operate with an external reference at pin REF. The external reference should be within the +1.0V to VDD voltage range to achieve specified accuracy. The minimum input impedance is  $18k\Omega$  for DC currents.

Note: To use an external reference with the AS1526, disable the internal reference by letting pin SHDNN float.

During conversion, the external reference should be capable of delivering up to 250µA of DC load current and have an output impedance  $\leq 10\Omega$ . The recommended minimum value for the bypass capacitor is 0.1µF. If the reference has higher output impedance or is noisy, bypass it close to pin REF with a 4.7µF capacitor.

# **9** Application Information

### Initialization

When power is first applied, and if SHDNN is not pulled low, it takes the fully discharged 4.7µF reference bypass capacitor up to 20ms to provide adequate charge for specified accuracy.

With an external reference, the initialization time is 10µs after the power supplies have stabilized.

Note: A/D conversions must not be started during initialization of the AS1526/AS1527.

### **Serial Interface**

The AS1526/AS1527 fully support SPI, QSPI, and Microwire interfaces. For SPI, select the correct clock polarity and sampling edge in the SPI control registers (set CPOL = 0 and CPHA = 0).

Microwire, SPI, and QSPI all transmit a byte and receive a byte at the same time.

#### **Serial Interface Configuration**

The AS1526/AS1527 serial interface can be configured with the following procedure:

- 1. Put the microprocessor's serial interface into master mode (so that it generates the serial clock).

- 2. Select a clock frequency up to 2.1MHz.

- 3. Keeping SCLK low, pull CSN low via one of the microprocessor's general-purpose I/O lines.

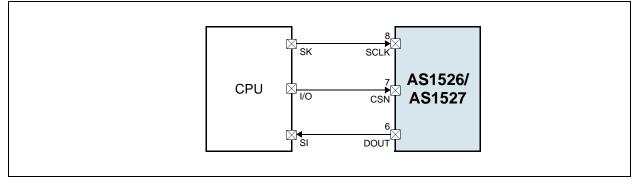

- 4. Monitor DOUT for its rising edge to determine the EOC, or wait the maximum conversion time specified before activating SCLK.

- 5. Activate SCLK for a minimum of 11 clock cycles. The first falling clock edge produces the MSB of the conversion. Output data transitions on the falling edge of SCLK, and is available in MSB-first format at pin DOUT. Observe the SCLK to DOUT valid timing characteristic. Data can be clocked into the microprocessor on the rising edge of SCLK.

- 6. CSN should be pulled high at or after the 13th falling clock edge. If CSN remains low, trailing zeros are clocked out after the LSB.

- 7. With CSN = high, wait the minimum specified time, tcs, before initiating a new conversion by pulling CSN low. If a conversion is aborted by pulling CSN high before the conversion's end, wait for the minimum acquisition time, tACQ, before starting a new conversion.

Note: CSN must be held low until all data bits are clocked out.

8. Data can be output in two bytes or continuously (see Figure 34 on page 17). The bytes contain the result of the conversion padded with one leading 1, two sub-bits, and trailing 0s.

#### **SPI and Microwire Interfaces**

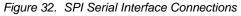

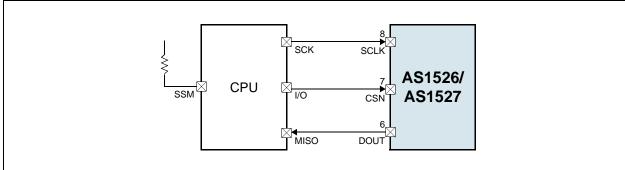

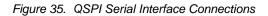

When interfacing the AS1526/AS1527 to a microprocessor's SPI or Microwire interface (see Figure 32 and Figure 33), set SPI control registers CPOL = 0 and CPHA = 0.

A conversion process begins on the falling edge of CSN (see Figure 34). DOUT goes low, indicating a conversion is in progress. Wait until DOUT goes high or until the maximum specified conversion time elapses before starting another conversion. Two consecutive 1-byte reads are required to retrieve the full 10+2 bits from the devices.

Output data transitions occurs on the falling edge of SCLK, and is clocked into the microprocessor on the rising edge of SCLK. The first byte contains a leading 1, and seven bits of conversion result data. The second byte contains the remaining three bits of conversion result data, two sub-bits, and three trailing zeros.

#### QSPI

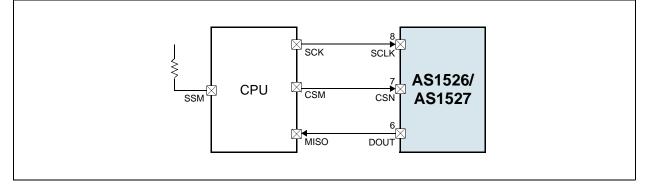

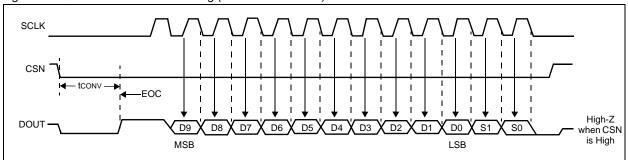

When interfacing the AS1526/AS1527 to a microprocessor's QSPI interface (see Figure 35), set QSPI control register CPOL = CPHA = 0.

Unlike the SPI interface, which requires two 1-byte reads to acquire the 10 data bits from the AS1526/AS1527, QSPI allows the minimum number of clock cycles necessary to clock in the data. The devices require 11 clock cycles from the microprocessor to clock out the 10 data bits with no trailing zeros or 13 clock cycles from the microprocessor to clock out the 10 data bits with no trailing zeros (see Figure 36).

Note: The maximum clock frequency to ensure compatibility with QSPI is 2.097MHz.

Figure 36. QSPI Serial Interface Timing (CPOL = CPHA = 0)

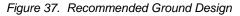

### Layout Considerations

The AS1526/AS1527 require proper layout and design procedures for optimum performance.

- Use printed circuit boards; wirewrap boards should not be used.

- Separate analog and digital traces from each other. Analog and digital traces should not run parallel to each other (especially clock traces).

- Digital traces should not run beneath the AS1526/AS1527.

- Use a single-point analog ground at GND, separate from the digital ground (see Figure 37). Connect all other analog grounds and DGND to this star ground point for further noise reduction. No other digital system ground should be connected to this single-point analog ground. The ground return to the power supply for this ground should be low impedance and as short as possible for noise-free operation.

- High-frequency noise in the VDD power supply may affect the AS1526/AS1527 high-speed comparator. Bypass this supply to the single-point analog ground with 0.1µF and 4.7µF bypass capacitors (see Figure 37). The bypass capacitors should be placed as close to the device as possible for optimum power supply noise-rejection. If the power supply is very noisy, a 10Ω resistor can be connected as a low-pass filter to attenuate supply noise.

*austriamicro*systems

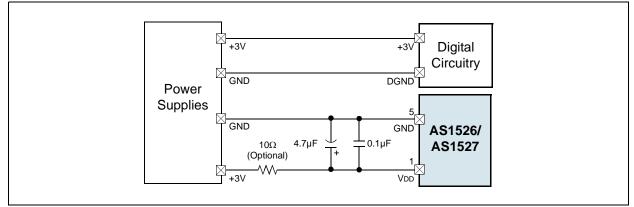

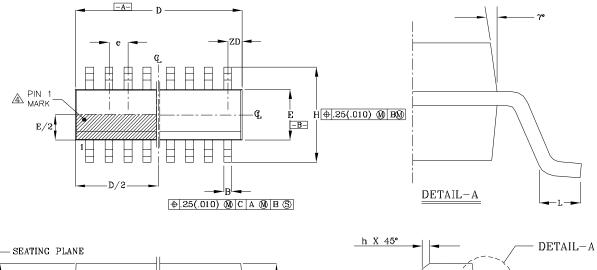

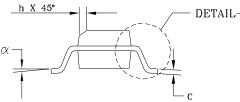

## **Package Drawings and Markings**

#### Figure 38. 8-pin SOIC-150 Package

#### Notes:

- 1. Lead coplanarity should be 0 to 0.10mm (.004") max.

- 2. Package surface finishing:

- (2.1) Top: matte (charmilles #18-30).

- (2.2) All sides: matte (charmilles #18-30).

- (2.3) Bottom: smooth or matte (charmilles #18-30).

- 3. All dimensions exclusive of mold flash, and end flash from the package body shall not exceed 0.24mm (0.10") per side (D).

- 4. Details of pin #1 identifier are optional but must be located within the zone indicated.

| Symbol | Min          | Max  |  |  |

|--------|--------------|------|--|--|

| A1     | 0.10         | 0.25 |  |  |

| В      | 0.36         | 0.46 |  |  |

| С      | 0.19         | 0.25 |  |  |

| D      | 4.80         | 4.98 |  |  |

| E      | 3.81         | 3.99 |  |  |

| е      | 1.27BSC      |      |  |  |

| Н      | 5.80         | 6.20 |  |  |

| h      | 0.25         | 0.50 |  |  |

| L      | .041         | 1.27 |  |  |

| A      | 1.52         | 1.72 |  |  |

|        | 0°           |      |  |  |

| ZD     | 0.53REF      |      |  |  |

| A2     | A2 1.37 1.57 |      |  |  |

# **10 Ordering Information**

The devices are available as the standard products shown in Table 5.

#### Table 5. Ordering Information

| Туре        | Description                                                                     | Delivery Form                                  | Package        |

|-------------|---------------------------------------------------------------------------------|------------------------------------------------|----------------|

| AS1526-BSOU | Single-Supply, Low-Power, 73ksps A/D Converter<br>with Internal +2.5V Reference | y, Low-Power, 73ksps A/D Converter Tubes Tubes |                |

| AS1526-BSOT | Single-Supply, Low-Power, 73ksps A/D Converter<br>with Internal +2.5V Reference | Tape and Reel                                  | 8-pin SOIC-150 |

| AS1527-BSOU | Single-Supply, Low-Power, 73ksps A/D Converter                                  | Tubes                                          | 8-pin SOIC-150 |

| AS1527-BSOT | Single-Supply, Low-Power, 73ksps A/D Converter                                  | Tape and Reel                                  | 8-pin SOIC-150 |

## Copyrights

Copyright © 1997-2007, austriamicrosystems AG, Schloss Premstaetten, 8141 Unterpremstaetten, Austria-Europe. Trademarks Registered ®. All rights reserved. The material herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner.

All products and companies mentioned are trademarks or registered trademarks of their respective companies.

## Disclaimer

Devices sold by austriamicrosystems AG are covered by the warranty and patent indemnification provisions appearing in its Term of Sale. austriamicrosystems AG makes no warranty, express, statutory, implied, or by description regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. austriamicrosystems AG reserves the right to change specifications and prices at any time and without notice. Therefore, prior to designing this product into a system, it is necessary to check with austriamicrosystems AG for current information. This product is intended for use in normal commercial applications. Applications requiring extended temperature range, unusual environmental requirements, or high reliability applications, such as military, medical life-support or life-sustaining equipment are specifically not recommended without additional processing by austriamicrosystems AG for each application. For shipments of less than 100 parts the manufacturing flow might show deviations from the standard production flow, such as test flow or test location.

The information furnished here by austriamicrosystems AG is believed to be correct and accurate. However, austriamicrosystems AG shall not be liable to recipient or any third party for any damages, including but not limited to personal injury, property damage, loss of profits, loss of use, interruption of business or indirect, special, incidental or consequential damages, of any kind, in connection with or arising out of the furnishing, performance or use of the technical data herein. No obligation or liability to recipient or any third party shall arise or flow out of austriamicrosystems AG rendering of technical or other services.

### **Contact Information**

Headquarters austriamicrosystems AG A-8141 Schloss Premstaetten, Austria

Tel: +43 (0) 3136 500 0 Fax: +43 (0) 3136 525 01

For Sales Offices, Distributors and Representatives, please visit:

http://www.austriamicrosystems.com/contact