# IBM 1394 400Mb/s Physical Layer Transceiver (PHY)

#### **Features**

- Designed to provisions of the IEEE 1394 Serial Bus Standard [1]

- 400Mb/s max data rate; interoperable with 100 & 200Mb/s devices

- Available with one or three ports

- Supports major P1394a enhancements

- Multi-speed Concatenation

- Arbitrated Short Reset

- ACK Accelerated Arbitration

- Three TpBias Regulators

- Connection Debounce

- · "Missing SID bits" register

- "No reset on unplug" option

- Fully Compliant with OpenHCI requirements

- Programmable Port Disable

- No phy ID wrap past 63

- Selectable Link-PHY interface timings

- Single 3.3V power supply

- · Advanced Power Management:

- Programmable Power Save Mode on unconnected ports

- Sleep Mode to minimize quiescent power

- Utilizes sophisticated clock gating to reduce power consumption

- Tolerant of extra IDLE indications which circumvents Link-PHY "Bus Collision" conditions

- On-device PLL generates the 50MHz SCLK using an external 25MHz crystal oscillator

- Supports optional 1394-1995 Isolation Barrier Feature at Link-PHY Interface

- Supports optional IBM Dynamic Termination Isolation Barrier Feature at Link-PHY Interface

- Interoperable with 5V Link Layer Controllers and 5V Transceivers

- Cable ports exceed 5kV of ESD protection (Human Body Model)

### **Overview**

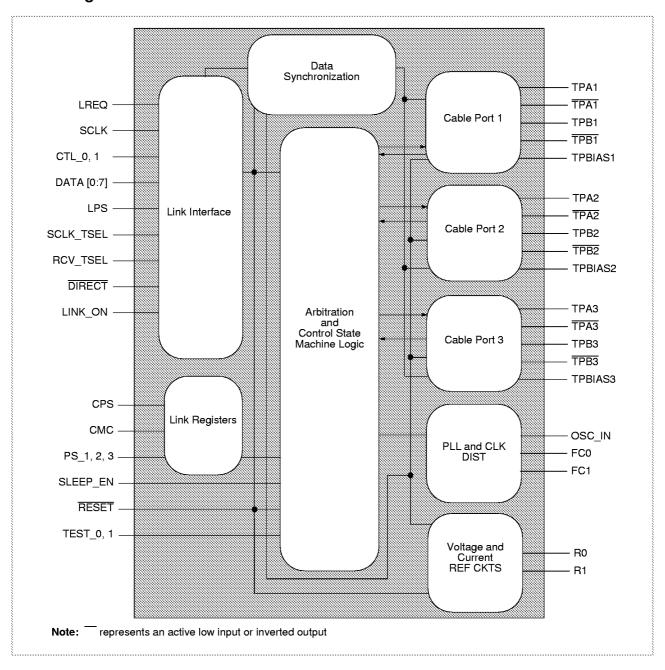

The IBM21S850 and IBM21S851 devices (PHYs) provide transceivers to implement a three or one port node in a 1394 cable based network. The PHY is designed to the provisions of the IEEE 1394-1995 specification [1] and includes many of the P1394a [2] and all OpenHCI enhancements. These enhancements include Arbitrated Short Reset (for uninterrupted Isochronous data transport), multispeed concatenation, ACK Accelerated Arbitration (to improve bandwidth utilization), Connection Debounce Hysteresis (to avoid "Reset Storms"), three independent TpBias regulators (providing the ability to disable individual ports), and numerous other features.

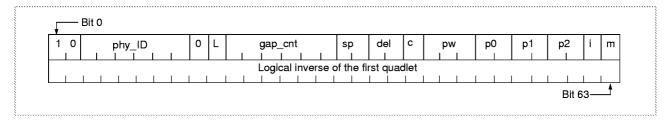

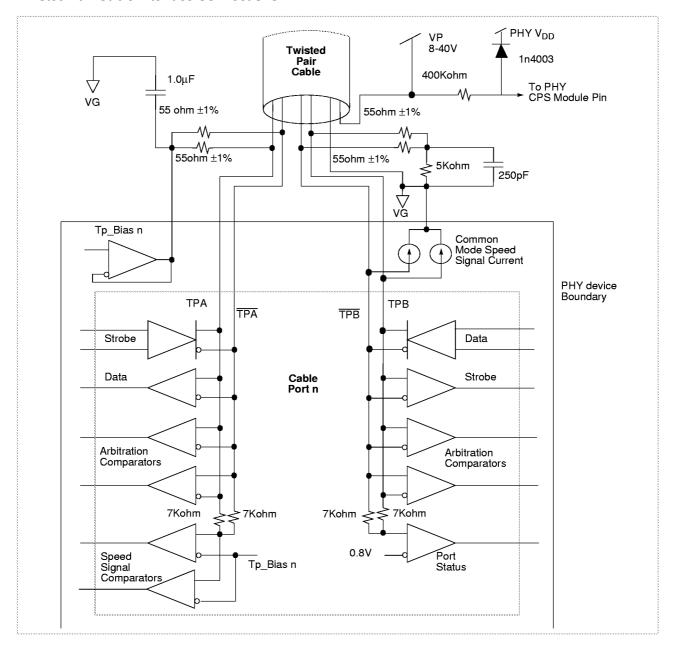

Each cable port is composed of two differential line transceivers (TPA and TPB) that transmit and receive serial data at 100, 200, or 400Mb/s (actually 98.304, 196.608, and 393.216Mb/s, respectively), depending on which data speed is routed through the bus. Each transceiver contains a differential current mode driver whose outputs provide signal swings around a common mode voltage called TpBias, which is generated on the PHY device. Two off-device 55 ohm resistors are connected in series across the differential outputs of each transceiver. TpBias voltage is connected to the midpoint connection of the resistors at TPA, while a 5K ohm resistor and a 250pF capacitor to ground are attached to the midpoint connection of the resistors at TPB. The TpBias voltage for the TPB line is supplied by the

TPA of the PHY at the other end of the cable.

In addition to providing bus transceivers, the PHY serializes and deserializes data using Data and Strobe encoding. Data is sent from the Link Layer Controller on an eight bit wide parallel bus to the PHY. The two devices are synchronized by a 49.152MHz reference clock provided by the PHY. The data is then serialized and transmitted to the cable as Strobe on TPA and Data on TPB. Received data is resynchronized to the reference clock and decoded for parallel transmission to the Link Layer Controller.

PHY devices communicate their speed capabilities to one another through a process called Speed Signaling, in which common mode currents are withdrawn from the cable at TPB and TPB. Three such common mode currents exist for this PHY: one for each of the supported transfer speeds. The nominal common mode currents are defined for 100Mb/s, 200Mb/s, and 400Mb/s as 0mA, -3.5mA, and -10mA respectively. The PHY is capable of 100, 200 or 400Mbits/sec operation, and will send or receive data at any of these speeds according to the capabilities of the adjacent PHYs.

Other functions of the PHY include system initialization and bus arbitration. The PHY also determines whether its ports are connected to other ports by detecting the presence or absence of TpBias volt-

age from the other transceiver. Moreover, it functions as a repeater to pass data along the bus.

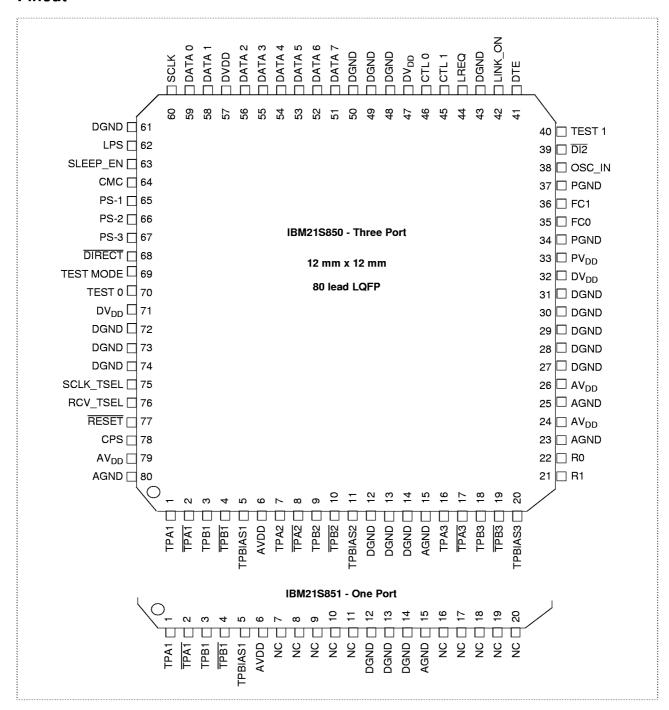

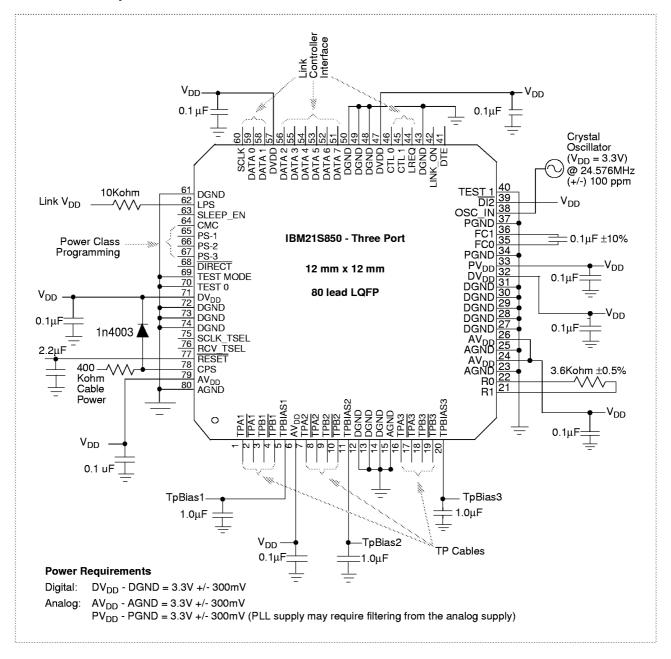

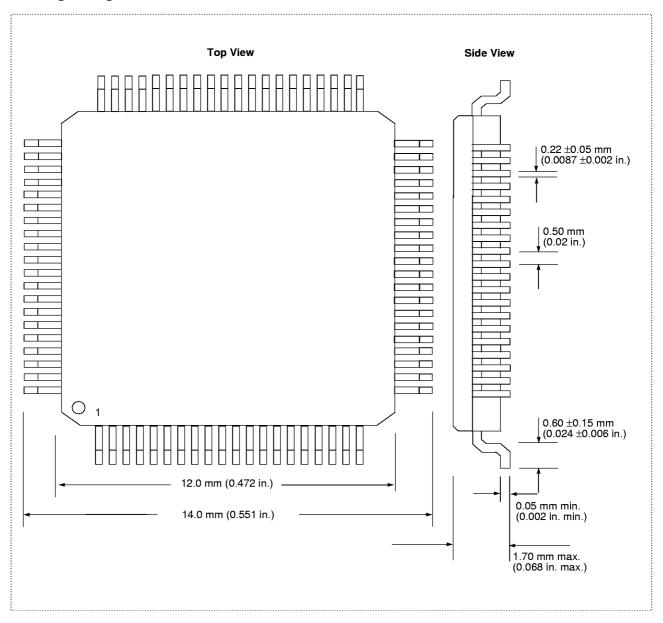

### **Pinout**

# **Ordering Information**

| Product Number | Product Number Number of Ports |         | Power Supply |  |

|----------------|--------------------------------|---------|--------------|--|

| IBM21S850      | 3                              | 400Mb/s | 3.3V         |  |

# **Ordering Information**

| Product Number | Number of Ports | Maximum Data Rate | Power Supply |

|----------------|-----------------|-------------------|--------------|

| IBM21S851      | 1               | 400Mb/s           | 3.3V         |

# **Block Diagram: Three-Port PHY**

IBM 1394 400Mb/s Physical Layer Transceiver (PHY)

## **Circuit Description**

### **Phase Locked Loop**

The system reference clocks are generated by a frequency synthesizing Phase Locked Loop. Using an external 24.576MHz crystal oscillator as a reference, the PLL generates a 49.152MHz system clock (SCLK) which is shipped to the Link Layer Controller to synchronize data transfer. The PLL also generates 98.304MHz, 196.608MHz and 393.216MHz clocks for data encode/decode. Several of the PLL loop filter components have been integrated onto the device, therefore only a single external capacitor is needed for the loop filter.

### **Bandgap Reference Generator**

The band gap reference generator provides a precision voltage supply from which several voltage and current sources required by the PHY are derived. One of the most important of these is the 4mA current source which is used in the current mode serial bus driver to maintain constant current.

#### **TpBias Circuits**

TpBias is a constant voltage source that maintains the common mode voltage of the TPA cable twisted pair at 1.84V nominal for each port. This PHY contains three independent TpBias circuits (one per port). Each TpBias circuit can be disabled via software (Link Accessible Register 0xE), thereby implementing the port disable feature required by OpenHCI. In order to meet the speed signaling requirements, each port must be used in conjunction with a 0.3μF minimum ceramic capacitor. However, a 1.0μF ceramic capacitor is recommended at each port for added margin. The capacitor physical size is recommended to be the 1206 or 1210 form factor to reduce the parasitic inductance associated with the capacitor.

The external capacitor on TpBias provides phase compensation. It is required that the capacitor be added even at unused ports of the three port PHY.

### **Analog Transceivers**

There are two 4mA differential current mode serial bus drivers per port. They are designed to operate with external 110 ohm line matching resistor networks located at each end of the twisted pair cable. Each driver can be placed in a Hi-Z state in which the drive current is shut off. The receivers are connected to the drivers in a Bi-Di configuration, and capture differential data and strobe signals at each port.

The arbitration comparators are connected across the driver outputs, similar to the receivers. They detect logical DC levels used during bus arbitration. Two comparators are required per driver output, one to detect a logical "1" and one for a logical "0". A logical "Z" state is also used in arbitration. It is considered to be the midpoint logical state in which both comparators are inactive.

The speed signaling comparator senses the common mode voltage at driver TPA and compares it with the TpBias reference, in order to detect whether any common mode controlled current signaling has been sent from the other end of the cable. The current pulses are used to signal the speed capability of the port at the other end.

The port status comparator senses the common mode voltage at driver TPB and compares it with a reference voltage, in order to detect whether TpBias voltage is being supplied by the port at the other end. It is used to determine whether or not the port is connected.

# **Absolute Maximum Ratings**

| Symbol           | Parameter                       | Rating      | Units | Notes |

|------------------|---------------------------------|-------------|-------|-------|

| $V_{DD}$         | Supply voltage range            | -0.3 to 5.1 | V     | 1     |

| $V_{IN}$         | Logic input voltage range       | -0.5 to 5.5 | V     | 1     |

| V <sub>OUT</sub> | Logic output voltage range      | -0.5 to 5.5 | ٧     | 1     |

| V <sub>T</sub>   | Test I/O voltage range          | -0.5 to 3.6 | V     | 1     |

| V <sub>C</sub>   | Cable transceiver voltage range | -0.5 to 3.6 | V     | 1     |

| T <sub>OPR</sub> | Operating Temperature           | 0 to 70     | °C    | 1, 2  |

| T <sub>STG</sub> | Storage Temperature             | -65 to +150 | °C    | 1     |

<sup>1.</sup> The device is not guaranteed to function at these limits, and exceeding the limits may damage the device.

<sup>2.</sup> See the Supply Current and Dissipation Rating tables on page 7.

# **Operating Conditions and Electrical Characteristics**

The current polarity convention used in these tables is that current *into* a transceiver input is considered positive, while a current *out of* a transceiver output is considered positive.

| Symbol             | Parameter                                                         | Pin                          | Min                      | Тур    | Max                      | Units | Notes                                    |

|--------------------|-------------------------------------------------------------------|------------------------------|--------------------------|--------|--------------------------|-------|------------------------------------------|

| $V_{DD}$           | Supply Voltage                                                    |                              | 3.0                      | 3.3    | 3.6                      | ٧     |                                          |

| V <sub>OH</sub>    | High Level Output Voltage                                         | CMOS outputs                 | V <sub>DD</sub> - 0.5    |        |                          | ٧     |                                          |

| $V_{OL}$           | Low Level Output Voltage                                          | CMOS outputs                 |                          |        | 0.5                      | ٧     | 6<br>6<br>6<br>6<br>7                    |

| V <sub>IH</sub>    | High Level Input Voltage                                          | CMOS inputs                  | 0.8 V <sub>DD</sub>      |        |                          | ٧     | (2000,000,000,000,000,000,000,000,000,00 |

| V <sub>IL</sub>    | Low Level Input Voltage                                           | CMOS inputs                  |                          |        | 0.2 V <sub>DD</sub>      | ٧     |                                          |

| V <sub>ID</sub>    | Differential Input Voltage                                        | Cable inputs                 | >90                      |        | 265                      | mV    | ***************************************  |

|                    | 0                                                                 | TPB, TPB                     | 1.165                    |        | 2.515                    | ٧     |                                          |

| V <sub>IC</sub>    | Common Mode input Voltage                                         | TPA, TPA                     | 1.665                    |        | 2.015                    | ٧     | \$2000000000000000000000000000000000000  |

| V <sub>IT</sub> +  | Positive input threshold Voltage, V <sub>IT</sub> +               | Hysteresis                   | V <sub>DD</sub> /2 + 0.1 |        | V <sub>DD</sub> /2 + 0.8 | ٧     |                                          |

| v T+               | Positive input tilleshold voltage, VIT +                          | RESET                        | V <sub>DD</sub> /2 + 0.2 |        | V <sub>DD</sub> /2 + 0.8 | ٧     |                                          |

| V <sub>IT</sub>    | Negative input threshold Voltage, V <sub>IT</sub> -               | Hysteresis                   | V <sub>DD</sub> /2 - 0.9 |        | V <sub>DD</sub> /2 - 0.3 | ٧     |                                          |

| ¥                  | rvegative input tilleshold voltage, v   -                         | RESET                        | V <sub>DD</sub> /2 - 0.9 |        | V <sub>DD</sub> /2 - 0.3 | ٧     |                                          |

| I <sub>IL</sub>    | Dynamic Termination Latch input Current @ V <sub>IL</sub> = 0.66V | LREQ, CTL, DATA              | 0.1                      |        | 1.2                      | mA    |                                          |

| I <sub>IH</sub>    | Dynamic Termination Latch input Current $@V_{IH} = 2.64V$         | LREQ, CTL, DATA              | -1.2                     |        | -0.1                     | mA    |                                          |

| V <sub>OD</sub>    | Differential output voltage                                       | Cable output                 | 172                      | 220    | 265                      | mV    | ************                             |

| Vo                 | Common mode output voltage                                        | TPBIAS                       | 1.665                    | 1.82   | 2.015                    | ٧     |                                          |

| I <sub>SP100</sub> | S100 common mode output current (signaling off)                   | трв, Трв                     | -0.81                    |        | 0.44                     | mA    |                                          |

| I <sub>SP200</sub> | S200 common mode output current (signaling on)                    | трв, <u>трв</u>              | -4.84                    | -3.5   | -2.53                    | mA    |                                          |

| I <sub>SP400</sub> | S400 common mode output current (signaling on)                    | трв, Трв                     | -12.40                   | -10.00 | -8.10                    | mA    |                                          |

| l <sub>OL</sub>    | Output current @ 0.4V                                             | SCLK                         | -12                      |        |                          | mA    | i                                        |

| l <sub>OH</sub>    | Output current @ 2.4V                                             | SCLK                         |                          |        | 16                       | mA    |                                          |

| l <sub>OL</sub>    | Output current @ 0.4V                                             | CTL, DATA                    | -12                      |        |                          | mA    | \$                                       |

| I <sub>OH</sub>    | Output current @ 2.4V                                             | CTL, DATA                    |                          |        | 16.0                     | mA    |                                          |

| lo                 | Output current IO                                                 | TPBIAS1, TPBIAS2,<br>TPBIAS3 | -2.0                     |        | 10.0                     | mA    |                                          |

| T <sub>OPR</sub>   | Free Air Temperature                                              |                              | 0                        |        | 70                       | °C    | 1                                        |

| P <sub>D</sub>     | Power dissipation                                                 |                              |                          | 1.0    | 1.30                     | W     | 1                                        |

<sup>1.</sup> See the Supply Current and Dissipation Rating tables on page 7.

# **Supply Current**

| Test Condition                        | Product     | Supply<br>Voltage (V) | Тур | Max | Units |

|---------------------------------------|-------------|-----------------------|-----|-----|-------|

| Poy on 1 port. Ty on 2 ports, 400Mb/s | IBM21S850   | 3.3                   | 262 |     | mA    |

| Rcv on 1 port, Tx on 2 ports, 400Mb/s | 10101212820 | 3.6                   |     | 360 |       |

| Transmitting or reaching              | IDM404.00E4 | 3.3                   | 150 |     |       |

| Transmitting or receiving             | IBM21S851   | 3.6                   |     | 190 |       |

| PHY Asleep                            |             | 3.3                   | 30  |     | mA    |

# **Dissipation Rating**

| Package                                             | T <sub>A</sub> ≤25°C | Derating Factor<br>Above 25°C | T <sub>A</sub> =70°C | Notes |  |  |

|-----------------------------------------------------|----------------------|-------------------------------|----------------------|-------|--|--|

| LQFP-80                                             | 2071mW               | 23.8 mW/°C                    | 1000 mW              | 1     |  |  |

| 1. Junction to free air thermal resistance = 42°C/W |                      |                               |                      |       |  |  |

# **Thermal Characteristics**

| Symbol         | Parameter                               | Test Condition                    |        |

|----------------|-----------------------------------------|-----------------------------------|--------|

| $R_{\ThetaJA}$ | Junction to free air thermal resistance | Board mounted, natural convection | 42°C/W |

# **Data Signal Characteristics**

| Symbol         | Parameter                |                   | Min                     | Тур | Max   | Units |

|----------------|--------------------------|-------------------|-------------------------|-----|-------|-------|

| T <sub>R</sub> | Output rise time         |                   | 0.5                     | 0.8 | 1.2   | ns    |

| T <sub>F</sub> | Output fall time         |                   | 0.5                     | 0.8 | 1.2   | ns    |

|                | Input slope              |                   | 175                     |     |       | mV/ns |

|                | Transmitter skew         |                   |                         |     | 0.10  | ns    |

|                | Transmitter jitter       |                   |                         |     | 0.15  | ns    |

|                |                          | Receiving 100Mb/s |                         |     | 0.80  | ns    |

|                | Skew at receive pins     | Receiving 200Mb/s |                         |     | 0.55  | ns    |

|                |                          | Receiving 400Mb/s | *********************** |     | 0.50  | ns    |

|                |                          | Receiving 100Mb/s |                         |     | 8.50  | ns    |

|                | Jitter at receiving pins | Receiving 200Mb/s |                         |     | 3.50  | ns    |

|                |                          | Receiving 400Mb/s | **********************  |     | 0.315 | ns    |

# I/O Pin Function (Part 1 of 3)

| Pin Name         | Function                                                                                                                                                                                                                                                                                       | Pin Number                                                              | Pin Type     | I/O Type | Notes |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--------------|----------|-------|

| TPA1             | Port 1, Twisted pair A, positive signal                                                                                                                                                                                                                                                        | 1                                                                       | Differential | I/O      |       |

| TPA1             | Port 1, Twisted pair A, negative signal                                                                                                                                                                                                                                                        | 2                                                                       | Differential | I/O      |       |

| TPB1             | Port 1, Twisted pair B, positive signal                                                                                                                                                                                                                                                        | 3                                                                       | Differential | I/O      |       |

| TPB1             | Port 1, Twisted pair B, negative signal                                                                                                                                                                                                                                                        | 4                                                                       | Differential | I/O      |       |

| TPBIAS1          | Bias voltage supply. Provides 1.84V nominal bias voltage for Port 1 twisted pair signal cables. Indicates a valid cable connection to remote nodes. This supply can be individually disabled via software when not needed.                                                                     | 5                                                                       | Supply       | Output   |       |

| AV <sub>DD</sub> | Analog circuit power (3.3V nom). These pins are separated from other power pins internal to the device to provide noise isolation. Decoupling capacitor networks are recommended at each pin. All the power supply pins should be tied together at a low impedance point on the circuit board. | 6, 24, 26, 79                                                           | Supply       | -        |       |

| TPA2             | Port 2, Twisted pair A, positive signal                                                                                                                                                                                                                                                        | 7                                                                       | Differential | I/O      | 1     |

| TPA2             | Port 2, Twisted pair A, negative signal                                                                                                                                                                                                                                                        | 8                                                                       | Differential | I/O      | 1     |

| TPB2             | Port 2, Twisted pair B, positive signal                                                                                                                                                                                                                                                        | 9                                                                       | Differential | I/O      | 1     |

| TPB2             | Port 2, Twisted pair B, negative signal                                                                                                                                                                                                                                                        | 10                                                                      | Differential | I/O      | 1     |

| TPBIAS2          | Bias voltage supply. Provides 1.84V nominal bias voltage for Port 2 twisted pair signal cables. Indicates a valid cable connection to remote nodes. This supply can be individually disabled via software when not needed.                                                                     | 11                                                                      | Supply       | Output   | 1     |

| DGND             | Digital circuit ground. These pins are separated from other ground pins internal to the device to provide noise isolation. All ground pins should be tied together at a low impedance point on the circuit board.                                                                              | 12, 13, 14, 27,<br>28, 29, 30, 31,<br>43, 48, 49, 50,<br>61, 72, 73, 74 | Supply       | -        |       |

| AGND             | Analog circuit ground. These pins are separated from other ground pins internal to the device to provide noise isolation. All ground pins should be tied together at a low impedance point on the circuit board.                                                                               | 15, 23, 25, 80                                                          | Supply       | -        |       |

| TPA3             | Port 3, Twisted pair A, positive signal                                                                                                                                                                                                                                                        | 16                                                                      | Differential | I/O      | 1     |

| TPA3             | Port 3, Twisted pair A, negative signal                                                                                                                                                                                                                                                        | 17                                                                      | Differential | I/O      | 1     |

| TPB3             | Port 3, Twisted pair B, positive signal                                                                                                                                                                                                                                                        | 18                                                                      | Differential | I/O      | 1     |

| TPB3             | Port 3, Twisted pair B, negative signal                                                                                                                                                                                                                                                        | 19                                                                      | Differential | I/O      | 1     |

| TPBIAS3          | Bias voltage supply. Provides 1.84V nominal bias voltage for Port 3 twisted pair signal cables. Indicates a valid cable connection to remote nodes. This supply can be individually disabled via software when not needed.                                                                     | 20                                                                      | Supply       | Output   | 1     |

| R1, R0           | 3.6 Kohm (±0.5%) external current setting resistor terminals                                                                                                                                                                                                                                   | 21, 22                                                                  | Analog       | Output   | -     |

| DV <sub>DD</sub> | Digital circuit power (3.3V nom). These pins are separated from other power pins internal to the device to provide noise isolation. Decoupling capacitor networks are recommended at each pin. All the power supply pins should be tied together                                               | 32, 47, 57, 71                                                          | Supply       | -        |       |

<sup>1.</sup> These ports exist on the three-port PHY only. These pins are NC on the one port PHY.

<sup>2.</sup> See Operating Conditions and Electrical Characteristics on page 6 for electrical characteristics.

# I/O Pin Function (Part 2 of 3)

| Pin Name         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Pin Number                        | Pin Type   | I/O Type | Notes |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------|----------|-------|

| PV <sub>DD</sub> | PLL analog circuit power (3.3V nom). These pins are separated from other power pins internal to the device to provide noise isolation. Decoupling capacitor networks are recommended at each pin. All the power supply pins should be tied together at a low impedance point on the circuit board.                                                                                                                                                              | 33                                | Supply     | -        |       |

| PGND             | PLL analog circuit ground. These pins are separated from other ground pins internal to the device to provide noise isolation. All ground pins should be tied together at a low impedance point on the circuit board.                                                                                                                                                                                                                                            | 34, 37                            | Supply     | -        |       |

| FC0, FC1         | 0.1μF Cap (±10%) external PLL filter capacitor terminals                                                                                                                                                                                                                                                                                                                                                                                                        | 35, 36                            | Analog     | Output   |       |

| OSC_IN           | Crystal Oscillator @ 24.576MHz (±100 ppm), 3.3V. External oscillator provides stable reference frequency without sensitivity to board parasitics, and without the need for tank circuit components.                                                                                                                                                                                                                                                             | 38                                | CMOS       | Input    |       |

| DI2              | Driver Inhibit 2 test pin only. 1 = normal operation.                                                                                                                                                                                                                                                                                                                                                                                                           | 39                                | CMOS       | Input    |       |

| TEST_1, 0        | Reserved for test only. 0 = normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                   | 40, 70                            | CMOS       | Input    |       |

| DTE              | Dynamic termination enable pin. Used for Link-PHY interface isolation in instances where the Link uses bus holder circuitry. 1 = enable.                                                                                                                                                                                                                                                                                                                        | 41                                | CMOS       | Input    |       |

| LINK_ON          | A 6MHz signal is transmitted from this pin when a Link Power On packet is addressed to the device's PHY ID and the LPS pin = 0.                                                                                                                                                                                                                                                                                                                                 | 42                                | CMOS       | Output   |       |

| LREQ             | Link request from controller for the PHY to perform some service.                                                                                                                                                                                                                                                                                                                                                                                               | 44                                | Hysteresis | I/O      | 2     |

| CTL_1, 0         | Link interface bidirectional control pins.                                                                                                                                                                                                                                                                                                                                                                                                                      | 45, 46                            | Hysteresis | I/O      | 2     |

| DATA [0:7]       | Link interface bidirectional data pins.                                                                                                                                                                                                                                                                                                                                                                                                                         | 59, 58, 56, 55,<br>54, 53, 52, 51 | Hysteresis | I/O      | 2     |

| SCLK             | 49.152MHz system clock to Link controller.                                                                                                                                                                                                                                                                                                                                                                                                                      | 60                                | CMOS       | Output   |       |

| SLEEP_EN         | Sleep enable pin. '1' tells the PHY to power down if none of its ports are in use.                                                                                                                                                                                                                                                                                                                                                                              | 63                                | CMOS       | Input    |       |

| CMC              | Bus Configuration Manager Contender. "1" causes the PHY to indicate in the self-ID packet that the node is capable of being the Bus Manager.                                                                                                                                                                                                                                                                                                                    | 64                                | CMOS       | Input    |       |

| LPS              | Link power status. This pin monitors the Link power status by receiving either the Link $V_{CC}$ or nominally a 1MHz signal indicating that the Link is powered. If this input is low for more than 1.3 $\mu$ S, then the Link is considered powered down. If the input is high for more than 20nS, then the Link is considered powered up. If the Link is not powered, then the Link-PHY interface is disabled, and the PHY performs basic repeater functions. | 62                                | Hysteresis | Input    | 2     |

| PS_1, 2, 3       | Power Status pins. These inputs are used to set the three POWER_CLASS bits in the self-ID packet. They are used to describe the power consumption and source characteristics of the node, and are programmed by tying the pins high or low. PS_1, 2, & 3 are reflected in the self_id bits 21, 22, & 23, respectively.                                                                                                                                          | 65, 66, 67                        | CMOS       | Input    |       |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                   | ÷          | :        | A     |

<sup>1.</sup> These ports exist on the three-port PHY only. These pins are NC on the one port PHY.

<sup>2.</sup> See Operating Conditions and Electrical Characteristics on page 6 for electrical characteristics.

### I/O Pin Function (Part 3 of 3)

| Pin Name  | Function                                                                                                                                                                                                                                                                                                                       | Pin Number | Pin Type   | I/O Type | Notes |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|----------|-------|

| DIRECT    | Indicates presence of an Isolation Barrier using differentiated signals between the Link & PHY. 0 (GND) = direct coupling 1 (V <sub>DD</sub> ) = isolation with differentiated signals                                                                                                                                         | 68         | CMOS       | Input    |       |

| TEST_MODE | Reserved for test. For normal operation, connect to '0' (GND).                                                                                                                                                                                                                                                                 | 69         | CMOS       | Input    |       |

| SCLK_TSEL | SEL Select SCLK setting. 0 = default SCLK timings. 1 = alternate timings. See Link-PHY Interface Timing on page 16.                                                                                                                                                                                                            |            | CMOS       | Input    |       |

| RCV_TSEL  | Select receive timing. This pin enables the selection of alternate timings between data received from the Link and the system clock. 0 = default timings. 1 = alternate timings. See Link-PHY Interface Timing on page 16.                                                                                                     | 76         | CMOS       | Input    |       |

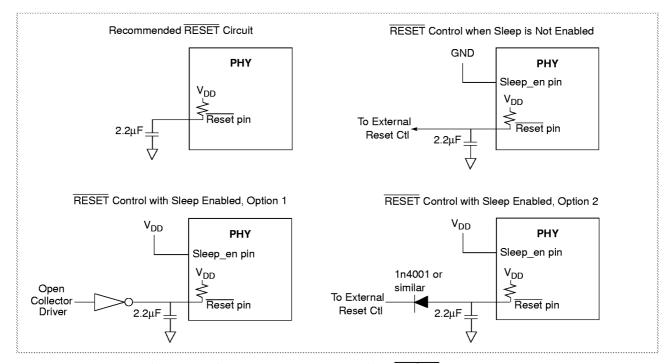

| RESET     | Reset (active low). The reset pin is connected to an internal 10K ohm resistor and an external 2.2μF capacitor to allow time for voltage buildup at power-on. 1 = normal operation of the PHY.                                                                                                                                 | 77         | Custom     | Input    | 2     |

| CPS       | Cable power status. This pin is connected to the cable power through a 400 K ohm resistor. When cable power is detected, the information is kept in an internal register which the Link can access through a register read. A diode is required between the module pin and the PHY V <sub>DD</sub> to clamp the input voltage. | 78         | Hysteresis | Input    | 2     |

<sup>1.</sup> These ports exist on the three-port PHY only. These pins are NC on the one port PHY.

# **Device Power Supply**

The PHY device uses a single 3.3V system power supply which can be sourced on the card or externally. The 3.3V system supply powers the Digital, Analog and  $PV_{DD}$  inputs. There may exist a need to electrically isolate the Digital, Analog and  $PV_{DD}$  (the portion of the Analog supply feeding the Phase Locked Loop) inputs using either a ferrite bead and/or decoupling capacitor configuration. The three power supplies ( $V_{DD}$ /GND,  $AV_{DD}$ /AGND,  $PV_{DD}$ /PGND) are separate within the PHY to allow for this electrical isolation on the card. The GND, AGND, and PGND are connected via the die substrate. See I/O Pin Function on page 8 or External Component Connections on page 39 for the locations of the power supply pins.

<sup>2.</sup> See Operating Conditions and Electrical Characteristics on page 6 for electrical characteristics.

# **Establishing the Link-PHY Interface**

### Overview

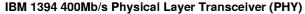

The Link-PHY interface is a scalable, cost effective method for connecting one 1394 Link device to one 1394 PHY device. The characteristics of this interface are described in the diagram below and in the Link-PHY Interface Pin Description on page 11. The PHY device has control of the bidirectional pins. The Link only drives these pins when control is transferred to it by the PHY.

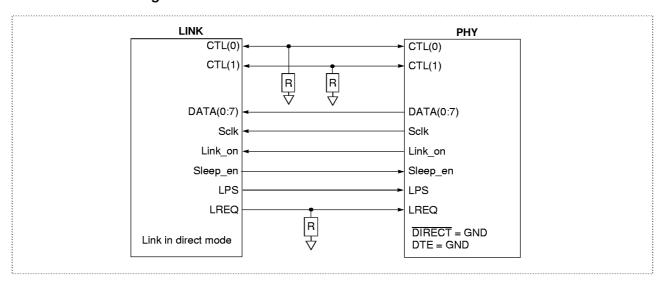

Data is transmitted between the two devices on the data bus. The data bus between the PHY and the Link device is clocked at the same rate for all supported speeds; however, the data rate is increased by widening the bus. The PHY uses two bits for 100Mb/s transfers, four bits for 200Mb/s, and eight bits for 400Mb/s. The control bus carries control information and is always two bits wide. The LREQ pin is used by the Link to request access to the serial bus and to read or write PHY registers. The DIRECT pin is used to disable the digital differentiator on the DATA and CTL pins, indicating that the two devices are connected directly, rather than through an isolation barrier requiring differentiating signals.

Specific guidelines for routing particular signals are given in Board Layout Recommendations on page 41.

### **Link-PHY Interface Diagram**

### **Link-PHY Interface Pin Description**

| Pin       | Driven By              | Description                                                                          |

|-----------|------------------------|--------------------------------------------------------------------------------------|

| DATA(0:7) | Link & PHY (tri-state) | Data                                                                                 |

| CTL(0:1)  | Link & PHY (tri-state) | Control                                                                              |

| LREQ      | Link                   | Link Request                                                                         |

| SCLK      | PHY                    | 49.152MHz (sync to serial bus) clock                                                 |

| LINK_ON   | PHY                    | Drives 6MHz signal to wake up Link when Link Power On packet is received and LPS = 0 |

| SLEEP_EN  | Link                   | Tells PHY to power down if none of its ports are in use                              |

| LPS       | Link                   | Link Power Status                                                                    |

| DIRECT    | neither                | Controls differentiator for interface pins                                           |

### **Link-PHY Electrical Isolation**

The need to isolate the Link from the PHY electrically may arise when a difference in potential exists between their respective grounds ( $GND_L$  and  $GND_P$ ). The particular device connected to the Link (CPU, disk drive, etc.) may also require isolation. Electrical isolation may also be implemented when the Link is disconnected and the cable becomes the PHY's source of power.

The PHY supports three types of connections between the Link and PHY: Direct, Capacitive, and IBM's Dynamic Termination for isolation between the IBM's PCI Link and PHY.

### **Direct Connection Between Link and PHY**

- 1. LREQ should have a pull down resistor (3.3Kohm recommended) if the PHY can be powered while the Link is powered down.

- 2. Each control line should have a pull down resistor if it is possible for the PHY to be in power-on-reset longer than the Link (less than 30mS with a 2.2μF cap on RESET) or if the preferred timing mode causes the control lines to float for a portion of a cycle in which noise may create problems for the Link. This is not a concern for the PHY.

- 3. LPS may be tied directly to the Link's V<sub>DD</sub> if the Link does not support LPS.

- 4. Sleep\_en may be tied directly to V<sub>DD</sub> or GND to control the sleep function if the Link is unable to control this function.

- 5. If Link\_on cannot be connected to the Link or Link support circuitry, it must be floated. This pin cannot be connected directly to ground.

- 6. The PHY supports communication with 3 or 5 volt Links.

### **Direct Connection Diagram**

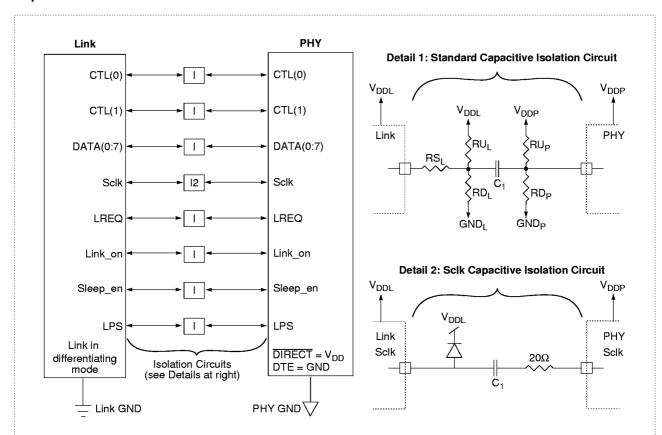

### **Capacitive Isolation with Differentiated Signals**

The diagram below shows electrical isolation between the Link and the PHY using cost efficient capacitive isolation barrier circuits. Each circuit provides isolation for one Link-PHY connection and handles a ground potential difference between the Link and the PHY based upon the voltage rating of the capacitor. See Component Values for Capacitive Isolation Barrier Circuit on page 14 for the specific component values based upon the Link  $V_{DD}$  supply (3.3V or 5V). Set the  $\overline{DIRECT}$  pin high for this operation.

### **Capacitive Isolation Barrier**

#### Notes:

- "I" represents the isolation circuit illustrated in Detail 1 and specified in Component Values for Capacitive Isolation Barrier Circuit on page 14. The isolation network can be reduced for most unidirectional signals (Link\_on, Sleep\_en, and LPS) by removing the resistors on the transmit side of the network.

- 2. "I2" represents the isolation circuit illustrated in Detail 2 and specified in Component Values for Capacitive Isolation Barrier Circuit on page 14.

- 3. Isolation networks are not needed for Link\_on, Sleep\_en, and LPS if the pin is not utilized by the Link or Host and are connected as described below.

- 4. LPS can NOT be tied directly to V<sub>DD</sub> of the PHY if the Link does not support LPS. LPS must be connected though a resistor (3.3K ohm recommended) if it is to be connected to a power source or GND.

- 5. Sleep\_en may be tied directly to  $V_{DD}$  or GND to control the sleep function if the Link is unable to do so.

- 6. Link\_on must be connected to a 3.3K ohm resistor to GND or floated if it is not utilized. This pin cannot be connected directly to ground.

### **Component Values for Capacitive Isolation Barrier Circuit**

| Component       | $V_{DDP} = 3.3V$ and $V_{DDL} = 3.3V$      | $V_{\rm DDP}$ = 3.3V and $V_{\rm DDL}$ = 5.0V |

|-----------------|--------------------------------------------|-----------------------------------------------|

| C <sub>1</sub>  |                                            | 1.0 nF                                        |

| RS <sub>L</sub> | Shorted                                    | 160 Ohm                                       |

| RU <sub>L</sub> | 5.0 KOhm                                   | 750 Ohm                                       |

| RD <sub>L</sub> | 5.0 KOhm                                   | 750 Ohm                                       |

| RD <sub>P</sub> | 5.0 KOhm                                   | 5.0 KOhm                                      |

| RU <sub>P</sub> | 5.0 KOhm                                   | 5.0 KOhm                                      |

| D <sub>l</sub>  | general purpose high-speed switching diode | general purpose high-speed switching diode    |

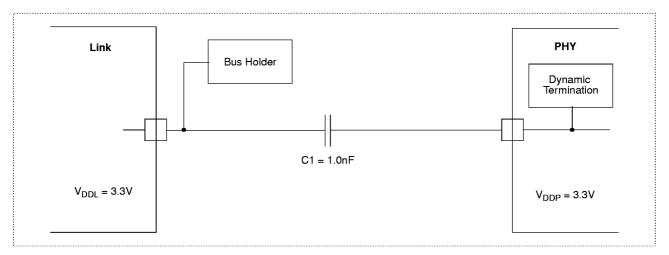

### **Isolation Using IBM's Dynamic Termination**

The Link and the PHY can be isolated using IBM's Dynamic Termination circuitry, provided that the power supply voltages of each are at the same nominal value. Isolation is achieved by using a 1.0nF capacitor, the PHY Dynamic Termination, and a Link bus latch, as shown below. For correct operation with isolation, this circuitry must be applied to each of the DATA, CTL, and LINK\_ON pins. LREQ, SLEEP\_EN, LPS, and SCLK only need capacitors.

The Link bus latch, which may be either built into the Link or external to it, holds received signals from the PHY at either an UP level or a DOWN level after they pass through the capacitor. Similarly, data pulses transmitted from the Link are held at their UP or DOWN levels by the Dynamic Termination of the PHY, which is enabled by tying the DTE pin high and the DIRECT pin low.

The PHY Dynamic Termination pins are automatically initialized at a DOWN level at power-on-reset. To assure proper data transmission, the Link must also be initialized at a DOWN level at power-on-reset.

Timing is not affected by the Dynamic Termination, so the timing values given in Link-PHY Interface Timing on page 16 are valid.

The Link and PHY ground planes must be connected to each other by at least one trio of  $0.001\mu F$ ,  $0.01\mu F$  and  $0.1\mu F$  coupling capacitors to provide an AC return path. The trio should be repeated as often as is feasible, equally distributed along the mutual borders of the ground planes, with a maximum spacing of about 1" between each capacitor and between each trio.

# **Dynamic Termination Diagram**

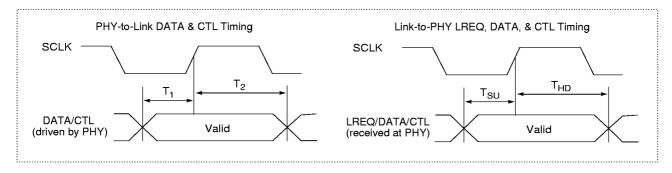

# **Link-PHY Interface Timing**

The IBM PHY features selectable SCLK timing that can be tailored to the needs of the Link device. The SCLK timing is controlled by the SCLK\_TSEL pin. When tied low, the SCLK has normal mode timing, and when tied high, the SCLK has early mode timing. In addition, the timing of data received from the Link can be adjusted using the RCV\_TSEL pin.

### **Link-PHY Interface Timing Relationships**

### **Normal Mode Timing**

| Symbol          | Parameter Min                                                             |      |    |  |  |  |

|-----------------|---------------------------------------------------------------------------|------|----|--|--|--|

| T <sub>1</sub>  | Time DATA/CTL valid before rising SCLK edge (PHY sending)                 | 16.0 | ns |  |  |  |

| T <sub>2</sub>  | Time DATA/CTL valid after rising SCLK edge (PHY sending)                  | 0.0  | ns |  |  |  |

| T <sub>SU</sub> | Setup time LREQ, DATA, CTL before rising SCLK edge (PHY receiving)        | 6.0  | ns |  |  |  |

| T <sub>HD</sub> | D Hold time LREQ, DATA, CTL after rising SCLK edge (PHY receiving) 0.0 ns |      |    |  |  |  |

### **Early Mode SCLK Timing**

| Symbol          | Parameter                                                               | Min  | Units |  |  |  |  |

|-----------------|-------------------------------------------------------------------------|------|-------|--|--|--|--|

| Т <sub>1</sub>  | Time DATA/CTL valid before rising SCLK edge (PHY sending)               | 8.0  | ns    |  |  |  |  |

| T <sub>2</sub>  | Time DATA/CTL valid after rising SCLK edge (PHY sending)                | 8.0  | ns    |  |  |  |  |

| T <sub>SU</sub> | Setup time LREQ, DATA, CTL before rising SCLK edge (PHY receiving)      | -2.0 | ns    |  |  |  |  |

| T <sub>HD</sub> | Hold time LREQ, DATA, CTL after rising SCLK edge (PHY receiving) 9.5 ns |      |       |  |  |  |  |

# **RCV Delayed Timing**

| Symbol          | Parameter                                                                                      | Min    | Units |  |  |  |  |

|-----------------|------------------------------------------------------------------------------------------------|--------|-------|--|--|--|--|

| T <sub>1</sub>  | Time DATA/CTL valid before rising SCLK edge (PHY sending)                                      | 16.0   | ns    |  |  |  |  |

| T <sub>2</sub>  | Time DATA/CTL valid after rising SCLK edge (PHY sending) 0.0 ns                                |        |       |  |  |  |  |

| T <sub>SU</sub> | Setup time LREQ, DATA, CTL before rising SCLK edge (PHY receiving) 12.5 ns                     |        |       |  |  |  |  |

| T <sub>HD</sub> | T <sub>HD</sub> Hold time LREQ, DATA, CTL after rising SCLK edge (PHY receiving) -2.5 ns       |        |       |  |  |  |  |

|                 | ated with C <sub>L</sub> = 10 pF<br>ettings: SCLK_TSEL = 'GND', RCV_TSEL = 'V <sub>DD</sub> '. | ······ |       |  |  |  |  |

# **Early Mode RCV Delayed Timing**

| Symbol          | Parameter                                                                               | Min | Units |  |  |  |  |

|-----------------|-----------------------------------------------------------------------------------------|-----|-------|--|--|--|--|

| T <sub>1</sub>  | Time DATA/CTL valid before rising SCLK edge (PHY sending)                               | 8.0 | ns    |  |  |  |  |

| T <sub>2</sub>  | Time DATA/CTL valid after rising SCLK edge (PHY sending)                                | 8.0 | ns    |  |  |  |  |

| T <sub>SU</sub> | Setup time LREQ, DATA, CTL before rising SCLK edge (PHY receiving)                      | 4.5 | ns    |  |  |  |  |

| T <sub>HD</sub> | T <sub>HD</sub> Hold time LREQ, DATA, CTL after rising SCLK edge (PHY receiving) 7.5 ns |     |       |  |  |  |  |

|                 | ated with $C_L = 10 \text{ pF}$ ettings: $SCLK_TSEL = \text{`V}_{DD}\text{'}$ .         |     |       |  |  |  |  |

### **Link-PHY Diagnostics**

The IBM21S851 and IBM21S850 offer the ability to test the Link-PHY interface using available Link-PHY protocol, a beneficial feature for hardware testing and field diagnostic software. When utilizing this feature outside a controlled environment, all ports should be disabled via PHY register 0xE.

The Link-PHY interface can be tested in both directions: Link-to-PHY and PHY-to-Link. The following tests the interface from the Link to the PHY.

The Link-PHY interface self test is enabled by writing a logic '1' to bit 1 of PHY register 0xD.

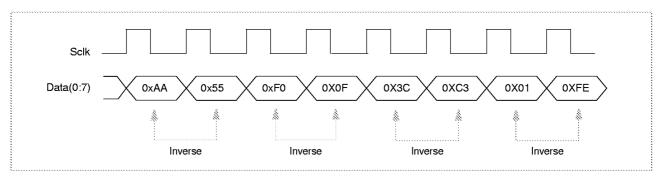

At this point, the link issues either a fair, priority, or isochronous bus request via the LREQ to transmit a 400Mb/s packet. When the PHY grants the bus to the Link, the Link must respond by sending a packet of any length (IEEE-1394 packet length rules do not apply) to the PHY. The data must be in groups of two bytes in which the second byte is the logical inverse of the previous byte. For example, the 400Mb/s packet may be as follows:

### 400Mb/s Diagnostic Packet Example

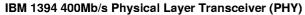

The Link may use normal protocol (i.e. issue a "Hold" prior to Transmit). The data integrity is confirmed by the PHY inverse checking of the packet. The PHY indicates an inverse error by setting the Link-PHY Error Ever Happened bit. To confirm data transmission from the PHY to the Link, the Link needs to set the Send Phy/Link Diag Pkt bit in PHY register 0xF. The PHY responds by sending its self\_ID packet to the Link as a 400Mb/s packet, at which time the Link and/or software may check that the last 32 bits are the inverse of the first 32 bits. The Phy/Link Diag Pkt bit is cleared after the transmission of the 400Mb/s self\_ID packet.

# **Configuring Hardware Alternatives**

# **RESET** Circuit Design

It is important that the following information be considered if the  $\overline{\text{RESET}}$  pin is to be controlled by something other than the recommended RC circuit shown above.

If the PHY is allowed to sleep, one of the two circuits shown in the RESET Control with Sleep Enabled diagrams is required for use in applications where the  $\overline{\text{RESET}}$  pin is controlled by something other than the RC circuit created with the 2.2 $\mu$ F capacitor and the internal resistor. The open collector driver should not be shared with any other circuitry.

The circuit shown in the RESET Control when Sleep is Not Enabled diagram is recommended when external control of the RESET pin is desired and the PHY is not allowed to go to sleep.

The  $2.2\mu F$  capacitor can only be removed if the external reset control will guarantee that the PHY remains in POR for no less than 10mS after power on. After power on, the PHY can be reset with a negative pulse lasting no less than 100nS. The PHY should not be held in POR for longer than 100mS after power on and less than 100 $\mu S$  during normal operation. Causing the PHY to enter POR will disrupt any activity on the serial bus and cause a long reset (not an arbitrated short reset). The Software POR in Link Accessible Register (LAR) 0xF bit 0 should be used as a first approach to resetting the PHY.

While in POR, the PHY tri-states the CTL(0:1), DATA(0:7), LREQ, and LPS interface pins. The SCLK continues to generate Sclk in POR. Link\_on is driven low at this time.

The PHY offers the Link the ability to issue a POR to the PHY by writing PHY register 0xF with 0x80. Within a few cycles, the PHY will issue the Link a status of bus reset as it exits POR and enters bus reset.

### Holding the PHY in Power-On-Reset

While in Power-On-Reset (POR), the PHY will create Tp\_Bias on all ports. Holding the PHY in POR could create problems on the serial bus as other nodes sense the PHY's Tp\_Bias and try to go through reset. All ports should be disabled by writing 0x7 in PHY register 0xE when holding the PHY off the network for long periods. Disabling a port reduces the amount of power consumed and prevents the PHY from generating TpBias. In addition, if ports are disabled within the remote PHY's debounce time (usually 0.3 seconds), the serial cable connection will not interrupt the existing network until after the port is enabled.

Normally when the PHY is initially powered on, the PHY is held in reset via an RC circuit created with a  $2.2\mu$ F capacitor and an internal resistor as shown in Recommended RESET Circuit on page 19.

## Setting Module Pins to Configure PHY as a Repeater

| Module Pin          | Connection                                           |

|---------------------|------------------------------------------------------|

| Sclk                | Float (or 3.3K ohm to GND to reduce EMI emissions).  |

| Ctl(0:1), Data(0:7) | Float                                                |

| Direct              | GND                                                  |

| DTE                 | GND                                                  |

| SLEEP_EN            | $V_DD$ to enable Sleep otherwise GND                 |

| LPS                 | Resistor to GND (1K to 3.3K ohm typical)             |

| Link_on             | Float (or 3.3 K ohm to GND to reduce EMI emissions). |

### **PHY Hardware Simulation Mode**

The IBM PHY offers the unique ability to operate in an environment that is at a very slow speed. This feature enables the IBM PHY to be connected directly to hardware emulators (i.e. emulating a Link), while supporting IEEE-1394 communication over the standard IEEE 1394 cable to other IBM PHYs running in the same mode. The PHY will initialize the bus and operate as it would normally, except much more slowly.

The procedure to slow down the PHY for simulation purposes is as follows.

- 1. The PHY must be wired normally as defined by this specification. The following changes must be made:

- Module pin TEST 0 must be tied to V<sub>DD</sub>.

- The TpBias capacitor must be changed according to the following equation:

$$C = \frac{0.0248 \text{Amps} \times 48 \text{cycles} \times \text{Toscin}}{0.05 \text{V}}$$

where Toscin = 1/(osc\_in input frequency)

- Osc in is applied a frequency that should not exceed 50MHz.

- 2. All the PHYs on the "slow down" network must have their oscillators set within 100 PPM to function properly. You must comply with all 1394 rules (e.g. max. packet length at a given speed). For example, if you request the bus for a 400Mb/s, your packet length must not exceed 4K bytes even though you slowed down the frequency.

# **Frequency Translation for Hardware Simulation Mode**

| Signal Name | Signal Rate  |

|-------------|--------------|

| Osc_in      | 400MHz       |

| Osc_in/2    | 200MHz       |

| Osc_in/4    | 100MHz       |

| Osc_in/8    | 50MHz (sclk) |

If you apply a 25MHz signal to osc\_in, your sclk will be 3.13MHz (Osc\_in/8) rather than the 50MHz if you were in normal mode. If you send the PHY a 400Mb/s link request, the PHY will transmit 400Mb/s speed signaling but the actual rate will be your osc\_in (25Mb/s in this example).

# **Using Only One or Two Ports of the Three-Port PHY**

| Unused Port                     | Wire As                |

|---------------------------------|------------------------|

| TPAn, TPAn                      | Floated or tied to GND |

| TPBn, TPBn                      | Connected to GND       |

| TpBias_n                        | ≥0.1µf cap to GND      |

| n = the number of unused ports. |                        |

# **Programming the PHY**

# **Register Mapping**

# Register Map for One-Port PHY

| Address           | 0                    | 1                      | 2                    | 3                       | 4                    | 5             | 6                      | 7               |  |

|-------------------|----------------------|------------------------|----------------------|-------------------------|----------------------|---------------|------------------------|-----------------|--|

| 00002             |                      | •••••                  | Physi                | CPS                     |                      |               |                        |                 |  |

| 0001 <sub>2</sub> | RHB                  | IBR                    | Gap_Count            |                         |                      |               |                        |                 |  |

| 00102             | SI                   | PD                     | E                    |                         | 1                    | Number of Por | ts                     |                 |  |

| 0011 <sub>2</sub> | AS                   | at 1                   | BSt                  | at 1                    | Ch 1                 | Con 1         | Peer                   | Sp 1            |  |

| 01002             | El                   | ٧V                     |                      | **********************  | Reg                  | Count         |                        |                 |  |

| 0101 <sub>2</sub> |                      |                        |                      |                         |                      |               |                        |                 |  |

| 0110 <sub>2</sub> |                      |                        |                      |                         |                      |               |                        |                 |  |

| 0111 <sub>2</sub> |                      | Reserved               |                      |                         |                      |               |                        |                 |  |

| 10002             |                      |                        |                      | Hese                    | ervea                |               |                        |                 |  |

| 1001 <sub>2</sub> |                      |                        |                      |                         |                      |               |                        |                 |  |

| 1010 <sub>2</sub> |                      |                        |                      |                         |                      |               |                        |                 |  |

| 1011 <sub>2</sub> | LPS Input            | PHY                    | Delay                | СМС                     |                      | Power Class   |                        | Reserved        |  |

| 11002             | CMC Input            | CPS<br>Interrupt       | L-P Self-test<br>EEH | Arbitratio              | on Phase             | ,             | Arbitration State      | €               |  |

| 1101 <sub>2</sub> | Reserved             | Enable L-P<br>Selftest | Rese                 | erved                   | En. Ack<br>Accel Arb | Reserved      | En. Multi Sp<br>Concat | Mask LPS<br>bit |  |

| 1110 <sub>2</sub> | En. TX/RX<br>timeout | lgnore<br>Unplug       | Override<br>CMC      | Soft<br>CMC             | Reserved             | Disable P1    | Rese                   | rved            |  |

| 1111 <sub>2</sub> | Soft<br>POR          | Reserved               | Send P-L<br>packet   | Ack_Accel<br>Cycle Sync | ISBR                 |               | Reserved               |                 |  |

# **Register Map for Three-Port PHY**

| Address           | 0                    | 1                      | 2                                     | 3                       | 4                    | 5           | 6                                       | 7               |

|-------------------|----------------------|------------------------|---------------------------------------|-------------------------|----------------------|-------------|-----------------------------------------|-----------------|

| 00002             |                      |                        | Physic                                | cal_ID                  |                      |             |                                         | CPS             |

| 00012             | RHB                  | IBR                    | · · · · · · · · · · · · · · · · · · · |                         | Gap_Count            |             | · · · · · · · · · · · · · · · · · · ·   |                 |

| 0010 <sub>2</sub> | SF                   | PD                     | E                                     |                         | ١                    | ts          |                                         |                 |

| 0011 <sub>2</sub> | ASt                  | at 1                   | BSt                                   | at 1                    | Ch 1                 | Con 1       | Peer Sp 1                               |                 |

| 01002             | ASt                  | at 2                   | BSt                                   | at 2                    | Ch 2                 | Con 2       | Peer                                    | Sp 2            |

| 0101 <sub>2</sub> | ASt                  | at 3                   | BSt                                   | at 3                    | Ch 3                 | Con 3       | Peer                                    | Sp 3            |

| 0110 <sub>2</sub> | Εľ                   | ٧V                     |                                       | •••••                   | Reg                  | Count       | *************************************** |                 |

| 0111 <sub>2</sub> |                      |                        |                                       |                         |                      |             |                                         |                 |

| 1000 <sub>2</sub> |                      |                        |                                       | Rese                    |                      |             |                                         |                 |

| 1001 <sub>2</sub> |                      |                        |                                       | nese                    | ervea                |             |                                         |                 |

| 1010 <sub>2</sub> |                      |                        |                                       |                         |                      |             |                                         |                 |

| 1011 <sub>2</sub> | LPS Input            | PHY                    | Delay                                 | CMC                     |                      | Power Class |                                         | Reserved        |

| 1100 <sub>2</sub> | CMC Input            | CPS<br>Interrupt       | L-P Self-test<br>EEH                  | Arbitratio              | on Phase             | ,           | Arbitration Stat                        | 9               |

| 1101 <sub>2</sub> | Reserved             | Enable L-P<br>Selftest | Reserved                              | Reserved                | En. Ack<br>Accel Arb | Reserved    | En. Multi Sp<br>Concat                  | Mask LPS<br>bit |

| 1110 <sub>2</sub> | En. TX/RX<br>timeout | lgnore<br>Unplug       | Override<br>CMC                       | Soft<br>CMC             | Reserved             | Disable P1  | Disable P2                              | Disable P3      |

| 11112             | Soft<br>POR          | Reserved               | Send P-L<br>packet                    | Ack_Accel<br>Cycle Sync | ISBR                 |             | Reserved                                |                 |

# PHY Register Fields (Part 1 of 3)

| Field           | Size | Туре | Description                                                                                                                                                                                                                                                                                                  |

|-----------------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Physical_ID     | 6    | r    | Node address determined during self-identification.                                                                                                                                                                                                                                                          |

| R               | 1    | r    | Root indication. 1 = this node is the root.                                                                                                                                                                                                                                                                  |

| CPS             | 1    | r    | Cable power status. 1 = power in the cable.                                                                                                                                                                                                                                                                  |

| RHB             | 1    | rw   | Root hold-off bit. 1 = the PHY will attempt to become the root during the next bus reset.                                                                                                                                                                                                                    |

| IBR             | 1    | rw   | Initiate bus reset.1 = initiate a bus reset at the next normal arbitration phase.                                                                                                                                                                                                                            |

| Gap_count       | 6    | rw   | Arbitration timer setting. Used to optimize the Subaction Gap time, the Arbitration Reset Gap time, and the Arbitration Response Time threshold, based on the size of the network. This field is initially reset to a value of 0b'111111'. See clauses 4.3.6 and 8.4.6.2 of the IEEE 1394-1995 Standard [1]. |

| SPD             | 2    | r    | Maximum data transfer rate.  00 = 98.304Mb/s  01 = 196.608Mb/s  10 = 393.216Mb/s  11 = reserved  When read, the IBMIBM21S850 and IBM21S851 both return 10 to indicate 400Mb/s.                                                                                                                               |

| E               | 1    | r    | Enhanced register map indication. This product has an enhanced register map, so this field will always be '1'.                                                                                                                                                                                               |

| Number of Ports | 5    | r    | The number of ports on this PHY. IBM21S850 will always read 0b'00011' indicating it has three ports. IBM21S851 will always read 0b'00001' indicating it has one port.                                                                                                                                        |

| AStat 1         | 2    | r    | TPA arbitration signal state on Port 1.<br>11 = Z<br>01 = 1<br>10 = 0<br>00 = invalid                                                                                                                                                                                                                        |

| BStat 1         | 2    | r    | TPB arbitration signal state on Port 1.  11 = Z  01 = 1  10 = 0  00 = Port not connected                                                                                                                                                                                                                     |

| Ch 1            | 1    | r    | Port 1 child indication. 1 = child port; 0 = parent port.                                                                                                                                                                                                                                                    |

| Con 1           | 1    | r    | Port 1 connection status. 1 = port 1 is connected; 0 = port 1 is disconnected.                                                                                                                                                                                                                               |

| Peer Sp 1       | 2    | r    | Maximum Peer Speed latched during SID Speed Capability Exchange for Port 1.                                                                                                                                                                                                                                  |

| AStat 2         | 2    | r    | TPA arbitration signal state on Port 2.  11 = Z  01 = 1  10 = 0  00 = invalid                                                                                                                                                                                                                                |

| BStat 2         | 2    | r    | TPB arbitration signal state on Port 2.  11 = Z  01 = 1  10 = 0  00 = Port not connected                                                                                                                                                                                                                     |

| Ch 2            | 1    | r    | Port 2 child indication. 1 = child port; 0 = parent port.                                                                                                                                                                                                                                                    |