# IOT7210 Low-Power CMOS IEEE 488 Controller Device

NEW

#### Features

- Completely meets IEEE Standard 488-1978:

- SH1, source handshake

- AH1, acceptor handshake

- T5 or TE5, talker or extended talker

- L3 or LE3, listener or extended listener

- SR1, service request

- www.DataSheckLl, remote local

- PP1 or PP2, parallel poll, remote, or local configuration

- DC1, device clear

- DT1, device trigger

- C1-C5, controller, all functions

- Programmable data transfer rate

- 16 registers, 8 read/8 write

- 2 address registers: detect MTA, MLA, MSA (my talk/my listen/my secondary addresses) and provide 2 device addresses

- End-of-string (EOS) message automatic detection

- Automatic (IEEE Standard 488-78) command processing and undefined command read capability

- DMA-capable

- Programmable bus transceiver I/O specification, Texas Instruments/ Motorola/Intel-compatible

- 1 MHz to 8 MHz clock range

- TTL-compatible

- CMOS

- +5V single power supply

- 40-pin plastic DIP or 44-pin plastic TQFP

- 8080/85/86-compatible

The IOT7210 low-power CMOS intelligent IEEE 488 controller meets all the functional requirements for talkers, listeners, and controllers as specified by the IEEE Standard 488-1978. It completely duplicates the NEC  $\mu$ PD7210's function and provides enhancements such as lower power consumption and increased speed. Fully compatible with most processor architectures, the IOT7210 requires only the addition of the bus driver/receiver components to implement any IEEE 488 interface.

In its 40-pin plastic DIP package, the IOT7210 provides users with a drop-in replacement for the  $\mu$ PD7210 and eliminates the need for either software or hardware modifications. It is also available in

The IOT7210 is an enhanced replacement for the NEC µPD7210 IEEE 488 controller device

a 44-pin, 1.27 mm thick plastic TQFP package for surface-mount applications.

# IOT7210 Operation on the IEEE 488 Bus

Since its introduction in the 1970s, the IEEE 488 standard has become the most popular means of interconnecting instruments and controllers. This highly sophisticated standard has been refined over the years to provide a great degree of flexibility, permitting it to meet most instrumentation requirements.

The IEEE 488 bus uses a common set of data and control lines to interconnect up to 15 devices. The device's capabilities are classified as a combination of talker, listener, and/or controller. Devices that incorporate the IOT7210 can perform all three functions—talker, listener, and controller.

Data is transferred on the IEEE 488 bus in a bit-parallel, byte-serial fashion over eight bidirectional data lines. A 3-wire handshake ensures synchronization of transmission and reception and allows more than one device to receive data at the same time, with the slowest device controlling the data rate. Other control lines perform a variety of functions, such as device addressing and interrupt generation. In addition to providing all the control and data lines necessary for IEEE 488 operation, the IOT7210 provides a flexible interface to the standard IEEE 488 transceivers.

The IOT7210 implements all the functions (including timing) that are required to interface to the IEEE 488 bus and provides high-level bus protocol management, which frees the host processor for other tasks. By performing these functions in dedicated hardware, the IOT7210 ensures bus compatibility with other IEEE 488 devices.

The IOT7210 is controlled by its 16 internal registers. To reduce CPU overhead, bus data bytes can be transferred to and from the IOT7210 using DMA. The IOT7210's DMA feature is generic enough that it can be used to interface to most processors and buses.

# Pin Configurations

| Pin<br>DIP | (TQFP)             | Symbol                                              | I/O | Functions                                                                                                                                                                               |

|------------|--------------------|-----------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | (40)               | T/R <sub>1</sub>                                    | 0   | <i>Transmit/Receive Control.</i> Input/output control signal for the IEEE 488 bus transceivers.                                                                                         |

| 2          | (41)               | T/R <sub>2</sub>                                    | 0   | Transmit/Receive Control. The values of TRM1and TRM0 of the address mode register control the functions of $T/R_2$ and $T/R_3$ .                                                        |

| 3          | (42)               | CLK                                                 | Ι   | Clock. 1 MHz to 8 MHz reference clock for generating the state change prohibit times $T_1$ , $T_6$ , $T_7$ , $T_8$ , specified in IEEE Standard 488-1978.                               |

| 4          | (43)               | RESET                                               | Ι   | <i>Reset.</i> Resets the IOT7210 to an idle state when high (active high).                                                                                                              |

| 5          | (44)               | T/R <sub>3</sub>                                    | 0   | Transmit/Receive Control. See T/R <sub>2</sub> .                                                                                                                                        |

| 6          | (1)                | DRQ                                                 | 0   | DMA Request. Requests data transfer. Becomes low on input of DMA acknowledge signal DACK.                                                                                               |

| 7          | (2)                | DACK                                                | I   | DMA Acknowledge. Active low. Connects the data bus $(D_0 - D_7)$ to the byte in or data out register of the IOT7210.                                                                    |

| 8          | (3)                | ĊŚ                                                  | Ι   | Chip Select. Active low. Enables access to the register selected by $RS_0 - RS_2$ (read or write operation).                                                                            |

| 9          | (4)                | RD                                                  | I   | <i>Read.</i> Active low. Places contents of read register specified $RS_0 - RS_2$ on $D_0 - D_7$ (computer bus).                                                                        |

| 10         | (5)                | WR                                                  | Ι   | <i>Write.</i> Active low. Writes data on $D_0 - D_7$ into the write register specified by $RS_0 - RS_2$ .                                                                               |

| 11         | (6)                | INT,<br>INT                                         | 0   | Interrupt Request. Active high/low. Becomes active<br>due to any 1 of 13 internal interrupt conditions<br>(unmasked). Active state software configurable.<br>Active high on chip reset. |

| 12-19      | (8-11,<br>13-16)   | D <sub>0</sub> - D <sub>7</sub>                     | I/O | <i>Data Bus.</i> 8-bit bidirectional data bus for interface to the computer system.                                                                                                     |

| 20         | (7, 17,<br>25, 34) | GND                                                 |     | Ground.                                                                                                                                                                                 |

| 21-23      | (18-20)            | RS <sub>0</sub> - RS <sub>2</sub>                   | Ι   | <i>Register Select</i> . Select one of eight read (write) registers during a read (write) operation.                                                                                    |

| 24         | (21)               | IFC                                                 | I/O | Interface Clear. IEEE 488 control line. Clears the interface functions.                                                                                                                 |

| 25         | (22)               | REN                                                 | I/O | <i>Remote Enable.</i> IEEE 488 control line. Selects remote or local control of the devices.                                                                                            |

| 26         | (23)               | ATN                                                 | I/O | Attention. IEEE 488 control line. Indicates whether data on DIO lines is an interface message or device dependent message.                                                              |

| 27         | (24)               | SRQ                                                 | I/O | <i>Service Request.</i> IEEE 488 control line. Requests the service from the controller.                                                                                                |

| 28-35      | (26-33)            | $\overline{\text{DIO}}_1 - \overline{\text{DIO}}_8$ | I/O | Data Input/Output. IEEE 488 8-bit bi-directional bus for transfer of message.                                                                                                           |

| 36         | (35)               | DAV                                                 | I/O | Data Valid. IEEE 488 handshake line. Indicates that data on DIO lines is valid.                                                                                                         |

| 37         | (36)               | NRFD                                                | I/O | <i>Ready for Data.</i> IEEE 488 handshake line. Indicates that device is ready for data.                                                                                                |

| 38         | (37)               | NDAC                                                | I/O | Data Accepted. IEEE 488 handshake line. Indicates completion of message reception.                                                                                                      |

| 39         | (38)               | EOI                                                 | I/O | <i>End or Identify.</i> IEEE 488 control line. Indicates the end of multiple byte transfer sequence or signals a parallel poll in conjunction with ATN.                                 |

| 40         | (12, 39)           | V <sub>CC</sub>                                     | I/O | +5V DC.                                                                                                                                                                                 |

### **IOT7210P**

| T/R <sub>1</sub>   | 1  | 40 | V <sub>cc</sub>  |

|--------------------|----|----|------------------|

| T/R <sub>2</sub>   | 2  | 39 | EOI              |

| CLK [              | 3  | 38 | NDAC             |

| RESET [            | 4  | 37 | NRFD             |

| T/R <sub>3</sub> [ | 5  | 36 | DAV              |

| DRQ [              | 6  | 35 | DIO <sub>8</sub> |

| DACK [             | 7  | 34 | DIO <sub>7</sub> |

| ĊS E               | 8  | 33 | DIO6             |

| RD [               | 9  | 32 | DIO5             |

| WR                 | 10 | 31 | DIO <sub>4</sub> |

| INT [              | 11 | 30 | DIO3             |

| D <sub>0</sub> [   | 12 | 29 | DIO2             |

| D <sub>1</sub> [   | 13 | 28 | DIO              |

| D <sub>2</sub> [   | 14 | 27 | SRQ              |

| D <sub>3</sub> [   | 15 | 26 | ATN              |

| D <sub>4</sub> [   | 16 | 25 | REN              |

| D <sub>5</sub> [   | 17 | 24 | IFC              |

| D <sub>6</sub> [   | 18 | 23 | RS <sub>2</sub>  |

| D <sub>7</sub> [   | 19 | 22 | RS <sub>1</sub>  |

| GND [              | 20 | 21 | RS               |

|                    | L  |    | 5                |

|                    |    |    |                  |

#

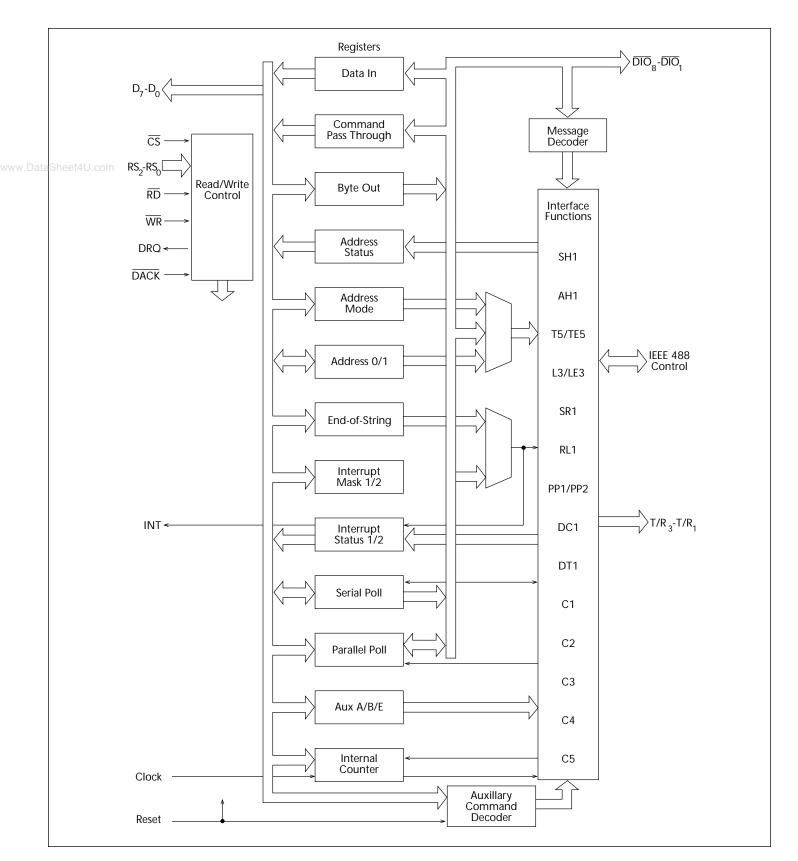

# Functional Block Diagram

# **Electrical Characteristics**

# Absolute Maximum Ratings

Exposing the device to stresses above those listed here could cause permanent damage to the IOT7210. The device is not meant to be operated under conditions outside the limits described in this specification. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| T <sub>A</sub> =                           | 25C                            |

|--------------------------------------------|--------------------------------|

| Supply Voltage, V <sub>cc</sub>            | -0.3V to +7.0V                 |

| Input Voltage, V <sub>I</sub>              | -0.3V to V <sub>cc</sub> +0.3V |

| Output Voltage, V <sub>o</sub>             | -0.3V to V <sub>cc</sub> +0.3V |

| Operating<br>Temperature, T <sub>OPR</sub> | 0C to +70C                     |

| Storage<br>Temperature, T <sub>STG</sub>   | -55C to 125C                   |

## Capacitance

| -                                   | $T_{A} = 25C; V_{CC} = GND = 0V$ |    |    |                                                        |  |  |  |  |  |  |

|-------------------------------------|----------------------------------|----|----|--------------------------------------------------------|--|--|--|--|--|--|

| Symbol Min Max Unit Test Conditions |                                  |    |    |                                                        |  |  |  |  |  |  |

| CIN                                 |                                  | 15 | рF | F = 1 MHz                                              |  |  |  |  |  |  |

| C <sub>OUT</sub>                    |                                  | 15 | pF | All pins except pin<br>under test tied to<br>AC ground |  |  |  |  |  |  |

| C <sub>I/O</sub>                    |                                  | 15 | pF |                                                        |  |  |  |  |  |  |

### **AC/DC Characteristics**

| AC Characteristics                                                  |                    |          |                           |      |                                                                                                                                  |  |  |  |  |

|---------------------------------------------------------------------|--------------------|----------|---------------------------|------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| $\rm T_{A}$ = 0C to 70C; $\rm V_{cc}~$ = 5V $\pm$ 10%               |                    |          |                           |      |                                                                                                                                  |  |  |  |  |

| Parameter                                                           | Symbol             | Min      | Max                       | Unit | Test Conditions                                                                                                                  |  |  |  |  |

| ĒOI ↓ → DIO                                                         | t <sub>EODI</sub>  |          | 35                        | ns   | PPSS→ PPAS, ATN = True                                                                                                           |  |  |  |  |

| ĒOI ↓ → T/R <sub>1</sub> ↑                                          | t <sub>EOTI1</sub> |          | 20                        | ns   | PPSS → PPAS, ATN = True                                                                                                          |  |  |  |  |

| $\overline{EOI} \uparrow \longrightarrow T/R_1 \downarrow$          | t <sub>EOTI2</sub> |          | 25                        | ns   | PPAS $\rightarrow$ PPSS, ATN = False                                                                                             |  |  |  |  |

| ATN ↓ → NDAC ↓                                                      | t <sub>ATN0</sub>  |          | 35                        | ns   | AIDS → ANRS, LIDS                                                                                                                |  |  |  |  |

| $\overline{\text{ATN}} \downarrow \longrightarrow T/R_1 \downarrow$ | t <sub>ATT1</sub>  |          | 30                        | ns   | TACS + SPAS → TADS, CIDS                                                                                                         |  |  |  |  |

| $\overline{\text{ATN}} \downarrow \longrightarrow T/R_2 \downarrow$ | t <sub>ATT2</sub>  |          | 30                        | ns   | TACS + SPAS → TADS, CIDS                                                                                                         |  |  |  |  |

| DAV ↓ → DRQ↑                                                        | t <sub>DVRQ</sub>  |          | 25                        | ns   | ACRS → ACDS, LACS                                                                                                                |  |  |  |  |

| DAV ↓ → NRFD ↓                                                      | t <sub>DVNR1</sub> |          | 30                        | ns   | ACRS -> ACDS                                                                                                                     |  |  |  |  |

| DAV ↓ → NDAC ↑                                                      | t <sub>DVND1</sub> |          | 40                        | ns   | $ACRS \rightarrow ACDS \rightarrow AWNS$                                                                                         |  |  |  |  |

| DAV ↑ → NDAC ↓                                                      | t <sub>DVND2</sub> |          | 45                        | ns   | AWNS -> ANRS                                                                                                                     |  |  |  |  |

| DAV ↑ → NRFD ↑                                                      | t <sub>DVNR2</sub> |          | 35                        | ns   | AWNS → ANRS → ACRS                                                                                                               |  |  |  |  |

| $\overline{RD}$ $\rightarrow$ $\overline{NRFD}$ $\uparrow$          | t <sub>RNR</sub>   |          | 30                        | ns   | ANRS $\rightarrow$ ACRS $\rightarrow$<br>LACS, DI register selected                                                              |  |  |  |  |

| NDAC ↑ → DRQ↑                                                       | t <sub>NDRQ</sub>  |          | 25                        | ns   | STRS →SWNS →SGNS, TACS                                                                                                           |  |  |  |  |

| NDAC ↑ → DAV ↑                                                      | t <sub>NDDV</sub>  |          | 25                        | ns   | $STRS \rightarrow SWNS \rightarrow SGNS$                                                                                         |  |  |  |  |

| $\overline{WR} \uparrow \longrightarrow \overline{DIO}$             | t <sub>WDI</sub>   |          | 30                        | ns   | SGNS → SDYS<br>BO register selected                                                                                              |  |  |  |  |

| NRFD ↑ → DAV ↓                                                      | t <sub>NRDV</sub>  |          | 30                        | ns   | SDYS $\rightarrow$ STRS, T <sub>1</sub> = True                                                                                   |  |  |  |  |

| $\overline{WR} \bigstar \longrightarrow \overline{DAV} \checkmark$  | t <sub>WDV</sub>   |          | 550<br>+t <sub>SYNC</sub> | ns   | SGNS $\rightarrow$ SDYS $\rightarrow$ STRS<br>BO register selected;<br>RFD = True; N + fc = 8MHz;<br>T <sub>1</sub> (high speed) |  |  |  |  |

| TRIG Pulse Width                                                    | t <sub>TRIG</sub>  | 50       |                           | ns   |                                                                                                                                  |  |  |  |  |

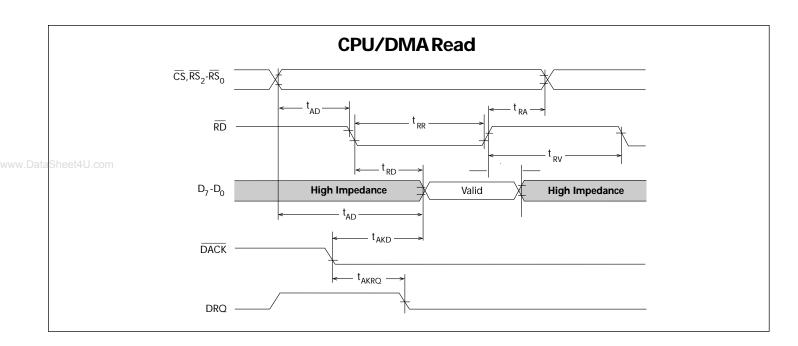

| Address Setup to RD                                                 | t <sub>AR</sub>    | 0        |                           | ns   | RS <sub>0</sub> to RS <sub>2</sub>                                                                                               |  |  |  |  |

|                                                                     |                    | 0        |                           | ns   | CS                                                                                                                               |  |  |  |  |

| Address Hold from RD                                                | t <sub>RA</sub>    | 0        |                           | ns   |                                                                                                                                  |  |  |  |  |

| RD Pulse Width                                                      | t <sub>RR</sub>    | 55       |                           | ns   |                                                                                                                                  |  |  |  |  |

| Data Delay from Address                                             | t <sub>AD</sub>    |          | 35                        | ns   |                                                                                                                                  |  |  |  |  |

| Data Delay from RD 🏼                                                | t <sub>RD</sub>    |          | 35                        | ns   |                                                                                                                                  |  |  |  |  |

| Output Float Delay from RD↑                                         | t <sub>DF</sub>    | 0        | 10                        | ns   |                                                                                                                                  |  |  |  |  |

| RD Recovery Time                                                    | t <sub>RV</sub>    | 50       |                           | ns   |                                                                                                                                  |  |  |  |  |

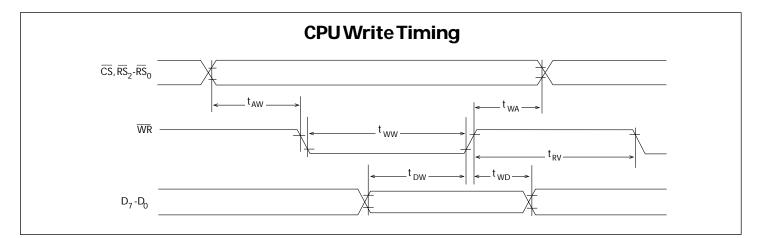

| Address Setup to WR                                                 | t <sub>AW</sub>    | 0        |                           | ns   |                                                                                                                                  |  |  |  |  |

| Address Hold from WR                                                | t <sub>WA</sub>    | 0        |                           | ns   |                                                                                                                                  |  |  |  |  |

| WR Pulse Width                                                      | t <sub>ww</sub>    | 55       |                           | ns   |                                                                                                                                  |  |  |  |  |

| Data Setup to WR                                                    | t <sub>DW</sub>    | 10       |                           | ns   |                                                                                                                                  |  |  |  |  |

| Data Hold from WR                                                   | t <sub>WD</sub>    | 0        |                           | ns   |                                                                                                                                  |  |  |  |  |

| WR Recovery Time                                                    | t <sub>RV</sub>    | 50       |                           | ns   |                                                                                                                                  |  |  |  |  |

| DRQ ↓ Delay from DACK ↓                                             | t <sub>AKRQ</sub>  |          | 25                        | ns   |                                                                                                                                  |  |  |  |  |

| Data Delay from DACK                                                | t <sub>AKD</sub>   |          | 35                        | ns   |                                                                                                                                  |  |  |  |  |

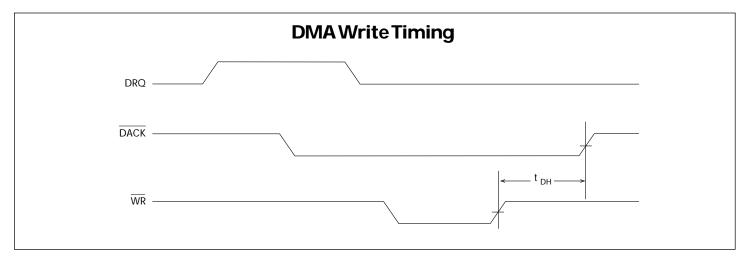

| DACK hold time from WR                                              | t <sub>DH</sub>    | 5        |                           | ns   |                                                                                                                                  |  |  |  |  |

|                                                                     | D                  | C Charad | teristics                 |      |                                                                                                                                  |  |  |  |  |

| DC Characteristics                        |                                           |                      |                      |    |                                  |  |  |  |

|-------------------------------------------|-------------------------------------------|----------------------|----------------------|----|----------------------------------|--|--|--|

|                                           | $T_A = 0C$ to 70C; $V_{cc} = 5V \pm 10\%$ |                      |                      |    |                                  |  |  |  |

| Input Low Voltage (except RESET)          | V <sub>IL</sub>                           | -0.3                 | +.08                 | V  |                                  |  |  |  |

| Input High Voltage (except RESET)         | Vін                                       | +2.0                 | V <sub>CC</sub> +0.3 | ٧  |                                  |  |  |  |

| Input Low Voltage (RESET)                 | -0.3                                      | 0.7                  | V                    |    |                                  |  |  |  |

| Input High Voltage (RESET)                | +2.1                                      | V <sub>CC</sub> +0.3 | V                    |    |                                  |  |  |  |

| Low-Level Output Voltage                  | V <sub>OL</sub>                           |                      | +0.4                 | V  |                                  |  |  |  |

| High-Level Output Voltage<br>(except INT) | V <sub>OH1</sub>                          | +2.4                 |                      | v  | I <sub>OH</sub> = 1mA            |  |  |  |

| High-Level Output                         | V <sub>OH2</sub>                          | +2.4                 |                      | V  | I <sub>OH</sub> = 1mA            |  |  |  |

| Voltage (INT)                             | - 082                                     | +3.5                 |                      | V  | I <sub>OH</sub> = 50 μA          |  |  |  |

| Input Leakage Current                     | I <sub>IL</sub>                           | -1                   | +1                   | μA | $V_{IN} = 0V \text{ to } V_{CC}$ |  |  |  |

| Output Leakage Current                    | I <sub>OL</sub>                           | -10                  | +10                  | μA | $V_{OUT} = 0$ to $V_{CC}$        |  |  |  |

| Supply Current                            | I <sub>CC</sub>                           |                      | 2                    | mA | Outputs Open                     |  |  |  |

# **Timing Waveforms**

### **Internal Registers**

The IOT7210 has 16 registers: 8 read and 8 write.

| Register Name                | A | dd | dre | essi | nç | J |      |      |      | Specif | ication |       |       |       |

|------------------------------|---|----|-----|------|----|---|------|------|------|--------|---------|-------|-------|-------|

|                              | R | R  | R   | W    | R  | С |      |      |      |        |         |       |       |       |

|                              | S | S  | S   | R    | D  | S |      |      |      |        |         |       |       |       |

|                              | 2 | 1  | 0   |      |    |   |      |      |      |        |         |       |       |       |

| Data In [OR]                 | 0 | 0  | 0   | 1    | 0  | 0 | DI7  | DI6  | DI5  | DI4    | DI3     | DI2   | DI1   | DIO   |

| Interrupt Status 1 [1R]      | 0 | 0  | 1   | 1    | 0  | 0 | CPT  | APT  | DET  | END    | DEC     | ERR   | DO    | DI    |

| Interrupt Status 2 [2R]      | 0 | 1  | 0   | 1    | 0  | 0 | INT  | SRQI | LOK  | REM    | CO      | LOKC  | REMC  | ADSC  |

| Serial Poll Status [3R]      | 0 | 1  | 1   | 1    | 0  | 0 | S8   | PEND | S6   | S5     | S4      | S3    | S2    | S1    |

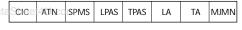

| Address Status [4R]          | 1 | 0  | 0   | 1    | 0  | 0 | CIC  | ĀTN  | SPMS | LPAS   | TPAS    | LA    | TA    | MJMN  |

| Command Pass<br>Through [5R] | 1 | 0  | 1   | 1    | 0  | 0 | CPT7 | CPT6 | CPT5 | CPT4   | CPT3    | CPT2  | CPT1  | СРТО  |

| Address 0 [6R]               | 1 | 1  | 0   | 1    | 0  | 0 | Х    | DT0  | DL0  | AD5-0  | AD4-0   | AD3-0 | AD2-0 | AD1-0 |

| Address 1 [7R]               | 1 | 1  | 1   | 1    | 0  | 0 | EOI  | DT1  | DL1  | AD5-1  | AD4-1   | AD3-1 | AD2-1 | AD1-1 |

|                              |   |    |     |      |    |   |      |      |      |        |         |       |       |       |

| Byte Out [0W]                | 0 | 0  | 0   | 0    | 1  | 0 | BO7  | BO6  | BO5  | BO4    | BO3     | BO2   | BO1   | BO0   |

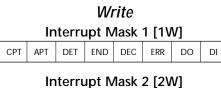

| Interrupt Mask 1 [1W]        | 0 | 0  | 1   | 0    | 1  | 0 | CPT  | APT  | DET  | END    | DEC     | ERR   | DO    | DI    |

| Interrupt Mask 2 [2W]        | 0 | 1  | 0   | 0    | 1  | 0 | 0    | SRQI | DMAO | DMAI   | CO      | LOKC  | REMC  | ADSC  |

| Serial Poll Mode [3W]        | 0 | 1  | 1   | 0    | 1  | 0 | S8   | rsv  | S6   | S5     | S4      | S3    | S2    | S1    |

| Address Mode [4W]            | 1 | 0  | 0   | 0    | 1  | 0 | ton  | lon  | TRM1 | TRM0   | 0       | 0     | ADM1  | ADM0  |

| Auxiliary Mode [5W]          | 1 | 0  | 1   | 0    | 1  | 0 | CNT2 | CNT1 | CNTO | COM4   | COM3    | COM2  | COM1  | COM0  |

| Address 0/1 [6W]             | 1 | 1  | 0   | 0    | 1  | 0 | ARS  | DT   | DL   | AD5    | AD4     | AD3   | AD2   | AD1   |

| End of String [7W]           | 1 | 1  | 1   | 0    | 1  | 0 | EC7  | EC6  | EC5  | EC4    | EC3     | EC2   | EC1   | EC0   |

CPT

## **Data Registers**

The data registers are used for data and command transfers between the IEEE 488 and the computer. The Data In register holds data sent from the IEEE 488 to the computer; the Byte Out register holds information written into it for transfer to the IEEE 488 bus.

|     |     | D   | ata I | n [0F | <b>?</b> ] |     |     |

|-----|-----|-----|-------|-------|------------|-----|-----|

| DI7 | DI6 | DI5 | DI4   | DI3   | DI2        | DI1 | DIO |

|     |     | Ву  | te O | ut [0' | W]  |     |     |

|-----|-----|-----|------|--------|-----|-----|-----|

| BO7 | BO6 | BO5 | BO4  | BO3    | BO2 | BO1 | BO0 |

### Interrupt Registers

The interrupt registers consist of interrupt status bits, interrupt mask bits, and some other non-interrupt bits.

| In  | terru |     | <i>ad</i><br>tatus | 1 [1 | R] |  |

|-----|-------|-----|--------------------|------|----|--|

| APT | DET   | END | DEC                | ERR  | DO |  |

DI

| Interrupt | Status 2 | [2R]  |

|-----------|----------|-------|

| micrupi   | Julius Z | נבוזן |

|     |      |     | -   |    |      | -    |      |

|-----|------|-----|-----|----|------|------|------|

| INT | SRQI | LOK | REM | СО | LOKC | REMC | ADSC |

| 0 SRQI DMAO DMAI CO LOKC REMC ADSC |   |      |      | •    |    | _    | _    |      |

|------------------------------------|---|------|------|------|----|------|------|------|

|                                    | 0 | SRQI | DMAO | DMAI | СО | LOKC | REMC | ADSC |

Thirteen factors can generate an interrupt from the IOT7210, each with its own status bit and mask bit.

The interrupt status bits are always set to 1 if the interrupt condition is met. The interrupt mask bits decide whether or not the INT bit and the interrupt pin will be active for that condition.

Interrupt Status Bits

|      | interrupt otatao Bito                       |

|------|---------------------------------------------|

| INT  | OR of All Unmasked Interrupt<br>Status Bits |

| CPT  | Command Pass Through                        |

| APT  | Address Pass Through                        |

| DET  | Device Trigger                              |

| END  | End (END or EOS Message<br>Received)        |

| DEC  | Device Clear                                |

| ERR  | Error                                       |

| DO   | Data Out                                    |

| DI   | Data In                                     |

| SRQI | Service Request Input                       |

| LOKC | Lockout Change                              |

| REMC | Remote Change                               |

| ADSC | Address Status Change                       |

| CO   | Command Output                              |

|      |                                             |

#### Noninterrupt Related Bits

| LOK  | Lockout                |

|------|------------------------|

| REM  | Remote/Local           |

| DMAO | Enable/Disable DMA Out |

| DMAI | Enable/Disable DMA In  |

### **Serial Poll Registers**

The serial poll mode register holds the STB (status byte: S8, S6-S1) sent over the IEEE 488 bus and the local message rsv (request service). The serial poll mode register may be read through the serial poll status register. The PEND is set by rsv = 1 and cleared by NPRS•rsv = 1 (NPRS = negative poll response state).

|   | Read                    |      |    |    |      |    |    |    |  |

|---|-------------------------|------|----|----|------|----|----|----|--|

|   | Serial Poll Status [3R] |      |    |    |      |    |    |    |  |

|   | S8                      | PEND | S6 | S5 | S4   | S3 | S2 | S1 |  |

| _ |                         |      |    | Wi | rite |    |    |    |  |

| С | Serial Poll Mode [3W]   |      |    |    |      |    |    |    |  |

|   | S8                      | rsv  | S6 | S5 | S4   | S3 | S2 | S1 |  |

### Address Status/Address Mode Registers

The address mode register selects the address mode of the device and also sets the mode for the transceiver control lines,  $T/R_3$  and  $T/R_2$ .

#### Address Status [4R]

#### Address Mode [4W]

ton lon TRM1 TRM0 0 0 AMD1 ADM0

The TRM1 and TRM0 values of the address mode register determine the functions of the  $T/R_2$  and  $T/R_3$  pins.

| T/R <sub>2</sub> | T/R <sub>3</sub> | TRM1 | TRM0 |

|------------------|------------------|------|------|

| EOIOE            | TRIG             | 0    | 0    |

| CIC              | TRIG             | 0    | 1    |

| CIC              | EOIOE            | 1    | 0    |

| CIC              | PE               | 1    | 1    |

EOIOE = TACS + SPAS + CIC • CSBS EOI pin output enable. When 1: output When 0: input

#### $CIC = \overline{CIDS + CADS}$

Controller in charge. When 1:  $\underline{ATN}$  = output,  $\overline{SRO}$  = input When 0:  $\overline{ATN}$  = input, SRO = output

PE = CIC + PPAS

Pull-up enable for DIO<sub>8</sub> - DIO<sub>1</sub> and DAV lines. When 1: Three-state When 0: Open-collector

#### TRIG

Pulses high when DTAS state is initiated or when a trigger auxiliary command is issued.

Upon reset, TRM0 and TRM1 become 0 (TRM0 = TRM1 = 0) so that  $T/R_2$  and  $T/R_3$  both become low.

#### Address Status Bits

| ATN  | Data Transfer Cycle<br>(Device in CSBS)               |

|------|-------------------------------------------------------|

| LPAS | Listener Primary Addressed State                      |

| TPAS | Talker Primary Addressed State                        |

| CIC  | Controller Active                                     |

| LA   | Listener Addressed                                    |

| TA   | Talker Addressed                                      |

| MJMN | Set = Minor T/L Address,<br>Reset = Major T/L Address |

| SPMS | Serial Poll Mode State                                |

|     | Address Modes |      |      |                                |                                                                         |                                                       |  |  |  |

|-----|---------------|------|------|--------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------|--|--|--|

| ton | lon           | ADM1 | ADM0 | Address<br>Mode                | Contents of<br>Address 0<br>Register                                    | Contents of<br>Address 1<br>Register                  |  |  |  |

| 1   | 0             | 0    | 0    | Talk only<br>mode              | Address identification necessary<br>(no controller on the IEEE 488 bus) |                                                       |  |  |  |

| 0   | 1             | 0    | 0    | Listen only<br>mode            | Not used                                                                |                                                       |  |  |  |

| 0   | 0             | 0    | 1    | Address<br>mode 1 <sup>1</sup> | Major talk<br>address or<br>major listen<br>address                     | Minor talk<br>address or<br>minor listen<br>address   |  |  |  |

| 0   | 0             | 1    | 0    | Address<br>mode 2 <sup>2</sup> | Primary<br>address<br>(talk or listen)                                  | Secondary<br>address<br>(talk or listen)              |  |  |  |

| 0   | 0             | 1    | 1    | Address<br>mode 3 <sup>3</sup> | Primary<br>address<br>(major talk or<br>major listen)                   | Primary<br>address<br>(minor talk or<br>minor listen) |  |  |  |

Notes: Combinations other than those indicated are prohibited.

1 Either MTA or MLA reception is indicated by coincidence of either address with the received address; interface function T or L

2 Address register 0 = primary: address register 1 = secondary; interface function TE or LE

3 CPU must read secondary address via Command Pass Through register; interface function (TE or LE)

## **Address Registers**

The IOT7210 is able to automatically detect two addresses that are held in address registers 0 and 1, as specified by the address mode register.

Address 0 [6R]

| х | DT0 | DL0 | AD5-0 | AD4-0 | AD3-0 | AD2-0 | AD1-0 |

|---|-----|-----|-------|-------|-------|-------|-------|

|---|-----|-----|-------|-------|-------|-------|-------|

| Addre | ess 1 | [7R] |

|-------|-------|------|

|       |       |      |

|  | EOI | DT1 | DL1 | AD5-1 | AD4-1 | AD3-1 | AD2-1 | AD1-1 |

|--|-----|-----|-----|-------|-------|-------|-------|-------|

|--|-----|-----|-----|-------|-------|-------|-------|-------|

#### Address 0/1 [6W]

| ARS | DT | DL | AD5 | AD4 | AD3 | AD2 | AD1 |

|-----|----|----|-----|-----|-----|-----|-----|

|-----|----|----|-----|-----|-----|-----|-----|

The addresses are set by writing into the address 0/1 register.

#### Address 0/1 Register Bit Selections

| ARS                              | Selects either address register<br>0 or 1             |

|----------------------------------|-------------------------------------------------------|

| DT                               | Permits or prohibits address to be detected as Talk   |

| DL                               | Permits or prohibits address to be detected as Listen |

| AD <sub>5</sub> -AD <sub>1</sub> | Device address value                                  |

| EOI                              | Holds the value of EOI line when data is received     |

### Command Pass Through Register

The CPT register enables the CPU to read the DIO lines in the cases of undefined command, secondary address, or parallel poll response.

#### Command Pass Through [5R]

### **End of String Register**

This register holds either a 7- or 8- bit EOS message byte used in the IEEE 488 system to detect the end of a data block. Auxiliary Mode register A controls the specific use of this register.

|          | End of String [7W] |     |     |     |     |     |     |     |

|----------|--------------------|-----|-----|-----|-----|-----|-----|-----|

| www.Data | EC7                | EC6 | EC5 | EC4 | EC3 | EC2 | EC1 | EC0 |

### Auxiliary Mode Register

This is a multipurpose register.

#### Auxiliary Mode [5W]

CNT2 CNT1 CNT0 COM4 C0M3 COM2 COM1 COM0

A write to this register generates one of the following operations according to the values of the CNT bits.

| С | N | Т |                | С              | ON             | 1              |                | Function                                                                          |

|---|---|---|----------------|----------------|----------------|----------------|----------------|-----------------------------------------------------------------------------------|

| 2 | 1 | 0 | 4              | 3              | 2              | 1              | 0              | runction                                                                          |

| 0 | 0 | 0 | C <sub>4</sub> |                | C <sub>2</sub> | C <sub>1</sub> | C <sub>0</sub> | Issues an auxiliary command specified by $C_4$ to $C_0$                           |

| 0 | 0 | 1 | 0              | F <sub>3</sub> | F <sub>2</sub> | F <sub>1</sub> | Fo             | The reference<br>clock frequency<br>determines $T_1$ , $T_6$ ,<br>$T_7$ , & $T_9$ |

| 0 | 1 | 1 | U              | S              | Р <sub>3</sub> | P <sub>2</sub> | P <sub>1</sub> | Sets the parallel poll register                                                   |

| 1 | 0 | 0 | A <sub>4</sub> | А <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> | Sets the auxiliary A register                                                     |

| 1 | 0 | 1 | В <sub>4</sub> | B <sub>3</sub> | В <sub>2</sub> | В <sub>1</sub> | B <sub>0</sub> | Sets the auxiliary B register                                                     |

| 1 | 1 | 0 | 0              | 0              | 0              | E <sub>1</sub> | Ε <sub>Ο</sub> | Sets the auxiliary E register                                                     |

#### **Auxiliary Commands**

#### Auxiliary Commands

|   |   |   | -              |    |                |                |                |

|---|---|---|----------------|----|----------------|----------------|----------------|

| 0 | 0 | 0 | C <sub>4</sub> | C3 | C <sub>2</sub> | C <sub>1</sub> | C <sub>0</sub> |

|   |   |   |                |    |                |                |                |

|   |   | nm<br>C <sub>2</sub> |   | - | Aux<br>Comm | Function                                                        |

|---|---|----------------------|---|---|-------------|-----------------------------------------------------------------|

| 0 | 0 | 0                    | 0 | 0 | iepon       | Immediate Execute<br>pon, Generate Local<br>pon message         |

| 0 | 0 | 0                    | 1 | 0 | crst        | Chip Reset (Same as<br>External Reset)                          |

| 0 | 0 | 0                    | 1 | 1 | rrfd        | Release RFD                                                     |

| 0 | 0 | 1                    | 0 | 0 | trig        | Trigger                                                         |

| 0 | 0 | 1                    | 0 | 1 | rtl         | Return to Local                                                 |

| 0 | 0 | 1                    | 1 | 0 | seoi        | Send EOI message                                                |

| 0 | 0 | 1                    | 1 | 1 | nvld        | Nonvalid (OSA<br>Reception), Release<br>DAC Holdoff             |

| 0 | 1 | 1                    | 1 | 1 | vld         | Valid (MSA Reception,<br>CPT, DEC, DET),<br>Release DAC Holdoff |

| 0 | Х | 0                    | 0 | 1 | sppf        | Set/Reset Parallel<br>Poll Flag                                 |

| 1 | 0 | 0                    | 0 | 0 | gts         | Go To Standby                                                   |

| 1 | 0 | 0                    | 0 | 1 | tca         | Take Control<br>Asynchronously                                  |

| 1 | 0 | 0                    | 1 | 0 | tcs         | Take Control<br>Synchronously                                   |

| 1 | 1 | 0                    | 1 | 0 | tcse        | Take Control<br>Synchronously<br>on End                         |

| 1 | 0 | 0                    | 1 | 1 | ltn         | Listen                                                          |

| 1 | 1 | 0                    | 1 | 1 | Itnc        | Listen with<br>Continuous Mode                                  |

| 1 | 1 | 1                    | 0 | 0 | lun         | Local Unlisten                                                  |

| 1 | 1 | 1                    | 0 | 1 | epp         | Execute Parallel Poll                                           |

| 1 | Χ | 1                    | 1 | 0 | sifc        | Set/Reset IFC                                                   |

| 1 | Х | 1                    | 1 | 1 | sren        | Set/Reset REN                                                   |

| 1 | 0 | 1                    | 0 | 0 | dsc         | Disable System<br>Control                                       |

### **Auxiliary A Register**

Of the 5 bits that may be specified as part of its access word, two bits control the IEEE 488 data receiving modes of the IOT7210 and 3 bits control how the EOS message is used.

#### **Auxiliary A Register**

| 1 | 0 | 0 | $A_4$ | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> |

|---|---|---|-------|----------------|----------------|----------------|----------------|

|   |   |   |       |                |                |                |                |

| A <sub>1</sub> | A <sub>0</sub>         | C                 | Data Receiving Mode                                                                                                                   |  |  |  |  |  |

|----------------|------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 0              | 0                      | No                | Normal Handshake Mode                                                                                                                 |  |  |  |  |  |

| 0              | 1                      |                   | RFD Holdoff on All Data<br>Modes                                                                                                      |  |  |  |  |  |

| 1              | 0                      | RF                | D Holdoff on End Mode                                                                                                                 |  |  |  |  |  |

| 1              | 1                      | Co                | ntinuous Mode                                                                                                                         |  |  |  |  |  |

|                |                        |                   |                                                                                                                                       |  |  |  |  |  |

| A <sub>2</sub> | 0 Proh<br>1 Peri       | nibit<br>mit      | Permits (prohibits) the<br>setting of the END bit by<br>reception of the EOS<br>message                                               |  |  |  |  |  |

| A <sub>3</sub> | 0 Prohibit<br>1 Permit |                   | Permits (prohibits)<br>automatic transmission<br>of END message simul-<br>taneously with the<br>transmission of EOS<br>message (TACS) |  |  |  |  |  |

| A <sub>1</sub> | 07-bit<br>08-bit       | <u>EOS</u><br>EOS | Makes the 8 bits (7 bits)<br>of the EOS register the<br>valid EOS message                                                             |  |  |  |  |  |

#### Internal Counter

The internal counter generates the state change prohibit times  $(T_1, T_6, T_7, T_9)$  specified in the IEEE Standard 488-1978 with reference to the clock frequency.  $F_3$ - $F_0$  specify the clock frequency from 1 to 8 MHz.

#### **Internal Counter**

| 0 | 0 | 1 | 0 | F <sub>3</sub> | $F_2$ | F <sub>1</sub> | F <sub>0</sub> |

|---|---|---|---|----------------|-------|----------------|----------------|

|---|---|---|---|----------------|-------|----------------|----------------|

#### **Auxiliary BRegister**

The auxiliary B register is much like the A register in that it controls the special operating features of the device.

#### **Auxiliary B Register**

| 1                | 0                                | 1                         | $B_4$          | B <sub>3</sub>                                                                                           | B <sub>2</sub>                                 | B <sub>1</sub>                       | B <sub>0</sub>    |  |

|------------------|----------------------------------|---------------------------|----------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------|--------------------------------------|-------------------|--|

| a <sub>b</sub> a |                                  | ermit<br>ohibit           | setti<br>rece  | Permits (prohibits) the<br>setting of the CPT bit on<br>receipt of an undefined<br>command               |                                                |                                      |                   |  |

| B <sub>1</sub>   |                                  | ermit<br>ohibit           | tran<br>mes    | Permits (prohibits) the<br>transmission of the END<br>message when in serial poll<br>active state (SPAS) |                                                |                                      |                   |  |

| B                |                                  | igh-<br>eed)              | function of se | tion a                                                                                                   | ce har<br>fter tra<br>byte i<br>missic         | ansmi:<br>follow                     | ssion             |  |

| B <sub>2</sub>   | 1 T <sub>1</sub> (low-<br>speed) |                           | Sets           | Sets T <sub>1</sub> in all cases                                                                         |                                                |                                      |                   |  |

| B <sub>3</sub>   | <u>1</u><br>0                    | INT<br>INT                |                | cifies t<br>INT pi                                                                                       | he act<br>in                                   | ive lev                              | vel of            |  |

| B <sub>4</sub>   | 1 <i>is</i><br>S                 | st =<br>RQS               | the<br>(the    | ist leve<br>value<br>flag is<br>SRQS                                                                     | cates t<br>el loca<br>of the<br>s ignor<br>= 1 | il mes<br>e para<br>red)<br>.ist = 1 | sage<br>llel<br>I |  |

| 4                |                                  | f =<br>Irallel<br>II Flag | poll           |                                                                                                          | of the<br>taker<br>sage                        |                                      |                   |  |

### **Auxiliary E Register**

The register controls the IOT7210's Data Acceptance modes.

Auxiliary E Register

| 1              | 1 | 0                 | 0 | 0              | 0      | E <sub>1</sub> | Ε <sub>Ο</sub> |

|----------------|---|-------------------|---|----------------|--------|----------------|----------------|

|                |   |                   |   |                |        |                |                |

| E <sub>O</sub> |   | Enable<br>Disable |   | C hold<br>DCAS | doff b | y initi        | ation          |

| E <sub>1</sub> |   | Enable<br>Disable |   | C hold<br>DTAS | doff b | y initi        | ation          |

#### **Parallel Poll Register**

The Parallel Poll register defines the IOT7210's parallel poll response.

#### **Parallel Poll Register**

|   |   |   |   |   | -              |                |                |

|---|---|---|---|---|----------------|----------------|----------------|

| 0 | 1 | 1 | U | S | P <sub>3</sub> | Ρ <sub>2</sub> | Р <sub>1</sub> |

| U              | 1 = No Parallel Poll Response<br>0 = Parallel Poll Response             |

|----------------|-------------------------------------------------------------------------|

| S              | Specify Status Bit Polarity<br>1 = In Phase<br>0 = Reverse Phase        |

| P <sub>3</sub> |                                                                         |

| P <sub>2</sub> | Specify Status Bit Output Line<br>(DIO <sub>1</sub> -DIO <sub>8</sub> ) |

| P <sub>1</sub> | (2.012.08)                                                              |

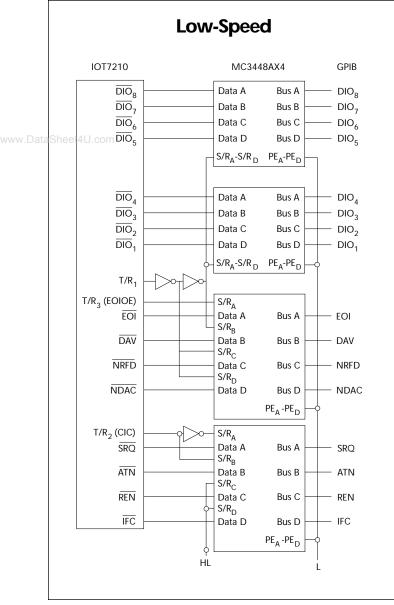

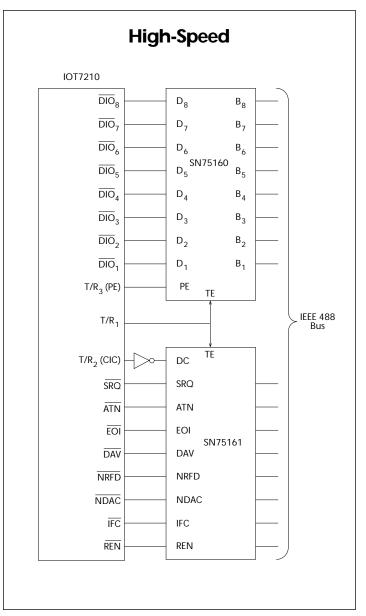

# **IEEE 488 Transceiver Examples**

In this example, a high-speed data transfer cannot be made since the bus transceiver is of the open-collector type (set  $B_2 = 0$ )

In the case of low-speed data transfer ( $B_2 = 0$ ), the  $TR_3$  pin can be used as a TRIG output; the PE input of SN75160 should be cleared to 0

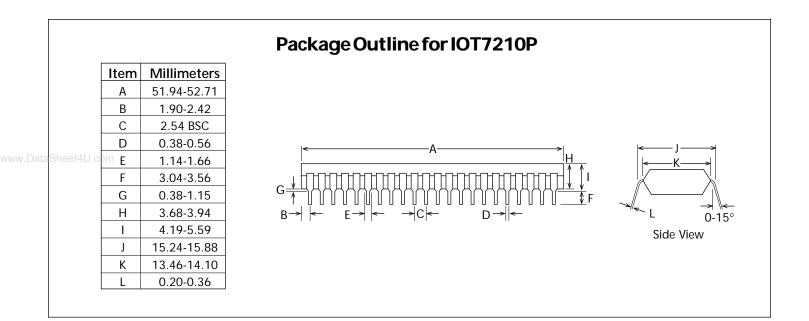

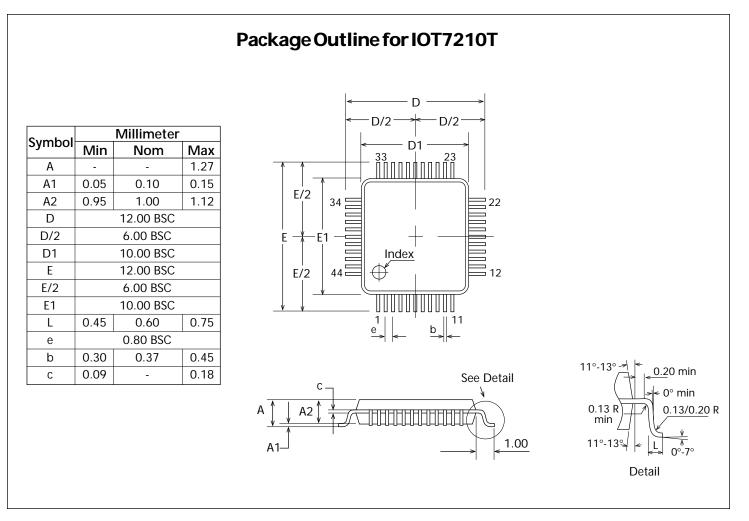

# Package Outlines

# Ordering Information

# **Ordering Information**

| Description                               | Part No. |

|-------------------------------------------|----------|

| Low-power CMOS IEEE 488 controller device |          |

| in a 40-pin plastic DIP                   | IOT7210P |

| Low-power CMOS IEEE 488 controller device |          |

| in a 44-pin plastic TQFP                  | IOT7210T |

|                                           |          |

ww.DataSheet4U.com

Printed in the U.S.A.