# DS31256DK 256-Channel, High-Throughput HDLC Controller Demonstration Kit

### www.maxim-ic.com

#### **GENERAL DESCRIPTION**

The DS31256DK is a demonstration and evaluation kit for the DS31256 Envoy 256-channel, high-throughput HDLC controller. The DS31256DK board is a PCI-based platform that offers quick and easy evaluation of the DS31256 HDLC controller, low-cost prototyping, and rapid software development. The DS31256DK operates with a software suite that runs under Microsoft Windows®95/98/NT. The PC platform must be at least a 200MHz+ Pentium II class CPU with 32MB of RAM.

Windows is a registered trademark of Microsoft Corp.

#### ORDERING INFORMATION

| PART    | DESCRIPTION       |  |

|---------|-------------------|--|

| DS31256 | Demonstration Kit |  |

### **FEATURES**

- Headers Provide Access to Clock, Sync, and Data for 16 Physical Ports

- Full Source Code

- Windows/Windows NT GUI for Device Configuration and Evaluation

- Programmable PLD for Port Connectivity and Clock Generation

- Local Bus Header for Control and Configuration of External Devices

- Hardware Prototyping Area

### **DEMO KIT CONTENTS**

**CD-ROM Includes:**

HDLC Application Notes

DS31256DK Data Sheet/Manual

Installation Guide

DS31256 Data Sheet

Executable Evaluation Application

Source Code for Driver and GUI Application

1 of 31 REV: 052703

## **TABLE OF CONTENTS**

| 1. |     | GENE  | ERAL OVERVIEW                     | 3    |

|----|-----|-------|-----------------------------------|------|

| 2. | 5   | SOF1  | TWARE                             | . 10 |

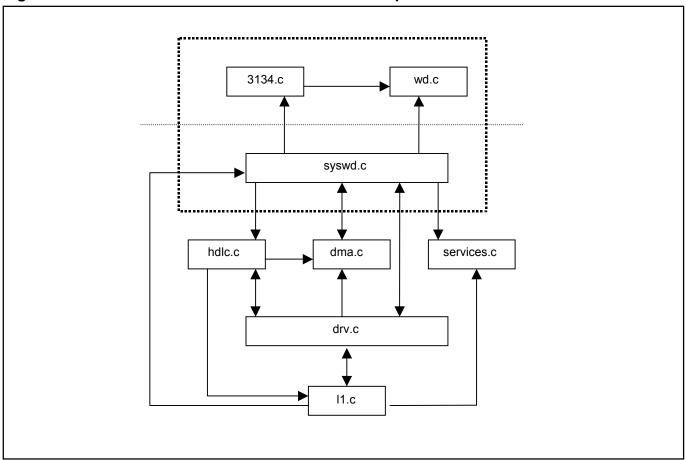

| 2  | 2.1 | ARG   | CHITECTURE                        | . 10 |

| 2  | 2.2 | Inti  | RODUCTION TO CHAT                 | . 10 |

| 2  | 2.3 | Сни   | AT GUI                            | . 11 |

|    | 2.3 | 3.1   | Main GUI Interface—Configuration. | . 11 |

|    | 2.3 | 3.2   | Show Results                      | . 17 |

|    | 2.3 | 3.3   | Memory Viewer                     | . 19 |

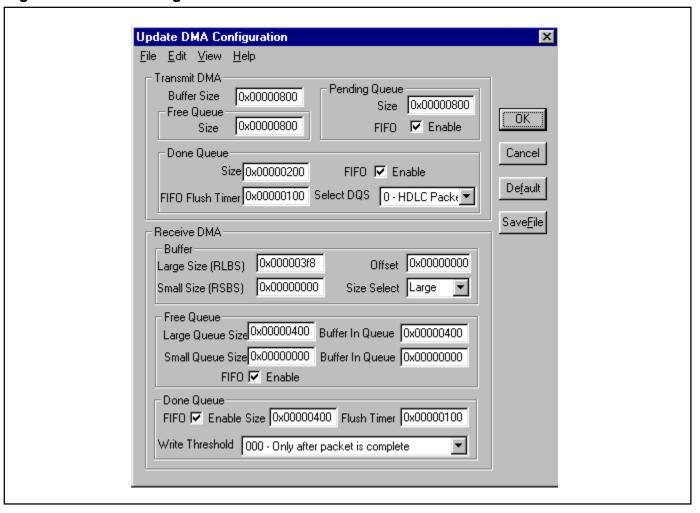

|    | 2.3 | 3.4   | DMA Configuration                 | . 20 |

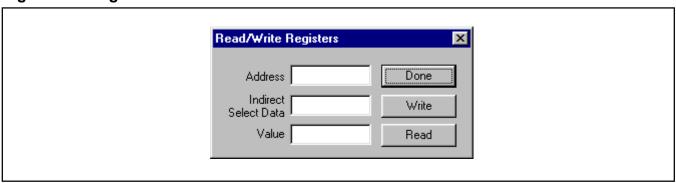

|    | 2.3 | 3.5   | Register Access                   | . 21 |

| 2  | 2.4 | DRI   | VER                               | . 22 |

| 3. | I   | NST   | ALLATION AND GETTING STARTED      | . 23 |

| 3  | 3.1 | CAF   | RD INSTALLATION                   | . 23 |

|    | 3.1 | 1.1   | Windows 95 Systems                | . 23 |

|    | 3.1 | 1.2   | Windows 98 Systems                | . 23 |

|    | 3.1 | 1.3   | Windows NT Systems                | . 24 |

| 3  | 3.2 | Sor   | TWARE INSTALLATION                | . 24 |

| 3  | 3.3 | ОРІ   | ERATIONAL TEST                    | . 24 |

| 1  |     | \ DDF | ENDLY A                           | 25   |

# **LIST OF FIGURES**

| Figure 1-1. PCI Card Configuration                   | 5  |

|------------------------------------------------------|----|

| Figure 1-2. Port PLD Schematic                       | 6  |

| Figure 2-1. Software Architecture                    | 10 |

| Figure 2-2. Software Main GUI                        | 11 |

| Figure 2-3. Show Results GUI                         | 17 |

| Figure 2-4. Memory Viewer GUI                        | 19 |

| Figure 2-5. DMA Configuration GUI                    | 20 |

| Figure 2-6. Registers Access GUI                     | 21 |

| Figure 2-7. Low-Level API Source Block Relationships | 22 |

| LIST OF TABLES                                       |    |

| Table 1-A. Header A Definition                       | 7  |

| Table 1-B. Header B Definition                       | 8  |

| Table 1-C. Header C Definition                       | 9  |

| Table 2-A Low-Level API Source Block Contents        | 22 |

#### 1. GENERAL OVERVIEW

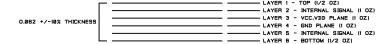

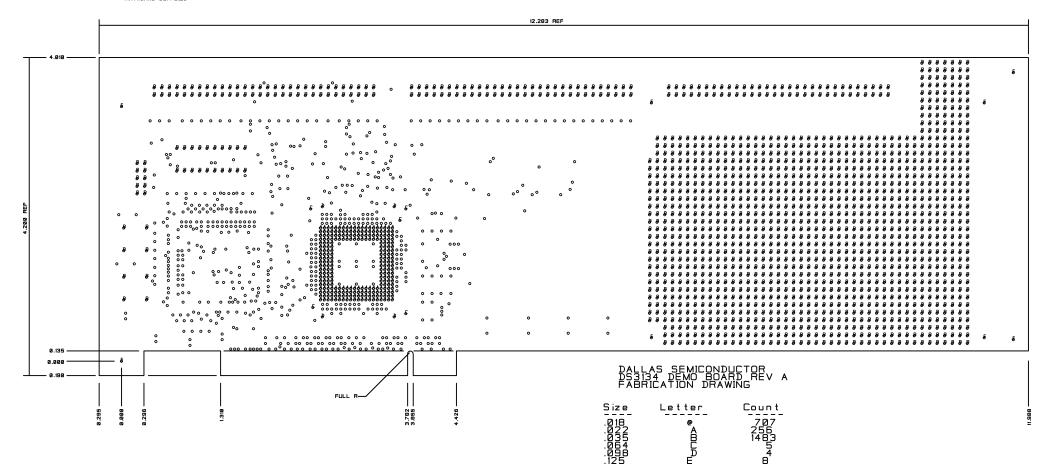

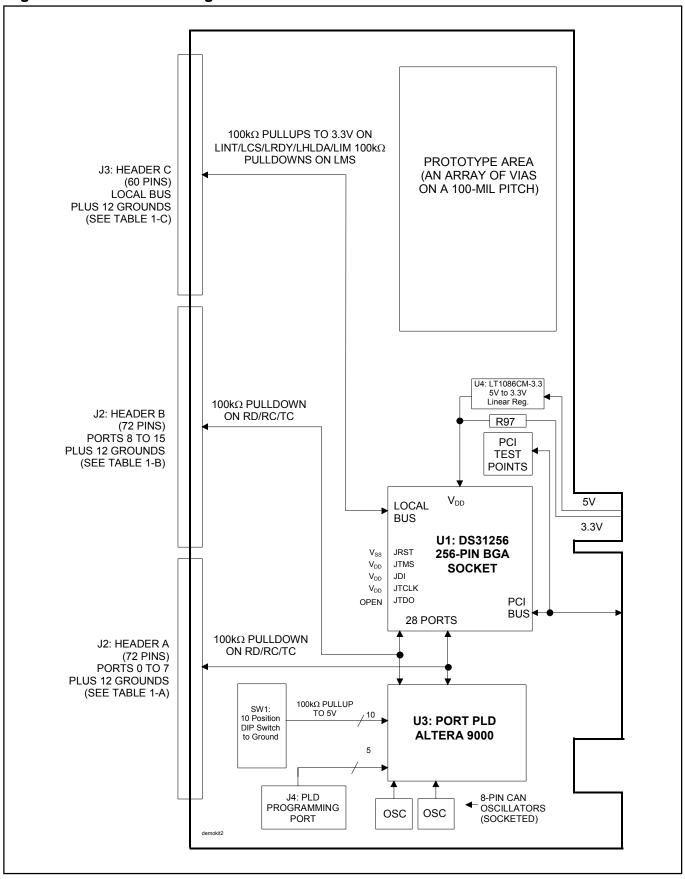

The DS31256DK is a demonstration and evaluation kit for the DS31256 Envoy 256-channel, high-throughput HDLC controller. The DS31256DK is intended to be used in a full-size PC platform, complete with PCI. The DS31256DK operates with a software suite that runs under Microsoft Windows 95/98/NT. The PC platform must be at least a 200MHz+ Pentium II class CPU with 32MB of RAM. <u>Figure 1-1</u> details an outline of the PCI board for the DS31256DK.

The DS31256DK was designed to be as simple as possible but offers the flexibility to be used in a number of different configurations. The DS31256DK has all the DS31256's port and local bus pins, which are easily accessible through headers on top of the card. A second DS31256DK can also be loaded into the PC in an adjacent PCI slot to add additional functions such as:

- Multiple T1/E1 framers

- T3 line interface

- HSSI interface

- V.35 interfaces

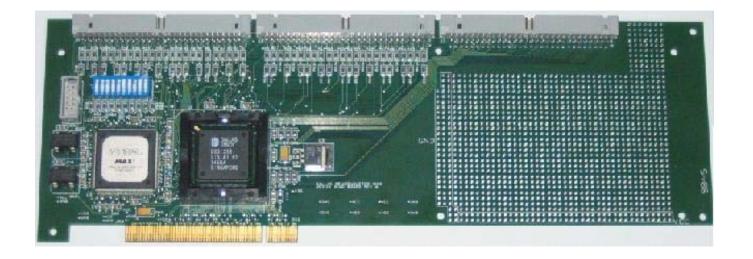

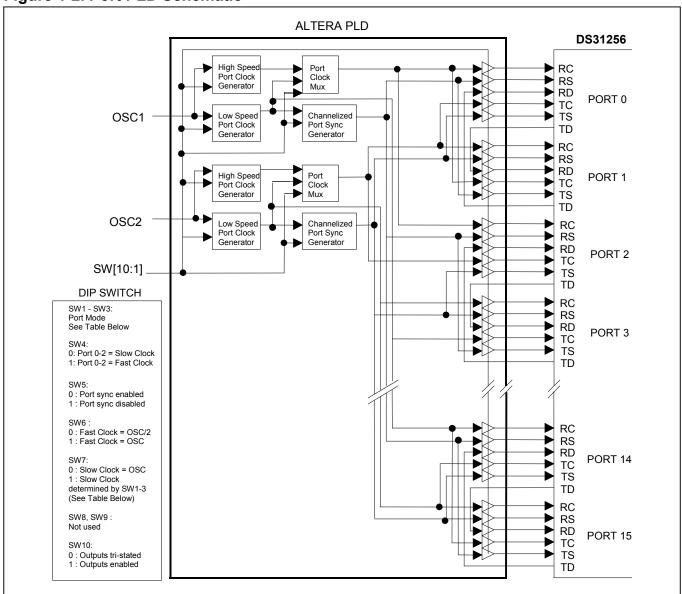

An Altera 9000 series PLD device is connected to all port pins on the DS31256. The PLD can be loaded with various configurations through a programming port (J4) that resides on the DS31256DK. This PLD generates clocks and frame syncs as well as routes data from one port to another in a daisy-chain fashion to allow testing the device under worst-case loading (Figure 1-2). Two oscillators provide the port timing.

The transmit side of a port is derived from one clock and the receive side from another, so that they can be asynchronous to one another. If the PLD is not needed, it can be tri-stated to remove it (electrically) from the board. Signals can then be sent to the DS31256 by the pin headers.

The board is intended to be a full-size PCI card that can only be plugged into a 5V PCI system environment. There is a 256-pin plastic BGA socket on the board for the DS31256.

Only the DS31256 operates at 3.3V. Since it cannot be guaranteed that a 3.3V supply exists in a 5V PCI system environment, the DS31256DK has a linear regulator on it (U4: LT1086) to convert from 5V to 3.3V. All of the other logic, including the PLD and oscillators, operate at 5V. If 3.3V exists on the PCI bus, the linear regulator can be removed and a  $0\Omega$  jumper can be installed at R97 (Figure 1-1).

The JTAG pins on the DS31256 are not active on the DS31256DK. Therefore, the JTCLK, JTDI, and JTMS signals are wired to 3.3V and JTRST is wired low.

Figure 1-1. PCI Card Configuration

Figure 1-2. Port PLD Schematic

### **Clock/Sync Definitions**

| SW7 | SW3 | SW2 | SW1 | MODE                       | SLOW PORT CLOCK        |

|-----|-----|-----|-----|----------------------------|------------------------|

| 0   | 0   | 0   | 0   | Unchannelized (sync = low) | OSC                    |

| 0   | 0   | 0   | 1   | 4 T1/E1 (sync active)      | OSC                    |

| 0   | 0   | 1   | 0   | 2 T1/E1 (sync active)      | OSC                    |

| 0   | 0   | 1   | 1   | E1 (sync active)           | OSC                    |

| 0   | 1   | 0   | 0   | T1 (sync active)           | OSC                    |

| 1   | 0   | 0   | 0   | Unchannelized (sync = low) | 66MHz / 6 = 11MHz      |

| 1   | 0   | 0   | 1   | 4 T1/E1 (sync active)      | 66MHz / 8 = 8.25MHz    |

| 1   | 0   | 1   | 0   | 2 T1/E1 (sync active)      | 66MHz / 16 = 4.125MHz  |

| 1   | 0   | 1   | 1   | E1 (sync active)           | 66MHz / 32 = 2.0625MHz |

| 1   | 1   | 0   | 0   | T1 (sync active)           | 66MHz / 42 = 1.572MHz  |

| Х   | 1   | 0   | 1   | Clock off (sync = low)     | Clock driven low       |

| Χ   | 1   | 1   | Χ   | Clock off (sync = low)     | Clock driven low       |

Note 1: Switch Open = Off = High (1).

**Note 2:** Switch Closed = On = Low (0).

Note 3: OSC1 and OSC2 are recommended to be the same frequency.

Note 4: The frequency of OSC1 and OSC2 supplied with the DK board is 66MHz.

Table 1-A. Header A Definition

| 1              | RS0        | 2              | TS0                                           |

|----------------|------------|----------------|-----------------------------------------------|

| 3<br>5         | RD0        | 4              | TD0                                           |

| 5              | RC0        | 6              | TC0                                           |

| 7              | GND        | 8              | GND                                           |

| 9              | RS1        | 10             | TS1<br>TD1                                    |

| 11             | RD1        | 12             | TD1                                           |

| 13             | RC1        | 12<br>14       | TC1                                           |

| 15             | GND        | 16             | GND                                           |

| 17             | RS2        | 18             | TS2                                           |

| 19             | RD2        | 20<br>22<br>24 | TS2<br>TD2                                    |

| 21             | RC2<br>GND | 22             | TC2                                           |

| 23             | GND        | 24             | GND                                           |

| 21<br>23<br>25 | DC3        | 26             | TS3                                           |

| 27<br>29<br>31 | RD3<br>RC3 | 28             | TD3                                           |

| 29             | RC3        | 30             | TC3                                           |

| 31             | RS4        | 32             | TS4                                           |

| 33             | RS4<br>RD4 | 34             | TC2<br>GND<br>TS3<br>TD3<br>TC3<br>TS4<br>TD4 |

| 35             | RC4        | 36             | TC4<br>GND                                    |

| 37             | GND        | 38             | GND                                           |

| 39             | RS5        | 40             | TS5<br>TD5                                    |

| 41             | RD5        | 42             | TD5                                           |

| 43             | RC5        | 44             | TC5                                           |

| 45             | GND        | 46             | GND                                           |

| 47             | RS6        | 48             | TS6                                           |

| 49             | RD6        | 50             | TS6<br>TD6                                    |

| 51             | RC6        | 52             | TC6                                           |

| 53             | GND        | 54             | GND                                           |

| 55             | RS7        | 56             | TS7                                           |

| 57             | RD7        | 58             | TS7<br>TD7                                    |

| 59             | RC7        | 60             | TC7                                           |

|                |            |                |                                               |

Table 1-B. Header B Definition

| 1         RS8         2         TS8           3         RD8         4         TD8           5         RC8         6         TC8           7         GND         8         GND           9         RS9         10         TS9           11         RD9         12         TD9           13         RC9         14         TC9           15         GND         16         GND           17         RS10         18         TS10           19         RD10         20         TD10           21         RC10         22         TC10           23         GND         24         GND           25         RS11         26         TS11           27         RD11         28         TD11           29         RC11         30         TC11           31         RS12         32         TS12           33         RD12         34         TD12           35         RC12         36         TC12           37         GND         38         GND           39         RS13         40         TS13                                                                        |    |      |    |      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------|----|------|

| 5         RC8         6         TC8           7         GND         8         GND           9         RS9         10         TS9           11         RD9         12         TD9           13         RC9         14         TC9           15         GND         16         GND           17         RS10         18         TS10           19         RD10         20         TD10           21         RC10         22         TC10           23         GND         24         GND           25         RS11         26         TS11           27         RD11         28         TD11           29         RC11         30         TC11           31         RS12         32         TS12           33         RD12         34         TD12           35         RC12         36         TC12           37         GND         38         GND           39         RS13         40         TS13           41         RD13         42         TD13           43         RC13         44         TC13      <                                                         |    | RS8  | 2  | TS8  |

| 9         RS9         10         TS9           11         RD9         12         TD9           13         RC9         14         TC9           15         GND         16         GND           17         RS10         18         TS10           19         RD10         20         TD10           21         RC10         22         TC10           23         GND         24         GND           25         RS11         26         TS11           27         RD11         28         TD11           29         RC11         30         TC11           31         RS12         32         TS12           33         RD12         34         TD12           35         RC12         36         TC12           37         GND         38         GND           39         RS13         40         TS13           41         RD13         42         TD13           43         RC13         44         TC13           45         GND         46         GND           47         RS14         48         TS14                                                          | 3  |      |    | TD8  |

| 9         RS9         10         TS9           11         RD9         12         TD9           13         RC9         14         TC9           15         GND         16         GND           17         RS10         18         TS10           19         RD10         20         TD10           21         RC10         22         TC10           23         GND         24         GND           25         RS11         26         TS11           27         RD11         28         TD11           29         RC11         30         TC11           31         RS12         32         TS12           33         RD12         34         TD12           35         RC12         36         TC12           37         GND         38         GND           39         RS13         40         TS13           41         RD13         42         TD13           43         RC13         44         TC13           45         GND         46         GND           47         RS14         48         TS14                                                          | 5  | RC8  |    | TC8  |

| 11         RD9         12         TD9           13         RC9         14         TC9           15         GND         16         GND           17         RS10         18         TS10           19         RD10         20         TD10           21         RC10         22         TC10           23         GND         24         GND           25         RS11         26         TS11           27         RD11         28         TD11           29         RC11         30         TC11           31         RS12         32         TS12           33         RD12         34         TD12           35         RC12         36         TC12           37         GND         38         GND           39         RS13         40         TS13           41         RD13         42         TD13           43         RC13         44         TC13           45         GND         46         GND           47         RS14         48         TS14           49         RD14         50         TD14 </td <td>7</td> <td>GND</td> <td></td> <td>GND</td>   | 7  | GND  |    | GND  |

| 11         RD9         12         TD9           13         RC9         14         TC9           15         GND         16         GND           17         RS10         18         TS10           19         RD10         20         TD10           21         RC10         22         TC10           23         GND         24         GND           25         RS11         26         TS11           27         RD11         28         TD11           29         RC11         30         TC11           31         RS12         32         TS12           33         RD12         34         TD12           35         RC12         36         TC12           37         GND         38         GND           39         RS13         40         TS13           41         RD13         42         TD13           43         RC13         44         TC13           45         GND         46         GND           47         RS14         48         TS14           49         RD14         50         TD14 </td <td>9</td> <td>RS9</td> <td>10</td> <td>TS9</td> | 9  | RS9  | 10 | TS9  |

| 15         GND         16         GND           17         RS10         18         TS10           19         RD10         20         TD10           21         RC10         22         TC10           23         GND         24         GND           25         RS11         26         TS11           27         RD11         28         TD11           29         RC11         30         TC11           31         RS12         32         TS12           33         RD12         34         TD12           35         RC12         36         TC12           37         GND         38         GND           39         RS13         40         TS13           41         RD13         42         TD13           43         RC13         44         TC13           45         GND         46         GND           47         RS14         48         TS14           49         RD14         50         TD14           51         RC14         52         TC14           53         GND         54         GND                                                     | 11 |      | 12 | TD9  |

| 15         GND         16         GND           17         RS10         18         TS10           19         RD10         20         TD10           21         RC10         22         TC10           23         GND         24         GND           25         RS11         26         TS11           27         RD11         28         TD11           29         RC11         30         TC11           31         RS12         32         TS12           33         RD12         34         TD12           35         RC12         36         TC12           37         GND         38         GND           39         RS13         40         TS13           41         RD13         42         TD13           43         RC13         44         TC13           45         GND         46         GND           47         RS14         48         TS14           49         RD14         50         TD14           51         RC14         52         TC14           53         GND         54         GND                                                     | 13 | RC9  |    | TC9  |

| 19         RD10         20         TD10           21         RC10         22         TC10           23         GND         24         GND           25         RS11         26         TS11           27         RD11         28         TD11           29         RC11         30         TC11           31         RS12         32         TS12           33         RD12         34         TD12           35         RC12         36         TC12           37         GND         38         GND           39         RS13         40         TS13           41         RD13         42         TD13           43         RC13         44         TC13           45         GND         46         GND           47         RS14         48         TS14           49         RD14         50         TD14           51         RC14         52         TC14           53         GND         54         GND           55         RS15         56         TS15           57         RD15         58         TD15                                                   | 15 | GND  | 16 | GND  |

| 21         RC10         22         TC10           23         GND         24         GND           25         RS11         26         TS11           27         RD11         28         TD11           29         RC11         30         TC11           31         RS12         32         TS12           33         RD12         34         TD12           35         RC12         36         TC12           37         GND         38         GND           39         RS13         40         TS13           41         RD13         42         TD13           43         RC13         44         TC13           45         GND         46         GND           47         RS14         48         TS14           49         RD14         50         TD14           51         RC14         52         TC14           53         GND         54         GND           55         RS15         56         TS15           57         RD15         58         TD15                                                                                                     |    |      | 18 | TS10 |

| 23         GND         24         GND           25         RS11         26         TS11           27         RD11         28         TD11           29         RC11         30         TC11           31         RS12         32         TS12           33         RD12         34         TD12           35         RC12         36         TC12           37         GND         38         GND           39         RS13         40         TS13           41         RD13         42         TD13           43         RC13         44         TC13           45         GND         46         GND           47         RS14         48         TS14           49         RD14         50         TD14           51         RC14         52         TC14           53         GND         54         GND           55         RS15         56         TS15           57         RD15         58         TD15                                                                                                                                                       | 19 | RD10 | 20 | TD10 |

| 25         RS11         26         TS11           27         RD11         28         TD11           29         RC11         30         TC11           31         RS12         32         TS12           33         RD12         34         TD12           35         RC12         36         TC12           37         GND         38         GND           39         RS13         40         TS13           41         RD13         42         TD13           43         RC13         44         TC13           45         GND         46         GND           47         RS14         48         TS14           49         RD14         50         TD14           51         RC14         52         TC14           53         GND         54         GND           55         RS15         56         TS15           57         RD15         58         TD15                                                                                                                                                                                                       | 21 | RC10 | 22 |      |

| 25         RS11         26         TS11           27         RD11         28         TD11           29         RC11         30         TC11           31         RS12         32         TS12           33         RD12         34         TD12           35         RC12         36         TC12           37         GND         38         GND           39         RS13         40         TS13           41         RD13         42         TD13           43         RC13         44         TC13           45         GND         46         GND           47         RS14         48         TS14           49         RD14         50         TD14           51         RC14         52         TC14           53         GND         54         GND           55         RS15         56         TS15           57         RD15         58         TD15                                                                                                                                                                                                       | 23 | GND  | 24 | GND  |

| 29         RC11         30         TC11           31         RS12         32         TS12           33         RD12         34         TD12           35         RC12         36         TC12           37         GND         38         GND           39         RS13         40         TS13           41         RD13         42         TD13           43         RC13         44         TC13           45         GND         46         GND           47         RS14         48         TS14           49         RD14         50         TD14           51         RC14         52         TC14           53         GND         54         GND           55         RS15         56         TS15           57         RD15         58         TD15                                                                                                                                                                                                                                                                                                           |    | RS11 | 26 | TS11 |

| 29         RC11         30         TC11           31         RS12         32         TS12           33         RD12         34         TD12           35         RC12         36         TC12           37         GND         38         GND           39         RS13         40         TS13           41         RD13         42         TD13           43         RC13         44         TC13           45         GND         46         GND           47         RS14         48         TS14           49         RD14         50         TD14           51         RC14         52         TC14           53         GND         54         GND           55         RS15         56         TS15           57         RD15         58         TD15                                                                                                                                                                                                                                                                                                           | 27 | RD11 | 28 | TD11 |

| 33         RD12         34         TD12           35         RC12         36         TC12           37         GND         38         GND           39         RS13         40         TS13           41         RD13         42         TD13           43         RC13         44         TC13           45         GND         46         GND           47         RS14         48         TS14           49         RD14         50         TD14           51         RC14         52         TC14           53         GND         54         GND           55         RS15         56         TS15           57         RD15         58         TD15                                                                                                                                                                                                                                                                                                                                                                                                               | 29 | RC11 | 30 |      |

| 35         RC12         36         TC12           37         GND         38         GND           39         RS13         40         TS13           41         RD13         42         TD13           43         RC13         44         TC13           45         GND         46         GND           47         RS14         48         TS14           49         RD14         50         TD14           51         RC14         52         TC14           53         GND         54         GND           55         RS15         56         TS15           57         RD15         58         TD15                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |      | 32 | TS12 |

| 37         GND         38         GND           39         RS13         40         TS13           41         RD13         42         TD13           43         RC13         44         TC13           45         GND         46         GND           47         RS14         48         TS14           49         RD14         50         TD14           51         RC14         52         TC14           53         GND         54         GND           55         RS15         56         TS15           57         RD15         58         TD15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 33 |      |    | TD12 |

| 39         RS13         40         TS13           41         RD13         42         TD13           43         RC13         44         TC13           45         GND         46         GND           47         RS14         48         TS14           49         RD14         50         TD14           51         RC14         52         TC14           53         GND         54         GND           55         RS15         56         TS15           57         RD15         58         TD15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |      | 36 | TC12 |

| 41       RD13       42       TD13         43       RC13       44       TC13         45       GND       46       GND         47       RS14       48       TS14         49       RD14       50       TD14         51       RC14       52       TC14         53       GND       54       GND         55       RS15       56       TS15         57       RD15       58       TD15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 37 | GND  | 38 | GND  |

| 43       RC13       44       TC13         45       GND       46       GND         47       RS14       48       TS14         49       RD14       50       TD14         51       RC14       52       TC14         53       GND       54       GND         55       RS15       56       TS15         57       RD15       58       TD15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    | RS13 | 40 | TS13 |

| 45         GND         46         GND           47         RS14         48         TS14           49         RD14         50         TD14           51         RC14         52         TC14           53         GND         54         GND           55         RS15         56         TS15           57         RD15         58         TD15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 41 | RD13 | 42 | TD13 |

| 47       RS14       48       TS14         49       RD14       50       TD14         51       RC14       52       TC14         53       GND       54       GND         55       RS15       56       TS15         57       RD15       58       TD15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 43 | RC13 | 44 |      |

| 49     RD14     50     TD14       51     RC14     52     TC14       53     GND     54     GND       55     RS15     56     TS15       57     RD15     58     TD15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 45 | GND  | 46 | GND  |

| 51         RC14         52         TC14           53         GND         54         GND           55         RS15         56         TS15           57         RD15         58         TD15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 47 | RS14 | 48 |      |

| 53         GND         54         GND           55         RS15         56         TS15           57         RD15         58         TD15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 49 | RD14 | 50 | TD14 |

| 55         RS15         56         TS15           57         RD15         58         TD15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 51 | RC14 | 52 | TC14 |

| 55         RS15         56         TS15           57         RD15         58         TD15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 53 | GND  | 54 | GND  |

| 57 RD15 58 TD15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 55 | RS15 | 56 | TS15 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 57 | RD15 | 58 | TD15 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 59 | RC15 | 60 | TC15 |

**Table 1-C. Header C Definition**

| 1  | LD0        | 2  | LD1         |

|----|------------|----|-------------|

| 3  | LD2        |    | LD3         |

| 5  | LD4        | 6  | LD5         |

| 7  | GND        | 8  | GND         |

| 9  | LD6        | 10 | LD7         |

| 11 | LD8        | 12 | LD9         |

| 13 | LD10       | 14 | LD11        |

| 15 | GND        | 16 | GND         |

| 17 | LD12       | 18 | LD13        |

| 19 | LD14       | 20 | LD15        |

| 21 | LIM        | 22 | LMS         |

| 23 | GND        | 24 | GND         |

| 25 | LHOLD      | 26 | LHLDA       |

| 27 | LBGACK     | 28 | LINT        |

| 29 | <u>LCS</u> | 30 | <b>LRDY</b> |

| 31 | LCLK       | 32 | LBHE        |

| 33 | LWR        | 34 | <u>LRD</u>  |

| 35 | LA0        | 36 | LA1         |

| 37 | GND        | 38 | GND         |

| 39 | LA2        | 40 | LA3         |

| 41 | LA4        | 42 | LA5         |

| 43 | LA6        | 44 | LA7         |

| 45 | GND        | 46 | GND         |

| 47 | LA8        | 48 | LA9         |

| 49 | LA10       | 50 | LA11        |

| 51 | LA12       | 52 | LA13        |

| 53 | GND        | 54 | GND         |

| 55 | LA14       | 56 | LA15        |

| 57 | LA16       | 58 | LA17        |

| 59 | LA18       | 60 | LA19        |

#### 2. SOFTWARE

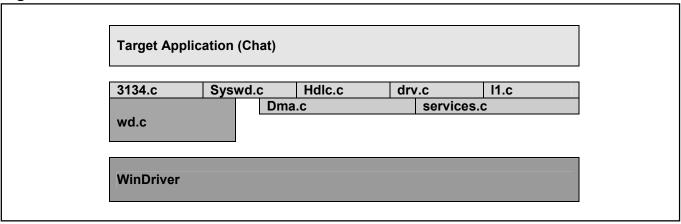

#### 2.1 Architecture

The DS31256DK software consists of a high-level piece of reference software called "Chat" that sits on top of a driver. This driver itself is composed of two discrete layers. The upper layer of the driver consists of various blocks of C code that are specific to the DS31256. These blocks contain an assortment of portable functions designed to serve as a low-level API for the Envoy. At the bottom level of the driver is the commercially available WinDriver, which interfaces with the Windows operating system to the DS31256DK's PCI hardware.

Figure 2-1. Software Architecture

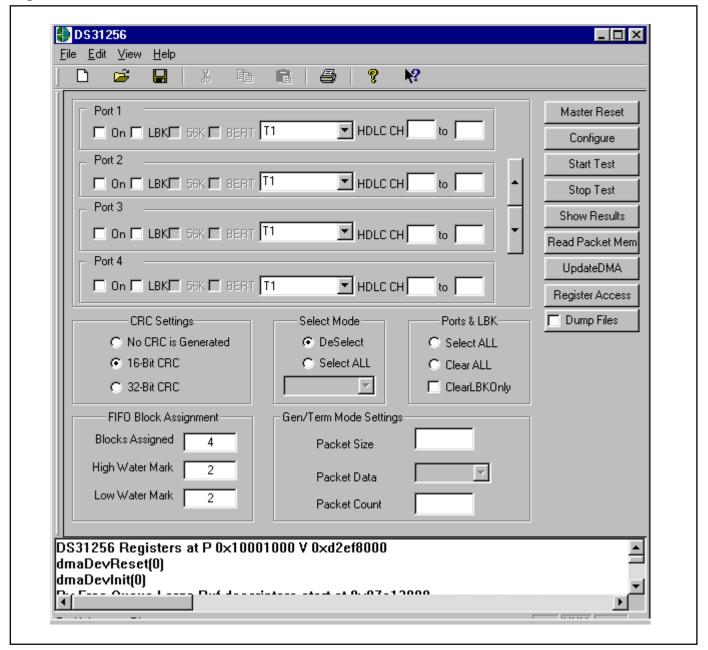

#### 2.2 Introduction to Chat

The DS31256DK software (Chat program) runs under a PC loaded with a Windows 95/98/NT operating system using the DS31256DK PCI card. The software includes two parts—the GUI interface (Figure 2-2) and the driver code. It is developed by Visual C++ and using WinDriver to create the driver.

The software provides:

- a simple demonstration of the DS31256 with the ability to set the device into a number of different configurations

- software drivers for the DS31256

- the ability to explore and load new data into the Envoy registers

- a utility to dump the internal Envoy registers to a file and to load Envoy from a file

- user-configurable DMA parameters

The software does not implement all the functions available in the DS31256. The user controls the software through a main GUI interface, as shown in <u>Figure 2-2</u>. The software implements 16 ports, coupled with 16 independent bidirectional HDLC channels. However, if a field in the main GUI is shaded gray, the function is not available.

**HDLC Channel Assignment Table**

| PORT NUMBER | HDLC CHANNEL NUMBER |

|-------------|---------------------|

| 0           | 1                   |

| 1           | 2                   |

| :           | :                   |

| 15          | 16                  |

When a test is run, the Envoy transmits data that is looped back to either the same port (if local loopback is used) or to an adjacent port (if the Altera PLD is used to loop the data). The software checks the receipt of packets to ensure they are received without error (i.e., the CRC is correct). For each HDLC channel that is enabled, the software also keeps track of the number of packets sent, number of packets received, number of packets received in error, and a variety of other statistics/counts.

#### 2.3 Chat GUI

### 2.3.1 Main GUI Interface—Configuration

Figure 2-2. Software Main GUI

### **General Configuration**

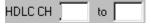

• The 16 ports on the Envoy are handled through a set of 16 check boxes. To save space on the screen, only four ports at a time are displayed. The user can scroll through the port boxes to access all 16 ports.

□On

■ The port number's box must be checked to be enabled. If this box is not checked, the software does not configure any of the RP[n]CR or TP[n]CR registers nor any of the R[n]CFG[j] and T[n]CFG[j] registers for that port.

□ LBK

• If this box is checked, the software sets the LLB bit (bit 10) in the RP[n]CR register to 1, configuring the port in loopback mode. If this box is not checked, the software clears the LLB bit.

T1 ▼

• Select the port mode from the drop-down box (same setting of the dip switch at the demo card):

T1 24 DS0 channels and 193 RC clocks between RS sync signals

E1 32 DS0 channels and 256 RC clocks between RS sync signals

4.096MHz 64 DS0 channels and 512 RC clocks between RS sync signals

8.192MHz 128 DS0 channels and 1024 RC clocks between RS sync signals

Unchannelized One HDLC channel and no RS sync signals, speeds up to 10Mbps

Unch-HiSpeed One HDLC high-speed channel and no RS sync signals (Ports 0–2 only), speeds

up to 52MHz

- If one of the channelized modes (T1/E1/4.096MHz/8.192MHz) is chosen, the software configures the RSS0/RSS1 (bits 6, 7) and TSS0/TSS1 (bits 6, 7) in the RP[n]CR and TP[n]CR registers, respectively.

- If one of the unchannelized modes (Unchannelized/Unch-HiSpeed) is selected, the software sets the RUEN bit (bit 9) and the TUEN bit (bit 9) in the RP[n]CR and TP[n]CR registers, respectively, to 1.

- If the Unch-HiSpd mode (Ports 0–2 only) is selected, the software sets the RP0HS/RP1HS bit (bit 8) and the TP0HS/TP1HS bit (bit 8) in the RP[n]CR and TP[n]CR registers, respectively, to 1.

- The user can select from number 1 to 256 which HDLC channels are assigned to each port. If the user assigns

the same HDLC channel to more than one port or inputs an invalid number, or the user assigns more than one

HDLC channel to one port when one of the unchannelized modes (Unchannelized/Unch-HiSpeed) is selected,

an error message is displayed when the Configure button is hit.

- If one of the channelized modes (T1/E1/4.096MHz/8.192MHz) is selected, the software uses the input from HDLC CH box to determine how to assign the time slots. The software divides the number of HDLC channels assigned into the number of time slots for the mode selected (i.e., 24 for T1, 32 for E1, 64 for 4.096MHz, and 128 for 8.192MHz) to determine how many time slots an HDLC channel occupies. It places the first HDLC channel for the port in the port's first time slot. All subsequent time slots are placed sequentially behind the previous one without a gap. If the result is a fraction, then a fraction of an HDLC channel fills the rest of the available bandwidth.

The table below shows an example of the T1 channel setting. Eight HDLC channels are assigned to port 1. Since there are 24 time slots in a T1 interface, the software divides 24 by 8 HDLC channels to get 3 time slots per HDLC channel and, therefore, it assigns 3 time slots (3 x 64kbps = 192kbps) for each HDLC channel. HDLC channel 2 is assigned to T1 time slots 0 to 2. HDLC channel 3 is assigned to T1 time slots 3 to 5, and so on.

| HDLC CHANNEL NUMBER | TIME SLOTS ASSIGNED | CHANNEL SPEED (kbps) |

|---------------------|---------------------|----------------------|

| 2                   | 0 to 2              | 192                  |

| 3                   | 3 to 5              | 192                  |

| 4                   | 6 to 8              | 192                  |

| 5                   | 9 to 11             | 192                  |

| 6                   | 12 to 14            | 192                  |

| 7                   | 15 to 17            | 192                  |

| 8                   | 18 to 20            | 192                  |

| 9                   | 21 to 23            | 192                  |

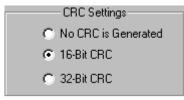

• The default CRC setting is 16-Bit CRC. The software sets the RCRC0/RCRC1 (bit 2, 3) and TCRC0/TCRC1 (bit 2, 3) in the RHCD and THCD registers, respectively.

- DeSelect: The user can deselect the mode setting of all 16 ports at once instead of unchecking them one by one.

- Select All: The user can select a desired mode for all 16 ports once instead of checking it one by one. The

mode list box is enabled when SelectAll is selected. The user selects the desired mode and the software

configures all 16 ports with the selected mode.

- Select All: All 16 ports and loopbacks are checked

- Clear All: All selected ports and loopbacks are unchecked

- ClearLBKOnly: All checked loopbacks are unchecked.

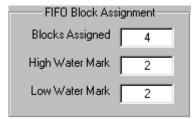

Default value of blocks within the FIFO is 4. High and low watermarks are two (50% is the recommendation). The user can input the desired number.

The software checks the maximum number of blocks that can be assigned, based on the following calculation.

The full size of the FIFO is 1024 (minimum size is 4) blocks divided by the total number of HDLC channels being used.

Blocks Assigned = 1024 / number of channels

An error message displays if the user inputs the invalid number.

Transmit high watermark can be set to a value of 1 to N - 2. Receive low watermark can be set to a value of 1 to N - 1. N is the number of blocks. (Refer to Section 8 in the DS31256 data sheet for details.)

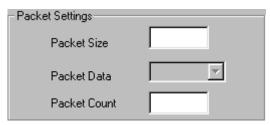

• The user can input the desired packet size in byte and an integer packet count through the Packet Size and Packet Count edit boxes for his/her test. The Packet Size edit box defaults to 0x100 and the edit box of Packet Count defaults to 100 if the user does not input any numbers.

### **Control Descriptions**

#### Master Reset

Chat program sets the Envoy into a default state by issuing a software reset and then writing 0s into all indirect

registers. The software also runs a register diagnostic to ensure it can correctly write and read all Envoy

registers. The address of the buffer, descriptor, and queue are displayed in the message box when the process

is done. If the diagnostic fails, the software creates an error message and displays it in the message box at the

bottom of the main GUI interface.

## Configure

• When this button is hit, the Chat program loads the Envoy registers with the settings in the GUI interface. "Successfully configured port #" is displayed in the message box if successful.

# Start Test

• The program transmits and receives packets based on the user's selections. "Test Done" is displayed in the message box when the test is done.

# Stop Test

• The user can stop the test any time. "Test stopped by user" is displayed in the message box when the user hits this button.

## Show Results

This brings up a screen (<u>Figure 2-3</u>) with detail information of the packet results.

### Read Packet Mem

• This brings the Physical Memory Viewer screen up (Figure 2-4). The software prompts the user for an address, then it dumps the next 32 dwords to the screen. The user manually cancels the screen. This button is only active when a test is not being run.

### UpdateDMA

• This brings up the DMA Configuration screen (<u>Figure 2-5</u>) for the user to configure the DMA by their desired values. Otherwise, the software uses default values to configure the DMA.

### Register Access

• This brings up the Envoy Registers screen (Figure 2-6) for the user to read from or write into the register by hex number.

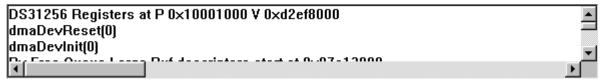

#### Dump Files

• The software dumps the data of transmit and receive queues into a text file when it is checked.

• The status of the process is displayed through the message box at the bottom of the main GUI.

# File Menu Descriptions

| Open        | All fields of the general configuration in the main GUI are filled from the file (that file should be saved by the software by Save under the File menu first). |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Save        | Copies all the selections from main GUI into a file when Save is selected.                                                                                      |  |

| Dump Regs   | Saves the settings of all registers into a text file. The user can dump information at any time.                                                                |  |

| Save Log    | Saves contents of the message box (at the bottom of the main GUI) into a text file.                                                                             |  |

| Dump Queues | Dumps all queue data into a text file.                                                                                                                          |  |

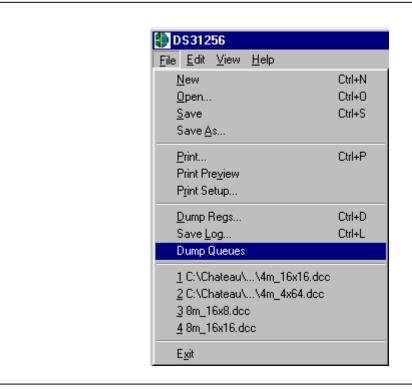

#### 2.3.2 Show Results

Figure 2-3. Show Results GUI

## **Descriptions of Driver Statistics**

| Rx Large Buffer Supplied    | Number of Rx large buffers used                |

|-----------------------------|------------------------------------------------|

| Rx Large Shadow Failed      | Number of Rx large shadow creation failures    |

| Rx Large Buf Fail Allocated | Number of Rx large buffer allocation failures  |

| RLBR                        | Read from SDMA Bit 6                           |

| RLBRE                       | Read from SDMA Bit 7                           |

| Rx Small Buffer Supplied    | Number of Rx small buffers used                |

| Rx Small Shadow Failed      | Number of Rx small shadow creation failures    |

| Rx Small Buf Fail Allocated | Number of Rx small buffers allocation failures |

| RSBR                        | Read from SDMA Bit 8                           |

| RSBRE                       | Read from SDMA Bit 9                           |

| RDQW                        | Read from SDMA Bit 10                          |

| RDQWE                       | Read from SDMA Bit 11                          |

| TPQR                        | Read from SDMA Bit 13                          |

| TDQW                        | Read from SDMA Bit 14                          |

| TDQWE                       | Read from SDMA Bit 15                          |

## **Descriptions of Application Statistics**

| Attempted Tx        | Number of packet transmission attempted             |  |

|---------------------|-----------------------------------------------------|--|

| Total Tx            | Total number of packets transmitted                 |  |

| Good Rx             | Number of packets received without error/problem    |  |

| Bad Rx              | Number of packets with errors                       |  |

| Data Errors         | For program debugging                               |  |

| DeadBeef Errors     | For program debugging                               |  |

| Rx Chan Data Errors | Number of packets with an incorrect channel number  |  |

| Rx Sequence Errors  | Number of packets with an incorrect sequence number |  |

## **Descriptions of HDLC Controller Statistics**

| Rx Done Queue (V Bit)  Number of V set occurrences in receive done-queue description |                                                                   |  |  |  |  |  |

|--------------------------------------------------------------------------------------|-------------------------------------------------------------------|--|--|--|--|--|

| Rx Callback Invocations                                                              | ck Invocations For program debugging                              |  |  |  |  |  |

| Rx Done Queue Entries Read                                                           | Number of done-queue entries read                                 |  |  |  |  |  |

| Rx-RL                                                                                | Status bit for receive HDLC length check (RLENC) in SDMA register |  |  |  |  |  |

The following seven items are read from receive done-queue descriptor, dword0, bits 27–29, reported at the final status of an incoming packet:

| Rx FIFO Overflows    | Remainder of the packet discarded                             |  |  |  |  |

|----------------------|---------------------------------------------------------------|--|--|--|--|

| Rx Checksum Error    | CRC checksum error                                            |  |  |  |  |

| Rx Long Frame Aborts | Max packet length exceeded; remainder of the packet discarded |  |  |  |  |

| Rx HDLC Frame Aborts | HDLC frame abort sequence detected                            |  |  |  |  |

| Rx Non-Aligned Byte  | Not an integral number of bytes                               |  |  |  |  |

| Rx PCI Aborts        | PCI abort or parity data error                                |  |  |  |  |

| Rx Reserved State    | Not a normal device operation event                           |  |  |  |  |

The following four items are read from transmit done-queue descriptor, dword0, bits 26–28, reported at the final status of an outgoing packet:

| Tx SW Provisioning Errors Channel was not enabled. |                                                                       |  |  |

|----------------------------------------------------|-----------------------------------------------------------------------|--|--|

| Tx PCI Errors                                      | PCI errors; abort                                                     |  |  |

| Tx Descriptor Errors                               | Either byte count = 0 or channel code inconsistent with pending queue |  |  |

| Tx FIFO Errors                                     | Underflow events                                                      |  |  |

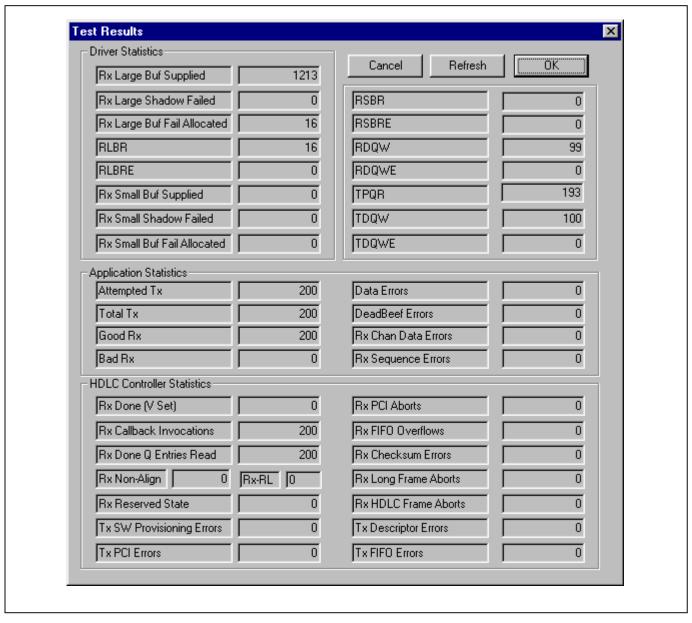

### 2.3.3 Memory Viewer

## Figure 2-4. Memory Viewer GUI

The physical memory viewer shows all the data within the start and end address space that is allocated by the Chat program. The user can step through memory by the address box or by using the scroll up/down buttons on the right.

### **Fields Descriptions**

| Start Address | Display the starting address of the DMA that the program allocated in the |  |  |

|---------------|---------------------------------------------------------------------------|--|--|

| Start Address | memory                                                                    |  |  |

| End Address   | Display the ending address of the DMA that the program allocated in the   |  |  |

| Liid Addiess  | memory                                                                    |  |  |

**Control Descriptions**

| _      | User can look at any address within the range of Start Address and End Address through the edit box;. (Input the desired physical address) and |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Engage | then hit the Engage button. All data displayed starts from the input physical address.                                                         |

### 2.3.4 DMA Configuration

Figure 2-5. DMA Configuration GUI

The DMA configuration displays default values at first, then the user can change the desired value and hit the Master Reset. The DMA in Envoy can read from the receive free queue and transmit pending queue as well as write to the receive done queue and transmit done queue. Therefore, each access of the descriptor queues are done one at a time, and sequentially.

### **Descriptions of Transmit DMA**

| Buffer Size     | Size of the transmit buffer side; maximum value = 0x1fff               |  |  |  |  |

|-----------------|------------------------------------------------------------------------|--|--|--|--|

| Free Queue Size | Number of free queues maximum value = 0xffff                           |  |  |  |  |

| Pending Queue   | Size: Size of pending queue, maximum = 0x10000;                        |  |  |  |  |

| Pending Queue   | FIFO: Enable/disable FIFO (TDMAQ bit 0)                                |  |  |  |  |

|                 | Size: Size of done queue in transmit DMA, maximum value = 0x10000      |  |  |  |  |

| Done Queue      | FIFO: Enable/disable FIFO (TDMAQ bit 2)                                |  |  |  |  |

| Done Queue      | Flush Timer: TDQFFT, maximum value = 0xffff                            |  |  |  |  |

|                 | Select DQS: HDLC packet (transmit DMA configuration RAM dword1, bit 1) |  |  |  |  |

# **Descriptions of Receive DMA**

|            | Large: RLBS register; maximum value = 0x1fff Small: RSBS register; maximum value = 0x1fff |  |  |

|------------|-------------------------------------------------------------------------------------------|--|--|

| Buffer     | Offset: Receive DMA configuration RAM, dword2, bits 3–6                                   |  |  |

|            | Size Select: Receive DMA configuration RAM dword2, bits 1 and 2                           |  |  |

|            | Large: Size of free queue for large buffer                                                |  |  |

|            | Buffer in Queue: Number of buffers to put into the free queue                             |  |  |

| Free Queue | Small: Size of free queue for large buffer                                                |  |  |

| Free Queue | Buffer in Queue: Number of buffers to put into the free queue                             |  |  |

|            | Maximum value of the free queue = 0x10000 (large + small)                                 |  |  |

|            | FIFO: Enable/disable FIFO (RDMAQ, bit 0)                                                  |  |  |

|            | Size: Size of receive done queue, maximum value = 0x10000                                 |  |  |

| Done Queue | FIFO: Enable/disable FIFO (RDMAQ, bit 4)                                                  |  |  |

| Done Queue | Flush Timer: RDQFFT, maximum value = 0xffff                                               |  |  |

|            | Threshold: Receive DMA configuration RAM, dword2, bits 7–9                                |  |  |

# **Control Descriptions**

| OK       | The DMA settings are updated with the value from all fields. |  |  |  |  |

|----------|--------------------------------------------------------------|--|--|--|--|

| SaveFile | Saves all the information from the GUI into a file.          |  |  |  |  |

| Default  | Restores all fields to Envoy default values.                 |  |  |  |  |

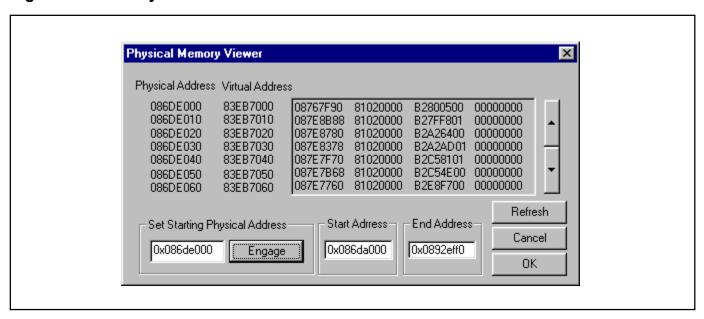

## 2.3.5 Register Access

# Figure 2-6. Registers Access GUI

## **Field Descriptions**

| Register Address     | Address of data register to read/write.                                                                                               |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Indirect Select Data | If the address is the indirect select register, user needs to input the value.                                                        |

| Value                | Display the value from the register when Read button is hit or specify the value to write into the register when Write button is hit. |

## **Control Descriptions**

| Done  | Close the screen.                                                                                                   |

|-------|---------------------------------------------------------------------------------------------------------------------|

| Write | Prompt the user for which register address to write and the value to be written and then it writes to the register. |

| Read  | Prompt the user for which register address to read and then it reads the register and return the value.             |

#### 2.4 Driver

The low-level API, or driver, shown in layer 2 of <u>Figure 2-1</u> may be used as a starting point in systems development to speed time to market. Low-level API source blocks are summarized in <u>Table 2-A</u>, and relate to one another structurally as shown in <u>Figure 2-7</u>. Note also in this figure a grouping of three particular source files: 3134.c, syswd.c, and wd.c. These are the files that must undergo modifications if the WinDriver package is not deployed in the target system.

Table 2-A. Low-Level API Source Block Contents

| SOURCE FILE | CONTENT/PURPOSE                                                     |  |  |  |  |  |

|-------------|---------------------------------------------------------------------|--|--|--|--|--|

| syswd.c     | Interface code to WindRiver; system and memory management functions |  |  |  |  |  |

| hdlc.c      | Channel management functions                                        |  |  |  |  |  |

| I1.c        | Port management and BERT functions                                  |  |  |  |  |  |

| drv.c       | Register management functions                                       |  |  |  |  |  |

| services.c  | Bit manipulation functions                                          |  |  |  |  |  |

| 3134.c      | WinDriver-generated PCI management functions                        |  |  |  |  |  |

| wd.c        | Generated WinDriver code                                            |  |  |  |  |  |

Section <u>4</u> (*Appendix A*) contains reference tables listing all of the functions in each of the above code blocks. Note that some of the data structures are elaborate, and that they are defined in the header files. Usage examples can be found in the Chat demonstration code.

Figure 2-7. Low-Level API Source Block Relationships

#### 3. INSTALLATION AND GETTING STARTED

Please contact <u>telecom.support@dalsemi.com</u> or call 972-371-6555 if you have any technical questions, or visit our website at <u>www.maxim-ic.com/telecom</u>.

#### 3.1 Card Installation

Separate instructions for Win95, Win98, and WinNT Systems.

### 3.1.1 Windows 95 Systems

- Power-down the host computer system, and open its case. Follow ESD precautions while in contact with the card, the DS31256, and system components.

- 2) If not already seated, install the DS31256 chip into the BGA socket on the DK's PC board.

- 3) Set the DIP switches on the card to configure the board and operational mode (Figure 1-2).

- 4) Plug the DS31256DK card into an empty PCI slot.

- 5) Reassemble the computer.

- 6) Boot the computer.

- 7) Insert the DS31256DK1 CD.

- 8) Open a DOS window to perform the following commands:

- Change directory to c:\windows\system\vmm32.

- Copy the file windrvr.vxd from the CD "Install\Win95" directory to c:\windows\system\vmm32.

- Copy the file wdreg.exe from the CD "Install\Win95" directory to c:\windows\system\vmm32.

- Run wdreg -vxd install from the DOS prompt in the current working directory.

- Close the DOS shell and reboot the machine.

#### 3.1.2 Windows 98 Systems

- 1) Power-down the host computer system, and open its case. Follow ESD precautions while in contact with the card, the DS31256, and system components.

- 2) If not already seated, install the DS31256 chip into the BGA socket on the DK's PC board.

- 3) Set the DIP switches on the card to configure the board and operational mode (Figure 1-2).

- 4) Plug the DS31256DK card into an empty PCI slot.

- 5) Reassemble the computer.

- 6) Boot the computer and do not allow the system to search for or install drivers for the new hardware.

- 7) Insert the DS31256DK1 CD.

- 8) Open a DOS window to perform the following commands.:

- Change directory to c:\windows\system\vmm32.

- Copy the file windryr.sys from the CD "Install\Win98" directory to c:\windows\system32\drivers.

- Copy the file *wdreg.exe* from the CD "Install\Win98" directory to c:\windows\system32\drivers.

- Run wdreg install from the DOS prompt in the current working directory.

- Close the DOS shell and reboot the machine.

### 3.1.3 Windows NT Systems

- 1) Power-down the host computer system, and open its case. Follow ESD precautions while in contact with the card, the DS31256, and system components.

- 2) If not already seated, install the DS31256 chip into the BGA socket on the DK's PC board.

- 3) Set the DIP switches on the card to configure the board and operational mode (Figure 1-2).

- 4) Plug the DS31256DK card into an empty PCI slot.

- 5) Reassemble the computer.

- 6) Boot the computer.

- 7) Insert the DS31256DK1 CD.

- 8) Open a DOS window to perform the following commands:

- Change directory to c:\winnt\system.

- Copy the file windrvr.sys from the CD "Install\WinNT" directory to c:\winnt\system32\drivers.

- Copy the file wdreg.exe from the CD "Install\WinNT" directory to c:\winnt\system32\drivers.

- Run wdreg install from the DOS prompt in the current working directory.

- Close the DOS shell, and reboot the machine.

#### 3.2 Software Installation

- 1) Make a directory on the system.

- 2) Copy Chat.exe from the CD "Install\<OS\_Type>" to the target directory.

- 3) Create a shortcut to the program, or set up a menu entry for it.

**Note:** The source code for Chat and the underlying drivers is in the CD "Source" directory. If desired, the source directory can also be copied off of the CD to the host.

### 3.3 Operational Test

After performing the card and software installations as described above,

1) Ensure that the board's DIP switches are set as follows:

| 1  | 2  | 3   | 4  | 5  | 6   | 7   | 8   | 9   | 10  |

|----|----|-----|----|----|-----|-----|-----|-----|-----|

| On | On | Off | On | On | Off | Off | Off | Off | Off |

- 2) Execute the Chat.exe program.

- 3) Click the on and LBK checkbox for Port 1.

- 4) Make sure the Port 1 pulldown selector is set to T1 mode.

- 5) Set the Port 1 channel range from 1 to 24 HDLC CH to

- 6) Set both the Packet Size and Packet Count to 100.

|     | Packet Size Packet Count                                                                                       |

|-----|----------------------------------------------------------------------------------------------------------------|

|     | a Master Reset                                                                                                 |

| 7)  | Click the button.                                                                                              |

| 8)  | Click the Configure button. This results in a message stating "Successfully configured Port 1."                |

| 9)  | Click the Start Test button. The message "Starting test with 100 packets" appears. The message "Test Done"     |

|     | prints when complete.                                                                                          |

| 10) | Next, click the Show Results button. In the Application Statistics portion of the results window the following |

|     | data (part of them) will appear:                                                                               |

|     | Atempted Tx 100                                                                                                |

Atempted Tx

100

Total Tx

100

Good Tx

100

Bad Tx

0

## 4. APPENDIX A

| FUNCTIO            | N PURPOSE                                                   | RETURNS              |

|--------------------|-------------------------------------------------------------|----------------------|

| SysDevOpen         | Open a particular card/device on PCI                        | int32                |

| SysDevClose        | Disable interrupts, unregister a card, and close the driver | int32                |

| SysIntInit         | Configure ISR                                               | Nothing              |

| SysCrash           | System crash error handler                                  | Nothing              |

| SysFail            | System failure handler                                      | Nothing              |

| SysRxBufAlloc      | Allocate receive large buffer                               | drvRxBuf *           |

| SysRxSmBufAlloc    | Allocate receive small buffer                               | DrvRxBuf *           |

| SysRxBufFree       | Free receive large buffer                                   | Nothing              |

| SysRxSmBufFree     | Free receive small buffer                                   | Nothing              |

| sysRxBufLastFree   | Free the buffer in final                                    | Nothing              |

| sysTxBufAlloc      | Allocate transmit buffer                                    | drvTxBuf *           |

| sysTxBufFree       | Free transmit buffer                                        | Nothing              |

| sysDevWrReg16      | Writes a word to an address space on the board              | Nothing              |

| sysDevRdReg16      | Reads a word f rom an address space on the board            | int32                |

| sysIntDisable      | Lock out interrupt thread                                   | int32                |

| sysIntEnable       | Enable interrupt processing                                 | Nothing              |