# DATA SHEET

# Generic device for portable multimedia applications SAA7750-N1D

Preliminary Specification version 1.3 File under Integrated Circuits, <Handbook>

2002 Jan 21

# Generic device for portable multimedia applications

| CONTEN         | ITS                                                | 6.9.1          | Functional Description                       |

|----------------|----------------------------------------------------|----------------|----------------------------------------------|

| 1              | FEATURES                                           | 6.9.2          | UART Pin Description                         |

| 1 1            | Hardware Features                                  | 6.9.3          | BaudRate Generator                           |

| 1.1<br>1.2     | General Features                                   | 6.10           | General Purpose I/O                          |

| 1.3            | Software features                                  | 6.10.1         | Functional Description                       |

|                |                                                    | 6.10.2         | Interrupts                                   |

| 2              | GENERAL DESCRIPTION                                | 6.11           | Real Time Clock (RTC)                        |

| 3              | APPLICATIONS                                       | 6.11.1         | Functional Description                       |

| 4              | BLOCK DIAGRAM                                      | 6.11.2         | Interrupts                                   |

| 5              | PINNING                                            | 6.11.3<br>6.12 | Power Down operation Timers                  |

|                |                                                    | 6.12.1         | Functional description                       |

| 6              | HARDWARE DESCRIPTION SSA                           | 6.12.2         | Interrupts                                   |

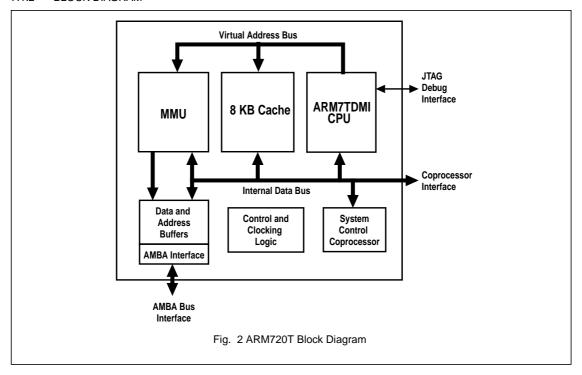

| 6.1            | ARM720T microcontroller                            | 6.13           | Watchdog Timer                               |

| 6.1.1          | Overview                                           | 6.13.1         | Functional description                       |

| 6.1.2          | BLOCK DIAGRAM                                      | 6.13.2         | Interrupts                                   |

| 6.1.3          | The THUMB Concept                                  | 6.14           | IIC master Interface                         |

| 6.2            | Internal busses                                    | 6.14.1         | Functional Description                       |

| 6.2.1          | Advanced High-performance Bus (AHB)                | 6.14.2         | Interrupt                                    |

| 6.2.2          | AHB Address Decoder                                | 6.15           | IIC slave Interface                          |

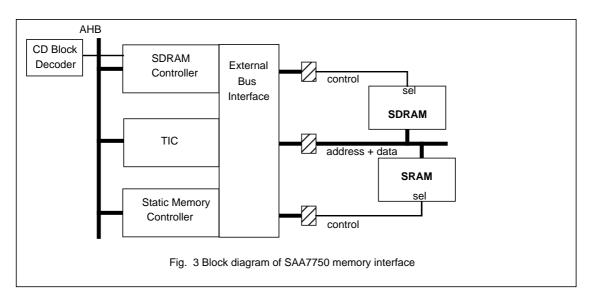

| 6.3            | Memory controllers                                 | 6.15.1         | Functional description                       |

| 6.3.1          | Overview                                           | 6.15.2         | Interrupt                                    |

| 6.3.2          | Static Memory Controller                           | 6.16           | LCD Interface                                |

| 6.3.3          | SDRAM Interface Controller                         | 6.16.1         | Functional Description                       |

| 6.3.4          | Internal Memory Controller                         | 6.16.2         | Interface                                    |

| 6.3.5          | FLASH memory controller                            | 6.16.3         | System Interface                             |

| 6.3.5.1        | FLASH reads                                        | 6.16.4         | Resetting the LCD controller                 |

| 6.3.5.2        | Erasing the FLASH block                            | 6.16.5         | Serial mode:                                 |

| 6.3.5.3        | Programming the FLASH block                        | 6.16.6         | Using wait states                            |

| 6.3.5.4        | Operating conditions                               | 6.16.7         | Checking the busy flag of the LCD controller |

| 6.4            | Interrupt Controller Overview                      | 6.16.8         | Loopback mode                                |

| 6.4.1<br>6.4.2 |                                                    | 6.16.9         | Interrupt                                    |

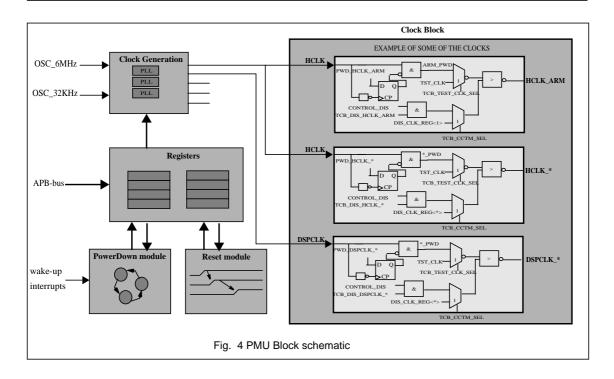

| 6.5            | Functional Description Power Management Unit (PMU) | 6.17           | Remote Control Interface                     |

| 6.5.1          | Functional Description                             | 6.17.1         | Functional Description                       |

| 6.5.2          | Wake-up behaviour                                  | 6.18           | Parallel Port Interface (PPI)                |

| 6.5.3          | Watchdog behaviour                                 | 6.19           | USB Interface                                |

| 6.5.4          | Pause behaviour                                    | 6.19.1         | Interrupts                                   |

| 6.5.5          | Power down behaviour                               | 6.19.1.1       | USB_int_req_FIQ                              |

| 6.5.5.1        | Power down Request                                 | 6.19.1.2       | USB_int_req_IRQ                              |

| 6.5.5.2        | Power down Acknowledge                             | 6.19.1.3       | Interrupt handling                           |

| 6.6            | Oscillators and clock generation                   | 6.19.1.4       | Zero overhead operation                      |

| 6.6.1          | Overview clock generation module                   | 6.20           | CD Block Decoder                             |

| 6.6.2          | Functional Description                             | 6.20.1         | Functional Description                       |

| 6.7            | Multi Media Card Interface (MMC)                   | 6.20.1.1       | Features                                     |

| 6.7.1          | Choice of flash memory cards                       | 6.20.2         | Input/Output Pin Function                    |

| 6.8            | 10-bit ADC                                         | 6.20.3         | I2C Interface                                |

| 6.8.1          | Overview                                           | 6.20.4         | Standard Serial Interface UART               |

| 6.8.2          | Functional description                             | 6.20.5         | Subcode Interface                            |

| 6.8.3          | Multi channel A/D conversion scan                  | 6.20.6         | Serial Data Interface                        |

| 6.8.4          | ADC resolution                                     | 6.20.7         | Minimal Block Decoder                        |

| 6.8.5          | Interrupts                                         | 6.20.8         | CD TEXT Mode                                 |

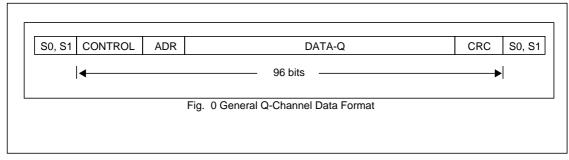

| 6.9            | UART                                               | 6.20.9         | Q-subcode Frame Format                       |

|                |                                                    | 6.21           | Digital Signal Processor (EPICS7a)           |

2002 Jan 21 2

# Generic device for portable multimedia applications

| 6.22 | Digital Audio input and output        |

|------|---------------------------------------|

| 7    | HARDWARE DESCRIPTION SSA CODE         |

| 7.1  | General                               |

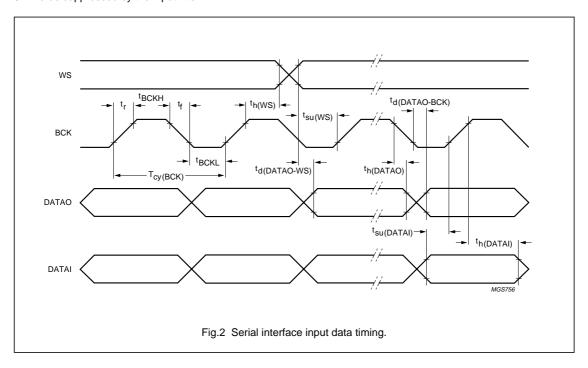

| 7.2  | Multiple format data INPUT interface  |

| 7.3  | Multiple format data OUTPUT interface |

| 7.4  | DAC digital sound processing          |

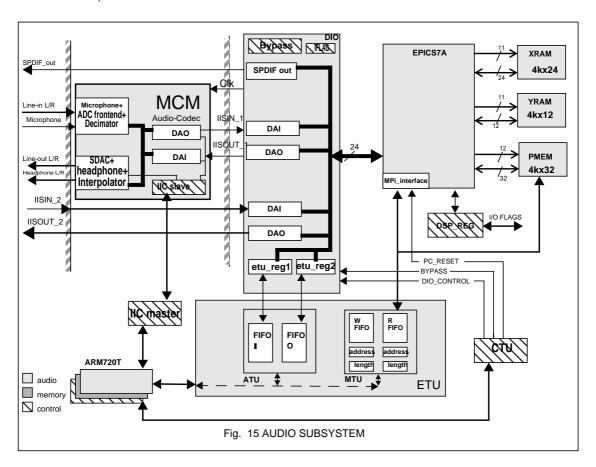

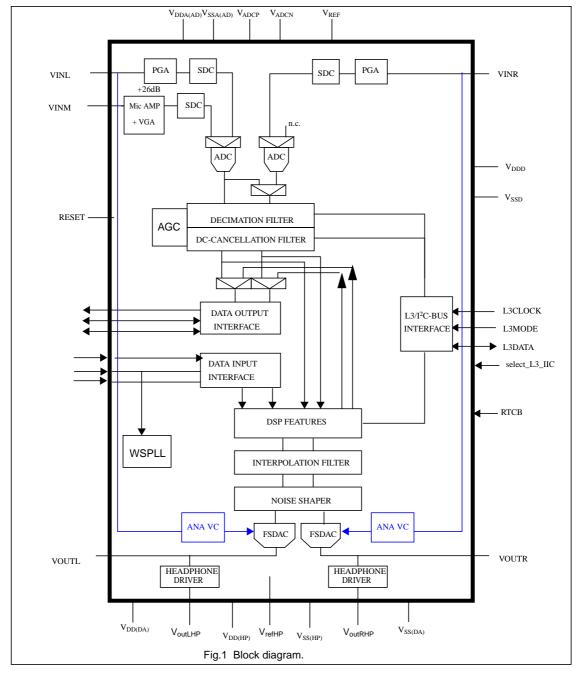

| 7.5  | Block diagram                         |

| 7.6  | Connections to SAA7750                |

| 8    | HARDWARE DESCRIPTION FLASH            |

| 9    | LIMITING VALUES                       |

| 10   | THERMAL CHARACTERISTICS               |

| 11   | DC CHARACTERISTICS                    |

| 12   | AC CHARACTERISTICS                    |

| 13   | PACKAGE OUTLINE                       |

| 14   | SOLDERING                             |

| 15   | DEFINITIONS                           |

| 16   | DISCLAIMERS                           |

17PURCHASE OF PHILIPS I2C COMPONENTS

2002 Jan 21 3

# Generic device for portable multimedia applications

### 1 FEATURES

NOTE: this datasheet is for SAA7750El version N1D onwards!!

### 1.1 Hardware Features

- Integrated ARM720T 32 bit RISC processor, capable of running at 72MHz.

- · High performance 32-bits bus (AHB)

- Centralized address decoding for all AHB devices

- Four possible memory maps:

- external boot

- internal flash boot

- internal ROM boot

- normal operation

- Supports USB 1.1 compliant interface for down loading data from PC

- · Support for flash-card applications:

- Supports the Multi Media Card (MMC)

- Supports Smart Media Card (EBI)

- NAND FLASH (EBI)

- Memory interface (EBI) supporting a number of memory types like Static RAM, SDRAM, external Flash.

The maximum bus frequency can be up to 48MHz.

- Integrated CD block decoder for CD-DA and MP3 CD applications

- UART + IrDA (IrDA is a new block on the N1D version)

- Integrated Master and Slave IIC interface

- Real-Time Clock (RTC)

- General-Purpose IO pins (28 pins)

- Integrated Remote Control interface

- Integrated LCD interface with 6800 / 8080 type interface

- Integrated 10 bits ADC with 8 selectable inputs (via analog multiplexer).

- · Integrated SPDIF output interface

- · Integrated IIS input and output interface

- · Integrated stereo Audio Codec

- Stereo Line input with Programmable Gain Amplifier (PGA)

- Mono Microphone input with embedded Low Noise Amplifier (LNA) and Variable Gain Amplifier (VGA

- stereo analog input with analog volume control (e.g. for tuner applications)

- stereo line output

- integrated stereo headphone driver which can be used in DC coupling (short circuit protection and detection build in).

### 1.2 General Features

- Integrated ARM720T 32 bit RISC processor

- Programmable architecture enables support of multiple audio decompression algorithms.

- · Designed for applications that require long battery life

# Generic device for portable multimedia applications

- Embedded 3Mbit (384kbyte) flash for Field upgradibility

- · Embedded Audio Codec with headphone driver

- · small footprint LFBGA208 package

### 1.3 Software features

- Audio Decoder support:

- Supports MPEG 1 layer 3 and MPEG 2 layer 2.5 and layer 3 audio decoding (MP3), up to 320kbit/s, fixed and variable bitrate.

- Supports Microsoft WMTA 4.0 decoding

- Supports AAC-LC decoding

- · Features on the audio codec:

- Digital Automatic Gain Control (AGC) on the microphone input.

- Programmable Gain Amplifier (PGA) for analog stereo line input

- Volume control (incl. balance)

- Bass-boost and Treble (left/right)

- · DSP features:

- UltraBass II

- Incredible headphone

- Infrapitch

### 2 GENERAL DESCRIPTION

The SAA7750 is an IC based on an embedded RISC processor in combination with a simple embedded DSP core for audio post-processing. The device is designed for hand-held applications like portable CD-DA/ MP3 players, memory card applications or other portable applications. The high level of integration, low power consumption and high processor performances make the SAA7750 very suitable for portable hand-held devices.

The SAA7750 is based on the powerful ARM720T CPU core, which is a full 32-bit RISC processor featuring the 16-bit Thumb instruction set for effective memory usage. The audio streaming and post-processing for the SAA7750 is handled by a separate audio co-processor DSP, which is a small, fast and powerful 24-bit Epics7A DSP core.

### 3 APPLICATIONS

- · Portable Solid State Audio player

- Portable MP3 CD player

- · Home audio applications

- · Non-automotive Car applications

- · Other portable applications like PDA

### 4 ORDERING INFORMATION

| TYPE NUMBER  |          | PACKAGE                                                                           |          |  |  |  |  |  |  |

|--------------|----------|-----------------------------------------------------------------------------------|----------|--|--|--|--|--|--|

| TIPE NOWBER  | NAME     | DESCRIPTION                                                                       | VERSION  |  |  |  |  |  |  |

| SAA7750EL/N1 | LFBGA208 | low profile fine-pitch ball grid array package; 208 balls; body 15 x 15 x 1.2 mm. | SOT631-1 |  |  |  |  |  |  |

2002 Jan 21

6

PHILIPS CONFIDENTIAL

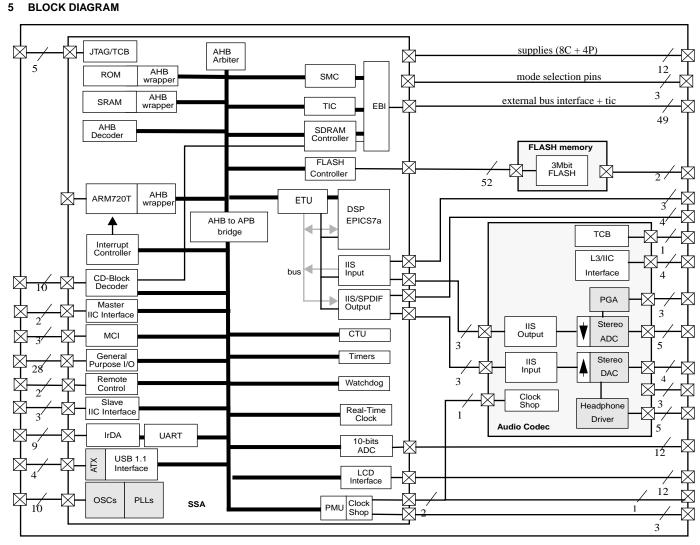

Fig. 1 Block diagram Solid State Audio 1

# Generic device for portable multimedia applications

### 6 PINNING

Table 1 Pin list SAA7750EL

| SYMBOL <sup>(1)</sup>   | LFBGA<br>208<br>PIN | DIGITAL I/O LEVEL | APPL.<br>FUNC | PIN STATE<br>AFTER<br>RESET | DESCRIPTION                  |

|-------------------------|---------------------|-------------------|---------------|-----------------------------|------------------------------|

| General Purpose Pins    | (fixed: 16 p        | oins)             |               |                             |                              |

| GPIO<27>                | A13                 | 0-5 VDC tolerant  | I/O           | 0                           | General Purpose IO pin       |

| GPIO<26>                | A12                 | 0-5 VDC tolerant  | I/O           | 0                           | General Purpose IO pin       |

| GPIO<25>                | B12                 | 0-5 VDC tolerant  | I/O           | 0                           | General Purpose IO pin       |

| GPIO<24>                | A11                 | 0-5 VDC tolerant  | I/O           | 0                           | General Purpose IO pin       |

| GPIO<23>                | B11                 | 0-5 VDC tolerant  | I/O           | 0                           | General Purpose IO pin       |

| GPIO<22>                | A10                 | 0-5 VDC tolerant  | I/O           | 0                           | General Purpose IO pin       |

| GPIO<21>                | B10                 | 0-5 VDC tolerant  | I/O           | 0                           | General Purpose IO pin       |

| GPIO<20>                | A9                  | 0-5 VDC tolerant  | I/O           | 0                           | General Purpose IO pin       |

| GPIO<19>                | B9                  | 0-5 VDC tolerant  | I/O           | 0                           | General Purpose IO pin       |

| GPIO<18>                | A8                  | 0-5 VDC tolerant  | I/O           | 0                           | General Purpose IO pin       |

| GPIO<17>                | B8                  | 0-5 VDC tolerant  | I/O           | 0                           | General Purpose IO pin       |

| GPIO<16>                | A7                  | 0-5 VDC tolerant  | I/O           | 0                           | General Purpose IO pin       |

| GPIO<15>                | F4                  | 0-5 VDC tolerant  | I/O           | 0                           | General Purpose IO pin       |

| GPIO<14>                | G2                  | 0-5 VDC tolerant  | I/O           | 0                           | General Purpose IO pin       |

| GPIO<13>                | F3                  | 0-5 VDC tolerant  | I/O           | 0                           | General Purpose IO pin       |

| GPIO<12>                | G1                  | 0-5 VDC tolerant  | I/O           | 0                           | General Purpose IO pin       |

| GPIO<11>                | F2                  | 0-5 VDC tolerant  | I/O           | 0                           | General Purpose IO pin       |

| GPIO<10>                | F1                  | 0-5 VDC tolerant  | I/O           | 0                           | General Purpose IO pin       |

| GPIO<9>                 | D3                  | 0-5 VDC tolerant  | I/O           | 0                           | General Purpose IO pin       |

| GPIO<8>                 | E2                  | 0-5 VDC tolerant  | I/O           | 0                           | General Purpose IO pin       |

| GPIO<7>                 | D4                  | 0-5 VDC tolerant  | I/O           | 0                           | General Purpose IO pin       |

| GPIO<6>                 | E1                  | 0-5 VDC tolerant  | I/O           | 0                           | General Purpose IO pin       |

| GPIO<5>                 | D2                  | 0-5 VDC tolerant  | I/O           | 0                           | General Purpose IO pin       |

| GPIO<4>                 | D1                  | 0-5 VDC tolerant  | I/O           | 0                           | General Purpose IO pin       |

| GPIO<3>                 | C2                  | 0-5 VDC tolerant  | I/O           | 0                           | General Purpose IO pin       |

| GPIO<2>                 | C1                  | 0-5 VDC tolerant  | I/O           | 0                           | General Purpose IO pin       |

| GPIO<1>                 | B1                  | 0-5 VDC tolerant  | I/O           | 0                           | General Purpose IO pin       |

| GPIO<0>                 | A1                  | 0-5 VDC tolerant  | I/O           | 0                           | General Purpose IO pin       |

| Memory Card Interface   | e (fixed: 3 p       | oins)             |               |                             |                              |

| MCI_DAT                 | A4                  | 0-5 VDC tolerant  | I/O           |                             | Data input/Data output       |

| MCI_CLK                 | A2                  |                   | 0             |                             | MCI clock output             |

| MCI_CMD                 | B2                  | 0-5 VDC tolerant  | I/O           |                             | Command input/Command output |

| USB Interface (fixed: 4 | pins)               |                   |               |                             |                              |

| USB_DP                  | C17                 |                   | Α             |                             | Positive USB data line       |

| USB_DM                  | D17                 |                   | Α             |                             | Negative USB data line       |

| USB_CONNECT_N           | D16                 |                   | 0             |                             | Soft connect output          |

| USB_VUSB                | C15                 | 0-5 VDC tolerant  | I             |                             | USB supply detection input   |

| 6 MHz oscillator (fixed | <del></del>         | 1                 | 1             |                             | T                            |

| XTAL1I                  | P4                  |                   | Α             |                             | 6MHz clock input             |

| XTAL1O                  | R3                  |                   | Α             |                             | 6MHz clock output            |

| SYMBOL <sup>(1)</sup>                 | LFBGA<br>208<br>PIN | DIGITAL I/O LEVEL  | APPL.<br>FUNC                                    | PIN STATE<br>AFTER<br>RESET | DESCRIPTION                                                      |  |

|---------------------------------------|---------------------|--------------------|--------------------------------------------------|-----------------------------|------------------------------------------------------------------|--|

| VDDA1                                 | R2                  |                    |                                                  |                             | Analog supply Oscillator 1                                       |  |

| VSSA1                                 | R1                  |                    |                                                  |                             | Analog ground Oscillator 1                                       |  |

| 32.768 kHz oscillator (fixed: 4 pins) |                     |                    |                                                  |                             |                                                                  |  |

| XTAL2I                                | N4                  |                    | Α                                                |                             | 32.768 kHz clock input                                           |  |

| XTAL2O                                | P3                  |                    | Α                                                |                             | 32.768 kHz clock output                                          |  |

| VDDA2                                 | P2                  |                    |                                                  |                             | Analog supply Oscillator 2                                       |  |

| VSSA2                                 | P1                  |                    |                                                  |                             | Analog ground Oscillator 2                                       |  |

| Voltage Supply PLLs (                 | fixed: 2 pin        | s)                 |                                                  |                             |                                                                  |  |

| VDDA3                                 | N2                  |                    |                                                  |                             | Analog supply PLLs                                               |  |

| VSSA3                                 | N1                  |                    |                                                  |                             | Analog ground PLLs                                               |  |

| PLL (fixed: 1 pin)                    | l                   |                    |                                                  | 1                           |                                                                  |  |

| CLKO1                                 | F15                 |                    | 0                                                | toggling                    | 256fs clock output                                               |  |

| LCD Interface (fixed: 1               | l                   |                    |                                                  | 33 3                        |                                                                  |  |

| LCD_WE                                | КЗ                  |                    | 0                                                |                             | Write Enable                                                     |  |

| LCD_RW_WR                             | A16                 |                    | 0                                                |                             | 6800 read/write select<br>8080 active 'high' write enable        |  |

| LCD_E_RD                              | B15                 |                    | 0                                                |                             | 6800 active 'low' enable<br>8080 active 'high' write enable      |  |

| LCD_DB<0>                             | D14                 | 0-5 VDC tolerant   | I/O                                              |                             | Data input 0/Data output 0                                       |  |

| LCD_DB<1>                             | B17                 | 0-5 VDC tolerant   | I/O                                              |                             | Data input 1/Data output 1                                       |  |

| LCD_DB<2>                             | C14                 | 0-5 VDC tolerant   | I/O                                              |                             | Data input 2/Data output 2                                       |  |

| LCD_DB<3>                             | C16                 | 0-5 VDC tolerant   | I/O                                              |                             | Data input 3/Data output 3                                       |  |

| LCD DB<4>                             | D13                 | 0-5 VDC tolerant   | I/O                                              |                             | Data input 4/Data output 4                                       |  |

| LCD_DB<5>                             | A17                 | 0-5 VDC tolerant   | 1/0                                              |                             | Data input 5/Data output 5/serial clock                          |  |

| LCD_DB<6>                             | C13                 | 0-5 VDC tolerant   | 1/0                                              |                             | Data input 6/Data output 6/Serial data input                     |  |

| LCD_DB<7>                             | B16                 | 0-5 VDC tolerant   | I/O                                              |                             | Data input 7/Data output 7/Serial data output                    |  |

| LCD_CSB                               | C12                 |                    | 0                                                |                             | Chip Select (active low)                                         |  |

| LCD_RS                                | D12                 |                    | 0                                                |                             | 'high' Data register select<br>'low' Instruction register select |  |

| Parallel Port Interface               | (fixed: 18 p        | ins) THIS FUNCTION | LITY HAS                                         | BEEN REMO                   | ·                                                                |  |

| 10-bit ADC (fixed: 12pi               |                     | .,                 |                                                  |                             |                                                                  |  |

| GPA<7>                                | B7                  |                    | Α                                                |                             | Analog General Purpose pin 7                                     |  |

| GPA<6>                                | A6                  |                    | Α                                                |                             | Analog General Purpose pin 6                                     |  |

| GPA<5>                                | B6                  |                    | Α                                                |                             | Analog General Purpose pin 5                                     |  |

| GPA<4>                                | A5                  |                    | A                                                |                             | Analog General Purpose pin 4                                     |  |

| GPA<3>                                | B5                  |                    | A                                                |                             | Analog General Purpose pin 3                                     |  |

| GPA<2>                                | J3                  |                    | A                                                |                             | Analog General Purpose pin 2                                     |  |

| GPA<1>                                | M4                  |                    | A                                                |                             | Analog General Purpose pin 1                                     |  |

| GPA<0>                                | N3                  |                    | A                                                |                             | Analog General Purpose pin 0                                     |  |

| VREFP<1>                              | M3                  |                    | A                                                |                             | 10-bit ADC Reference voltage 1                                   |  |

| VREFP<0>                              | L2                  |                    | A                                                |                             | 10-bit ADC Reference voltage 0                                   |  |

| VDDA4                                 | M2                  |                    | <u> </u>                                         |                             | Analog supply 10-bit ADC                                         |  |

| VSSA4                                 | M1                  |                    | <del>                                     </del> |                             | Analog ground 10-bit ADC                                         |  |

| Remote Control (fixed:                | l                   | I                  | L                                                | L                           | Tritalog ground 10-bit ADO                                       |  |

| DO<0>                                 | K1                  |                    | 0                                                |                             | Remote Control Data Output 0                                     |  |

| DI<0>                                 | K2                  | 0-5 VDC tolerant   | Ī                                                |                             | Remote Control Data Input 0                                      |  |

| IIS input (fixed: 3 pins)             | l                   | 0 0 VDO tolerant   | <u>'</u>                                         | 1                           | Tromoto Control Data Input o                                     |  |

| BCKI1                                 | J15                 | 0-5 VDC tolerant   | 1                                                |                             | Bitclock input (external)                                        |  |

| DOMI                                  | 010                 | 0-3 VDC tolerant   | <u> </u>                                         | 1                           | Ditolock input (external)                                        |  |

| SYMBOL <sup>(1)</sup>     | LFBGA<br>208<br>PIN | DIGITAL I/O LEVEL | APPL.<br>FUNC | PIN STATE<br>AFTER<br>RESET | DESCRIPTION                                                             |  |  |

|---------------------------|---------------------|-------------------|---------------|-----------------------------|-------------------------------------------------------------------------|--|--|

| WSI1                      | H15                 | 0-5 VDC tolerant  | 1             |                             | Wordselect input (external)                                             |  |  |

| DATAI1                    | G15                 | 0-5 VDC tolerant  | - 1           |                             | Serial data input (external)                                            |  |  |

| IIS output (fixed: 3 pins | s)                  |                   | -             | -                           |                                                                         |  |  |

| BCKO1                     | M14                 |                   | 0             | Tri-state                   | Bitclock output (external)                                              |  |  |

| WSO1                      | F16                 |                   | 0             | Tri-state                   | Wordselect output (external)                                            |  |  |

| DATAO1                    | E16                 |                   | 0             | Output/Low                  | Serial data output (external)                                           |  |  |

| SPDIF output (fixed: 1    | pin)                |                   | -             |                             |                                                                         |  |  |

| DATAO2_SPDIFO             | E15                 |                   | 0             |                             | Serial data output (internal), SPDIF output                             |  |  |

| JTAG (fixed: 5 pins)      |                     |                   | -             |                             |                                                                         |  |  |

| JTAG_NTRST                | K15                 | 0-5 VDC tolerant  | - 1           |                             | JTAG Reset Input                                                        |  |  |

| JTAG_TCK                  | U12                 | 0-5 VDC tolerant  | I             |                             | JTAG Clock Input                                                        |  |  |

| JTAG_TMS                  | K16                 | 0-5 VDC tolerant  | 1             |                             | JTAG Mode Select Input                                                  |  |  |

| JTAG_TDI                  | T13                 | 0-5 VDC tolerant  | I             |                             | JTAG Data Input                                                         |  |  |

| JTAG_TDO                  | U13                 |                   | 0             |                             | JTAG Data Output                                                        |  |  |

| IIC slave Interface (fixe | d: 3 pins)          | •                 | •             | •                           |                                                                         |  |  |

| SCL_SLAVE                 | P12                 | 0-5 VDC tolerant  | - 1           |                             | Serial clock IIC Slave                                                  |  |  |

| SDA_SLAVE                 | R12                 | 0-5 VDC tolerant  | I/O           |                             | Serial data IIC Slave                                                   |  |  |

| A0_SLAVE                  | T12                 | 0-5 VDC tolerant  | 1             |                             | Address selection Slave                                                 |  |  |

| IIC master interface (fix | xed: 2 pins         | )                 |               |                             |                                                                         |  |  |

| SDA_MASTER                | R13                 | 0-5 VDC tolerant  | I/O           |                             | IIC data I/O line (open drain output)/<br>UART Serial Data Input        |  |  |

| SCL_MASTER                | P13                 | 0-5 VDC tolerant  | I/O           |                             | IIC clock line output/<br>UART Serial Data Output                       |  |  |

| CD Block Decoder (fixe    | ed: 10 pins         | )                 |               |                             |                                                                         |  |  |

| CDB_CRQ_NERDY             | C5                  | 0-5 VDC tolerant  | I             |                             | Communication request line/CD engine is ready to receive the next frame |  |  |

| CDB_NCRST_NHRDY           | D5                  |                   | 0             |                             | CD engine reset line/Host is ready to receive the next frame            |  |  |

| CDB_CLAB                  | C9                  | 0-5 VDC tolerant  | - 1           |                             | IIS/EIAJ input bit clock                                                |  |  |

| CDB_DAAB                  | C7                  | 0-5 VDC tolerant  | - 1           |                             | IIS/EIAJ serial data                                                    |  |  |

| CDB_WSAB                  | C8                  | 0-5 VDC tolerant  | - 1           |                             | IIS/EIAJ word clock                                                     |  |  |

| CDB_EFAB                  | D9                  | 0-5 VDC tolerant  | I             |                             | IIS/EIAJ error flags                                                    |  |  |

| CDB_V4_SUB                | D8                  | 0-5 VDC tolerant  | I             |                             | Versatile pin 4:single wire subcode/EIAJ subcode data bits              |  |  |

| CDB_CFLAG_SBSY            | D6                  | 0-5 VDC tolerant  | I             |                             | Absolute time sync/EIAJ subcode block sync                              |  |  |

| CDB_SFSY                  | D7                  | 0-5 VDC tolerant  | I             |                             | EIAJ subcode frame sync                                                 |  |  |

| CDB_RCK                   | C6                  |                   | 0             |                             | EIAJ subcode clock output                                               |  |  |

| EBI (fixed: 49 pins)      |                     |                   |               |                             |                                                                         |  |  |

| EBI_NCS<2>                | G16                 |                   | 0             |                             | Chip Selected 2                                                         |  |  |

| EBI_NCS<1>                | T10                 |                   | 0             |                             | Chip Selected 1                                                         |  |  |

| EBI_NCS<0>                | U10                 |                   | 0             |                             | Chip Selected 0                                                         |  |  |

| EBI_SDNCS<0>              | H3                  |                   | 0             |                             | External SDRAM selection1 and SDRAM selection0                          |  |  |

| EBI_WEN                   | J2                  |                   | 0             |                             | Write enable not                                                        |  |  |

| EBI_A<20>                 | J16                 |                   | 0             |                             | EBI address                                                             |  |  |

| EBI_A<19>                 | H16                 |                   | 0             |                             | EBI address                                                             |  |  |

| EBI_A<18>                 | F14                 |                   | 0             |                             | EBI address                                                             |  |  |

| EBI_A<17>                 | G14                 |                   | 0             |                             | EBI address                                                             |  |  |

| EBI_A<16>                 | H14                 |                   | 0             |                             | EBI address                                                             |  |  |

| EBI_A<15>                 | J14                 |                   | 0             |                             | EBI address                                                             |  |  |

| EBI_A<14>                 | R9                  |                   | 0             |                             | EBI address                                                             |  |  |

| SYMBOL <sup>(1)</sup> | LFBGA<br>208<br>PIN | DIGITAL I/O LEVEL | APPL.<br>FUNC | PIN STATE<br>AFTER<br>RESET | DESCRIPTION                 |

|-----------------------|---------------------|-------------------|---------------|-----------------------------|-----------------------------|

| EBI_A<13>             | T9                  |                   | 0             |                             | EBI address                 |

| EBI_A<12>             | U9                  |                   | 0             |                             | EBI address                 |

| EBI_A<11>             | R8                  |                   | 0             |                             | EBI address                 |

| EBI_A<10>             | T8                  |                   | 0             |                             | EBI address                 |

| EBI_A<9>              | U8                  |                   | 0             |                             | EBI address                 |

| EBI_A<8>              | P11                 |                   | 0             |                             | EBI address                 |

| EBI_A<7>              | R7                  |                   | 0             |                             | EBI address                 |

| EBI_A<6>              | P10                 |                   | 0             |                             | EBI address                 |

| EBI_A<5>              | U7                  |                   | 0             |                             | EBI address                 |

| EBI_A<4>              | P9                  |                   | 0             |                             | EBI address                 |

| EBI_A<3>              | T7                  |                   | 0             |                             | EBI address                 |

| EBI_A<2>              | P8                  |                   | 0             |                             | EBI address                 |

| EBI_A<1>              | R6                  |                   | 0             |                             | EBI address                 |

| EBI_A<0>              | U6                  |                   | 0             |                             | EBI address                 |

| EBI_D<15>             | Т6                  | 0-5 VDC tolerant  | I/O           |                             | EBI data                    |

| EBI_D<14>             | U5                  | 0-5 VDC tolerant  | I/O           |                             | EBI data                    |

| EBI_D<13>             | T5                  | 0-5 VDC tolerant  | I/O           |                             | EBI data                    |

| EBI_D<12>             | U4                  | 0-5 VDC tolerant  | I/O           |                             | EBI data                    |

| EBI_D<11>             | T4                  | 0-5 VDC tolerant  | I/O           |                             | EBI data                    |

| EBI_D<10>             | U3                  | 0-5 VDC tolerant  | 1/0           |                             | EBI data                    |

| EBI_D<9>              | T3                  | 0-5 VDC tolerant  | 1/0           |                             | EBI data                    |

| EBI_D<8>              | P7                  | 0-5 VDC tolerant  | 1/0           |                             | EBI data                    |

| EBI_D<7>              | U2                  | 0-5 VDC tolerant  | 1/0           |                             | EBI data                    |

| EBI_D<6>              | P6                  | 0-5 VDC tolerant  | I/O           |                             | EBI data                    |

| EBI_D<5>              | U1                  | 0-5 VDC tolerant  | I/O           |                             | EBI data                    |

| EBI_D<4>              | R5                  | 0-5 VDC tolerant  | I/O           |                             | EBI data                    |

| EBI_D<3>              | T2                  | 0-5 VDC tolerant  | I/O           |                             | EBI data                    |

| EBI_D<2>              | P5                  | 0-5 VDC tolerant  | I/O           |                             | EBI data                    |

| EBI_D<1>              | T1                  | 0-5 VDC tolerant  | I/O           |                             | EBI data                    |

| EBI_D<0>              | R4                  | 0-5 VDC tolerant  | 1/0           |                             | EBI data                    |

| EBI_SDCLKOUT          | J1                  | 0-5 VDC tolerant  | 0             |                             | SDRAM clock                 |

| EBI_CKE<0>            | H4                  |                   | 0             |                             | SDRAM clock enable          |

|                       | T11                 |                   | 0             |                             | SDRAM data mask 1           |

| EBI_DQM<1>            | U11                 |                   | 0             |                             | SDRAM data mask 0           |

| EBI_DQM<0>            |                     |                   | 0             |                             |                             |

| EBI_NRAS              | R10                 |                   |               |                             | SDRAM row address strobe    |

| EBI_NCAS              | R11<br>H2           |                   | 0             |                             | SDRAM column address strobe |

| EBI_NOE               | ПZ                  |                   |               |                             | EBI output enable           |

| Test pins (3 pins)    | P2                  | 0.5.VDC toloroot  | 1/0           |                             | Data input/Data output      |

| TEST_DAT<3>           | B3                  | 0-5 VDC tolerant  | 1/0           |                             | Data input/Data output      |

| TEST_DAT<2>           | A3                  | 0-5 VDC tolerant  | 1/0           |                             | Data input/Data output      |

| TEST_DAT<1>           | B4                  | 0-5 VDC tolerant  | I/O           |                             | Data input/Data output      |

| UART (fixed: 9 pins)  |                     | 0.F.VDC tolorest  |               | I                           |                             |

| UART_IO_NRI           | E14                 | 0-5 VDC tolerant  | 1             |                             |                             |

| UART_DIR_TX           | D10                 | 0.57/00/27        | 0             |                             |                             |

| UART_REQ_RX           | C10                 | 0-5 VDC tolerant  | ı             |                             |                             |

| UART_RST_NRTS         | C11                 | 0.51/00/          | 0             |                             |                             |

| UART_CLK              | D11                 | 0-5 VDC tolerant  | I/O           |                             |                             |

| UART_NOTS    Martinoper   Mart | SYMBOL <sup>(1)</sup> | LFBGA<br>208<br>PIN | DIGITAL I/O LEVEL     | APPL.<br>FUNC | PIN STATE<br>AFTER<br>RESET | DESCRIPTION                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------------|-----------------------|---------------|-----------------------------|------------------------------------------------------------|

| UART_NDTR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | UART_NCTS             | B14                 | 0-5 VDC tolerant      | I             |                             |                                                            |

| Mode Selection prins SAA7750 (fixed: 3 pins)   Mode Selection prins SAA7750 (fixed: 3 pins)   MODE<2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | UART_NDCD             | A15                 | 0-5 VDC tolerant      | I             |                             |                                                            |

| MODE-2>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | UART_NDSR             | B13                 | 0-5 VDC tolerant      | I             |                             |                                                            |

| MODE<2>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | UART_NDTR             | A14                 |                       | 0             |                             |                                                            |

| MODE<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Mode Selection pins S | AA7750 (fix         | xed: 3 pins)          |               |                             |                                                            |

| MODE-clook   M16    0-5 VDC tolerant   1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | MODE<2>               | L16                 | 0-5 VDC tolerant      | - 1           |                             |                                                            |

| Wake-up input pin SAA7750 (fixed: 1 pin)           WAKE_UP         L1         0.5 VDC tolerant         I         Wake up input pin           Reset input pin SAA7750 (fixed: 1 pin)         Image: I                                                                                                                         | MODE<1>               | M15                 | 0-5 VDC tolerant      | - 1           |                             |                                                            |

| Wake up input pin SAA7759 (fixed: 1 pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | MODE<0>               | M16                 | 0-5 VDC tolerant      | - 1           |                             |                                                            |

| Reset input pin SAA7750 (fixed: 1 pin)   NRESET_IN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Wake-up input pin SA  | A7750 (fixe         | d: 1 pin)             |               |                             |                                                            |

| NRESET_IN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | WAKE_UP               | L1                  | 0-5 VDC tolerant      | I             |                             | Wake up input pin                                          |

| NRESET_IN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Reset input pin SAA77 | '50 (fixed: 1       | l pin)                |               |                             |                                                            |

| RESET_OUT         N16         O         Reset output           Reset input pin SSA ∠utio Codec (fixed: 1 pin)         RESET         N15         0.5 VDC tolerant         I         Reset input pin with pull-down for creating Power-On-Reset           DAC SSA Audio Codec (fixed: 4 pins)         VDUTL         P15         A         A nalog left output pin           VOUTR         R16         A         A nalog right output pin           VDDA(DA)         R17         A nalog ground DAC           Headphone Amplifier SSA Audio Codec (fixed: 5 pins)         A nalog ground DAC           WOUTL(HP)         T17         A nalog right output pin           VOUTR(HP)         T16         A nalog right output pin           VOUTR(HP)         T16         A nalog right output pin           VOUTR(HP)         T16         A nalog right output pin           VOUTK(HP)         T16         A nalog right output pin           VOUTK(HP)         T16         A nalog right output pin           VDEALD(HP)         T16         A nalog supply Headphone Driver           VSSA(HP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                       |                     | 1                     | I             |                             | System Reset Input                                         |

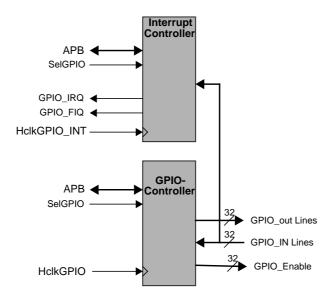

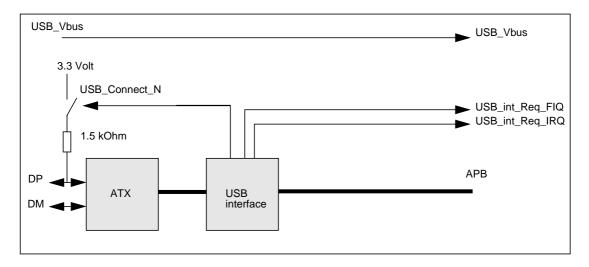

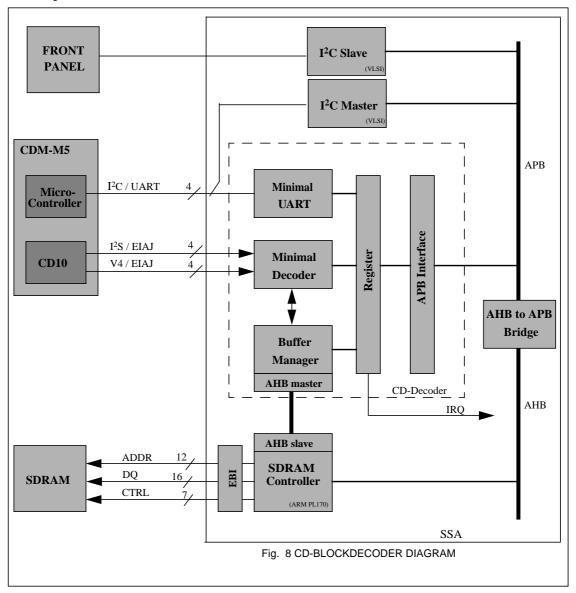

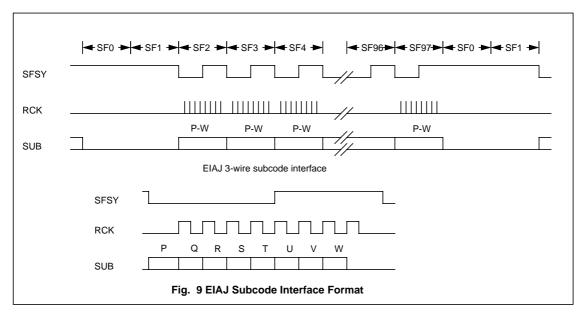

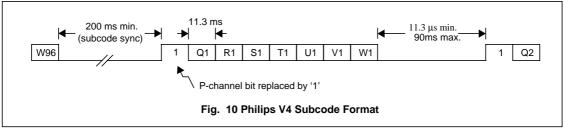

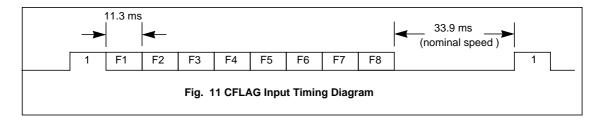

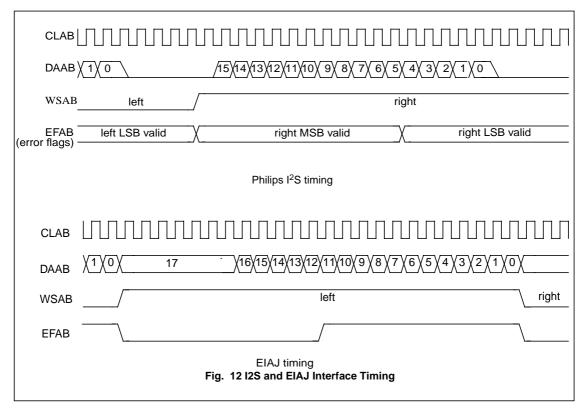

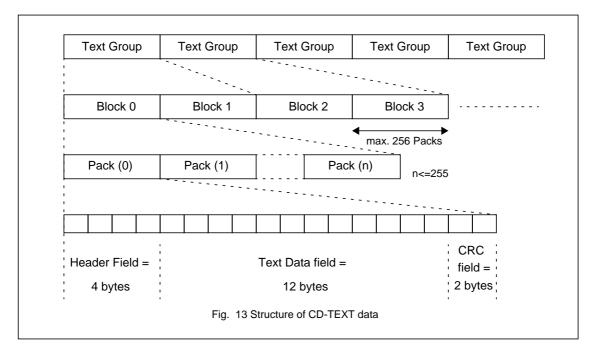

| Reset input pin SSA Audio Codec (fixed: 1 pin)         RESET         N15         0-5 VDC tolerant         I         Reset input pin with pull-down for creating Power-On-Reset           DAC SSA Audio Codec (fixed: 4 pins)           VOUTL         P15         A         A nalog left output pin           VOUTR         R16         A         A nalog right output pin           VOUTA (AP)         R17         A         A nalog ground DAC           Headphone Amplifier SSA Audio Codec (fixed: 5 pins)           VOUTL(HP)         T17         A         A nalog ground DAC           Headphone Amplifier SSA Audio Codec (fixed: 5 pins)           VOUTL(HP)         T17         A         A nalog left output pin           VOUTL(HP)         T16         A         A nalog gregored back           VPDDA(HP)         R15         A         A nalog gregored back pins           VOUTL(HP)         T16         A         A nalog gregored back pins           VODA(HP)         R15         A         A nalog gregored because pins pins           VODA(HP)         M17         A         Left line input           VINL         M17         A         Right line input <td>Reset output pin SAA7</td> <td>7750 (fixed:</td> <td>1 pin)</td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Reset output pin SAA7 | 7750 (fixed:        | 1 pin)                |               |                             |                                                            |