# DOUBLE DATA RATE (DDR) SDRAM

- PC1600 and PC2100 compatible

- VDD =  $+2.5V \pm 0.2V$ , VDDQ =  $+2.5V \pm 0.2V$

- Bi-directional data strobe (DQS) transmitted/ received with data, i.e., source-synchronous data capture (x16 has two one per byte)

- Internal, pipelined double-data-rate (DDR) architecture; two data accesses per clock cycle

- Differential clock inputs (CK and CK#)

- Commands entered on each positive CK edge

- DQS edge-aligned with data for READs; center-aligned with data for WRITEs

- DLL to align DQ and DQS transitions with CK

- Four internal banks for concurrent operation

- Data mask (DM) for masking write data (x16 has two one per byte)

- Programmable burst lengths: 2, 4, or 8

- Auto precharge option

- · Auto Refresh

- Longer lead TSOP for improved reliability (OCPL)

- 2.5V I/O (SSTL 2 compatible)

| Options:                                                                                               | <b>Designation:</b> |

|--------------------------------------------------------------------------------------------------------|---------------------|

| <u>Family</u><br>SpecTek Memory                                                                        | SAA                 |

| <b>Configuration</b>                                                                                   |                     |

| 32 Meg x 4 (8 Meg x 4 x 4 banks)                                                                       | 32M4                |

| 16 Meg x 8 (4 Meg x 8 x 4 banks)                                                                       | 16M8                |

| 8 Meg x 16 (2 Meg x 16 x 4 banks)                                                                      | 8M16                |

| Design ID  DDR 128 Megabit Design (Call SpecTek Sales for details on availability of "x" placeholders) | Yx6x                |

| Voltage and refresh                                                                                    |                     |

| 2.5V, Auto Refresh                                                                                     | V4                  |

| 2.5V, Self or Auto Refresh                                                                             | R4                  |

| Plastic Package – OCPL<br>66-pin TSOP<br>(400 mil width, 0.65mm pin pitch)                             | TL                  |

| <u>Timing – Cycle Time</u>                     |      |

|------------------------------------------------|------|

| 7.5 ns                                         | -75A |

| $10 \text{ns} \ \triangle CI = 2.5 \ (PC1600)$ | -8A  |

Part number example: SAA16M8T95AV4TL-75A (For part numbers prior to December

2004, refer to page 13 for decoding.)

# PIN ASSIGNMENT (TOP VIEW) 66-Pin TSOP

|                                       | VDD NC VDDQ NC DQ0 NC NC NC VDDQ NC NC VDDQ NC NC VDDQ NC NC VDDQ NC NC NC VDD NC NC AC ABAB A1 A10 A2 A2 | VDD<br>DQO<br>VDDQ<br>NC<br>DQ1<br>VSsQ<br>NC<br>DQ3<br>VSSQ<br>NC<br>VDDQ<br>NC<br>VDDQ<br>NC<br>VDDQ<br>NC<br>VDDQ<br>NC<br>NC<br>VDDQ<br>NC<br>AC<br>NC<br>AC<br>AS#<br>AAS#<br>A1<br>A10<br>A2<br>A2 | VDD DQD VDDQ VDDQ DQ1 DQ2 VssQ DQ3 DQ4 VDDQ CSSQ DQ7 NC VDDQ LDQS NC VDDQ LDQS NC VDD BAU LDM# RAS# NC BA0 BA1 A10/AP A0 A1 A2 A3 | 1 • 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 8 9 20 21 22 23 24 25 26 27 28 29 30 31 32 | 66<br>66<br>66<br>55<br>55<br>55<br>55<br>55<br>55<br>55<br>55<br>55<br>55<br>5 | 665 544 53 2 1 1 60 9 8 5 7 6 5 5 4 5 3 2 2 1 1 6 1 5 4 4 1 3 2 2 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | Vss   DQ15   VssQ   DQ14   DQ13   DQ12   DQ11   DQ11   DQ11   DQ9   DQ8   DQ8   DQ8   DNU   VssQ   DDU   VssQ   DDU   VssQ   DDU   VssQ   DDU   VssQ   DDU   CK#   CK   CKE   DC   CK#   A11   A9   A8   A7   A6   A5   A4 | Vss DQ7 VssQ NC DQ6 VbDQ NC DQ5 VssQ NC NC NC NC NC SSQ DNU VREF Vss DM CK# CK CKE NC A11 A9 A8 A7 A6 A5 A4 | Vss NC VssQ NC |

|---------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| VDD VDD VDD III 33 34 III Vss Vss Vss | A3                                                                                                        | A3                                                                                                                                                                                                       |                                                                                                                                   | 32                                                                                     | 3                                                                               | 35                                                                                                | □ A4                                                                                                                                                                                                                       | A4                                                                                                          | A4                                                 |

|                   | 32 Meg x 4          | 16 Meg x 8          | 8 Meg x 16           |

|-------------------|---------------------|---------------------|----------------------|

| Configuration     | 8 Meg x 4 x 4 banks | 4 Meg x 8 x 4 banks | 2 Meg x 16 x 4 banks |

| Refresh Count     | 4K                  | 4K                  | 4K                   |

| Row Addressing    | 4K(A0-A11)          | 4K(A0-A11)          | 4K(A0-A11)           |

| Bank Addressing   | 4 (BA0, BA1)        | 4(BA0, BA1)         | 4(BA0, BA1)          |

| Column Addressing | 2K(A0-A9, A11)      | 1K (A0-A9)          | 512(A0-A8)           |

# www.DataSheet4U.com

#### **GENERAL DESCRIPTION**

The 128Mb DDR SDRAM is a high-speed CMOS, dynamic random-access memory containing 134,217,728 bits. It is internally configured as a quad-bank DRAM.

The 128Mb DDR SDRAM uses a double data rate architecture to achieve high-speed operation. The double data rate architecture is essentially a 2*n*-prefetch architecture with an interface designed to transfer two data words per clock cycle at the I/O pins. A single read or write access for the 128Mb DDR SDRAM effectively consists of a single 2*n*-bit wide, one-clock-cycle data transfer at the internal DRAM core and two corresponding *n*-bit wide, one-half-clock-cycle data transfers at the I/O pins.

A bi-directional data strobe (DQS) is transmitted externally, along with data, for use in data capture at the receiver. DQS is a strobe transmitted by the DDR SDRAM during READs and by the memory controller during WRITEs. DQS is edge-aligned with data for READs and center-aligned with data for WRITEs. The x16 offering has two data strobes, one for the lower byte and one for the upper byte.

The 128Mb DDR SDRAM operates from a differential clock (CK and CK#); the crossing of CK going HIGH and CK# going LOW will be referred to as the positive edge of CK. Commands (address and control signals) are registered at every positive edge of CK. Input data is registered on both edges of DQS, and output data is referenced to both edges of DQS, as well as to both edges of CK.

Read and write accesses to the DDR SDRAM are burst oriented; accesses start at a selected location and continue for a programmed number of locations in a programmed sequence. Accesses begin with the registration of an ACTIVE command, which is then followed by a READ or WRITE command. The address bits registered coincident with the ACTIVE command are used to select the bank and row to be accessed. The address bits registered coincident with the READ or WRITE command are used to select the bank and the starting column location for the burst access.

The DDR SDRAM provides for programmable READ or WRITE burst lengths of 2, 4, or 8 locations. An auto precharge function may be enabled to provide a self-timed row precharge that is initiated at the end of the burst access.

As with standard SDR SDRAMs, the pipelined, multibank architecture of DDR SDRAMs allows for concurrent operation, thereby providing high effective bandwidth by hiding row precharge and activation time.

An auto refresh mode is provided, along with a power-saving power-down mode. All inputs are compatible with the JEDEC Standard for SSTL\_2. All full drive strength outputs are SSTL\_2, Class II compatible.

**NOTE 1:** The functionality and the timing specifications discussed in this data sheet are for the DLL-enabled mode of operation.

NOTE 2: Throughout the data sheet, the various figures and text refer to DQs as "DQ." The DQ term is to be interpreted as any and all DQ collectively, unless specifically stated otherwise.

Additionally, the x16 is divided in to two bytes—the

Additionally, the x16 is divided in to two bytes — the lower byte and upper byte. For the lower byte (DQ0 through DQ7) DM refers to LDM and DQS refers to LDQS; and for the upper byte (DQ8 through DQ15) DM refers to UDM and DQS refers to UDQS.

#### ABSOLUTE MAXIMUM RATINGS\*

#### Disclaimer:

Except as specifically provided in this document, SpecTek makes no warranties, expressed or implied, including, but not limited to, any implied warranties of merchantability or fitness for a particular purpose.

Any claim against SpecTek must be made within 1 year from the date of shipment from SpecTek, and SpecTek has no liability thereafter. Any liability is limited to replacement of the defective items or return of amounts paid for defective items (at buyer's election). In no event will SpecTek be responsible for special, indirect, consequential or incidental damages, even if SpecTek has been advised for the possibility of such damages. SpecTek's liability from any cause pursuant to this specification shall be limited to general monetary damages in an amount not to exceed the total purchase price of the products covered by this specification, regardless of the form in which legal or equitable action may be brought against SpecTek.

## www.DataSheet4U.com

#### DC ELECTRICAL CHARACTERISTICS AND OPERATING CONDITIONS

$(25^{\circ}C \leq T_{\rm A} \leq +70^{\circ}C; \ V_{\rm DD} = +2.5V \ \pm 0.2V, \ V_{\rm DD}Q = +2.5V \ \pm 0.2V)$

| PARAMETER/CONDITION                                                             | SYMBOL          | MIN              | MAX             | UNITS | NOTES  |

|---------------------------------------------------------------------------------|-----------------|------------------|-----------------|-------|--------|

| Supply Voltage                                                                  | V <sub>DD</sub> | 2.3              | 2.7             | V     | 41     |

| I/O Supply Voltage                                                              | VddQ            | 2.3              | 2.7             | V     | 41, 44 |

| I/O Reference Voltage                                                           | Vref            | 0.49 X VDDQ      | 0.51 X VDDQ     | V     | 6, 44  |

| I/O Termination Voltage (system)                                                | VTT             | Vref – 0.04      | Vref – 0.04     | V     | 7, 44  |

| Input High (Logic 1) Voltage                                                    | VIH (DC)        | $V_{REF} + 0.15$ | $V_{DD} + 0.3$  | V     | 28     |

| Input Low (Logic 0) Voltage                                                     | VIL (DC)        | -0.3             | Vref – 0.15     | V     | 28     |

| Clock Input Voltage Level; CK and CK#                                           | Vin             | -0.3             | $V_{DDQ} + 0.3$ | V     |        |

| Clock Input Differential Voltage; CK and CK#                                    | Vid             | 0.36             | $V_{DDQ} + 0.6$ | V     | 8      |

| Clock Input Crossing Point Voltage; CK and CK#                                  | Vix             | 1.15             | 1.35            | V     | 9      |

| INPUT LEAKAGE CURRENT                                                           | II              | -2               | 2               | μA    |        |

| Any input, $0V \le V_{IN} \le V_{DD}$ , $V_{REF}$ pin $0V \le V_{IN} \le 1.35V$ |                 |                  |                 |       |        |

| (All other pins not under test = $0V$ )                                         |                 |                  |                 |       |        |

| OUTPUT LEAKAGE CURRENT                                                          | Ioz             | -7               | 7               | μA    |        |

| (DQs are disabled; $0V \le V_{OUT} \le V_{DD}Q$ )                               |                 |                  |                 |       |        |

| OUTPUT LEVELS:                                                                  | Іон             | -16.8            |                 | mA    | 37, 39 |

| Full drive option - x4, x8, x16                                                 | IOL             | 16.8             |                 | mA    |        |

| High Current (Vout = VddQ-0.373V, minimum Vref, minimum                         | IOL             | 10.8             |                 | ША    |        |

| V <sub>TT</sub> )                                                               |                 |                  |                 |       |        |

| Low Current (Vout = 0.373V, maximum Vref,maximum Vtt)                           | _               |                  |                 |       | 20.20  |

| OUTPUT LEVELS: Reduced drive option - x16 only                                  | IOHR            | -9               |                 | mA    | 38, 39 |

| High Current (Vout = VDDQ-0.763V, minimum VREF, minimum                         | IOLR            | 9                |                 | mA    |        |

| VTT) Low Current (Vout = 0.763V, maximum Vref,maximum VTT)                      |                 |                  |                 |       |        |

#### **AC INPUT OPERATING CONDITIONS**

$(25^{\circ}C \leq T_{A} \leq +~70^{\circ}C;~V_{DD} = +2.5V~\pm 0.2V,~V_{DD}Q = +2.5V~\pm 0.2V)$

| PARAMETER/CONDITION                            | SYMBOL    | MIN              | MAX               | UNIT<br>S | NOTES         |

|------------------------------------------------|-----------|------------------|-------------------|-----------|---------------|

| Input High (Logic 1) Voltage                   | VIH (AC)  | VREF + 0.310     |                   | V         | 14, 28,<br>40 |

| Input Low (Logic 0) Voltage                    | VIL (AC)  |                  | VREF - 0.310      | V         | 14, 28,<br>40 |

| Clock Input Differential Voltage; CK and CK#   | VID (AC)  | 0.7              | $V_{DDQ} + 0.6$   | V         | 8             |

| Clock Input Crossing Point Voltage; CK and CK# | Vix (ac)  | 0.5 X VDDQ - 0.2 | 0.5  X VDDQ + 0.2 | V         | 9             |

| I/O Reference Voltage                          | VREF (AC) | 0.49 X VDDQ      | 0.51 X VDDQ       | V         | 6             |

#### **CAPACITANCE** (x4, x8)

$(25^{\circ}C \le T_A \le +70^{\circ}C; V_{DD}Q = +2.5V \pm 0.2V, V_{DD} = +2.5V \pm 0.2V)$

| PARAMETER                                    | SYMBOL | MIN | MAX  | UNITS | NOTES |

|----------------------------------------------|--------|-----|------|-------|-------|

| Delta Input/Output Capacitance: DQs, DQS, DM | DCio   |     | 0.50 | pF    | 24    |

| Delta Input Capacitance: Command and Address | DC11   |     | 0.50 | pF    | 29    |

| Delta Input Capacitance: CK, CK#             | DCI2   |     | 0.25 | pF    | 29    |

| Delta Input Capacitance: DQs, DQS, DM        | Cio    | 4.0 | 5.0  | pF    |       |

| Input Capacitance: Command and Address       | C11    | 2.0 | 3.0  | pF    |       |

| Input Capacitance: CK, CK#                   | Cı2    | 2.0 | 3.0  | pF    |       |

| Input Capacitance: CKE                       | CI3    | 2.0 | 3.0  | pF    |       |

# IDD SPECIFICATIONS AND CONDITIONS (x4, x8) $(25^{\circ}\text{C} \le T_A \le +70^{\circ}\text{C}; V_{DDQ} = +2.5V \pm 0.2V, V_{DD} = +2.5V \pm 0.2V)$

| PARAMETER/CONDITION                                                                                    | ,                          | SYMBOL | -75 | -8  | UNITS | NOTES   |

|--------------------------------------------------------------------------------------------------------|----------------------------|--------|-----|-----|-------|---------|

| OPERATING CURRENT: One bank; Active-Precharge;                                                         | $^{t}RC = {}^{t}RC (MIN);$ | Idd0   | 105 | 100 | mA    | 22, 48  |

| <sup>t</sup> CK = <sup>t</sup> CK (MIN); DQ, DM, and DQS inputs changing once per clock                |                            |        |     |     |       |         |

| cycle; Address and control inputs changing once every two clock cycles;                                |                            |        |     |     |       |         |

| OPERATING CURRENT: One bank; Active-Read-Prech                                                         |                            | Idd1   | 120 | 115 | mA    | 22, 48  |

| ${}^{t}RC = {}^{t}RC \text{ (MIN)}; {}^{t}CK = {}^{t}CK \text{ (MIN)}; IOUT = 0mA; Address$            | ss and control             |        |     |     |       |         |

| inputs changing once per clock cycle                                                                   |                            |        |     |     |       |         |

| PRECHARGE POWER-DOWN STANDBY CURRENT:                                                                  | All banks idle;            | Idd2p  | 10  | 10  | mA    | 23, 32, |

| Power-down mode; <sup>t</sup> CK = <sup>t</sup> CK(MIN); CKE=LOW;                                      |                            |        |     |     |       | 50      |

| IDLE STANDBY CURRENNT: CS# = HIGH; All banks                                                           |                            | Idd2n  | 50  | 45  | mA    | 51      |

| (MIN); CKE = HIGH; Address and other control inputs ch                                                 | nanging once per           |        |     |     |       |         |

| clock cycle. VIN = VREF for DQ, DQS, and DM                                                            |                            |        |     |     |       |         |

| ACTIVE POWER-DOWN STANDBY CURRENT: One                                                                 | bank active;               | IDD3p  | 18  | 18  | mA    | 23, 32, |

| Power-down mode; ${}^{t}CK = {}^{t}CK \text{ (MIN)}$ ; $CKE = LOW$                                     |                            |        |     |     |       | 50      |

| ACTIVE STANDBY CURRENT: CS# = HIGH; CKE = 1                                                            |                            | Idd3n  | 50  | 45  | mA    | 22      |

| Active-Precharge; ${}^{t}RC = {}^{t}RAS (MAX)$ ; ${}^{t}CK = {}^{t}CK (MIN)$ ;                         |                            |        |     |     |       |         |

| DQS inputs changing twice per clock cycle; Address and o                                               | other control              |        |     |     |       |         |

| inputs changing once per clock cycle.                                                                  |                            |        |     |     |       |         |

| OPERATING CURRENT: Burst = 2; Reads; Continuous                                                        |                            | Idd4r  | 120 | 110 | mA    | 22, 48  |

| active; Address and control inputs changing once per clock                                             | k cycle; 'CK =             |        |     |     |       |         |

| $^{t}CK (MIN); IOUT = 0mA$                                                                             |                            |        |     |     |       |         |

| OPERATING CURRENT: Burst = 2; Writes; Continuous                                                       |                            | Idd4w  | 120 | 110 | mA    | 22      |

| active; Address and control inputs changing once per clock                                             |                            |        |     |     |       |         |

| <sup>t</sup> CK (MIN); DQ, DM, and DQS inputs changing twice per clock cycle                           |                            |        |     |     |       |         |

|                                                                                                        | C = tRFC (MIN)             | Idd5   | 250 | 225 | mA    | 22, 50  |

| SELF REFRESH CURRENT (Part number 'R' only)                                                            |                            | Idd7   | 2   | 2   | mA    | 11      |

| OPERATING CURRENT: Four bank interleaving READs                                                        |                            | Idd8   | 330 | 285 | mA    | 22, 49  |

| auto precharge, <sup>t</sup> RC = <sup>t</sup> RC (MIN); <sup>t</sup> CK = <sup>t</sup> RC (MIN); Addi |                            |        |     |     |       |         |

| inputs change only during Active, READ, or WRITE com-                                                  | mands.                     |        |     |     |       |         |

#### **CAPACITANCE** (x16)

$(25^{\circ}\text{C} \le \text{T}_{\text{A}} \le +70^{\circ}\text{C}; \text{V}_{\text{DD}}\text{Q} = +2.5\text{V} \pm 0.2\text{V}, \text{V}_{\text{DD}} = +2.5\text{V} \pm 0.2\text{V})$

| PARAMETER                                            | SYMBOL | MIN | MAX  | UNITS | NOTES |

|------------------------------------------------------|--------|-----|------|-------|-------|

| Delta Input/Output Capacitance: DQ0 – DQ7, LDQS, LDM | DCIOL  |     | 0.50 | pF    | 24    |

| Delta Input/Output Capacitance: DQ8-DQ15, UDQS, UDM  | DCiou  | -   | 0.50 | pF    | 24    |

| Delta Input Capacitance: Command and Address         | DC11   | -   | 0.50 | pF    | 29    |

| Delta Input Capacitance: CK, CK#                     | DCI2   | -   | 0.25 | pF    | 29    |

| Input/Output Capacitance: DQs, LDQS, UDQS, LDM, UDM  | Cio    | 4.0 | 5.0  | pF    |       |

| Input Capacitance: Command and Address               | C11    | 2.0 | 3.0  | pF    |       |

| Input Capacitance: CK, CK#                           | Ci2    | 2.0 | 3.0  | pF    |       |

| Input Capacitance: CKE                               | CI3    | 2.0 | 3.0  | pF    |       |

#### **IDD SPECIFICATIONS AND CONDITIONS (x16)**

$(25^{\circ}C \le T_A \le +70^{\circ}C; V_{DD}Q = +2.5V \pm 0.2V, V_{DD} = +2.5V \pm 0.2V)$

| PARAMETER/CONDITION                                                                                                   | SYMBOL | -75 | -8  | UNITS | NOTES   |

|-----------------------------------------------------------------------------------------------------------------------|--------|-----|-----|-------|---------|

| OPERATING CURRENT: One bank; Active-Precharge; <sup>t</sup> RC = <sup>t</sup> RC (MIN);                               | Idd0   | 115 | 105 | mA    | 22, 48  |

| <sup>t</sup> CK = <sup>t</sup> CK (MIN); DQ, DM, and DQS inputs changing once per clock                               |        |     |     |       |         |

| cycle; Address and control inputs changing once every two clock cycles;                                               |        |     |     |       |         |

| OPERATING CURRENT: One bank; Active-Read-Precharge; Burst = 2;                                                        | IDD1   | 140 | 115 | mA    | 22, 48  |

| <sup>t</sup> RC = <sup>t</sup> RC (MIN); <sup>t</sup> CK = <sup>t</sup> CK (MIN); IOUT = 0mA; Address and control     |        |     |     |       |         |

| inputs changing once per clock cycle                                                                                  |        |     |     |       |         |

| PRECHARGE POWER-DOWN STANDBY CURRENT: All banks idle;                                                                 | Idd2p  | 10  | 10  | mA    | 23, 32, |

| Power-down mode; <sup>t</sup> CK = <sup>t</sup> CK(MIN); CKE=LOW;                                                     |        |     |     |       | 50      |

| IDLE STANDBY CURRENNT: CS# = HIGH; All banks idle; <sup>t</sup> CK = <sup>t</sup> CK                                  | Idd2n  | 50  | 45  | mA    | 51      |

| (MIN); CKE = HIGH; Address and other control inputs changing once per                                                 |        |     |     |       |         |

| clock cycle. VIN = VREF for DQ, DQS, and DM                                                                           |        |     |     |       |         |

| ACTIVE POWER-DOWN STANDBY CURRENT: One bank active;                                                                   | Idd3p  | 18  | 18  | mA    | 23, 32, |

| Power-down mode; <sup>t</sup> CK = <sup>t</sup> CK (MIN); CKE = LOW                                                   |        |     |     |       | 50      |

| ACTIVE STANDBY CURRENT: CS# = HIGH; CKE = HIGH; One bank;                                                             | Idd3n  | 50  | 45  | mA    | 22      |

| Active-Precharge; <sup>t</sup> RC = <sup>t</sup> RAS (MAX); <sup>t</sup> CK = <sup>t</sup> CK (MIN); DQ, DM, and      |        |     |     |       |         |

| DQS inputs changing twice per clock cycle; Address and other control                                                  |        |     |     |       |         |

| inputs changing once per clock cycle.                                                                                 |        |     |     |       |         |

| OPERATING CURRENT: Burst = 2; Reads; Continuous burst; One bank                                                       | Idd4r  | 170 | 160 | mA    | 22, 48  |

| active; Address and control inputs changing once per clock cycle; <sup>t</sup> CK =                                   |        |     |     |       |         |

| $^{t}CK (MIN); IOUT = 0mA$                                                                                            |        |     |     |       |         |

| OPERATING CURRENT: Burst = 2; Writes; Continuous burst; One bank                                                      | Idd4w  | 150 | 145 | mA    | 22      |

| active; Address and control inputs changing once per clock cycle; <sup>t</sup> CK =                                   |        |     |     |       |         |

| <sup>t</sup> CK (MIN); DQ, DM, and DQS inputs changing twice per clock cycle                                          |        |     |     |       |         |

| AUTO REFRESH CURRENT TRC = tRFC (MIN)                                                                                 | Idd5   | 255 | 225 | mA    | 22, 50  |

| SELF REFRESH CURRENT (Part number 'R' only)                                                                           | Idd7   | 2   | 2   | mA    | 11      |

| OPERATING CURRENT: Four bank interleaving READs (BL = 4) with                                                         | Idd8   | 330 | 285 | mA    | 22, 49  |

| auto precharge, <sup>t</sup> RC = <sup>t</sup> RC (MIN); <sup>t</sup> CK = <sup>t</sup> RC (MIN); Address and control |        |     |     |       |         |

| inputs change only during Active, READ, or WRITE commands.                                                            |        |     |     |       |         |

### ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS

$(25^{\circ}C \le T_A \le +70^{\circ}C; V_{DD}Q = +2.5V \pm 0.2V, V_{DD} = +2.5V \pm 0.2V)$

| AC CHARACTERISTICS                                    |                                           | -7              | 75     |                 | 8      |                 |        |

|-------------------------------------------------------|-------------------------------------------|-----------------|--------|-----------------|--------|-----------------|--------|

| PARAMETER                                             | SYMBOL                                    | MIN             | MAX    | MIN             | MAX    | UNITS           | NOTES  |

| Access window of DQs from CK/CK#                      | <sup>t</sup> AC                           | -0.75           | +0.75  | -0.8            | +0.8   | ns              |        |

| CK high-level width                                   | <sup>t</sup> CH                           | 0.45            | 0.55   | 0.45            | 0.55   | <sup>t</sup> CK | 30     |

| CK low-level width                                    | <sup>t</sup> CL                           | 0.45            | 0.55   | 0.45            | 0.55   | <sup>t</sup> CK | 30     |

| Clock cycle time CL = 2.5                             | <sup>t</sup> CK (2.5)                     | 7.5             | 12     | 10              | 12     | ns              | 52     |

|                                                       |                                           |                 |        |                 |        |                 |        |

| DQ and DM input hold time relative to DQS             | <sup>t</sup> DH                           | 0.5             |        | 0.6             |        | ns              | 26, 31 |

| DQ and DM input setup time relative to DQS            | <sup>t</sup> DS                           | 0.5             |        | 0.6             |        | ns              | 26, 31 |

| DQ and DM input pulse width (for each input)          | <sup>t</sup> DIPW                         | 1.75            |        | 2               |        | ns              | 31     |

| Access window of DQS from CK/CK#                      | <sup>t</sup> DQSCK                        | -0.75           | +0.75  | -0.8            | +0.8   | ns              |        |

| DQS input high pulse width                            | <sup>t</sup> DQSH                         | 0.35            |        | 0.35            |        | <sup>t</sup> CK |        |

| DQS input low pulse width                             | <sup>t</sup> DQSL                         | 0.35            |        | 0.35            |        | <sup>t</sup> CK |        |

| DQS-DQ skew, DQS to last DQ valid, per group, per     | <sup>t</sup> DQSQ                         |                 | 0.5    |                 | 0.6    | ns              | 25, 26 |

| access                                                |                                           |                 |        |                 |        |                 |        |

| DQS-DQ skew, first DQS to last DQ valid, per access   | <sup>t</sup> DQSQA                        |                 | 0.7    |                 | 0.8    | ns              | 36     |

| Write command to first DQS latching transition        | <sup>t</sup> DQSS                         | 0.75            | 1.25   | 0.75            | 1.25   | <sup>t</sup> CK |        |

| DQS falling edge to CK rising – setup time            | <sup>t</sup> DSS                          | 0.2             |        | 0.2             |        | <sup>t</sup> CK |        |

| DQS falling edge from CK rising – hold time           | <sup>t</sup> DSH                          | 0.2             |        | 0.2             |        | <sup>t</sup> CK |        |

| Half clock period                                     | <sup>t</sup> HP                           | tCH,            |        | tCH,            |        | ns              | 34     |

|                                                       |                                           | <sup>t</sup> CL |        | <sup>t</sup> CL |        |                 |        |

| Data-out high-impedance window from CK/CK#            | <sup>t</sup> HZ                           | -0.75           | +0.75  | -0.8            | +0.8   | ns              | 18     |

| Data-out low-impedance window from CK/CK#             | <sup>t</sup> LZ                           | -0.75           | +0.75  | -0.8            | +0.8   | ns              | 18     |

| Address and control input hold time (fast slew rate)  | $^{ m t} { m IH}_{ m f}$                  | .90             |        | 1.1             |        | ns              | 14     |

| Address and control input setup time (fast slew rate) | ${}^{\mathrm{t}}\mathrm{IS}_{\mathrm{f}}$ | .90             |        | 1.1             |        | ns              | 14     |

| Address and control input hold time (slow slew rate)  | <sup>t</sup> IH <sub>s</sub>              | 1               |        | 1.1             |        | ns              | 14     |

| Address and control input setup time (slow slew rate) | <sup>t</sup> IS <sub>s</sub>              | 1               |        | 1.1             |        | ns              | 14     |

| LOAD MODE REGISTER command cycle time                 | <sup>t</sup> MRD                          | 15              |        | 16              |        | ns              |        |

| DQ-DQS hold, DQS to first DQ to go non-valid, per     | tQH                                       | tHP -           |        | tHP -           |        | ns              | 25, 26 |

| access                                                |                                           | tQHS            |        | tQHS            |        |                 |        |

| Data hold skew factor                                 | <sup>t</sup> QHS                          |                 | 0.75   |                 | 1      | ns              |        |

| ACTIVE to PRECHARGE command                           | <sup>t</sup> RAS                          | 45              | 16,000 | 50              | 16,000 | ns              | 35     |

| ACTIVE to READ with Auto precharge command            | <sup>t</sup> RAP                          |                 |        |                 |        | ns              | 46     |

| ACTIVE to ACTIVE/AUTO REFRESH command                 | <sup>t</sup> RC                           | 65              |        | 70              |        | ns              |        |

| period                                                |                                           |                 |        |                 |        |                 |        |

| AUTO REFRESH command period                           | <sup>t</sup> RFC                          | 75              |        | 80              |        | ns              | 50     |

| ACTIVE to READ or WRITE delay                         | <sup>t</sup> RCD                          | 20              |        | 20              |        | ns              |        |

| PRECHARGE command period                              | <sup>t</sup> RP                           | 20              |        | 20              |        | ns              |        |

| DQS read preamble                                     | <sup>t</sup> RPRE                         | 0.9             | 1.1    | 0.9             | 1.1    | <sup>t</sup> CK | 42     |

| DQS read postamble                                    | <sup>t</sup> RPST                         | 0.4             | 0.6    | 0.4             | 0.6    | <sup>t</sup> CK |        |

| ACTIVE bank a to ACTIVE bank b command                | <sup>t</sup> RRD                          | 15              |        | 15              |        | ns              |        |

#### ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS,

(continued)

| AC CHARACTERISTICS                                         |                    | -     | 75    | -       | 8     |                 |        |

|------------------------------------------------------------|--------------------|-------|-------|---------|-------|-----------------|--------|

| PARAMETER                                                  | SYMBOL             | MIN   | MAX   | MIN     | MAX   | UNITS           | NOTES  |

| DQS write preamble                                         | <sup>t</sup> WPRE  | 0.25  |       | 0.25    |       | <sup>t</sup> CK |        |

| DQS write preamble setup time                              | <sup>t</sup> WPRES | 0     |       | 0       |       | ns              | 20, 21 |

| DQS write postamble                                        | <sup>t</sup> WPST  | 0.4   | 0.6   | 0.4     | 0.6   | <sup>t</sup> CK | 19     |

| Write recovery time                                        | <sup>t</sup> WR    | 15    |       | 15      |       | ns              |        |

| Internal WRITE to READ command delay                       | <sup>t</sup> WTR   | 1     |       | 1       |       | <sup>t</sup> CK |        |

| Data valid output window                                   | na                 | tQH - | tDQSQ | tQH - 1 | tDQSQ | ns              | 25     |

| REFRESH to REFRESH command interval                        | <sup>t</sup> REFC  |       | 140.6 |         | 140.6 | μs              | 23     |

| Average periodic refresh interval                          | <sup>t</sup> REFI  |       | 15.6  |         | 15.6  | μs              | 23     |

| Terminating voltage delay to Vdd                           | tVTD               | 0     |       | 0       |       | ns              |        |

| Exit SELF REFRESH to non-READ command (Part number R only) | <sup>t</sup> XSNR  | 75    |       | 80      |       | ns              |        |

| Exit SELF REFRESH to READ command (Part number R only)     | <sup>t</sup> XSRD  | 200   |       | 200     |       | <sup>t</sup> CK |        |

## 128Mb: x4, x8, x16 DDR SDRAM

#### **NOTES**

- 1. All voltages referenced to Vss.

- Tests for AC timing, IDD, and electrical AC and DC characteristics may be conducted at nominal reference/supply voltage levels, but the related specifications and device operation are guaranteed for the full voltage range specified.

- Outputs measured with equivalent load: properly initialized, and is averaged at the defined cycle rate.

- 4. AC timing and IDD tests may use a VIL- to-VIH swing of up to 1.5V in the test environment, but input timing is still referenced to VREF (or to the crossing point for CK/CK#), and parameter specifications are guaranteed for the specified AC input levels under normal use conditions. The minimum slew rate for the input signals used to test the device is 1V/ns in the range between VIL(AC) and VIH(AC).

- 5. The AC and DC input level specifications areas defined in the SSTL\_2 Standard (i.e., the receiver will effectively switch as a result of the signal crossing the AC input level, and will remain in that state as long as the signal does not ring back above [below] the DC input LOW [HIGH] level).

- 6. VREF is expected to equal VDDQ/2 of the transmitting device and to track variations in the DC level of the same. Peak-to-peak noise (non-common mode) on VREF may not exceed ±2 percent of the DC value. Thus, from VDDQ/2, VREF is allowed ±25mV for DC error and an additional ±25mV for AC noise.

- 7. VTT is not applied directly to the device. VTT is a system supply for signal termination resistors, is expected to be set equal to VREF and must track variations in the DC level of VREF.

- 8. VID is the magnitude of the difference between the input level on CK and the input level on CK#.

- 9. The value of Vix is expected to equal VddQ/2 of the transmitting device and must track variations in the DC level of the same.

- 10. Idd is dependent on output loading and cycle rates. Specified values are obtained with minimum cycle time at CL = 2.5 for -7.5 and -8 with the outputs open.

- 11. Enables on-chip refresh and address counters.

- 12. IDD specifications are tested after the device is properly initialized, and is averaged at the defined cycle rate.

- 13. This parameter is sampled. VDD =  $\pm 2.5V \pm 0.2V$ , VDDQ =  $\pm 2.5V \pm 0.2V$ , VREF = Vss, f = 100 MHz,  $T_A = 25^{\circ}C$ , VOUT(DC) = VDDQ/2, VOUT (peak to peak) = 0.2V. DM input is grouped with I/O pins, reflecting the fact that they are matched in loading.

- 14. Command/Address input slew rate = 0.5V/ns. For -7 and -75 with slew rates 1V/ns and faster, <sup>t</sup>IS and <sup>t</sup>IH are reduced to 900ps. If the slew rate is less than 0.5V/ns, timing must be derated: <sup>t</sup>IS has an additional 50ps per each 100mV/ns reduction in slew rate from the 500mV/ns. <sup>t</sup>IH has 0ps added, that is, it remains constant. If the slew rate exceeds 4.5V/ns, functionality is uncertain.

- 15. The CK/CK# input reference level (for timing referenced to CK/CK#) is the point at which CK and CK# cross; the input reference level for signals other than CK/CK# is VREF.

- 16. Inputs are not recognized as valid until VREF stabilizes. Exception: during the period before VREF stabilizes, CKE ≤ 0.3 x VDDQ is recognized as LOW.

- 17. The output timing reference level, as measured at the timing reference point indicated in Note 3, is

- 18. <sup>t</sup>HZ and <sup>t</sup>LZ transitions occur in the same access time windows as valid data transitions. These parameters are not referenced to a specific voltage level, but specify when the device output is no longer driving (HZ) or begins driving (LZ).

- 19. The maximum limit for this parameter is not a device limit. The device will operate with a greater value for this parameter, but system performance (bus turnaround) will degrade accordingly.

- 20. This is not a device limit. The device will operate with a negative value, but system performance could be degraded due to bus turnaround.

- 21. It is recommended that DQS be valid (HIGH or LOW) on or before the WRITE command. The case shown (DQS going from High-Z to logic LOW) applies when no WRITEs were previously in progress on the bus. If a previous WRITE was in progress, DQS could be HIGH during this time, depending on tDQSS.

## 128Mb: x4, x8, x16 DDR SDRAM

#### NOTES, continued

- 22. MIN ( <sup>t</sup>RC or <sup>t</sup>RFC) for IDD measurements is the smallest multiple of <sup>t</sup>CK that meets the minimum absolute value for the respective parameter. <sup>t</sup>RAS (MAX) for IDD measurements is the largest multiple of <sup>t</sup>CK that meets the maximum absolute value for <sup>t</sup>RAS.

- 23. The refresh period 64ms. This equates to an average refresh rate of 15.625μs. However, an AUTO REFRESH command must be asserted at least once every 140.6μs; burst refreshing or posting by the DRAM controller greater than eight refresh cycles is not allowed.

- 24. The I/O capacitance per DQS and DQ byte/group will not differ by more than this maxi-or mum amount for any given device.

- 25. The valid data window is derived by achieving other specifications 'HP ( 'CK/2), 'DQSQ, and 'QH ( 'QH = 'HP 'QHS). The data valid window derates directly proportional with the clock duty cycle and a practical data valid window can be derived. The clock is allowed a maximum duty cycle variation of 45/55. Functionality is uncertain when operating beyond a 45/55 ratio. The data valid window derating curves are provided below for duty cycles ranging between 50/50 and 45/55.

- 26. Referenced to each output group: x4 = DQS with DQ0-DQ3; x8 = DQS with DQ0-DQ7; x16 = LDQS with DQ0-DQ7 and UDQS with DQ8-DQ15.

- 27. This limit is actually a nominal value and does not result in a fail value. CKE is HIGH during REFRESH command period ( 'RFC [MIN]) else CKE is LOW (i.e., during standby).

- 28. To maintain a valid level, the transitioning edge of the input must:

- a) Sustain a constant slew rate from the Current AC level through to the target AC level, VIL(AC) VIH(AC).

- b) Reach at least the target AC level.

- c) After the AC target level is reached, continue to maintain at least the target DC level, VIL(DC) or VIH(DC).

- 29. The Input capacitance per pin group will not differ by more than this maximum amount for any given device.

- 30. CK and CK# input slew rate must be >1V/ns.

- 31. DQ and DM input slew rates must not deviate from DQS by more than 10%. If the DQ/DM/DQS slew rate is less than 0.5V/ns, timing must be derated: 50ps must be added to <sup>t</sup>DS and <sup>t</sup>DH for each 100mv/ns reduction in slew rate. If slew rate exceeds 4V/ns, functionality is uncertain.

- 32. VDD must not vary more than 4% if CKE is not active while any bank is active.

- 33. The clock is allowed up to ±150ps of jitter. Each timing parameter is allowed to vary by the same amount.

- 34. <sup>t</sup>HP min is the lesser of <sup>t</sup>CL minimum and <sup>t</sup>CH minimum actually applied to the device CK and CK/inputs, collectively during bank active.

- 35. READs and WRITEs with auto precharge are not allowed to be issued until <sup>t</sup>RAS (MIN) can be satisfied prior to the internal precharge command being issued.

- Applies to x16 only. First DQS (LDQS or UDQS) to transition to last DQ (DQ0-DQ15) to transition valid. Initial JEDEC specifications suggested this to be same as <sup>t</sup>DOSO.

- 37. Note 37 is not used.

- 38. Note 38 is not used.

- 39. Note 39 is not used.

- 40. VIH overshoot: VIH(MAX) = VDDQ+1.5V for a pulse width ≤ 3ns and the pulse width can not be greater than 1/3 of the cycle rate. VIL undershoot: VIL(MIN) = -1.5V for a pulse width ≤ 3ns and the pulse width can not be greater than 1/3 of the cycle rate.

- 41. VDD and VDDQ must track each other.

- 42. Note 42 is not used.

- 43. Note 43 is not used.

- 44. During initialization, VddQ, Vtt, and Vref must be equal to or less than Vdd + 0.3V. Alternatively, Vtt may be 1.35V maximum during power up, even if Vdd /VddQ are 0 volts, provided a minimum of 42 ohms of series resistance is used between the Vtt supply and the input pin.

## 128Mb: x4, x8, x16 **DDR SDRAM**

NOTES, continued

- 45. Note 45 is not used.

- 46.  ${}^{t}RAP \ge {}^{t}RCD$ .

- 47. Note  $\overline{47}$  is not used.

- 48. Random addressing changing 50% of data changing at every transfer.

- 49. Random addressing changing 100% of data changing at every transfer.

- 50. CKE must be active (high) during the entire time a refresh Whenever the operating frequency is altered, not command is executed. That is, from the time the AUTO

- REFRESH command is registered, CKE must be active at each rising clock edge, until <sup>t</sup>REF later.

- 51. IDD2N specifies the DQ, DQS, and DM to be driven to a valid high or low logic level. IDD2Q is similar to IDD2F except IDD2Q specifies the address and control inputs to remain stable. Although IDD2F, IDD2N, and IDD2Q are similar, IDD2F is "worst case."

- including jitter, the DLL is required to be reset. This is followed by 200 clock cycles.

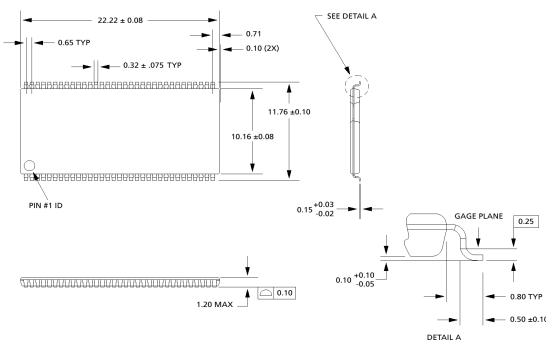

#### 66-PIN PLASTIC TSOP (400 mil)

**NOTE:** 1. All dimensions in millimeters  $\frac{MAX}{MIN}$  or typical here noted.

2. Package width and length do not include mold protrusion; allowable mold protrusion is 0.25mm per side.

ODTIONO

#### PART NUMBERS FOR PRODUCT PRIOR TO DECEMBER 2004

NA DIZING

| OPTIONS         | MARKING |

|-----------------|---------|

| • Configuration |         |

| • | Configuration                                          |        |

|---|--------------------------------------------------------|--------|

|   | 32 Meg x 4 (8 Meg x 4 x 4 banks)                       | S40032 |

|   | 16 Meg x 8 (4 Meg x 8 x 4 banks)                       | S80016 |

|   | 8 Meg x 16 (2 Meg x 16 x 4 banks)                      | S16008 |

| • | Voltage and refresh                                    |        |

|   | 2.5V, Auto Refresh                                     | VH     |

|   | 2.5V, Self or Auto Refresh                             | RH     |

| • | Parent Device Configuration                            |        |

|   | 32 Meg x 4                                             | 8      |

|   | 16 Meg x 8                                             | 7      |

|   | 8 Meg x 16                                             | 9      |

| • | Plastic Package – OCPL                                 |        |

|   | 66-pin TSOP                                            | TW     |

|   | (400 mil width, 0.65mm pin pitch)                      |        |

| • | Timing – Cycle Time                                    |        |

|   | 7.5 ns @ CL = $2.5$ (PC2100)                           | -75A   |

|   | $10 \text{ns} \ @ \ \text{CL} = 2.5 \ (\text{PC}1600)$ | -8A    |

|   |                                                        |        |

(Example part number: S80016VH7TW-75A)

http://www.spectek.com/menus/part\_guides.asp