Highly-integrated MPU

(ARM Based 32-Bit Microprocessor)

# **Datasheet**

Version 1.4

www.DataSheet.in

MagnaChip Semiconductor Ltd.

# www.DataSheet.in

# Copyright. 2004 MagnaChip Semiconductor Ltd.

ALL RIGHTS RESERVED. No part of this publication may be copied in any form, by photocopy, microfilm, retrieval system, or by any other means now known or hereafter invented without the prior written permission of MagnaChip Semiconductor Ltd.

MagnaChip Semiconductor Ltd.

#1, Hyangjeong-dong, Heungduk-gu, Cheongju-si, Chungcheongbuk-do, Republic of Korea

**Taiwan**

Telephone: 886-(0)2-2500-8357

Facsimile: 886-(0)2-2509-8977

Homepage: www.magnachip.com

Technical Support Homepage: www.softonchip.com

## H.Q. of MagnaChip Semiconductor Ltd.

Telephone: 82-(0)43-270-4070 Telephone: 82-(0)43-270-4085 Facsimile: 82-(0)43-270-4099 Facsimile: 82-(0)43-270-4099

# **World Wide Sales Network**

#### U.S.A.

Telephone: 1-408-232-8757 Facsimile: 1-408-232-8135

HMS30C7202 Datasheet, ver1.4

May 12, 2004

# Marketing Site Sales in Korea

Telephone: 82-(0)2-3459-3843 Facsimile: 82-(0)2-3459-3945

# **Hong Kong**

Telephone: 852-2971-1640 Facsimile: 852-2971-1622

# **Proprietary Notice**

MagnaChip logo is trademark of MagnaChip Semiconductor Ltd.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material from excepts with the prior permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by MagnaChip in good faith. However, all warranties implied or expressed, including but not limited to implied warranties or merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. MagnaChip Semiconductor Ltd. shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product. MagnaChip Semiconductor Ltd. may make changes to specification and product description at any time without notice.

# **Change Log**

| Issue | Date       | Ву        | Change                                                  |

|-------|------------|-----------|---------------------------------------------------------|

| A-01  | 2002/08/27 | Kisun Kim | The First Draft                                         |

| A-02  | 2002/08/28 | Kisun Kim | PMU Freq. Range / QFP Footprint / BGA Pin Diagram       |

| A-03  | 2002/10/01 | Kisun Kim | PKG Soldering Condition / Harry's Update                |

| A-04  | 2002/10/05 | Kisun Kim | CAN Interrupt Desc. / Interrupt controller FIQ Desc.    |

| A-05  | 2002/10/14 | Kisun Kim | Harry's Review (Chapter 1~5)                            |

| A-06  | 2002/12/28 | Kisun Kim | Harry's Review (Chapter 6~11)                           |

| A-07  | 2003/01/09 | Kisun Kim | SMI example / SMC / USB                                 |

| A-08  | 2003/02/26 | Injae Koo | DC Electrical Characteristics / RTC / USB               |

| A-10  | 2003/03/03 | Injae Koo | The First Release (Version 1.0)                         |

| A-11  | 2003/03/28 | Injae Koo | LCD / CAN / Overview / DC E. Char. / GPIO (Version 1.1) |

| A-12  | 2003/06/03 | Injae Koo | DMA / DC Char. / GPIO / Delete the I2S (Version 1.2)    |

| A-13  | 2003/09/15 | Injae Koo | ERRATA(version 1.0) is incorporated into this version   |

| A-14  | 2004/05/12 | Injae Koo | ADC/GPIO/SDRAMC/MMC/LCD/AC Characteristics (SMI)        |

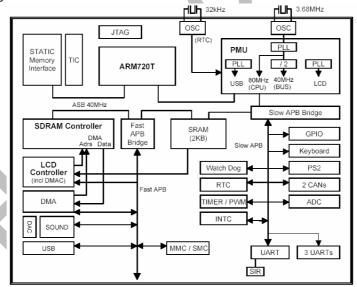

## **FEATURES**

- 32-bit ARM7TDMI RISC static CMOS CPU core : Running up to 70 MHz

- 8Kbytes combined instruction/data cache

- Memory management unit

- Supports Little Endian operating system

- 2Kbytes SRAM for internal buffer memory

- On-chip peripherals with individual power-down:

- Multi-channel DMA

- 4 Timer Channels with Watch Dog Timer

- Intelligent Interrupt Controller

- Memory controller for ROM, Flash, SRAM, SDRAM

- Power management unit

- LCD Controller for mono/color STN and TFT LCD

- Real-time clock (32.768kHz oscillator)

- Infrared communications (SIR support)

- 4 UARTs (16C550 compatible)

- PS/2 External Keyboard / Mouse interface

- 2 Pulse-Width-Modulated (PWM) interface

- Matrix Keyboard control interface (8\*8)

- GPIC

- MMC / SMC Card interface

- 2 Controller Area Network (CAN)

- USB (slave)

- On-chip ADC and interface module (Battery Check, Audio In, Touch Panel)

- On-chip DAC and interface module (8 Bit Stereo Audio Output)

- 3 PLLs

Figure A. Functional Block Diagram

- JTAG debug interface and boundary scan

- 0.25um Low Power CMOS Process

- 2.5V internal / 3.3V IO supply voltage

- 256-pin MQFP / FBGA package

- Low power consumption

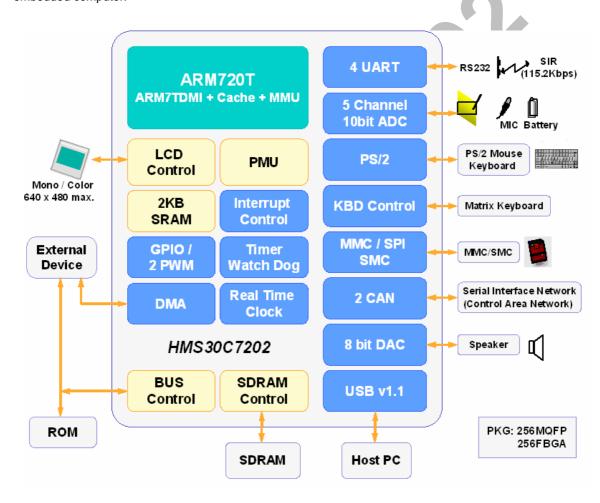

#### **OVERVIEW**

The HMS30C7202 is a highly integrated low power microprocessor for personal digital assistants, and other applications described below. The device incorporates an ARM720T CPU and system interface logic to interface with various types of devices. HMS30C7202 is a highly modular design based on the AMBA bus architecture between CPU and internal modules.

The on-chip peripherals include LCD controller with DMA support for external SDRAM memory, analog functions such as ADC, DAC, and PLLs. Intelligent interrupt controller and internal 2Kbytes SRAM can support an efficient interrupt service execution. The HMS30C7202 also supports voice recording, sound playback and a touch panel interface. UART, USB, PS2 and CAN provide serial communication channels for external systems. The power management features result in very low power consumption. The HMS30C7202 provides an excellent solution for personal digital assistants (PDAs), and data terminal running the Microsoft Windows CE operating system. Other applications include smart phones, Internet appliances, telematic systems and embedded computer.

Figure B. System Configuration

# **TABLE OF CONTENTS**

| 1 ARCHITECTURAL OVERVIEW              | 9       |

|---------------------------------------|---------|

| 1.1 Processor                         |         |

|                                       | (       |

|                                       | (       |

|                                       |         |

|                                       | (       |

|                                       | (       |

|                                       | (       |

| 1.5 SDRAM CONTROLLER                  |         |

| 1.6 PERIPHERAL DMA                    |         |

| 1.6.1 Overview                        |         |

| 1.6.2 Transfer sizes                  |         |

|                                       |         |

|                                       |         |

| 1.6.5 Sound output                    |         |

| 1.7 Peripherals                       |         |

|                                       |         |

|                                       |         |

|                                       |         |

| 1.9 Test and debug                    |         |

| 2 PIN DESCRIPTION                     |         |

|                                       |         |

|                                       | 13      |

| 2.1.1 MQFP Type                       |         |

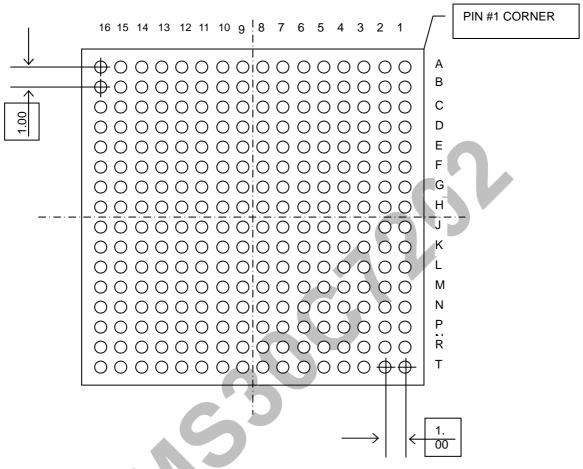

| 2.1.2 FBGA Type                       | 15      |

| 2.2 PIN DESCRIPTIONS                  |         |

| 2.2.1 External Signal Functions       |         |

|                                       |         |

| 2.2.2.1 PORT A                        | 20      |

| 2.2.2.2 PORT B                        | 20      |

|                                       | 2]      |

|                                       | 21      |

|                                       |         |

|                                       |         |

|                                       | 23      |

|                                       |         |

| 3 ARM720T MACROCELL                   | 24      |

|                                       |         |

| 3.1 ARM720T MACROCELL                 |         |

| 4 MEMORY MAP                          |         |

|                                       |         |

| 5 PMU & PLL                           | 27      |

|                                       |         |

|                                       |         |

|                                       |         |

|                                       |         |

| 8                                     |         |

| · · · · · · · · · · · · · · · · · · · |         |

|                                       |         |

| 9 ,                                   |         |

|                                       |         |

| ę ,                                   | T)      |

|                                       |         |

|                                       | (UDBCT) |

|                                       |         |

| 5.4 Timings                           |         |

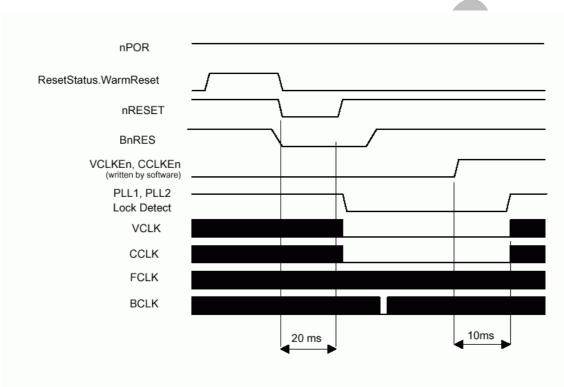

|   | 5.4.1  | Reset Sequences of Power On Reset                          |    |

|---|--------|------------------------------------------------------------|----|

|   | 5.4.2  | Software Generated Warm Reset                              | 35 |

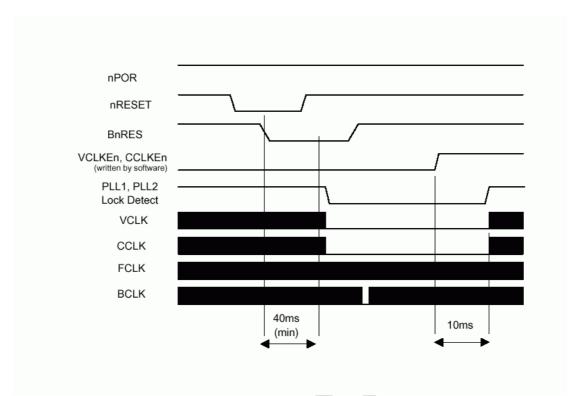

|   | 5.4.3  | An Externally generated Warm Reset                         |    |

|   |        |                                                            |    |

| 6 | SDRAM  | M CONTROLLER                                               | 37 |

|   |        |                                                            |    |

|   |        | JPPORTED MEMORY DEVICES                                    |    |

|   | 6.2 RE | GISTERS                                                    | 38 |

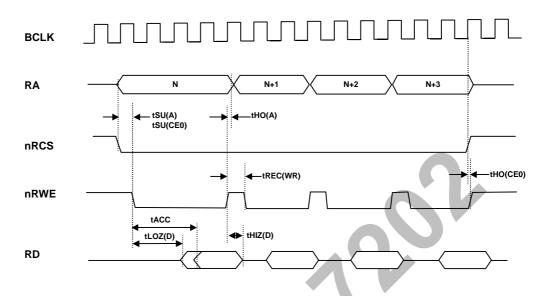

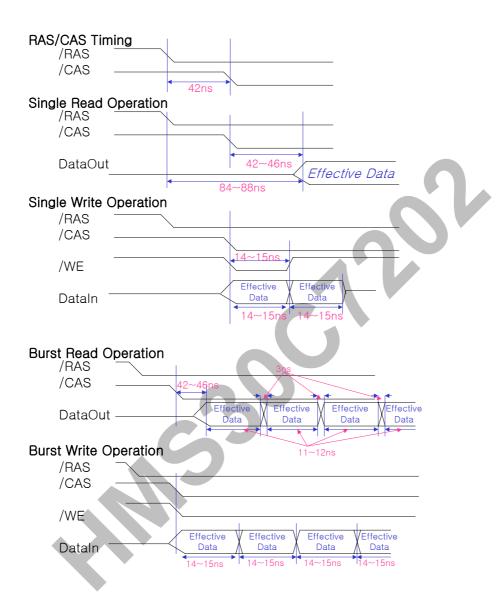

|   | 6.2.1  | SDRAM Controller Configuration Register (SDCON)            | 38 |

|   | 6.2.2  | SDRAM Controller Refresh Timer Register (SDREF)            |    |

|   | 6.2.3  |                                                            |    |

|   |        | SDRAM Controller Write buffer flush timer Register (SDWBF) |    |

|   | 6.2.4  | SDRAM Controller Wait Driver Register (SDWAIT)             |    |

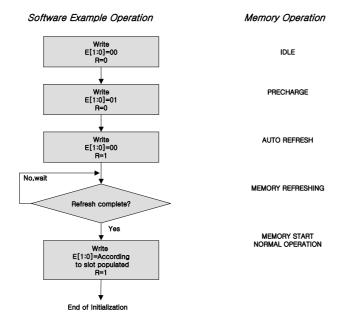

|   | 6.3 Po | OWER-UP INITIALIZATION OF THE SDRAMS                       | 40 |

|   | 6.4 SE | DRAM Memory Map                                            | 4  |

|   | 6.5 AN | MBA Accesses and Arbitration                               | 43 |

|   |        | ERGING WRITE BUFFER                                        |    |

|   |        |                                                            |    |

| 7 | STATI  | C MEMORY INTERFACE                                         | 4  |

| ′ |        |                                                            |    |

|   | 7.1 Ex | KTERNAL SIGNALS                                            | 44 |

|   |        | INCTIONAL DESCRIPTION                                      |    |

|   | 7.2.1  | Memory bank select                                         |    |

|   |        |                                                            |    |

|   | 7.2.2  | Access sequencing                                          | 44 |

|   | 7.2.3  | Wait states generation                                     | 45 |

|   | 7.2.4  | Burst read control                                         | 43 |

|   | 7.2.5  | Byte lane write control                                    |    |

|   |        | EGISTERS                                                   |    |

|   |        |                                                            |    |

|   | 7.3.1  | MEM Configuration Register                                 |    |

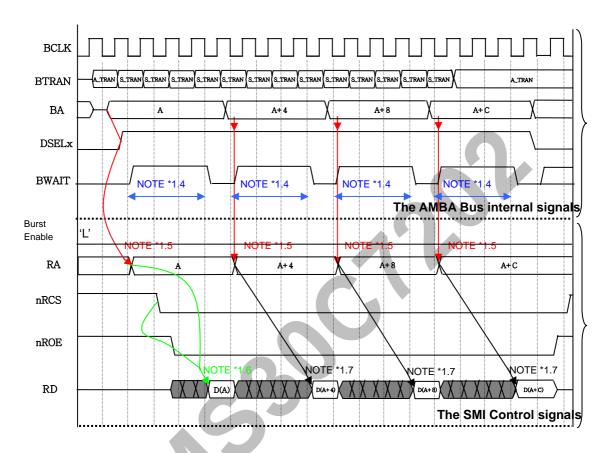

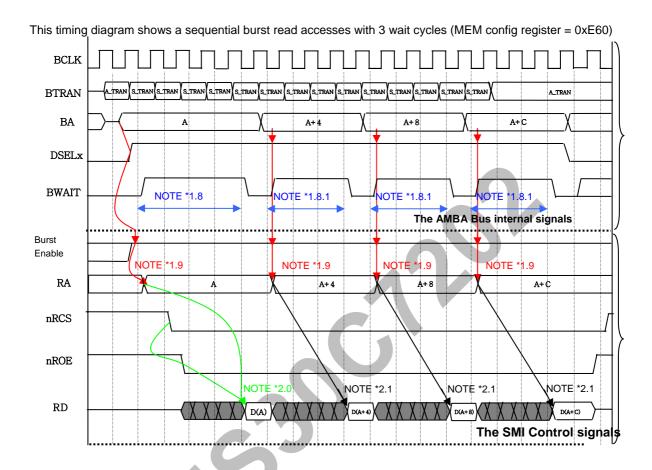

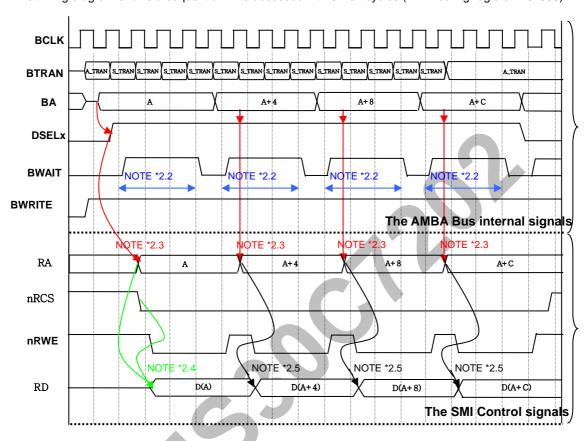

|   | 7.4 Ex | XAMPLES OF THE SMI READ, WRITE WAIT TIMING DIAGRAM         |    |

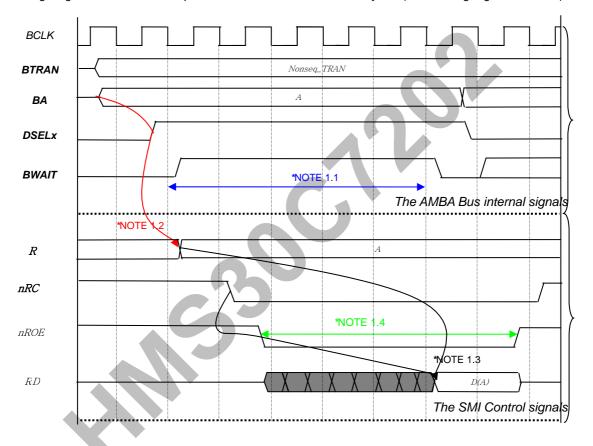

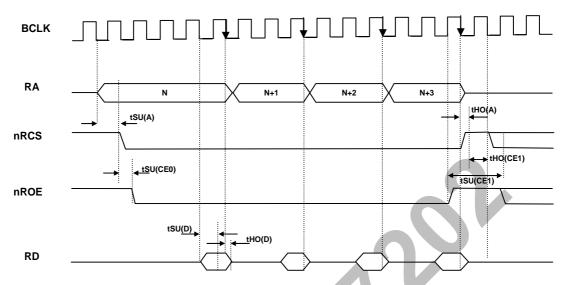

|   | 7.4.1  | Read normal wait (Non-Sequential mode)                     | 47 |

|   | 7.4.2  | Read normal wait (Sequential mode)                         | 48 |

|   | 7.4.3  | Read burst wait (Sequential mode)                          |    |

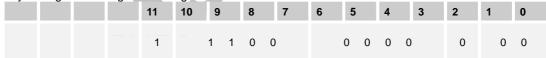

|   | 7.4.4  | Write normal wait (Sequential mode)                        |    |

|   |        |                                                            |    |

|   |        | TERNAL SRAM                                                |    |

|   | 7.5.1  | Remapping Enable Register                                  |    |

|   | 7.5.2  | Remap Source Address Register                              | 53 |

| _ | T CD C | CONTROLLED.                                                |    |

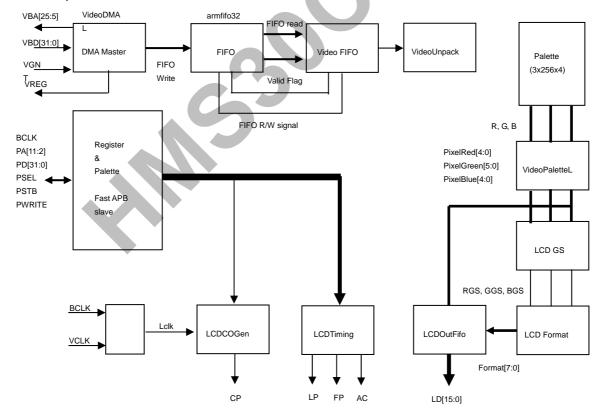

| 8 | LCD C  | CONTROLLER                                                 | 52 |

|   | 0.1 37 | DEO OPERATION                                              | 51 |

|   |        |                                                            |    |

|   | 8.1.1  | LCD datapath                                               |    |

|   | 8.1.1  |                                                            |    |

|   | 8.1.2  | Color/Grayscale Dithering                                  | 55 |

|   | 8.1.3  | How to order the bit on LD[7:0] output                     | 5  |

|   | 8.1.4  | TFT mode                                                   |    |

|   |        |                                                            |    |

|   |        | GGISTERS                                                   | 20 |

|   | 8.2.1  | LCD Power Control                                          |    |

|   | 8.2.2  | LCD Controller Status/Mask and Interrupt Registers         | 57 |

|   | 8.2.3  | LCD DMA Base Address Register                              | 58 |

|   | 8.2.4  | LCD DMA Channel Current Address Register                   |    |

|   | 8.2.5  | LCD Timing 0 Register                                      |    |

|   |        |                                                            |    |

|   | 8.2.6  | LCD Timing 1 Register                                      | 39 |

|   | 8.2.7  | LCD Timing 2 Register                                      | 60 |

|   | 8.2.8  | LCD Test Register                                          | 6. |

|   | 8.2.9  | Grayscaler Test Registers                                  |    |

|   | 8.2.10 | LCD Palette registers                                      |    |

|   |        | <u>g</u>                                                   |    |

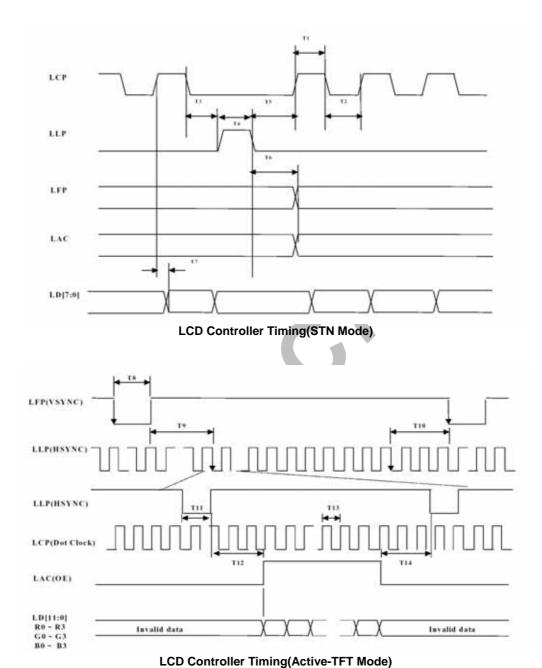

|   | 8.3 Ti | MINGS                                                      | 63 |

| 9 | FACT / | AMBA PERIPHERALS                                           | 6  |

| y | TASI A | MIDA I EMII HERALS                                         | 04 |

|   | 9.1 DN | MA CONTROLLER                                              | 64 |

|   | 9.1.1  | External Signals                                           |    |

|   |        |                                                            |    |

|   | 9.1.2  | Registers                                                  |    |

|   | 9.1.2  | .1 ADR0                                                    | 6. |

| 9.1.2.2 | ASR                                     | <br>65 |

|---------|-----------------------------------------|--------|

| 9.1.2.3 |                                         |        |

| 9.1.2.4 | TSR                                     | <br>65 |

| 9.1.2.5 | CCR0                                    | <br>65 |

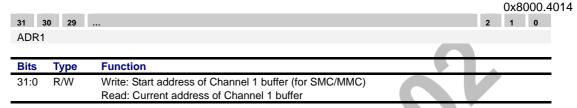

| 9.1.2.6 | ADR1                                    | <br>66 |

| 9.1.2.7 | TNR1                                    | <br>66 |

| 9.1.2.8 | CCR1                                    | 66     |

| 9.1.2.9 | ADR2                                    | 66     |

| 9.1.2.1 |                                         |        |

| 9.1.2.1 |                                         |        |

| 9.1.2.1 |                                         |        |

| 9.1.2.1 |                                         |        |

| 9.1.3   | DMAC operation                          |        |

|         | C/ SPI Controller                       |        |

| 9.2.1   | External Signals                        |        |

|         |                                         |        |

| 9.2.2   | Registers (SPI Mode)                    | <br>09 |

|         | SPIMMC Control Register (SPICR)         | <br>70 |

| 9.2.2.2 |                                         |        |

| 9.2.2.3 |                                         |        |

| 9.2.2.4 |                                         | 70     |

| 9.2.2.5 |                                         | <br>70 |

| 9.2.2.6 |                                         |        |

| 9.2.3   | Timings                                 | <br>71 |

| 9.2.4   | SPI Operation for MMC                   | 72     |

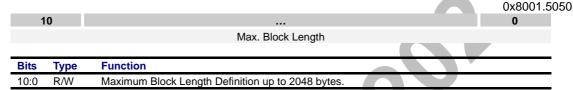

| 9.2.5   | Multimedia Card Host Controller         |        |

| 9.2.6   | Registers                               |        |

| 9.2.6.1 | MMC Mode Register                       | <br>73 |

| 9.2.6.2 | MMC Operation Register                  | 74     |

| 9.2.6.3 |                                         | 74     |

| 9.2.6.4 |                                         | 75     |

| 9.2.6.5 |                                         |        |

| 9.2.6.6 |                                         | 76     |

| 9.2.6.7 |                                         |        |

| 9.2.6.8 |                                         |        |

| 9.2.6.9 |                                         | <br>76 |

| 9.2.6.1 |                                         |        |

| 9.2.6.1 |                                         |        |

| 9.2.6.1 | 3                                       |        |

| 9.2.7   | Basic Operation in MMC Mode             |        |

| 9.2.7   |                                         |        |

|         |                                         |        |

| 9.2.7.2 |                                         |        |

|         | C CONTROLLER                            |        |

| 9.3.1   | External Signals                        |        |

|         |                                         |        |

| 9.3.2.1 | SMC Command Register (SMCCMD)           |        |

| 9.3.2.2 |                                         |        |

| 9.3.2.3 |                                         |        |

| 9.3.2.4 |                                         |        |

| 9.3.2.5 |                                         | <br>81 |

| 9.3.2.6 | SMC Timing Parameter Register (SMCTIME) | <br>82 |

| 9.3.2.7 | SMC Status Register (SMCSTAT)           | <br>82 |

| 9.4 Sou | ND INTERFACE                            | <br>84 |

| 9.4.1   | External Signals                        | <br>84 |

| 9.4.2   | Registers                               | <br>84 |

| 9.4.2.1 | SCONT                                   |        |

| 9.4.2.2 |                                         |        |

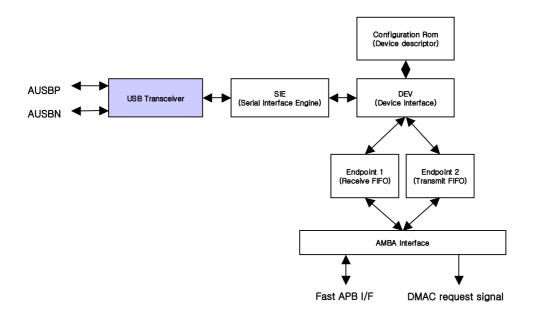

|         | S SLAVE INTERFACE                       |        |

| 9.5.1   | Block Diagram                           |        |

| 9.5.2   | Theory of Operation                     |        |

| 9.5.3   | Endpoint FIFOs (Rx. Tx)                 | 90     |

|         |                                         |        |

|             | ternal Signals                                  |     |

|-------------|-------------------------------------------------|-----|

| 9.5.5 Re    | gistersgisters                                  | 90  |

| 9.5.5.1     | GCTRL                                           | 90  |

| 9.5.5.2     | EPCTRL                                          | 90  |

| 9.5.5.3     | INTMASK                                         | 91  |

|             | INTSTAT                                         |     |

|             | PWR                                             |     |

|             | DEVID                                           |     |

| 9.5.5.7     | DEVCLASS                                        | 92  |

|             | INTCLASS                                        |     |

|             | SETUPO / SETUP1                                 |     |

| 9.5.5.10    | ENDPORD                                         |     |

| 9.5.5.11    | ENDPOWT                                         |     |

| 9.5.5.12    | ENDP1RD.                                        |     |

| 9.5.5.13    | ENDP2WT                                         |     |

|             |                                                 |     |

|             | MBA PERIPHERALS                                 |     |

| 10.1 ADC Iv | TERFACE CONTROLLER                              | 05  |

| 10.1 ADC IN | TERFACE CONTROLLER                              | 93  |

| 10.1.1 Ext  | ternal Signals                                  | 93  |

| ,           | gisters                                         |     |

| 10.1.2.1    | ADC Control Register (ADCCR)                    | 96  |

| 10.1.2.2    | ADC Touch Panel Control Register (ADCTPCR)      | 96  |

| 10.1.2.3    | ADC Battery check Control Register (ADCBACR)    |     |

| 10.1.2.4    | ADC Sound Control Register (ADCSDCR)            |     |

| 10.1.2.5    | ADC Interrupt Status Register (ADCISR)          |     |

| 10.1.2.6    | ADC Tip Down Control Status Register (ADCTDCSR) |     |

| 10.1.2.7    | ADC Direct Control Register (ADCDIRCR)          |     |

| 10.1.2.8    | ADC Direct Data Read Register (ADCDIRDATA)      | 98  |

| 10.1.2.9    | ADC 1 <sup>ST</sup> Touch Panel Data register   | 99  |

| 10.1.2.10   | ADC 2 <sup>ND</sup> Touch Panel Data Register   |     |

| 10.1.2.11   | ADC Main Battery Data Register (ADCMBDATA)      |     |

| 10.1.2.12   | ADC Backup Battery Data Register (ADCBBDATA)    |     |

| 10.1.2.13   | ADC Sound Data Register (ADCSDATA0 – ADCSDATA7) |     |

|             | TERFACE                                         |     |

|             | ock Diagram                                     |     |

| 10.2.2 Re   | gister Map                                      | 103 |

| 10.2.3 Re   | gisters                                         |     |

| 10.2.3.1    | CAN Control Register                            |     |

| 10.2.3.2    | CAN Status Register                             | 105 |

| 10.2.3.3    | CAN Error Counting Register                     |     |

| 10.2.3.4    | CAN Bit Timing Register                         |     |

| 10.2.3.5    | CAN Interrupt Register                          | 106 |

| 10.2.3.6    | CAN Test Register                               |     |

| 10.2.3.7    | CAN BRP Extension Register                      | 107 |

| 10.2.3.8    | CAN Enable Register                             | 107 |

| 10.2.3.9    | Interface X Command Request Register            | 107 |

| 10.2.3.10   | Interface X Command Mask Register               | 107 |

| 10.2.3.11   | Interface X Mask 1 Register                     | 108 |

| 10.2.3.12   | Interface X Mask 2 Register                     | 108 |

| 10.2.3.13   | Interface X Arbitration 1 Register              | 109 |

| 10.2.3.14   | Interface X Arbitration 2 Register              |     |

| 10.2.3.15   | Interface X Message Control Register            |     |

| 10.2.3.16   | Interface X Data A1 Register                    |     |

| 10.2.3.17   | Interface X Data A2 Register                    |     |

| 10.2.3.18   | Interface X Data B1 Register                    |     |

| 10.2.3.19   | Interface X Data B2 Register                    |     |

| 10.2.3.20   | Transmission Request 1 Register                 |     |

| 10.2.3.21   | Transmission Request 2 Register                 |     |

| 10.2.3.22   | New Data 1 Register                             |     |

| 10.2.3.23   | New Data 2 Register                             |     |

| 10.2.3.24   | Interrupt Pending 1 Register                  | 112 |

|-------------|-----------------------------------------------|-----|

| 10.2.3.25   | Interrupt Pending 2 Register                  | 112 |

| 10.2.3.26   | Message Valid 1 Register                      | 112 |

| 10.2.3.27   | Message Valid 2 Register                      | 112 |

| 0.3 GPIO    |                                               |     |

| 10.3.1 Exte | ernal Signals                                 | 114 |

|             | isters                                        |     |

| 10.3.2.1    | ADATA                                         |     |

| 10.3.2.2    | ADIR                                          |     |

| 10.3.2.3    | AMASK                                         |     |

| 10.3.2.4    | ASTAT                                         |     |

| 10.3.2.5    | AEDGE                                         |     |

| 10.3.2.6    | ACLR                                          |     |

| 10.3.2.7    | APOL                                          |     |

| 10.3.2.8    | GPIO PORT A Enable Register                   |     |

| 10.3.2.9    | BDATA                                         |     |

| 10.3.2.10   | BDIR                                          |     |

| 10.3.2.11   | BMASK                                         |     |

| 10.3.2.12   | BSTAT                                         |     |

| 10.3.2.13   | BEDGE                                         |     |

| 10.3.2.14   | BCLK                                          |     |

| 10.3.2.15   | BPOL                                          | 117 |

| 10.3.2.16   | GPIO PORT B Enable Register                   |     |

| 10.3.2.17   | CDATA                                         |     |

| 10.3.2.17   | CDIR                                          |     |

| 10.3.2.19   | CMASK                                         |     |

| 10.3.2.20   | CBSTAT                                        |     |

| 10.3.2.21   | CEDGE                                         |     |

| 10.3.2.22   | CCLK                                          |     |

| 10.3.2.23   | CPOL                                          |     |

| 10.3.2.24   | GPIO PORT C Enable Register                   |     |

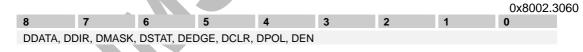

| 10.3.2.25   | DDATA                                         |     |

| 10.3.2.26   | DDIR                                          |     |

| 10.3.2.27   | DMASK                                         |     |

| 10.3.2.28   | DBSTAT                                        | 118 |

| 10.3.2.29   | DEDGE                                         |     |

| 10.3.2.30   | DCLK                                          |     |

| 10.3.2.31   | DPOL                                          |     |

| 10.3.2.32   | GPIO PORT D Enable Register                   |     |

| 10.3.2.33   | EDATA                                         |     |

| 10.3.2.34   | EDIR                                          |     |

| 10.3.2.35   | EMASK                                         |     |

| 10.3.2.36   | EBSTAT                                        |     |

| 10.3.2.37   | EEDGE                                         |     |

| 10.3.2.38   | ECLK.                                         |     |

| 10.3.2.39   | EPOL                                          |     |

| 10.3.2.40   | GPIO PORT E Enable Register                   |     |

| 10.3.2.41   | Tic Test mode Register(TICTMDR)               |     |

| 10.3.2.42   | PORTA Multi-function Select register(AMULSEL) |     |

| 10.3.2.43   | SWAP Pin Configuration Register(SWAP)         |     |

|             | IO Interrupt                                  |     |

|             | IO Rise/Fall Time                             |     |

|             | PT CONTROLLER                                 |     |

|             | ck diagram                                    |     |

|             | isters                                        |     |

| 10.4.2.1    | Interrupt Enable Register (IER)               |     |

| 10.4.2.2    | Interrupt Status Register (ISR)               |     |

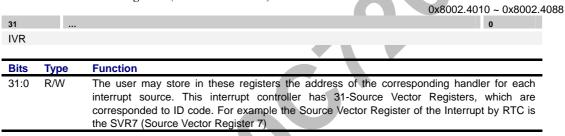

| 10.4.2.3    | IRQ Vector Register (IVR)                     |     |

| 10.4.2.4    | Source Vector Register (SVR0 to SVR30)        |     |

| 10.4.2.5    | Interrupt ID Register (IDR)                   |     |

|             |                                               |     |

| 10.4.2.6             | Priority Set Register (PSR0 to PSR7)                          | 125 |

|----------------------|---------------------------------------------------------------|-----|

|                      | KEYBOARD INTERFACE CONTROLLER                                 |     |

| 10.5.1 Ext           | ernal Signals                                                 | 127 |

| 10.5.2 Reg           | gisters                                                       | 127 |

| 10.5.2.1             | Keyboard Configuration Register (KBCR)                        | 128 |

| 10.5.2.2             | Keyboard Scanout Register(KBSC)                               | 128 |

| 10.5.2.3             | Keyboard Test Register (KBTR)                                 |     |

| 10.5.2.4             | Keyboard Value Register (KVR0)                                |     |

| 10.5.2.5             | Keyboard Value Register (KVR1)                                |     |

| 10.5.2.6             | Keyboard Status Register (KBSR)                               |     |

|                      | TERFACE CONTROLLER                                            |     |

|                      | ernal Signals                                                 |     |

|                      | gisters                                                       |     |

| 10.6.2.1             | PSDATA                                                        |     |

| 10.6.2.1             | PSSTAT                                                        |     |

| 10.6.2.3             | PSCONF                                                        |     |

| 10.6.2.4             | PSINTR                                                        |     |

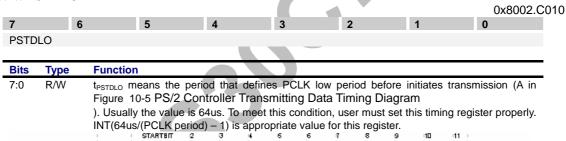

| 10.6.2.5             | PSTDLO                                                        |     |

|                      | PSTPRI                                                        |     |

| 10.6.2.6<br>10.6.2.7 | PSTXMT                                                        |     |

|                      | PSTREC                                                        |     |

| 10.6.2.8             | PSTRECPSPWDN                                                  |     |

| 10.6.2.9             |                                                               |     |

|                      | plication Notes                                               |     |

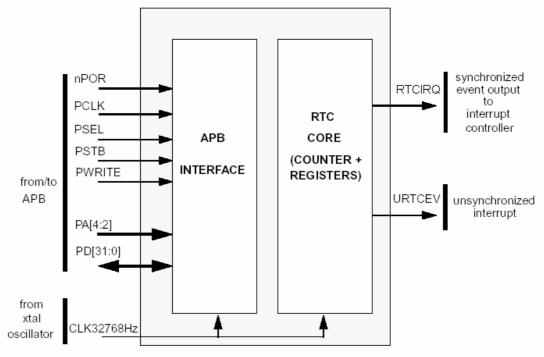

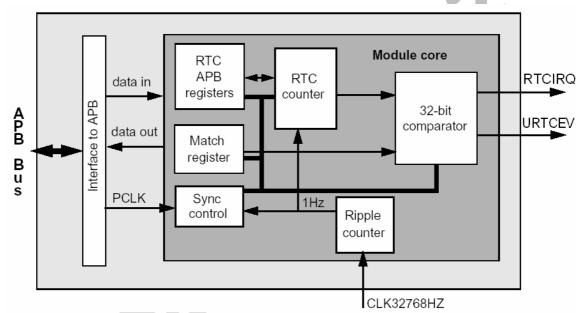

| 10.7 RTC             |                                                               | 136 |

|                      | ernal Signals                                                 |     |

|                      | nctional Description                                          |     |

|                      | gisters                                                       |     |

| 10.7.3.1             | RTC Data Register (RTCDR)                                     | 137 |

| 10.7.3.2             | RTC Match Register (RTCMR)                                    |     |

| 10.7.3.3             | RTC Status Register (RTCS)                                    |     |

| 10.7.3.4             | RTC Control Register (RTCCR)                                  |     |

|                      |                                                               |     |

| 10.8.1 Ext           | ernal Signals                                                 | 139 |

| 10.8.2 Reg           | gisters                                                       | 139 |

| 10.8.2.1             | Timer [0,1,2] Base Register (T[0,1,2]BASE)                    | 139 |

| 10.8.2.2             | Timer [0,1,2] Count Register (T[0,1,2]COUNT)                  | 140 |

| 10.8.2.3             | Timer [0,1,2] Control Register (T[0,1,2]CTRL)                 | 140 |

| 10.8.2.4             | Timer Top-level Control Register (TOPCTRL)                    | 140 |

| 10.8.2.5             | Timer Status Register (TOPSTAT)                               |     |

| 10.8.2.6             | Timer Lower 32-bit Count Register of 64-bit Counter (T64LOW)  | 141 |

| 10.8.2.7             | Timer Upper 32-bit Count Register of 64-bit Counter (T64HIGH) |     |

| 10.8.2.8             | Timer 64-bit Counter Control Register (T64CTRL)               |     |

| 10.8.2.9             | Timer 64-bit Counter Test Register (T64TR)                    |     |

| 10.8.2.10            | Timer Lower 32-bit Base Register of 64-bit Counter (T64LBASE) |     |

| 10.8.2.11            | Timer Upper 32-bit Base Register of 64-bit Counter (T64HBASE) |     |

| 10.8.2.12            | PWM Channel [0,1] Count Register (P[0,1]COUNT)                |     |

| 10.8.2.13            | PWM Channel [0,1] Width Register (P[0,1]WIDTH)                |     |

| 10.8.2.14            | PWM Channel [0,1] Period Register (P[0,1]PERIOD)              |     |

| 10.8.2.15            | PWM Channel [0,1] Control Register (P[0,1]CTRL)               |     |

| 10.8.2.16            | PWM Channel[0,1] Test Register(P[0,1]PWMTR)                   |     |

|                      | SIR                                                           |     |

|                      | ernal Signals                                                 |     |

|                      | gisters                                                       |     |

| 10.9.2 Keg           | RBR/THR/DLL                                                   |     |

| 10.9.2.1             | IER/DLM                                                       |     |

|                      | IIR/FCR                                                       |     |

| 10.9.2.3             |                                                               |     |

| 10.9.2.4             | LCR                                                           |     |

| 10.9.2.5             | MCR                                                           |     |

| 10.9.2.6             | LSR                                                           |     |

| 10.9.2.7             | MSR                                                           | 151 |

| 10.9.2.8 SCR                                              |     |

|-----------------------------------------------------------|-----|

| 10.9.2.9 UartEn                                           | 152 |

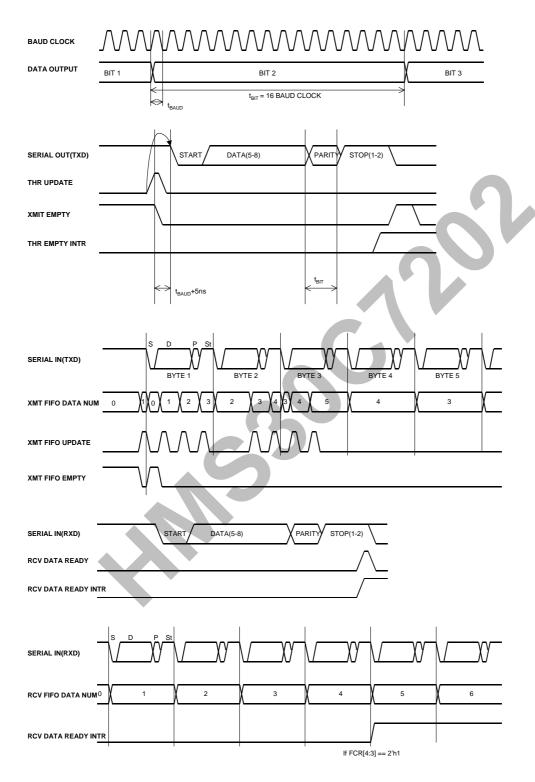

| 10.9.3 FIFO Interrupt Mode Operation                      |     |

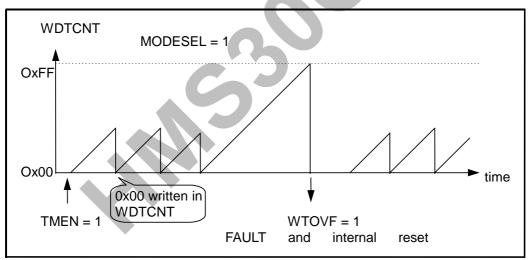

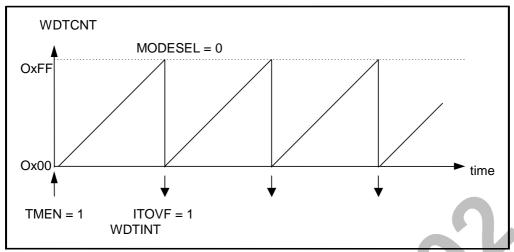

| 10.10 WATCHDOG TIMER                                      |     |

| 10.10.1 Watchdog Timer Operation                          |     |

| 10.10.1.1 The Watchdog Timer Mode                         | 154 |

| 10.10.1.2 The Interval Timer Mode                         |     |

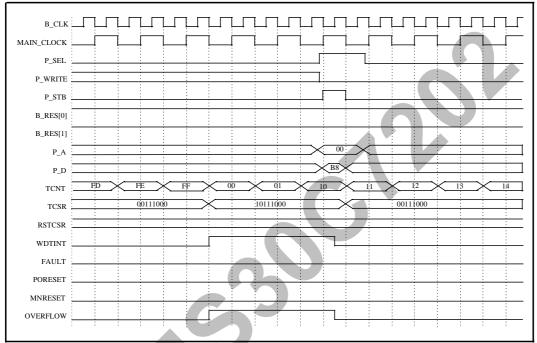

| 10.10.1.3 Timing of setting the overflow flag             | 155 |

| 10.10.1.4 Timing of clearing the overflow flag            |     |

| 10.10.2 Registers                                         |     |

| 10.10.2.1 WDT Control Register (WDTCTRL)                  | 155 |

| 10.10.2.2 WDT Status Register (WDTSTAT)                   | 156 |

| 10.10.2.3 WDT Counter (WDTCNT)                            |     |

| 10.10.3 Examples of Register Setting                      |     |

| 10.10.3.1 Interval Timer Mode                             |     |

| 10.10.3.2 Watchdog Timer Mode with Internal Reset Disable |     |

| 10.10.3.3 Watchdog Timer Mode with Manual Reset           | 158 |

| 11 DEBUG AND TEST INTERFACE                               | 150 |

|                                                           |     |

| 11.1 Overview                                             | 159 |

| 11.2 SOFTWARE DEVELOPMENT DEBUG AND TEST INTERFACE        | 159 |

| 11.3 TEST ACCESS PORT AND BOUNDARY-SCAN                   | 159 |

| 11.3.1 Reset                                              |     |

| 11.3.2 Pull up Resistors                                  |     |

| 11.3.3 Instruction Register                               | 161 |

| 11.3.4 Public Instructions                                | 161 |

| 11.3.5 Test Data Registers                                |     |

| 11.3.6 Boundary Scan Interface Signals                    |     |

| 11.4 PRODUCTION TEST FEATURES                             | 172 |

| 12 ELECTRICAL CHARACTERISTICS                             | 173 |

|                                                           |     |

| 12.1 ABSOLUTE MAXIMUM RATINGS                             | 173 |

| 12.2 DC CHARACTERISTICS                                   |     |

| 12.3 A/D CONVERTER ELECTRICAL CHARACTERISTICS             | 175 |

| 12.4 D/A Converter Electrical Characteristics             |     |

| 12.5 AC CHARACTERISTICS                                   |     |

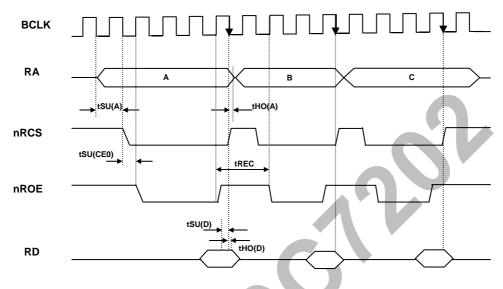

| 12.5.1 Static Memory Interface                            |     |

| 12.5.1.1 READ Access Timing (Single Mode)                 | 177 |

| 12.5.1.2 READ Access Timing (Burst Mode)                  |     |

| 12.5.1.3 WRITE Access Timing                              |     |

| 12.5.2 SDRAM Interface                                    |     |

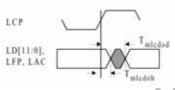

| 12.5.3 LCD Interface                                      |     |

| 12.5.4 UART(Universal Asynchronous Receiver Transmitter)  |     |

| 12.6 PACKAGE                                              |     |

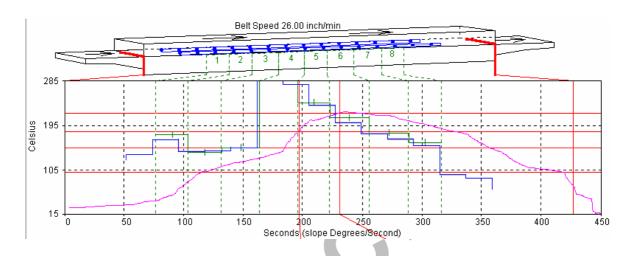

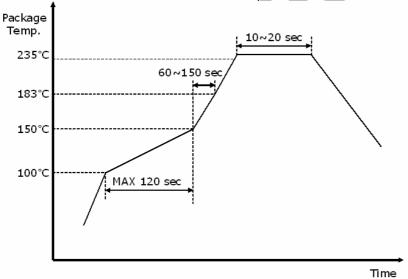

| 12.6.1 Recommended Soldering Conditions                   |     |

| 12.6.1.1 MQFP(Metric Quad Flat Pack ) Type                |     |

| 12.6.1.2 FBGA(Chip Array Ball Grid Array) Type            |     |

| 12.6.2 Pictures of Package Marking                        |     |

| 13 APPENDIX                                               | 186 |

|                                                           |     |

| 13.1 DEEP-SLEEP, WAKE-UP ISSUES OF HMS30C7202 PMU         |     |

| 13.1.1 Wake-up                                            |     |

| 13.1.2 Deep-sleep                                         | 186 |

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

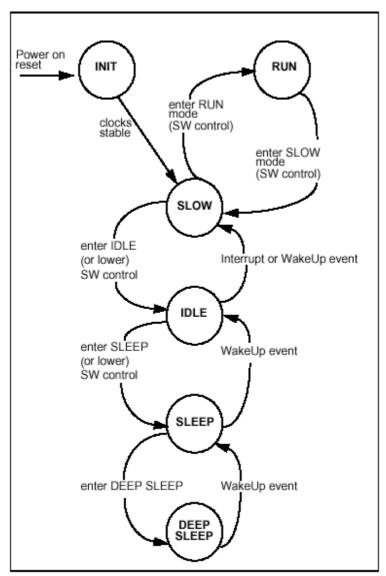

| Figure 5-1 PMU Power Management State Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 28                                                                               |

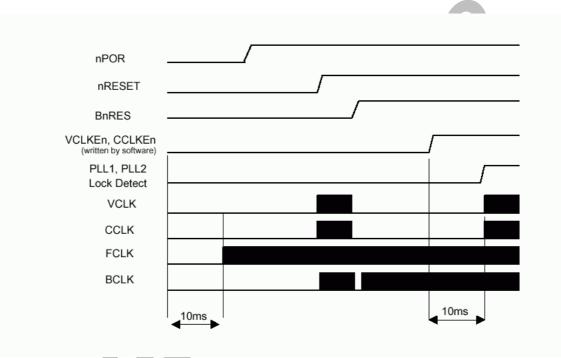

| Figure 5-2 PMU Cold Reset Event                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 34                                                                               |

| Figure 5-3 PMU Software Generated Warm Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

| Figure 5-4 PMU An Externally Generated Warm Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                  |

| Figure 6-1 SDRAM Controller Software Example and Memory Operation Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                  |

| Figure 8-1 Video System Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                  |

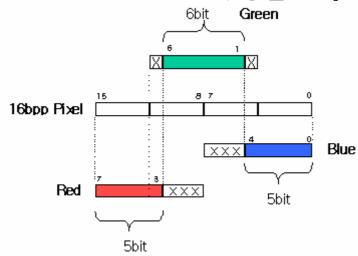

| Figure 8-2 5:6:5 Combination of 16bpp Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                  |

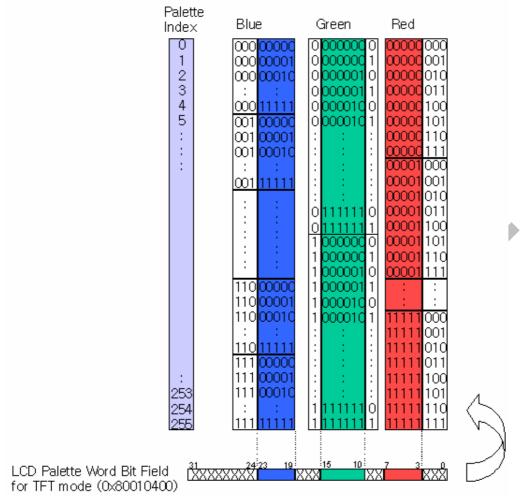

| Figure 8-3 Palette RAM Entries for 5:6:5 Combination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                  |

| Figure 8-4 Sample Code for 5:6:5 Palette Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                  |

| Figure 8-5 LCD Palette Word Bit Field for STN mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                  |

| Figure 8-6 LCD Palette Word Bit Field for TFT mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                  |

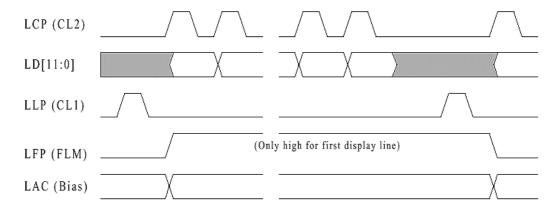

| Figure 8-7 Example Mono STN LCD Panel Signal Waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                  |

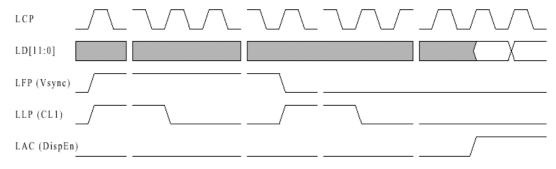

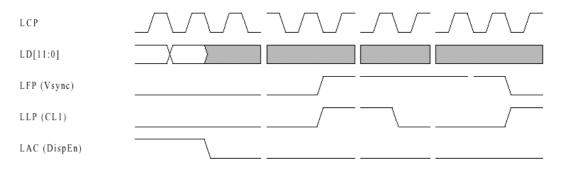

| Figure 8-8 Example TFT Signal Waveforms, Start of Frame                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                  |

| Figure 8-9 Example TFT Signal Waveforms, End of Last Line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                  |

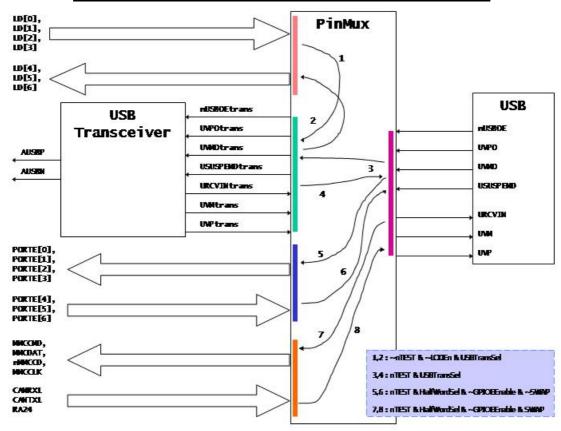

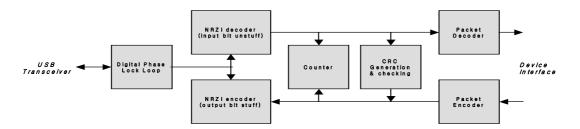

| Figure 9-1 USB Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

| Figure 9-2 USB Serial Interface Engine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 88                                                                               |

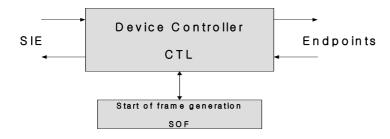

| Figure 9-3 USB Device Interface Device Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                  |

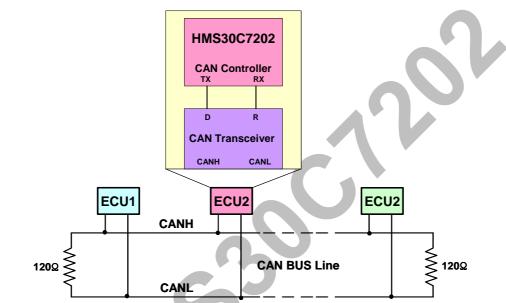

| Figure 10-1 Typical CAN Network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 102                                                                              |

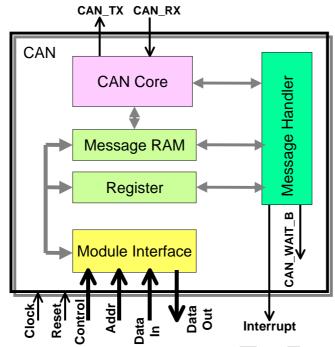

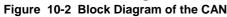

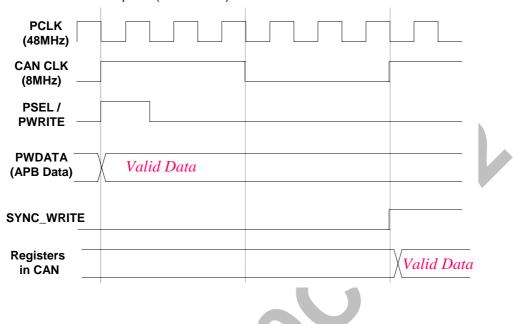

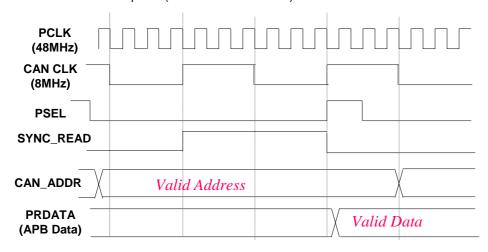

| Figure 10-2 Block Diagram of the CAN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 103                                                                              |

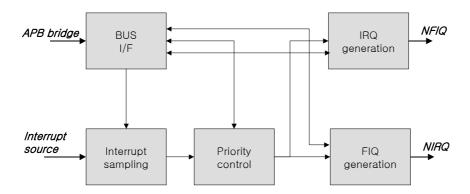

| Figure 10-3 Interrupt controller block diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 122                                                                              |

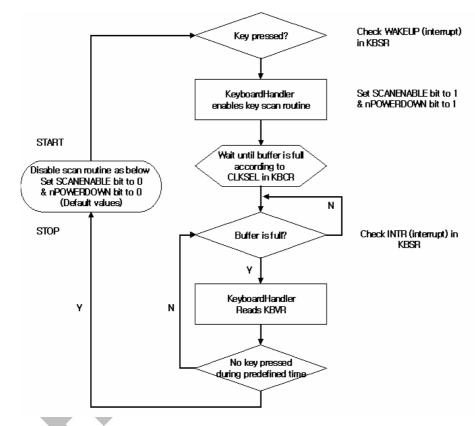

| Figure 10-4 A flow chart of the keyboard controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 127                                                                              |

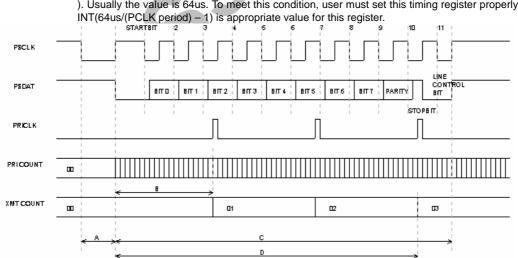

| Figure 10-5 PS/2 Controller Transmitting Data Timing Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

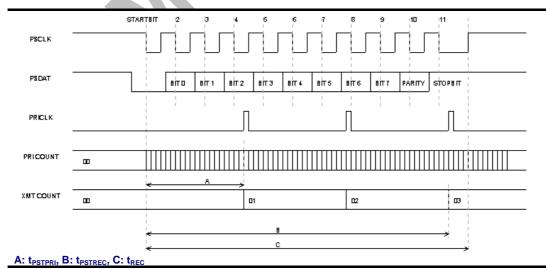

| Figure 10-6 PS/2 Controller Receiving Data Timing Diagram  Figure 10-7 RTC Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                  |

| Figure 10-7 RTC Confidential Figure 10-8 RTC Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 127                                                                              |

| Figure 10-9 WDT Operation in the Watchdog Timer mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 137<br>157                                                                       |

| Figure 10-9 WDT Operation in the Interval Timer mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                  |

| Figure 10-11 Interrupt Clear in the interval timer mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                  |

| Figure 10-12 Interrupt Clear in the watchdog timer mode with reset disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 158                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 158                                                                              |

| Figure 10-13 Interrupt Clear in the watchdog timer mode with manual reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 158                                                                              |

| Figure 10-13 Interrupt Clear in the watchdog timer mode with manual reset  LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                  |

| Figure 10-13 Interrupt Clear in the watchdog timer mode with manual reset  LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                  |

| Figure 10-13 Interrupt Clear in the watchdog timer mode with manual reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 17                                                                               |

| Figure 10-13 Interrupt Clear in the watchdog timer mode with manual reset  LIST OF TABLES  Table 2-1 Pin Signal Type Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 17<br>19                                                                         |

| Figure 10-13 Interrupt Clear in the watchdog timer mode with manual reset  LIST OF TABLES  Table 2-1 Pin Signal Type Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 17<br>19                                                                         |

| Figure 10-13 Interrupt Clear in the watchdog timer mode with manual reset  LIST OF TABLES  Table 2-1 Pin Signal Type Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 17<br>19<br>25<br>26                                                             |

| LIST OF TABLES  Table 2-1 Pin Signal Type Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                  |

| LIST OF TABLES  Table 2-1 Pin Signal Type Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                  |

| LIST OF TABLES  Table 2-1 Pin Signal Type Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                  |

| LIST OF TABLES  Table 2-1 Pin Signal Type Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                  |

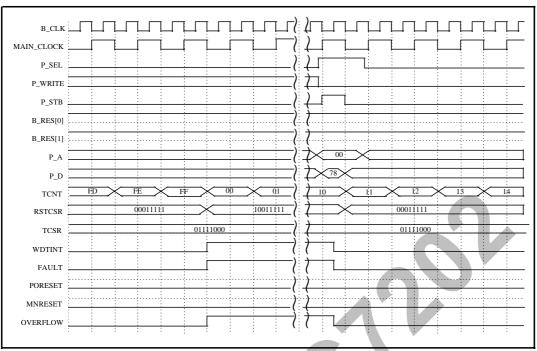

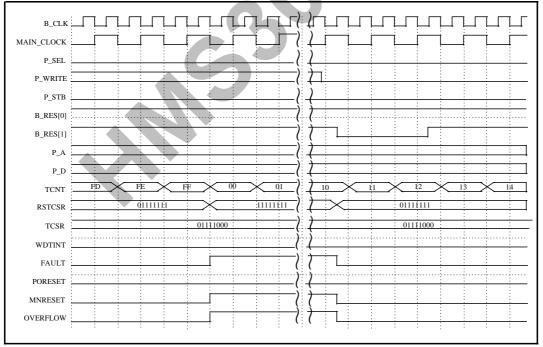

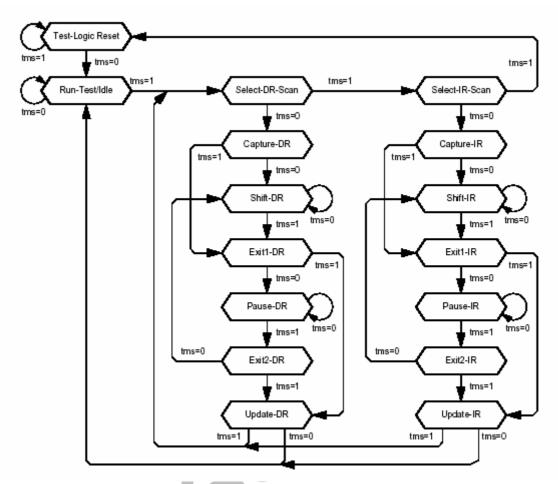

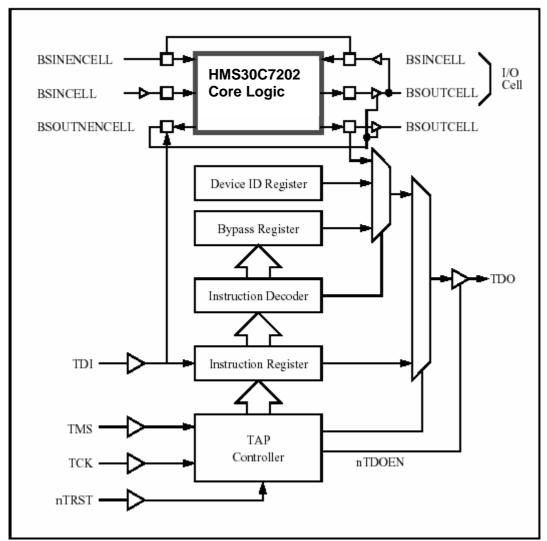

| LIST OF TABLES  Table 2-1 Pin Signal Type Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                  |