## **Linear Mixer with Integrated LO Buffer**

#### **Description:**

The CMY 211 is an all port single ended general purpose Up- and Down-Converter.

It combines small conversion losses and excellent intermodulation characteristics with a low demand of LO- and DC-power.

The internal level controlled LO-Buffer enables a good performance over a wide LO level range.

The internal mixers principle with one port RF and IF requires a frequency separation at pin 1 and 6 respectively.

#### Features:

- High Input-IP3 of typical 17.5dBm

- Very low LO-Power demand of typ. 0dBm; Wide LO-Level Range

- Wide LO-Frequency Range: <500MHz to >2.5GHz

- Single ended Ports

- RF- and IF-Port Impedance 50 Ohm

- Operating Voltage Range: < 3 to 6V</li>

- Very low Current Consumption of typical 2.5mA

- All Gold Metallization

#### **Applications:**

- Up-or Down-Converters

- Mobile Phone Receivers

- WLAN Receivers

- Mobile Phone or WLAN Basestations

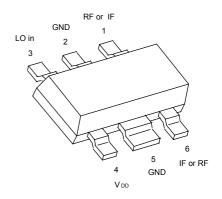

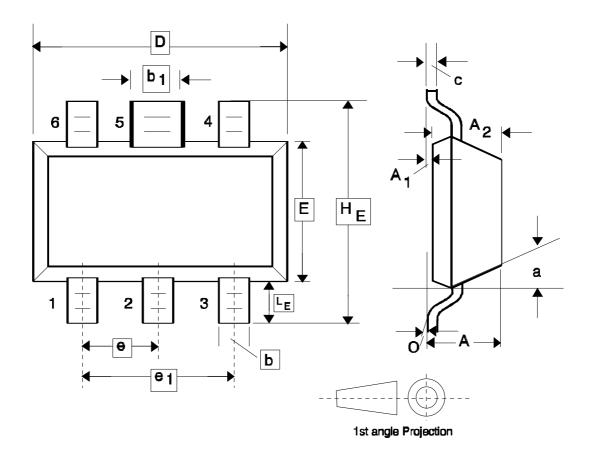

# Package Outline, MW-6:

## **CMY211 Datasheet**

# **Maximum Ratings:**

| Parameter                      | Port        | Symbol           | Value |       | Unit |

|--------------------------------|-------------|------------------|-------|-------|------|

|                                |             |                  | min   | max   |      |

| Supply Voltage                 | 4           | $V_{DD}$         | 0     | 6     | V    |

| DC-Voltage at LO Input         | 3           | $V_3$            | -3    | 0,5   | V    |

| DC-Voltage at RF-IF Ports 2)   | 1, 6        | V <sub>1,6</sub> | - 0,5 | + 0,5 | V    |

| Power into RF-IF Ports         | 1, 6        | $P_{in,RF}$      |       | 17    | dBm  |

| Power into LO Input            | 3           | $P_{in,LO}$      |       | 10    | dBm  |

| Operating Temperature          |             | $T_{op}$         | -40   | +85   | °C   |

| Channel Temperature            |             | $T_Ch$           |       | 150   | °C   |

| Storage Temperature            |             | $T_{stg}$        | -55   | 150   | °C   |

| Thermal Resistance             |             |                  |       |       |      |

| Channel to Soldering Point (GN | $R_{thChS}$ | ≤100             |       | K/W   |      |

<sup>1)</sup> For detailed dimensions see page 7.

<sup>2)</sup> For DC test purposes only, no DC voltages at pins 1, 6 in application

#### **Electrical Characteristics:**

**Test conditions:**  $T_a = 25$ °C;  $V_{DD} = 3$ V, see test circuit;  $f_{RF} = 808$ MHz;  $f_{LO} = 965$ MHz;  $P_{LO} = 0$ dBm;  $f_{IF} = 157$ MHz, unless otherwise specified:

| Parameter, Test Conditions                                                                                            | Symbol              | min | typ    | max | Unit |

|-----------------------------------------------------------------------------------------------------------------------|---------------------|-----|--------|-----|------|

| Operating Current                                                                                                     | I <sub>op</sub>     | ı   | 2.5    | 4.0 | mA   |

| Conversion Loss                                                                                                       | L <sub>c</sub>      | ı   | 6.0    | 7.5 | dB   |

| SSB Noise Figure                                                                                                      | F <sub>ssb</sub>    | ı   | 6.0    | ı   | dB   |

| 2 Tone 3rd Order IMD<br>$P_{RF1} = P_{RF2} = -3dBm$<br>$f_{RF1} = 806MHz$ ; $f_{RF2} = 810MHz$ ;<br>$f_{LO} = 965MHz$ | d <sub>IM3</sub>    | 1   | 41     | 1   | dBc  |

| 3rd Order Input Intercept Point                                                                                       | IP3 <sub>in</sub>   | 16  | 17.5   | ı   | dBm  |

| P <sub>-1dB</sub> Input Power                                                                                         | P <sub>-1dB</sub>   | ı   | t.b.d. | ı   | dBm  |

| LO Leakage at RF/IF-Port (1,6)                                                                                        | P <sub>LO 1,6</sub> | -   | -13    | -   | dBm  |

## **Applications Information:**

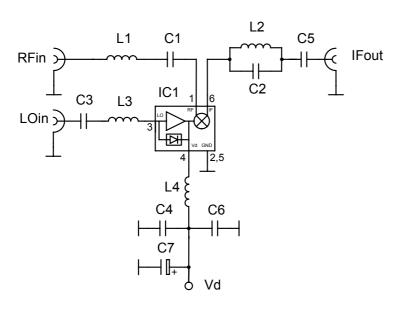

Test circuit / application example

Notes for external elements:

L1, C1: Filter for upper frequency; C2, L2: Filter for lower frequency; each filter is a throughpath for the desired frequency (RF or IF) and isolates the other frequency (IF or RF) and its harmonics. These two filters must be connected to pin 1 and pin 6 directly.

Parasitic capacitances at the ports 1 and 6 must be as small as possible.

L4 and C4 are optimized by indicating lowest *l*<sub>op</sub> at used LO-frequency; same procedure for L3. The ports 1, 3 and 6 must be DC open.

Element values for 800MHz test and application circuit:

|   | f LO | F <i>RF</i> | F <i>IF</i> | L1 | C1  | L2 | C2  | L3  | C3 | L4 | C4 | C5 | C6   | C7   |

|---|------|-------------|-------------|----|-----|----|-----|-----|----|----|----|----|------|------|

|   | MHz  | MHz         | MHz         | nΗ | рF  | nΗ | рF  | nΗ  | рF | nΗ | рF | nF |      | μF   |

| ſ | 965  | 808         | 157         | 10 | 3.9 | 10 | 3.3 | 6.8 | 47 | 15 | 33 | 1  | n.c. | 0.47 |

# **Applications Information, Continued:**

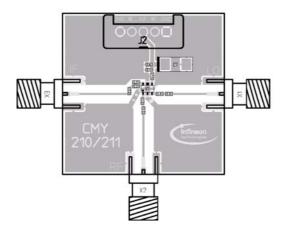

PCB-Layout for 800MHz test and application circuit (Size: 35 x 35mm):

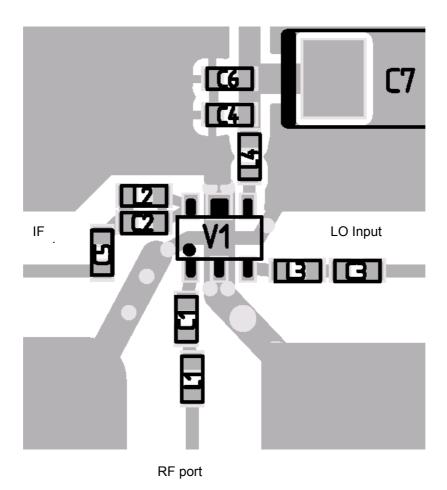

#### PCB Layout detail:

# **Applications Information, Continued:**

Typical lumped element values for different RF-frequencies:

| f <i>RF</i> | L1  | C1  | L2  | C2  |

|-------------|-----|-----|-----|-----|

| MHz         | nΗ  | pF  | nΗ  | pF  |

| 400         | 12  | 15  | 12  | 12  |

| 450         | 12  | 12  | 12  | 10  |

| 900         | 8.2 | 3.9 | 8.2 | 3.3 |

| 1500        | 3.3 | 2.7 | 3.3 | 2.2 |

| 1800        | 3.3 | 2.2 | 3.3 | 1.8 |

| 2000        | 3.3 | 1.8 | 3.3 | 1.2 |

| 2400        | 1.8 | 2.7 | 1.8 | 1.5 |

Typical lumped element values for different LO-frequencies:

| f LO | L3  | C3 | L4  | C4 |

|------|-----|----|-----|----|

| MHz  | nΗ  | pF | nΗ  | pF |

| 500  | 15  | 82 | 47  | 82 |

| 750  | 6.8 | 33 | 22  | 33 |

| 800  | 6.8 | 33 | 18  | 33 |

| 950  | 6.8 | 27 | 15  | 27 |

| 1100 | 6.8 | 27 | 12  | 27 |

| 1400 | 6.8 | 22 | 6.8 | 22 |

| 1600 | 6.8 | 18 | 4.7 | 18 |

| 1800 | 6.8 | 15 | 3.3 | 15 |

| 2000 | 6.8 | 12 | 2.2 | 12 |

| 2100 | 6.8 | 12 | 1.8 | 12 |

| 2300 | 4.7 | 12 | 1.2 | 12 |

#### **Electrical Characteristics, Continued:**

#### General description and notes:

The CMY 211 is an all port single ended general purpose Up- and Down-Converter. It combines small conversion losses and excellent intermodulation characteristics with a low demand of LO- and DC-power.

The internal level controlled LO-Buffer enables a good performance over a wide LO level range. The internal mixers principle with one port RF and IF requires a frequency separation at pin 1 and 6 respectively.

#### Note 1:

Best performance with lowest conversion loss is achieved when each circuit or device for the frequency separation meets the following requirements:

**Input Filter:** Throughpass for the signal to be mixed; reflection of the mixed signal and the harmonics of both.

**Output Filter:** Throughpass for the mixed signal and reflection of the signal to be mixed and the harmonics of both.

The impedance for the reflecting frequency range of each filter toward the ports 1 and 6 should be as high as possible.

In the simplest case a series- and a parallel- resonator circuit will meet these requirements but also others as appropriate drop in filters or micro stripline elements can be used.

The two branches with filters should meet immediately at the package leads of the port 1 and 6. Parasitic capacitances at these ports must be kept as small as possible.

The mixer also can be driven with a source- and a load impedance different to  $50\Omega$ , but performance will degrade at larger deviations.

#### Note 2:

The LO-Buffer needs an external inductor L4 at port 4; the value of inductance depends on the LO frequency. It is tuned for minimum *l*<sub>op</sub> consumption into port 4.

#### Note 3:

The LO Input impedance at Port 3 can be matched with a series inductor. It also can be tuned for a minimum current  $I_{op}$  into port 4. C3 is a DC blocking capacitor.

Since the input impedance of port 3 can be slightly negative, the source reflection coefficient should be kept below 0.8 ( $Z_0 = 50 \Omega$ ).

The Conversion Noise Figure Fssb is corresponding with the value of Conversion Loss  $L_c$ . The LO signal must be clean of noise and spurious at the frequencies  $f_{Lo} \pm f_{IE}$ .

### Semiconductor Device Outline MW-6:

Gradient Dim. min. nom. max. Remark Α 1.1 0.1 A<sub>1</sub>  $A_2$ 1.0 0.3 b 0.6  $b_1$ 0.08 С 0.15 D 2.8 3.0 Ε 1.2 1.4 |e| 0.95 1.9  $|e_1|$ 2.6  $H_{\mathsf{F}}$  $\mathsf{L}_\mathsf{F}$ 0.6 max 10° а 2°...30° q

1. Applicable on all case top sides

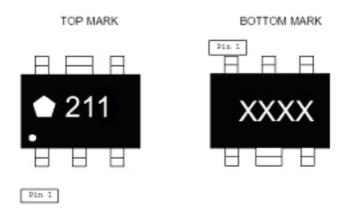

#### **Part Marking:**

#### Part Orientation on Reel:

## **Ordering Information:**

| Type   | Marking | Ordering code (tape and reel) | Package <sup>1)</sup> |

|--------|---------|-------------------------------|-----------------------|

| CMY211 | M4s     | Q62702-M0017                  | MW-6                  |

# ESD: **E**lectro**s**tatic **d**ischarge sensitive device Observe handling Precautions!

Published by TriQuint Semiconductor GmbH, Marketing, Konrad-Zuse-Platz 1, D-81829 Munich.

Copyright TriQuint Semiconductor GmbH 2003. All Rights Reserved.

As far as patents or other rights of third parties are concerned, liability is only assumed for components per se, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

### **CMY211 Datasheet**

For questions on technology, delivery, and prices please contact the Offices of TriQuint Semiconductor in Germany or the TriQuint Semiconductor Companies and Representatives worldwide.

Due to technical requirements components may contain dangerous substances. For information on the type in question please contact your nearest TriQuint Semiconductors Office.