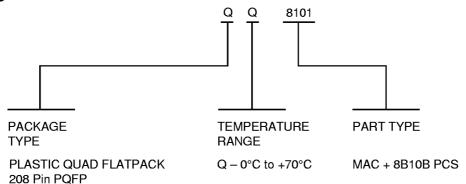

# 8101 Gigabit Ethernet Controller

99110

This document is an LSI Logic document. Any reference to SEEQ Technology should be considered LSI Logic.

Note: Check for latest Data Sheet revision before starting any designs.

SEEQ Data Sheets are now on the Web, access SEEQ Home Page www.seeq.com

- or -

LSI Logic at www.lsilogic.com

# Features

- Pin Compatible Upgrade of Seeq 8100

- Combined Ethernet MAC and 8B10B PCS

- Data Rate 1000 Mbps

- 64-Bit @ 66 Mhz Interface to External Bus 4 Gbps Bandwidth

- 10-Bit Interface to External PHY or SerDes Chip

- 16-Bit Interface to Internal Registers and Management Counters

- Full RMON, SNMP, Ethernet Management Counter Support

- Independent Receive and Transmit FIFO's with Programmable Watermarks Receive FIFO Size - 16K Bytes Transmit FIFO Size - 4K Bytes

- AutoNegotiation Algorithm On Chip

- Full Duplex Only

- Flow Control per IEEE 802.3x

- Automatic CRC Generation and Checking

- Automatic Packet Error Discarding

- Programmable Transmit Start Threshold

- Interrupt Capability

- Supports Fiber and Short Haul Copper Media

- 3.3v Power Supply, 5v Tolerant Inputs

- Meets all applicable IEEE 802.3 and 802.3z Specifications

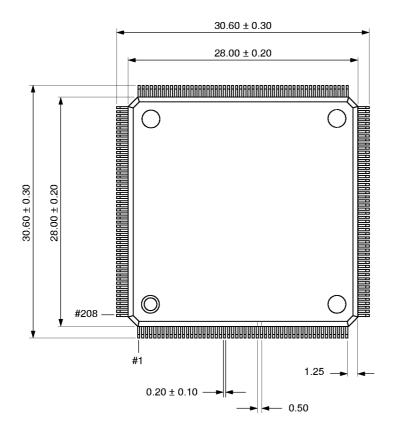

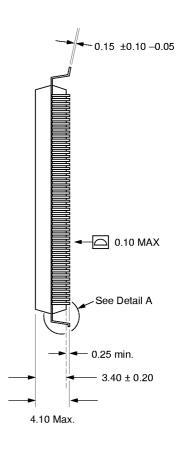

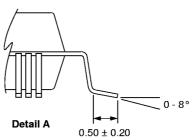

- **■** 208L PQFP

# Description

The 8101 is a Ethernet controller for gigabit applications. The 8101 integrates the Media Access Control sublayer (MAC) and the Physical Coding Sublayer (PCS) for fiber and short haul copper media.

The 8101 is an improved version of the Seeq 8100. The 8101 is also pin compatible with the 8100 with the exception that the 8101 is powered from a 3.3V supply voltage. All inputs and outputs on the 8101 are 5V tolerant.

The 8101 consists of a full duplex Ethernet MAC, receive/ transmit FIFO's, 32-bit System Interface, 8B10B encoder/ decoder, 10-bit PHY Interface, and a 16-bit Register Interface.

The 8101 also contains all the necessary circuitry to implement the flow control algorithm defined by IEEE 802.3x. Flow control messages can be sent automatically without any host intervention.

The 8101 contains 53 counters that completely satisfies the management objectives of the RMON Statistics Group MIB, (RFC 1757), SNMP Interfaces Group MIB (RFC 1213 & 1573), Ethernet-Like Group MIB (RFC 1643) and Ethernet MIB (IEEE 802.3z Clause 30).

The 8101 contains one hundred thirty six internal 16-bit registers that can be accessed though the Register Interface. These registers contain configuration inputs, status outputs, and management counter results.

The 8101 is ideal as an Ethernet controller for Gigabit Ethernet switch ports, uplinks, backbones, and adapter cards

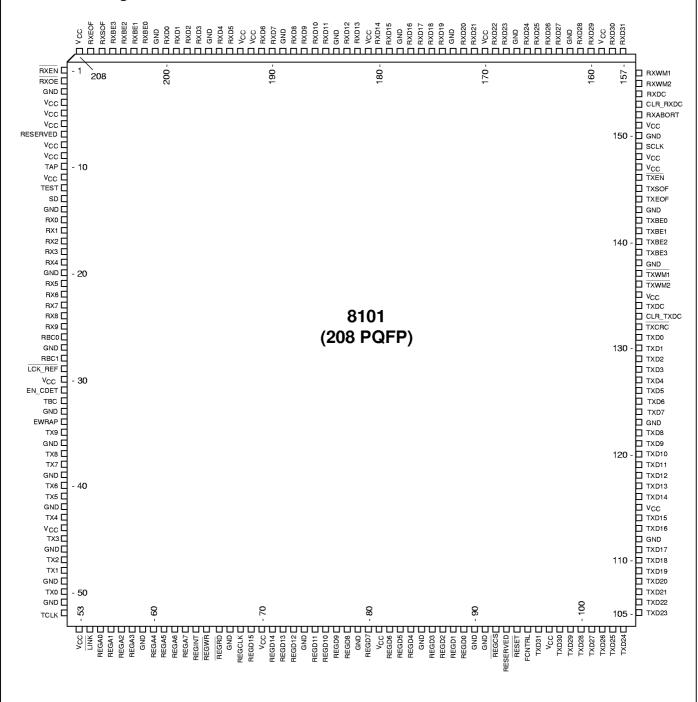

# Pin Configuration

# Table of Contents

# 1.0 Pin Description

# 2.0 Block Diagram

# 3.0 Functional Description

# 3.1 GENERAL

# 3.2 ETHERNET FRAME FORMAT

- 3.2.1 General

- 3.2.2 Preamble & SFD

- 3.2.3 Destination Address

- 3.2.4 Source Address

- 3.2.5 Length/Type Field

- 3.2.6 Data

- 3.2.7 Frame Check Sequence

- 3.2.8 Interpacket Gap

# 3.3 SYSTEM INTERFACE

- 3.3.1 General

- 3.3.2 Data Format and Bit Order

- 3.3.3 Transmit Timing

- 3.3.4 Receive Timing

- 3.3.5 Bus Width

- 3.3.6 System Interface Disable

#### 3.4 TRANSMIT MAC

- 3.4.1 General

- 3.4.2 Preamble & SFD Generation

- 3.4.3 AutoPad

- 3.4.4 CRC Generation

- 3.4.5 Interpacket Gap

- 3.4.6 MAC Control Frame Generation

# 3.5 RECEIVE MAC

- 3.5.1 General

- 3.5.2 Preamble & SFD Stripping

- 3.5.3 CRC Stripping

- 3.5.4 Unicast Address Filter

- 3.5.5 Multicast Address Filter

- 3.5.6 Broadcast Address Filter

- 3.5.7 Reject Or Accept All Packets

- 3.5.8 Frame Validity Checks

- 3.5.9 Maximum Packet Size

- 3.5.10 MAC Control Frame Check

#### 3.6 TRANSMIT FIFO

- 3.6.1 General

- 3.6.2 AutoSend

- 3.6.3 Watermarks

- 3.6.4 TX Underflow

- 3.6.5 TX Overflow

- 3.6.6 Link Down FIFO Flush

# 3.6 RECEIVE FIFO

- 3.6.1 General

- 3.6.2 Watermarks

- 3.6.3 RX Overflow

- 3.6.4 RX Underflow

#### 3.7 8B10B PCS

- 3.7.1 Transmit

- 3.7.2 Receive

- 3.7.3 8B10B Encoder

- 3.7.4 8B10B Decoder 3.7.5 Start of Packet

- 3.7.6 End Of Packet

- 3.7.7 Idle

- 3.7.8 Receive Word Synchronization

- 3.7.9 AutoNegotiation

#### 3.8 10-BIT PHY INTERFACE

- 3.8.1 General

- 3.8.2 Data Format and Bit Order

- 3.8.3 Transmit

- 3.8.4 Receive

- 3.8.5 Lock To Reference

- 3.8.6 PHY Loopback

- 3.8.7 Signal Detect

- 3.8.8 TBC Disable

# 3.9 PACKET DISCARD

- 3.9.1 General

- 3.9.2 Transmit Discards

- 3.9.3 Receive Discards

- 3.9.4 Discard Output Indication

- 3.9.5 AutoClear Mode

- 3.9.6 AutoAbort Mode

# 3.10 RECEIVE STATUS WORD

- 3.10.1 General

- 3.10.2 Format

- 3.10.3 Append Options

- 3.10.4 Status Word for Discarded Packets

- 3.10.5 Status Word for RXABORT Packets

# 3.11 AUTONEGOTIATION

- 3.11.1 General

- 3.11.2 Next Page

- 3.11.3 Negotiation Status

- 3.11.4 AutoNegotiation Restart

- 3.11.5 AutoNegotiation Disable

- 3.11.6 Link Indication

# 3.12 FLOW CONTROL

# 3.13 MAC CONTROL FRAMES

# Table of Contents (cont'd)

3.13.1 General

3.13.2 Automatic Pause Frame Generation

3.13.3 Transmitter Pause Disable

3.13.4 Passthrough to FIFO

3.13.5 Reserved Multicast Address Disable

3.13.6 MAC Control Frame AutoSend

# 3.14 RESET

# 3.15 COUNTERS

3.15.1 General

3.15.2 Counter Half Full

3.15.3 Counter Reset On Read

3.15.4 Counter Rollover

3.15.5 Counter Maximum Packet Size

3.15.6 Counter Reset

# 3.16 LOOPBACK

# 3.17 TEST MODE

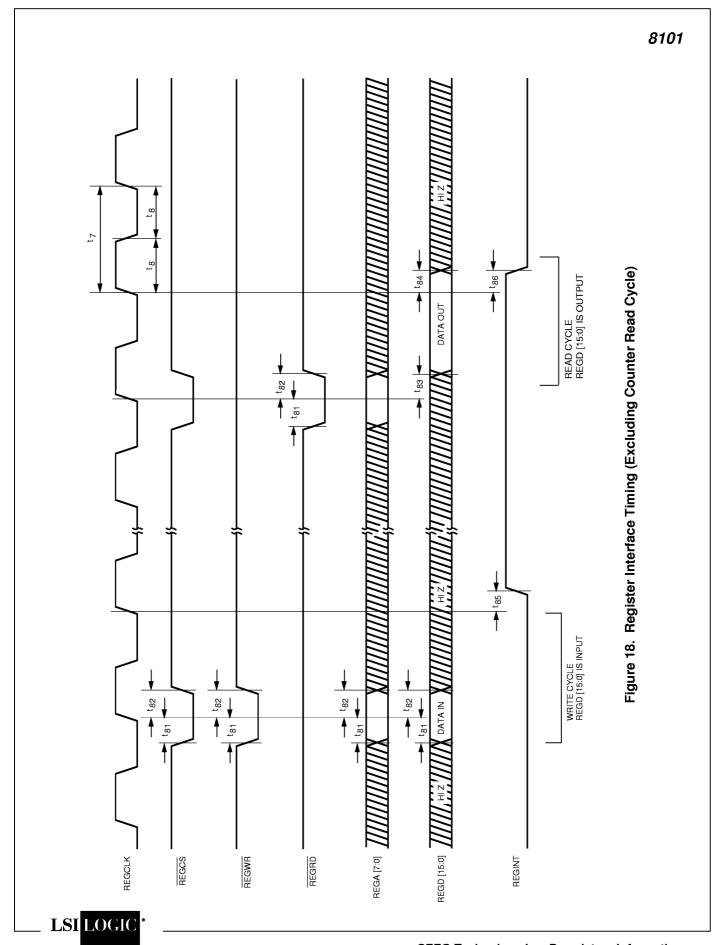

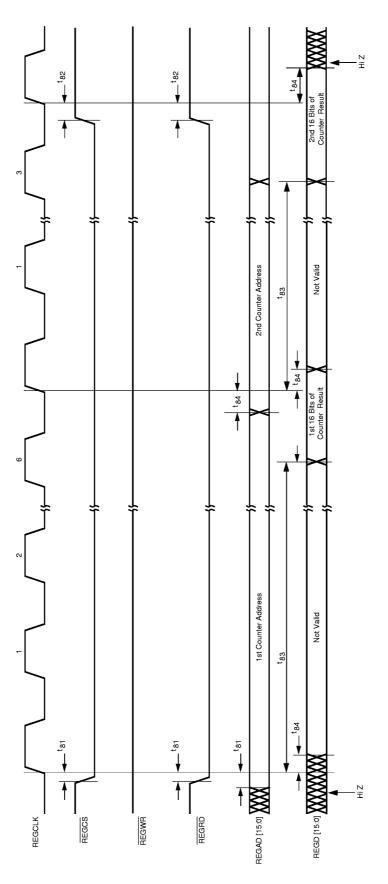

# 3.18 REGISTER INTERFACE

3.18.1 General

3.18.2 Bit Types

3.18.3 Interrupt

3.18.4 Register Structure

# 4.0 Registers

# 5.0 Application Information

# 5.1 EXAMPLE SCHEMATICS

**5.2 PHY INTERFACE**

5.2.1 External Physical Layer Devices

5.2.2 PCB Layout

# **5.3 SYSTEM INTERFACE**

5.3.1 Watermarks

5.3.2 PCB Layout

5.4 RESET

5.5 LOOPBACK

# 5.6 AUTONEGOTIATION

5.6.1 AutoNegotion at Powerup

5.6.2 Negotiation with a

Non-AutoNegotiation Able Device

# **5.7 MANAGEMENT COUNTERS**

5.7.1 Relationship to IETF and IEEE Specs

5.7.2 TX Packet & Octet Counters

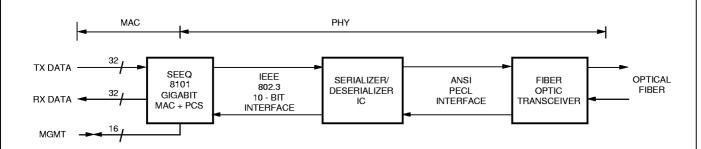

5.8 POWER SUPPLY DECOUPLING

# 6.0 Specifications

6.1 ABSOLUTE MAXIMUM RATINGS

6.2 DC ELECTRICAL CHARACTERISTICS

6.3 AC ELECTRICAL CHARACTERISTICS

# 1.0 Pin Description

| Pin #                                                                                                                                        | Pin Name    | I/O | Description                                                                                                                                                                                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Su                                                                                                                                     | pplies      |     |                                                                                                                                                                                                                                                                                                                               |

| 4 5 6<br>8 9 11<br>30 44<br>53 70<br>81 97<br>115 135<br>147 148<br>151 159<br>170 181<br>192 193<br>208                                     | VCC[22:0]   |     | Positive Supply. +3.3v +/-5% Volts.                                                                                                                                                                                                                                                                                           |

| 3 14 20<br>27 33 36<br>39 42 46<br>49 51 59<br>67 74 79<br>85 90 91<br>112 123<br>138 143<br>150 162<br>167 173<br>178 184<br>189 196<br>201 | GND[30:0]   |     | Ground. 0 Volts.                                                                                                                                                                                                                                                                                                              |

| 10-Bit PH                                                                                                                                    | Y Interface |     |                                                                                                                                                                                                                                                                                                                               |

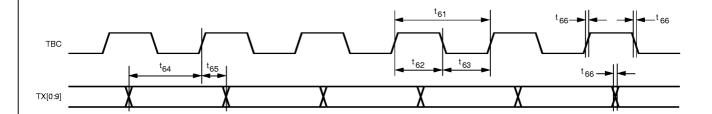

| 32                                                                                                                                           | TBC         | 0   | <b>Transmit Clock Output.</b> This 10-Bit PHY Interface output clocks transmit data out on TX[0:9] on rising edges. TBC is a 125 MHZ clock and is generated from TCLK.                                                                                                                                                        |

| 50 48 47<br>45 43 41<br>40 38 37<br>35                                                                                                       | TX[0:9]     | 0   | Transmit Data Output. These 10-Bit PHY Interface outputs contain transmit data which are clocked out on rising edges of TBC.                                                                                                                                                                                                  |

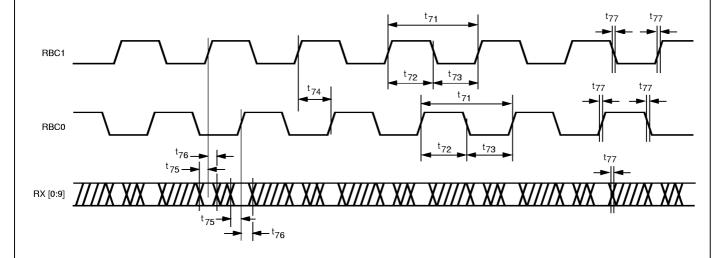

| 28<br>26                                                                                                                                     | RBC[1:0]    | I   | Receive Clock Input. These 10-Bit PHY Interface inputs clock in receive data on RX[0:9] on rising edges. RBC[1:0] are 62.5 MHZ clocks, 180° out of phase, used to clock in data on RX[0:9] at an effective 125 MHZ rate. For the device to acquire sync, the comma code must be input on RXD[0:9] on RBC1 rising edges.       |

| 15 16 17<br>18 19 21<br>22 23 24<br>25                                                                                                       | RX[0:9]     | I   | Receive Data Input. These 10-Bit PHY Interface inputs contain receive data which are clocked in on rising edges of RBC[1:0].                                                                                                                                                                                                  |

| 31                                                                                                                                           | EN_CDET     | 0   | Comma Detect Enable Output. This 10-Bit PHY Interface output is asserted when either the receive 8B10B PCS state machine is in the loss of synchronization state or the EN_CDET bit is set in the internal Registers. This output is typically used to enable the comma detect function in an external Physical Layer device. |

| Pin#                                                                                                                                                                      | Pin Name  | I/O | Description                                                                                                                                                                                                                                                                                                           |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 34                                                                                                                                                                        | EWRAP     | 0   | Loopback Output Enable. This 10-Bit PHY Interface output is asserted whenever the EWRAP bit is set in the internal Registers. This output is typically used to enable loopback in an external Physical Layer device.                                                                                                  |  |  |

| 29                                                                                                                                                                        | LCK_REF   | 0   | Receiver Lock Output. This 10-Bit PHY Interface output is asserted whenever the LCK_REF bit is set in the internal Registers. This output is typically used to enable the receive lock-to-reference mechanism in an external Physical Layer device.                                                                   |  |  |

| System I                                                                                                                                                                  | nterface  |     |                                                                                                                                                                                                                                                                                                                       |  |  |

| 149                                                                                                                                                                       | SCLK      | I   | System Interface Clock Input. This input clocks data in and out of the receive and transmit FIFO's on TXD[31:0] and RXD[31:0], respectively. All System Interface inputs and outputs are also clocked in and out on rising edges of SCLK, with the exception of RXOE. SCLK clock frequency must be between 33-66 MHZ. |  |  |

| 146                                                                                                                                                                       | TXEN      | I   | <b>Transmit Enable Input.</b> This input has to be asserted active low to enable the current data word on TXD[31:0] to be clocked into the transmit FIFO. TXEN is clocked in on rising edges of system interface clock, SCLK.                                                                                         |  |  |

| 96 98<br>99 100<br>101 102<br>103 104<br>105 106<br>107 108<br>109 110<br>111 113<br>114 116<br>117 118<br>119 120<br>121 122<br>124 125<br>126 127<br>128 129<br>130 131 | TXD[31:0] | I   | Transmit Data Input. This input bus contains the 32-bit data word that is clocked into the transmit FIFO on rising edges of the system interface clock, SCLK.                                                                                                                                                         |  |  |

| 139<br>140<br>141<br>142                                                                                                                                                  | TXBE[3:0] | I   | <b>Transmit Byte Enable Input.</b> These inputs determine which bytes of the current 32-bit word on TXD[31:0] contain valid data. TXBE[3:0] is clocked into the device on rising edges of the system interface clock, SCLK.                                                                                           |  |  |

| 145                                                                                                                                                                       | TXSOF     | I   | Transmit Start Of Frame Indication. This input has to be asserted active high on the same clock cycle when first word of the packet is being clocked in on TXD[31:0]. TXSOF is clocked into the device on rising edges of the system interface clock, SCLK.                                                           |  |  |

| 144                                                                                                                                                                       | TXEOF     | I   | Transmit End Of Frame Indication. This input has to be asserted active high on the same clock cycle when the last word of the packet is being clocked in on TXD[31:0]. TXEOF is clocked into the device on rising edges of the system interface clock, SCLK.                                                          |  |  |

| 137                                                                                                                                                                       | TXWM1     | 0   | Transmit FIFO Watermark 1 Output.                                                                                                                                                                                                                                                                                     |  |  |

|                                                                                                                                                                           |           |     | 1 = Transmit FIFO Data ≤ Transmit FIFO Watermark 1 Threshold<br>0 = Above Threshold                                                                                                                                                                                                                                   |  |  |

|                                                                                                                                                                           |           |     | TXWM1 is clocked out on rising edges of the system clock, SCLK.                                                                                                                                                                                                                                                       |  |  |

| Pin # | Pin Name | I/O | Description                                                                                                                                                                                                                                                          |  |  |

|-------|----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 136   | TXWM2    | 0   | Transmit FIFO Watermark 2 Output.                                                                                                                                                                                                                                    |  |  |

|       |          |     | 1 = Transmit FIFO Data ≤ Transmit FIFO Watermark 2 Threshold<br>0 = Above Threshold                                                                                                                                                                                  |  |  |

|       |          |     | TXWM2 is clocked out on rising edges of the system clock, SCLK                                                                                                                                                                                                       |  |  |

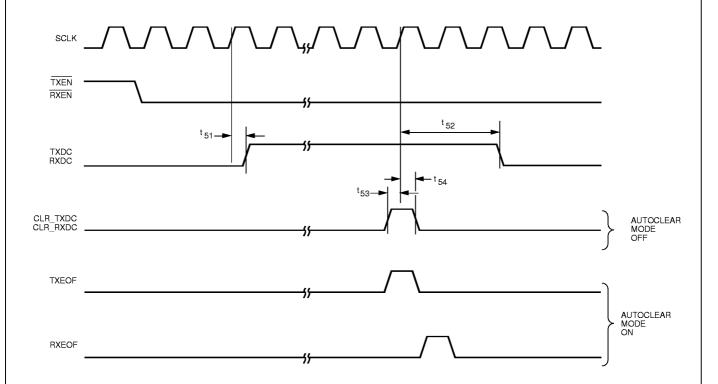

| 134   | TXDC     | 0   | Transmit Packet Discard Output.                                                                                                                                                                                                                                      |  |  |

|       |          |     | Device Detects that Current Packet Being Input on the System Interface     has an Error, Rest of Packet Ignored.                                                                                                                                                     |  |  |

|       |          |     | 0 = No Discard                                                                                                                                                                                                                                                       |  |  |

|       |          |     | TXDC is clocked out on rising edges of the system clock, SCLK.                                                                                                                                                                                                       |  |  |

|       |          |     | If Autoclear Mode is not enabled, this output is latched high and stays latched until cleared with the CLR_TXDC pin. If Autoclear Mode is enabled, this output is latched high and automatically clears itself low two clock cycles after the next TXEOF occurrence. |  |  |

| 133   | CLR_TXDC | ı   | Clear TXDC Input.                                                                                                                                                                                                                                                    |  |  |

|       |          |     | 1 = TXDC Pin Cleared Low 0 = Not Cleared                                                                                                                                                                                                                             |  |  |

|       |          |     | TXDC is clocked in on rising edges of the system clock, SCLK.                                                                                                                                                                                                        |  |  |

|       |          |     | This pin only clears TXDC when Autoclear Mode is disabled. When Autoclear Mode is enabled, this pin is ignored and TXDC is automatically cleared two clock cycles after the next TXEOF occurrence.                                                                   |  |  |

| 95    | FCNTRL   | ı   | Flow Control Enable Input.                                                                                                                                                                                                                                           |  |  |

|       |          |     | 1 = Transmitter Automatically Transmit a MAC Control Pause Frame<br>0 = Normal Operation                                                                                                                                                                             |  |  |

|       |          |     | FCNTRL is clocked in on rising edges of the system clock, SCLK.                                                                                                                                                                                                      |  |  |

| 132   | TXCRC    | ı   | Transmit CRC Enable Input.                                                                                                                                                                                                                                           |  |  |

|       |          |     | 1 = No CRC                                                                                                                                                                                                                                                           |  |  |

|       |          |     | 0 = CRC Calculated and Appended to Current Packet Being Inputted<br>on System Interface                                                                                                                                                                              |  |  |

|       |          |     | TXCRC is clocked in on rising edges of the system clock, SCLK, and must be asserted on the same SCLK clock cycle as TXSOF.                                                                                                                                           |  |  |

| 1     | RXEN     | I   | Receive Enable Input. This input has to be asserted active low to enable the current data word to be clocked out of the receive FIFO on RXD[31:0]. RXEN is clocked in on rising edges of system interface clock, SCLK.                                               |  |  |

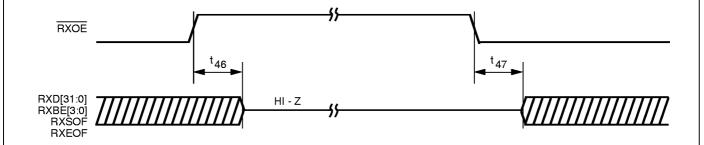

| 2     | RXOE     | ı   | Receive Output Enable Input.                                                                                                                                                                                                                                         |  |  |

|       |          |     | 1 = Receive Outputs High Impedance (RXD[31:0], RXBE[3:0], RXSOF, RXEOF) 0 = Receive Outputs Active                                                                                                                                                                   |  |  |

| Pin #                                                                                                                                                                        | Pin Name  | I/O | Description                                                                                                                                                                                                                                                                                                       |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 157 158<br>160 161<br>163 164<br>165 166<br>168 169<br>171 172<br>174 175<br>176 177<br>179 180<br>182 183<br>185 186<br>187 188<br>190 191<br>194 195<br>197 198<br>199 200 | RXD[31:0] | 0   | Receive Data Input. This output bus contains the 32-bit data word that is clocked out of the receive FIFO on rising edges of the system interface clock, SCLK.                                                                                                                                                    |  |

| 205<br>204<br>203<br>202                                                                                                                                                     | RXBE[3:0] | 0   | Receive Byte Enable Output. These outputs determine which bytes of the current 32-bit word on RXD[31:0] contain valid data. RXBE[3:0] is clocked out of the device on rising edges of the system interface clock, SCLK.                                                                                           |  |

| 206                                                                                                                                                                          | RXSOF     | 0   | Receive Start Of Frame Indication. This output is asserted active high on the same clock cycle when the first word of the packet is being read out of the receive FIFO on RXD[31:0]. RXSOF is clocked out of the device on rising edges of the system interface clock, SCLK.                                      |  |

| 207                                                                                                                                                                          | RXEOF     | 0   | Receive End Of Frame Indication. This output is asserted active high on the same clock cycle when the last word of the packet is being read out of the receive FIFO on RXD[31:0]. RXEOF is clocked out of the device on rising edges of the system interface clock, SCLK.                                         |  |

| 156                                                                                                                                                                          | RXWM1     | 0   | Receive FIFO Watermark 1 Output.                                                                                                                                                                                                                                                                                  |  |

|                                                                                                                                                                              |           |     | 1 = Receive FIFO Data > Receive FIFO Watermark 1 Threshold<br>0 = Equal to or Below Threshold                                                                                                                                                                                                                     |  |

|                                                                                                                                                                              |           |     | RXWM1 is clocked out on rising edges of the system clock, SCLK. Data is valid on RXD[31:0] when either RXWM1 or RXWM2 is asserted high, independent of RXEN.                                                                                                                                                      |  |

| 155                                                                                                                                                                          | RXWM2     | 0   | Receive FIFO Watermark 2 Output.                                                                                                                                                                                                                                                                                  |  |

|                                                                                                                                                                              |           |     | 1 = Receive FIFO > Receive FIFO Watermark 2 Threshold Or Complete Packet Loaded Into Receive FIFO 0 = Equal to or Below Threshold and no EOF in FIFO RXWM2 is clocked out on rising edges of the system clock, SCLK. Data is valid on RXD[31:0] when either RXWM1 or RXWM2 is asserted high, independent of RXEN. |  |

| Pin #                                                          | Pin Name   | I/O | Description                                                                                                                                                                                                                                                                                                                        |  |  |

|----------------------------------------------------------------|------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 154                                                            | RXDC       | 0   | Receive Packet Discard Output.                                                                                                                                                                                                                                                                                                     |  |  |

|                                                                |            |     | <ul> <li>1 = Device Detects that Current Packet Being Output on the System Interface has an Error and Should be Discarded.</li> <li>0 = No Discard</li> </ul>                                                                                                                                                                      |  |  |

|                                                                |            |     | Packet being output on System Interface can be discarded by asserting the RXABORT pin or automatically discarded if AUTORXAB bit is set. RXDC is clocked out on rising edges of the system clock, SCLK.                                                                                                                            |  |  |

|                                                                |            |     | If Autoclear Mode is not enabled, this output is latched high and stays latched until cleared with the CLR_RXDC pin. If Autoclear Mode is enabled, this output is latched high and automatically clears itself low two clock cycles after the next RXEOF occurrence. RXDC can also be cleared with RXABORT if programmed to do so. |  |  |

| 153                                                            | CLR_RXDC   | 1   | Clear RXDC Input.                                                                                                                                                                                                                                                                                                                  |  |  |

|                                                                |            |     | 1 = RXDC Pin Cleared Low<br>0 = Not Cleared                                                                                                                                                                                                                                                                                        |  |  |

|                                                                |            |     | CLR_RXDC is clocked in on rising edges of the system clock, SCLK.                                                                                                                                                                                                                                                                  |  |  |

|                                                                |            |     | This pin only clears RXDC when Autoclear Mode is disabled. When Autoclear Mode is enabled, this pin is ignored and RXDC is automatically cleared two clock cycles after the next RXEOF occurrence.                                                                                                                                 |  |  |

| 152                                                            | RXABORT    | I   | Receive FIFO Data Abort Input.                                                                                                                                                                                                                                                                                                     |  |  |

|                                                                |            |     | 1 = Abort & Discard Receive Packet Being Read Out On RXD[31:0]<br>0 = No Discard                                                                                                                                                                                                                                                   |  |  |

|                                                                |            |     | RXABORT is clocked in on rising edges of the system clock, SCLK.                                                                                                                                                                                                                                                                   |  |  |

| Register                                                       | Interface  |     |                                                                                                                                                                                                                                                                                                                                    |  |  |

| 92                                                             | REGCS      | I   | Register Interface Chip Select Input. This input has to be asserted active low to enable reading and writing of data on REGD[15:0] and REGA[7:0]. This input is clocked in on rising edges of REGCLK.                                                                                                                              |  |  |

| 68                                                             | REGCLK     | -   | Register Interface Clock Input. This input clocks data in and out on REGD[15:0], REGA[7:0], REGRD, and REGWR on rising edges. REGCLK frequency must be between 5-40 MHz.                                                                                                                                                           |  |  |

| 69 71 72<br>73 75 76<br>77 78 80<br>82 83 84<br>86 87 88<br>89 | REGD[15:0] | I/O | <b>Register Interface Data Bus</b> . This bus is a bidirectional 16-bit data path to and from the internal registers. Data is read/written from/to the internal registers on rising edges of the register clock, REGCLK.                                                                                                           |  |  |

| 63 62 61<br>60 58 57<br>56 55                                  | REGA[7:0]  | Ι   | <b>Register Interface Address Input.</b> These inputs provide the address for the specific internal register to be accessed. These inputs are clocked into the device on rising edges of REGCLK.                                                                                                                                   |  |  |

| 66                                                             | REGRD      | -   | Register Interface Read Input. When this input is asserted active low, the accessed internal register is read out, i.e. data is outputted from the register. This input is clocked into the device on rising edges of REGCLK.                                                                                                      |  |  |

| Pin #    | Pin Name | I/O | Description                                                                                                                                                                                                                   |  |  |

|----------|----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 65       | REGWR    | I   | Register Interface Write Input. When this input is asserted active low, the accessed internal register is written to, i.e. data is inputted to the register. This input is clocked into the device on rising edges of REGCLK. |  |  |

| 64       | REGINT   | 0   | Register Interface Interrupt Output. This output is asserted active high when certain interrupt bits in the registers are set, and it remains latched high until all interrupt bits are read and cleared.                     |  |  |

| Miscella | neous    |     |                                                                                                                                                                                                                               |  |  |

| 52       | TCLK     | _   | Transmit Clock Input. This 125 MHZ input clock is used by the 8B10B PCS Section and generates the 125 MHZ transmit output clock, TBC, used to output data on the 10-Bit PHY Interface.                                        |  |  |

| 54       | LINK     | 0   | Receive Link Output.                                                                                                                                                                                                          |  |  |

|          |          |     | 1 = No Link<br>0 = Receive Link Synchronized & Configured.                                                                                                                                                                    |  |  |

| 13       | SD       | I   | Signal Detect Input                                                                                                                                                                                                           |  |  |

|          |          |     | 1 = Data Detected on Receive 10-Bit PHY Interface is Valid 0 = Data Not Valid, 8B10B PCS Receiver Forced to Loss of Sync State                                                                                                |  |  |

|          |          |     | This pin is ignored (assumed high) unless it is enabled by setting the SD enable bit in the Configuration 3 Register.                                                                                                         |  |  |

| 94       | RESET    | 1   | Reset Input.                                                                                                                                                                                                                  |  |  |

|          |          |     | 1 = Normal                                                                                                                                                                                                                    |  |  |

|          |          |     | 0 = Device Reset, FIFO's Cleared, Counters Cleared, Register Bits<br>Set to Defaults                                                                                                                                          |  |  |

| 10       | TAP      | ı   | Tristate All Pin Input. This pin is used for testing purposes only.                                                                                                                                                           |  |  |

|          |          |     | 1 = All Output and Bidirectional Pins Placed in High Impedance State     0 = Normal Operation                                                                                                                                 |  |  |

| 12       | TEST     | _   | <b>Test Mode Input.</b> This pin is reserved for factory test and must be tied low for proper operation.                                                                                                                      |  |  |

| 7<br>93  | RESERVED |     | Reserved. These pins are reserved and must be left floating.                                                                                                                                                                  |  |  |

MD400176/B

# 3.0 Functional Description

# 3.1 GENERAL

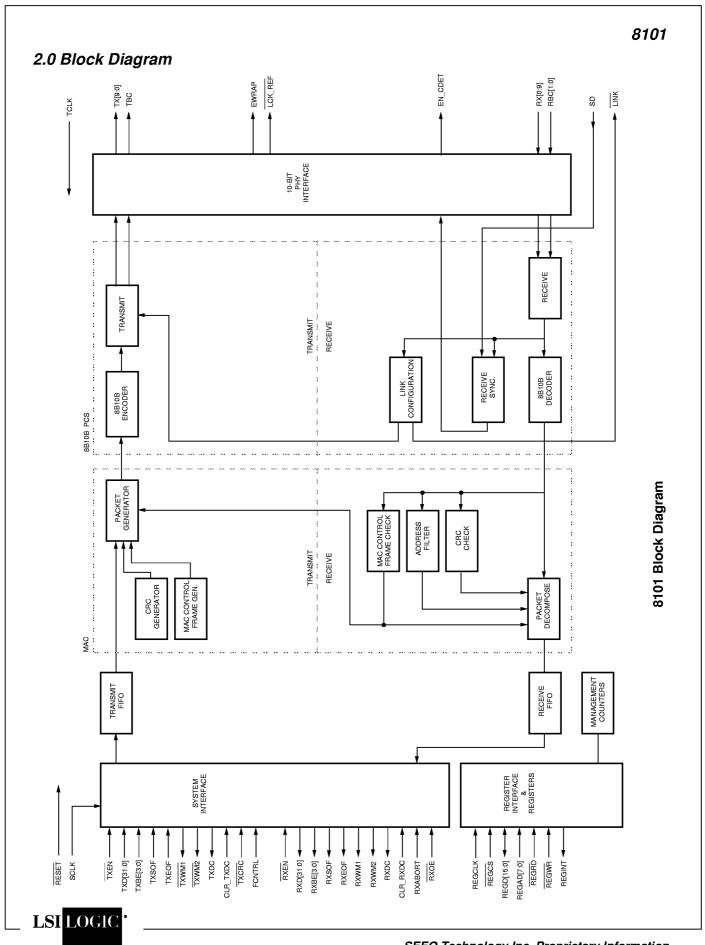

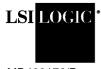

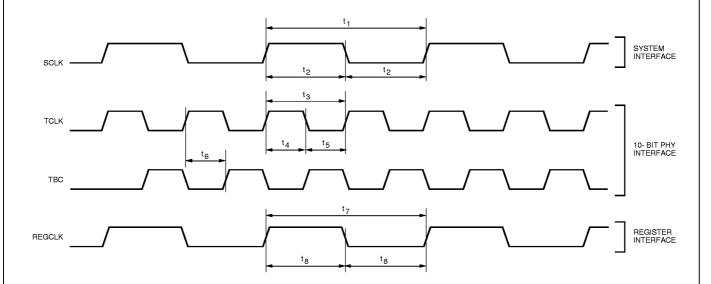

The 8101 is a complete Media Access Controller (MAC sublayer) with integrated coding logic for fiber and short haul copper media (8B10B PCS sublayer) for 1000 Mbps Gigabit Ethernet systems. The 8101 has six main sections: System Interface, FIFO's, MAC, 8B10B PCS, 10-Bit PHY Interface, and Register Interface. A block diagram is shown in Figure 1.

The 8101 has a transmit data path and a receive data path. The transmit data path goes in the System Interface and out the 10-Bit PHY Interface, as shown in the top half of Figure 1. The receive data path goes in the 10-Bit PHY Interface and out the System Interface, as shown in the bottom half of Figure 1.

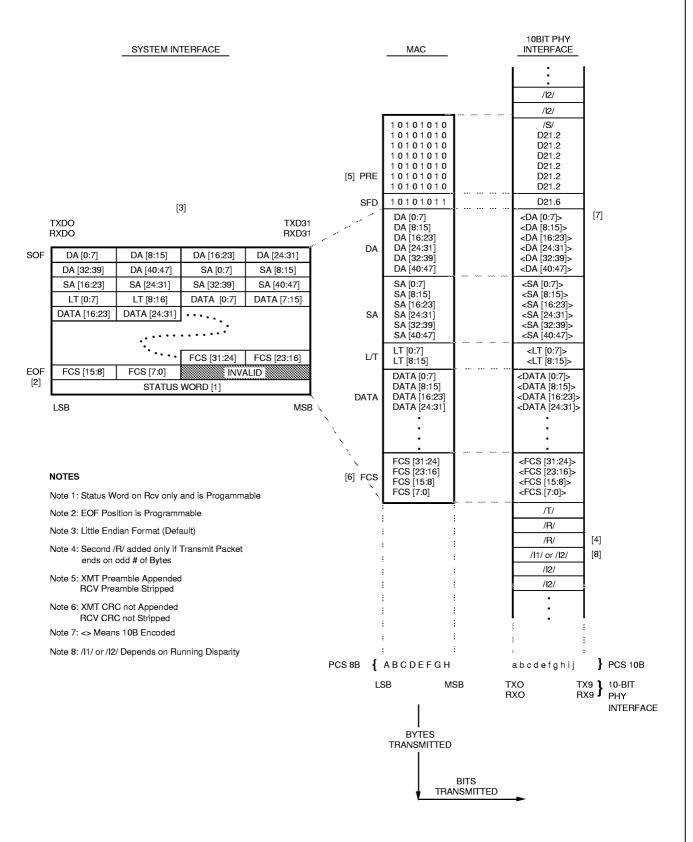

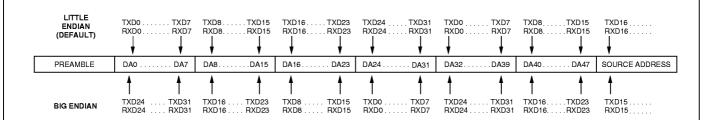

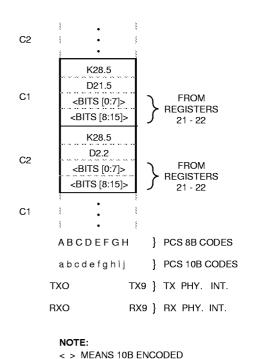

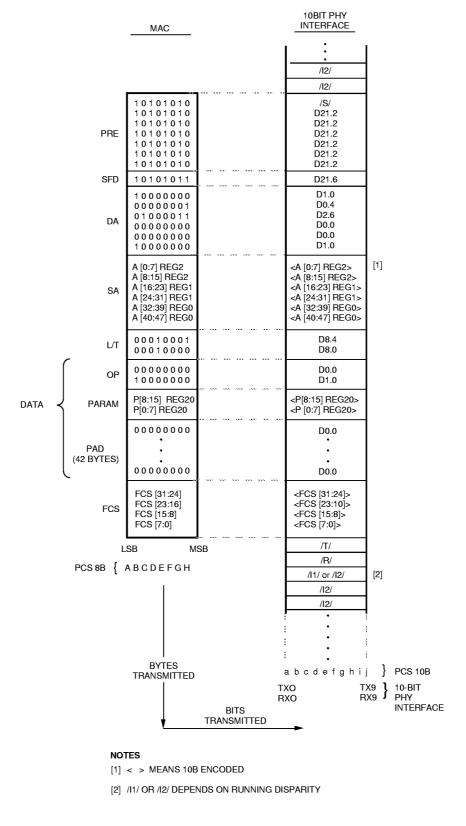

On the transmit data path, data is input into the System Interface from an external bus. The data is then sent to the transmit FIFO. The transmit FIFO provides temporary storage of the data until it is sent to the transmit MAC section. The transmit MAC takes the data and formats it into an Ethernet packet per IEEE 802.3 specifications and shown in Figure 2. The Ethernet packet then goes to the 8B10B PCS section. The 8B10B PCS section encodes the data and adds the appropriate framing delimiters to create a 10-Bit PHY frame as specified in IEEE 802.3z and shown in Figure 3. The encoded data then goes to the 10-Bit PHY Interface for transmission to an external PHY chip. The transmit side also generates MAC Control frames and includes logic for AutoNegotiation.

On the receive data path, the 10-Bit PHY Interface receives incoming encoded data from an external PHY chip. The incoming encoded data must be encoded in the 10-Bit PHY format specified in IEEE 802.3z and shown in Figure 3. The incoming encoded data is then sent to the receive 8B10B PCS block which strips off the framing delimiters, decodes the data, and converts the encoded data into an

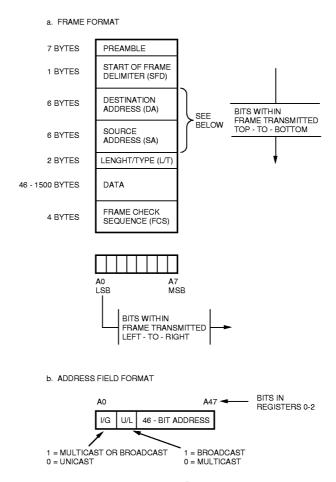

Figure 2. Ethernet MAC Frame Format

Ethernet packet per IEEE 802.3 specifications and shown in Figure 2. The Ethernet packet data is then sent to the receive MAC section. The receive MAC section decomposes the packet, checks the validity of the packet against certain error criteria and address filters, and checks for MAC Control frames. The receive MAC then sends valid packets to the receive FIFO. The receive FIFO provides temporary storage of data until it is demanded by the System Interface. The System Interface outputs the data to an external bus.

The Register Interface is a separate bidirectional 16-bit data bus through which configuration inputs can be set, status outputs can be read, and management counters can be accessed from the internal registers.

Each block plus the operating modes are described in more detail in the following sections.

#### 3.2 ETHERNET FRAME FORMAT

#### 3.2.1 General

Information in an Ethernet network is transmitted and received in packets or frames. The basic function of the 8101 is to process Ethernet frames. An Ethernet frame is defined in IEEE 802.3 and consists of a preamble, start of frame delimiter (SFD), destination address (DA), source address (SA), length/type field (L/T), data, frame check sequence (FCS), and interpacket gap (IPG). The format for the Ethernet frame is shown in Figure 2.

An Ethernet frame is specified by IEEE 802.3 to have a minimum length of 64 bytes and a maximum length of 1518 bytes, exclusive of the preamble and SFD. Packets which are less than 64 bytes or greater than 1518 bytes are referred to as undersize and oversize packets, respectively.

# 3.2.2 Preamble & SFD

The preamble & SFD is a combined 64-bit field consisting of 62 alternating 1's and 0's followed by a 11 end of preamble indicator. The first 56-bits of 1's and 0's are considered to be the preamble, and the last 8-bits of 10101011 are considered to be the SFD (Start of Frame Delimiter).

#### 3.2.3 Destination Address

The destination address is a 48-bit field containing the address of the station(s) to which the frame is directed. The format of the address field is the same as defined in IEEE 802.3 and shown in Figure 2b. The destination address can be either a unicast address to a specific station, a multicast address to a group of stations, or a broadcast address to all stations. The first and second bits determine whether an address is unicast, multicast or

broadcast, and the remaining 46-bits are the actual address bits, as shown in Figure 2b.

# 3.2.4 Source Address

The source address is a 48-bit field containing the specific station address from which the frame originated. The format of the address field is the same as defined in IEEE 802.3 and shown in Figure 2b.

# 3.2.5 Length/Type Field

The 16-bit length/type field takes on the meaning of either packet length or packet type, depending on its numeric value, as described in Table 1.

Table 1. Length/Type Field Definition

| Length/Type<br>Field Value<br>(Decimal) | Length<br>or Type | Definition                                                  |

|-----------------------------------------|-------------------|-------------------------------------------------------------|

| 0-1500                                  | Length            | Total Number of Bytes<br>In Data Field minus<br>any padding |

| 1501-1517                               | Neither           | Undefined                                                   |

| ≥1518                                   | Туре              | Frame Type                                                  |

#### 3.2.6 Data

The data is a 46-1500 byte field containing the actual data to be transmitted between two stations. If the actual data is less than 46 bytes, extra 0's are added to increase the data field to the 46 byte minimum size. Adding these extra 0's is referred to as padding.

# 3.2.7 Frame Check Sequence

The frame check sequence (FCS), is a 32-bit cyclic redundancy check (CRC) value computed on the entire frame, exclusive of preamble & SFD. The FCS algorithm is defined in IEEE 802.3. The FCS is appended to the end of the frame and is used to determine frame validity.

# 3.2.8 Interpacket Gap

The interpacket gap (IPG) is the time interval between packets. The minimum IPG value is defined to be 96 bits, where 1 bit = 1nS for Gigabit Ethernet. There is no maximum IPG limit.

# 3.3 SYSTEM INTERFACE

#### 3.3.1 General

The System Interface is a 64-bit wide data interface consisting of separate 32-bit data bus for transmit and a separate 32-bit data bus for receive.

#### 3.3.2 Data Format and Bit Order

The format of the data word on TXD[31:0] and RXD[31:0] and its relationship to the MAC frame format and 10-Bit PHY Interface format is shown in Figure 3. Note that the device can be programmed to append an additional 32-bit status word to the end of the receive packet; refer to the Receive Status Word section for more details on this status word.

The byte ordering of the TXD and RXD data bits is programmable by setting the endian select bit in the Configuration 4 register. The byte order shown in Figure 3 is with little endian format mode (default). If the device is placed in big endian format, then the byte order shown in Figure 3 is reversed, i.e. DA[0:7] occurs on pins RXD[24:31], DA[24:31] occurs on pins RXD[0:7], etc. All bytes in the frame are affected by the endian select bit, including the receive status word if appended. The difference between little endian and big endian format is illustrated in Figure 4.

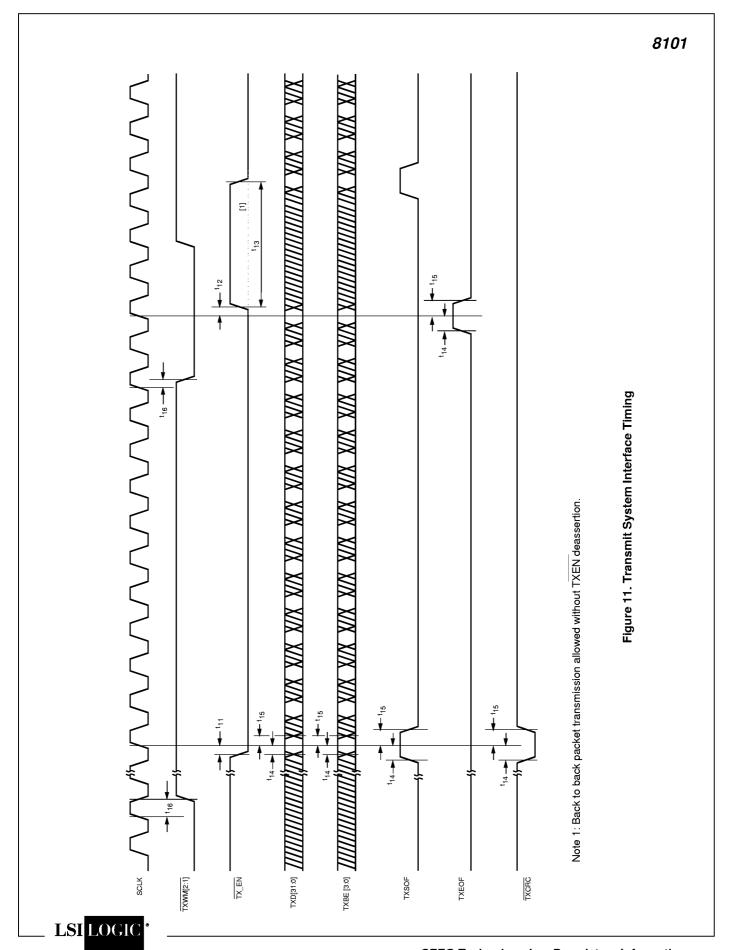

# 3.3.3 Transmit Timing

The transmit portion of the System Interface consists of 45 signals: 32 transmit data input bits (TXD[31:0]), one transmit enable (TXEN), four transmit byte enable inputs (TXBE[3:0]), two transmit start of frame and end of frame inputs (TXSOF and TXEOF), two transmit FIFO watermark outputs (TXWM1 and TXWM2), one transmit discard output (TXDC), one transmit discard clear input (CLR\_TXDC), one transmit CRC enable input (TXCRC), and one flow control enable input (FCNTRL). All receive and transmit data is clocked in/out on rising edges of the system clock, SCLK. SCLK must operate between 33-66 MHZ.

The SCLK input needs to be continuously input to the device at 33-66 MHz. When TXEN is deasserted, the transmit interface is not selected and subsequently, no input data is accepted by the device from the transmit System Interface inputs. When TXEN is asserted, a data word on the TXD[31:0] input is clocked into the transmit FIFO on each rising edge of the SCLK clock input. Multiple packets may be clocked in on one TXEN assertion. TXD[31:0] input data is 32-bit wide packet data whose format and relationship to the MAC packet and 10-Bit PHY data is described in Figure 3.

The transmit byte enable inputs, TXBE[3:0], determine which bytes of the 32-bit TXD[31:0] data word contain valid data. TXBE[3:0] are clocked in on rising edges of SCLK along with each TXD[31:0] data word. The correspondence between the byte enable inputs and the valid bytes of each data word on TXD[31:0] is defined in Table 2. Any logic combination of TXBE[3:0] inputs is allowed, with the

one exception that TXBE[3:0] must not be 0000 on the SCLK cycle when TXSOF or TXEOF is asserted.

Table 2. Byte Enable Pin vs. Valid Byte Position

| TXBE/RXBE Pins | Valid Bytes on<br>TXD/RXD Pins |

|----------------|--------------------------------|

| TXBE3/RXBE3    | TXD[31:24]/RXD[31:24]          |

| TXBE2/RXBE2    | TXD[23:16]/RXD[23:16]          |

| TXBE1/RXBE1    | TXD[15:8]/RXD[15:8]            |

| TXBE0/RXBE0    | TXD[7:0]/RXD[7:0]              |

The transmit start of frame and end of frame inputs, TXSOF and TXEOF, indicate to the device which data words start and end the Ethernet data packet, respectively. These signals are input on the same SCLK rising edge as the first and last word of the data packet.

The transmit watermark outputs, TXWM1 and TXWM2, indicate when the transmit FIFO has exceeded the programmable watermark thresholds. The watermarks will be asserted or deasserted by the device on rising edges of SCLK, depending on the fullness of the transmit FIFO. Refer to the transmit FIFO section for more details on these watermarks.

TXDC is a transmit packet discard output. TXDC is asserted every time the transmission of the packet being input on the System Interface was halted and packet discarded due to some error. This signal is latched active high and can be cleared by either asserting the clearing signal, CLR\_TXDC, or cleared automatically if the device is placed in the AutoClear mode. See the Packet Discard section for more details on discards and TXDC.

TXCRC is an input which can enable the internal generation and appending of the 4 byte CRC value onto the end of the data packet. TXCRC is sampled on rising edges of SCLK and has to be asserted at the beginning of the packet, coincident with TXSOF, to cause the removal or addition of the CRC to that packet. CRC generation can also be enabled by setting the transmit CRC enable bit in the Configuration 1 register. The interaction between the TXCRC pin and CRC enable bit is defined in Table 3.

FCNTRL is an input which will cause the automatic generation and transmission of a MAC Control Pause frame. FCNTRL is input on rising edges of SCLK. See the MAC Control Frame section for more details about this feature.

Figure 3. Frame Formats and Bit Ordering

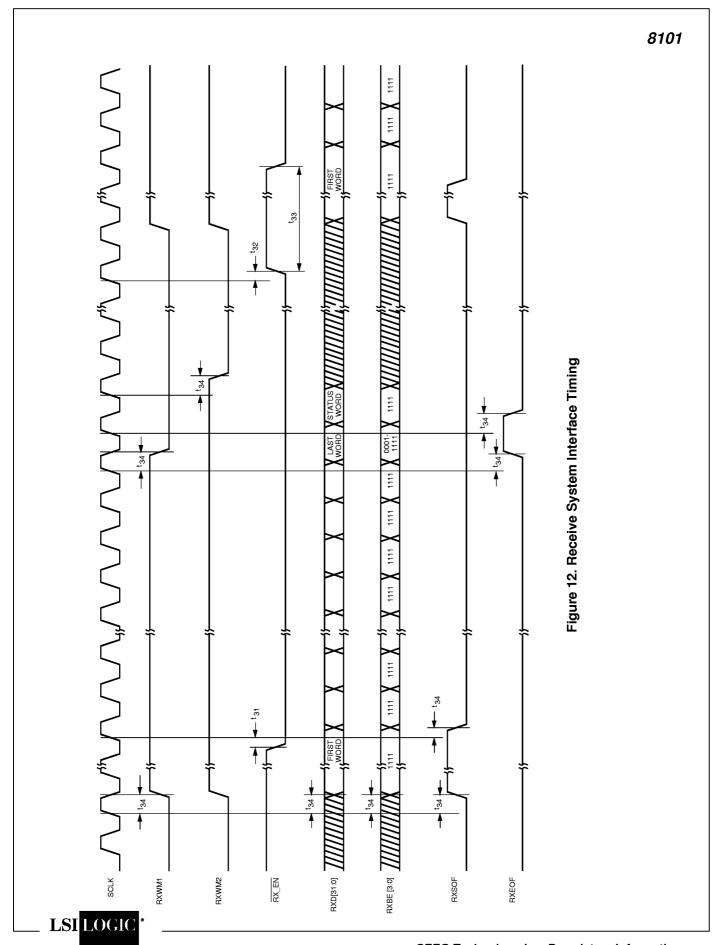

# 3.3.4 Receive Timing

The receive portion of the System Interface consists of 45 signals: 32 receive output\_data bits (RXD[31:0]), one receive enable input (RXEN), four receive byte enable outputs (RXBE[3:0]), two receive start of frame and end of frame outputs (RXSOF and RXEOF), two receive FIFO watermark outputs (RXWM1 and RXWM2), one receive discard output (RXDC), one receive discard clear input (CLR\_RXDC), one receive packet abort input (RXABORT), and one receive output enable (RXOE). All receive and transmit data is clocked in/out with the system clock, SCLK. SCLK must operate between 33-66 MHz.

The SCLK input needs to be continuously input at 33-66 Mhz. When RXEN is deasserted, the receive interface is not selected and subsequently, no data from the receive FIFO can be output over the System Interface. If the receive watermarks are asserted while RXEN is deasserted, the next data word from the receive FIFO appears on the RXD[31:0] outputs and stays there until RXEN is asserted. When RXEN is asserted, a data word from the receive FIFO is clocked out onto the RXD[31:0] outputs after each rising edge of the SCLK input. Once the entire packet has been clocked out, then no more data is clocked out on RXD[31:0] until RXEN is deasserted and reasserted, thus allowing extra dribble SCLK clock cycles to occur after the end of packet. RXD[31:0] output data is 32-bit wide packet data whose format and relationship to the MAC packet and 10-Bit PHY data is described in Figure

The receive byte enable outputs, RXBE[3:0], determine which bytes of the 32-bit RXD[31:0] data word contain valid data. RXBE[3:0] are clocked out on rising edges of SCLK along with each RXD[31:0] data word. Note that RXBE[3:0]=1111 for all words of the packet except the last word; the last word of the packet may end on any one of the four byte boundaries of the 32-bit data word. The correspondence between the byte enable inputs and the valid data bytes of each data word on RXD[31:0] is defined in Table 2.

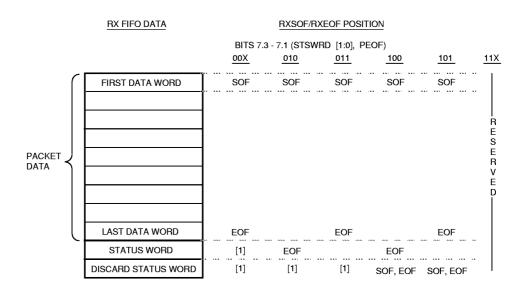

The receive start of frame and end of frame outputs, RXSOF and RXEOF, indicate which words start and end the Ethernet data packet, respectively. These signals are generally clocked out on the same SCLK rising edge as the first and last word of the data packet, respectively. However their exact position relative to the data packet is dependent on the programming of the EOF position bit and status word option bits in the Configuration 1 register. The exact RXSOF and RXEOF position for combinations of these two bits is depicted in Figure 5. More details about the definition of these bits can be found in the Configuration 1 Register Bit Definition, and more details about the status word can be found in the Receive Status Word section.

The receive watermarks, RXWM1 and RXWM2, indicate when the receive FIFO has exceeded the programmable watermark thresholds. The watermarks will be asserted or deasserted on rising edges of SCLK, depending on the fullness of the receive FIFO. Refer to Receive FIFO section for more details on these watermarks.

RXDC is a receive packet discard output. RXDC is asserted every time the reception of a packet being output over the System Interface was halted and the packet discarded due to some error. This signal is latched active high and can be cleared by either asserting the clearing signal, CLR\_RXDC, or cleared automatically if the device is placed in the AutoClear mode. See the Packet Discard section for more details on discards and RXDC.

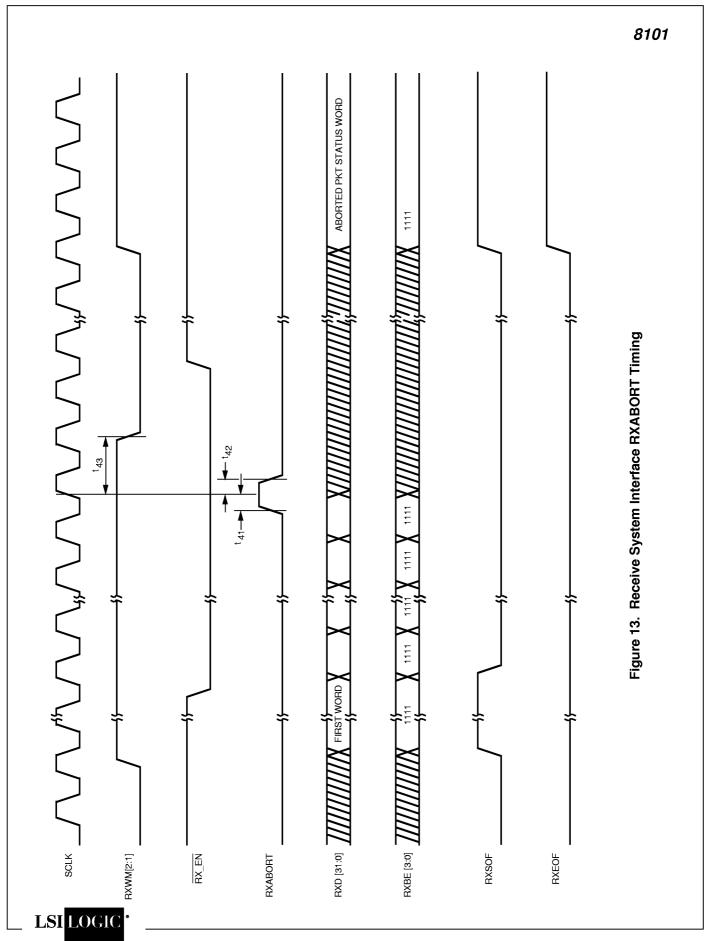

The RXABORT input, when asserted, will discard the current packet being output on the System Interface. When a packet is discarded by asserting RXABORT, the remaining contents of that packet in the receive FIFO are flushed. The process of flushing a receive packet from the receive FIFO with the RXABORT pin requires extra SCLK cycles equal to the (packet length in bytes)/8 + 6. Refer to

Figure 4. Little Endian vs. Big Endian Format

the Packet Discard section for more information about discarded packets. The device can be programmed to ignore the RXABORT pin by clearing the discard RXABORT enable bit in the Configuration 2 register. The device can also be programmed to discard either the data packet and its status word or just the data packet itself exclusive of its status word by setting the RXABORT definition bit in the Configuration 3 register.

RXOE is an output enable input which, when asserted, will place certain receive outputs in the high impedance state. The output pins affected by  $\overline{RXOE}$  are RXD[31:0], RXBE[3:0], RXSOF, and RXEOF.

# 3.3.5 Bus Width

The receive word width can be changed from 32-bits to 16-bits by appropriately setting the bus word width select bit in the Configuration 4 register. When the bus width is configured to 16-bits, the receive System Interface data outputs appear on RXD[15:0] and the data words are now 16-bits wide instead of 32-bits wide. Note that the transmit word width can be adjusted by appropriately setting the transmit byte enable inputs, TXBE[3:0], as described in Table 2.

#### 3.3.6 System Interface Disable

The system interface can be disabled by setting the system interface disable bit in the Configuration 3 register. When the System Interface is disabled, the device (1)

places all System Interface outputs in high impedance state (i.e. TXWM1/2, TXDC, RXD, RXBE, RXSOF, RXEOF, RXWM1/2, RXDC), (2) ignores all inputs (i.e. SCLK, TXEN, TXD, TXBE, TXSOF, TXEOF, CLR\_TXDC, FCNTRL, TXCRC, RXEN, RXOE, CLR\_RXDC, RXABORT), and (3) transmits /C/ ordered sets with the remote fault bits RF[1:0]=10 over the 10-Bit PHY Interface outputs.

#### 3.4 TRANSMIT MAC

#### 3.4.1 General

The transmit MAC (Media Access Control) section generates an Ethernet MAC frame from transmit FIFO data by (1) generating preamble & SFD, (2) padding undersize packet with 0's to meet minimum packet size requirements, (3) calculating and appending CRC value, and (4) maintaining a minimum interpacket gap between packets. Each of the above four operations can be individually disabled and altered, if desired. The transmit MAC then sends the fully formed Ethernet packet to the 8B10B PCS block for encoding. The transmit MAC section also generates MAC Control frames.

#### 3.4.2 Preamble & SFD Generation

The transmit MAC normally appends the preamble and SFD to the packet. The device can be programmed to **not** append the preamble & SFD to the transmit packet by clearing the transmit preamble enable bit in the Configuration 1 register.

NOTE 1: STATUS WORDS DO NOT EXIST WITH THIS BIT COMBINATION

Figure 5. RXSOF/RXEOF Position

#### 3.4.3 AutoPad

The transmit MAC normally AutoPad's packets. AutoPadding is the process of automatically adding enough zeroes on packets with data fields less than 46 bytes to make the data field exactly 46 bytes in length and meet the 46 byte minimum data field requirement of IEEE 802.3. The device can be programmed to **not** AutoPad by clearing the AutoPad bit in the Configuration 1 register.

# 3.4.4 CRC Generation

The transmit MAC normally appends the CRC value to the packet. The device can be programmed to **not** append the CRC value to the end of the packet from the transmit FIFO by asserting the TXCRC pin or by appropriately setting the transmit CRC enable bit in the Configuration 1 register, as described in Table 3.

Table 3. TXCRC Bit & TXCRC Pin Logic

| TXCRC Bit 7.5<br>1 = Append<br>0 = No Append | TXCRC Pin 1 = No Append 0 = Append | CRC<br>Appended to<br>End of Packet? |

|----------------------------------------------|------------------------------------|--------------------------------------|

| 1                                            | 1                                  | Yes                                  |

| 1                                            | 0                                  | Yes                                  |

| 0                                            | 1                                  | No                                   |

| 0                                            | 0                                  | Yes                                  |

# 3.4.5 Interpacket Gap

If packets from the transmit FIFO arrive at the transmit MAC sooner than the minimum interpacket gap time (referred to as IPG), the transmit MAC will add enough time between packets to equal the minimum IPG value. The default IPG time is set to 96 bits (1 bit=1ns), but the IPG can be programmed to other values by appropriately setting the transmit IPG select bits in the Configuration 1 register and also summarized in Table 4.

**Table 4. Transmit IPG Selection**

| IPG Select<br>Bits 7.[9:7] | IPG<br>(Bits) | Comments         |

|----------------------------|---------------|------------------|

| 111                        | 96            | IEEE Min Spec    |

| 110                        | 112           |                  |

| 101                        | 80            |                  |

| 100                        | 64            |                  |

| 011                        | 192           | 2x IEEE Min Spec |

| 010                        | 384           | 4x IEEE Min Spec |

| 001                        | 768           | 8x IEEE Min Spec |

| 000                        | 32            |                  |

#### 3.4.6 MAC Control Frame Generation

The transmit MAC can automatically generate and transmit MAC Control Pause frames. MAC Control Pause frames are used for flow control. This function is described in more detail in the MAC Control Frame section.

# 3.5 RECEIVE MAC

#### 3.5.1 General

The receive MAC (Media Access Control) section decomposes Ethernet packets received from the receive 8B10B PCS section by (1) stripping off the preamble & SFD, (2) stripping off the CRC, (3) checking the destination address against the address filters to determine packet validity, (4) checking frame validity against the discard conditions, and (5) checking the length/type field for MAC Control frames. Each of the above five operations can be individually disabled and altered, if desired. The receive MAC then sends valid packets to the receive FIFO for storage.

# 3.5.2 Preamble & SFD Stripping

The transmit MAC normally strips the preamble and SFD from the receive packet. The device can be programmed to **not** strip the preamble & SFD by setting the receive preamble enable bit in the Configuration 1 register. When this bit is set, the preamble & SFD are left on the receive packet and are stored in the receive FIFO as a part of the packet.

# 3.5.3 CRC Stripping

The receive MAC normally strips the FCS from the receive packet. The device can be programmed to **not** strip the FCS field by setting the receive CRC enable bit in the Configuration 1 register. When this bit is set, the last 4-bytes of the packet containing the CRC value are left on the receive packet and are stored in the receive FIFO as part of the packet.

# 3.5.4 Unicast Address Filter

Unicast packets are filtered by comparing the destination address of the receive packet against the 48-bit value stored in the three MAC Address 1-3 registers. When the destination address of a unicast packet matches the value stored in this register, the unicast packet is deemed valid and passed to the receive FIFO; otherwise, the packet is rejected. The correspondence between the bits in the MAC Address register and the incoming bits in the destination address of the receive packet is defined in the MAC Address register definition table.

The device can be programmed to always reject unicast packets by setting the reject unicast packet bit in the Configuration 2 register. When this bit is set, all unicast packets are rejected regardless of their address.

The reception of MAC Control frames is unaffected by any of the unicast packet address filtering functions and is controlled by other bits described in the MAC Control Frame section.

#### 3.5.5 Multicast Address Filter

Multicast packets can be filtered by processing the destination address with the multicast address filter function. The multicast address filter function computes the CRC on the incoming DA and produces a 6-bit number that is compared against the 64 values stored in the MAC Address Filter 1-4 registers. When the multicast packet destination address passes the address filter, the packet is deemed valid and passed to the receive FIFO; otherwise, the packet is rejected.

The multicast address filter requires 64 address filter bits to be written into the Address Filter 1-4 registers. The multicast address filtering algorithm is as follows:

- (1) Compute a separate 32-bit CRC on the destina tion address field using the same IEEE 802.3 defined method that computes the transmit CRC.

- (2) Use bits 0-3 of the destination address FCS to select one of the bytes in the 64-bit address filter, as shown in Table 5.

- (3) Use bits 4-6 of the destination address FCS to select one of the bits within the byte selected in (2) as shown in Table 5.

- (4) If the bit selected in (3) is a "1", the destination address passes the filter; otherwise, the address fails the filter and the packet is rejected and discarded.

Note that if all 64-bits of the address filter are programmed to all 1's, then the address filter passes all multicast addresses.

The device can be programmed to reject multicast packets by setting the reject multicast packet bit in the Configuration 2 register. When this bit is set, all multicast packets are rejected regardless of their address.

The reception of MAC Control frames is unaffected by any of the multicast packet address filtering functions and is controlled by other bits described in the MAC Control Frame section

Table 5. Multicast Address Filter Map

| FCS Bits<br>[0:2] | Address<br>Filter Byte | FCS Bits<br>[3:5] | Address<br>Filter Bit |

|-------------------|------------------------|-------------------|-----------------------|

| 000               | F0[7:0]                | 000               | Fx[0]                 |

| 001               | F1[7:0]                | 001               | Fx[1]                 |

| 010               | F2[7:0]                | 010               | Fx[2]                 |

| 011               | F3[7:0]                | 011               | Fx[3]                 |

| 100               | F4[7:0]                | 100               | Fx[4]                 |

| 101               | F5[7:0]                | 101               | Fx[5]                 |

| 110               | F6[7:0]                | 110               | Fx[6]                 |

| 111               | F7[7:0]                | 111               | Fx[7]                 |

F[7:0] are bytes in Address Filter 1-4 Registers. Fx[7:0] are bits within each byte in Address Filter 1-4 Registers. Bits 0-5 are the six least significant bits of the CRC.

# 3.5.6 Broadcast Address Filter

The device does not do any filtering on broadcast packets. However, the device can be programmed to reject broadcast packets by setting the reject broadcast packet bit in the Configuration 2 register. When this bit is set, all broadcast packets are rejected regardless of their address

The reception of MAC Control frames is unaffected by any of the broadcast packet address filtering functions and is controlled by other bits described in the MAC Control Frame section

# 3.5.7 Reject Or Accept All Packets

The device can be programmed to accept or reject all packets regardless of type or whether the packet passes the address filter by setting the accept all packet or reject all packet bits, respectively, in the Configuration 2 register.

The reception of MAC Control frames is unaffected by these bits and is controlled by other bits described in the MAC Control Frame section.

# 3.5.8 Frame Validity Checks

The receive MAC determines the validity of each receive packet by checking for (1) valid FCS, (2) oversize packet, and (3) undersize packet.

Valid FCS is determined by computing the CRC value on the incoming receive packet per IEEE 802.3 specifications and comparing it against the actual CRC value in the FCS field of the received packet. If the values are not the same, the frame is determined to be invalid and the packet is discarded. Refer to the Packet Discard section for more information about discards. The device can be programmed to **not** discard a packet with bad FCS by clearing the discard CRC error bit in the Configuration 2 register.

Oversize packets are packets whose length is greater than the maximum packet size. If a received packet is an oversize packet, then the packet is determined to be invalid and it is discarded. Refer to the Packet Discard section for more information about discards. The maximum packet size can be programmed to be either 1518 bytes, 1522 bytes, or 1535 bytes, exclusive of preamble & SFD, by appropriately setting the maximum packet size bit in the Configuration 3 register. The device can be programmed to **not** discard an oversize packet and thus allow packets of unlimited length by clearing the discard oversize packet bit in the Configuration 2 register.

Undersize packets are packets whose length is less than the minimum packet size. Minimum packet size is defined to be 64 bytes, exclusive of preamble & SFD. If a received packet is an undersize packet, then the frame is determined to be invalid and it is discarded. Refer to the Packet Discard section for more information about discards. The device can be programmed to **not** discard an undersize packet by clearing the discard oversize packet bit in the Configuration 2 register.

# 3.5.9 Maximum Packet Size

The maximum packet size used for receive MAC frame validity checking can be programmed to be one of four values by appropriately setting the receive MAC maximum packet size select bits in the Configuration 3 register and the discard oversize packet enable bit in the Configuration 2 register as shown in Table 6. This selection is also described in the register descriptions for those registers.

The bits shown in Table 6 affect the receive MAC section only; the maximum packet size for the management counters is determined by other bits as described in the Counters section.

Table 6. Receive Maximum Packet Size Selection

| 11000110 1110                                                                | x Packet Size<br>ct Bits |                            |  |

|------------------------------------------------------------------------------|--------------------------|----------------------------|--|

| Discard RX MAC Oversize Max Packet Packet, Size Select, Bit 8.7 Bits 9.[5:4] |                          | Max Packet Size<br>(bytes) |  |

| 0                                                                            | xx                       | unlimited                  |  |

| 1                                                                            | 10                       | 1535                       |  |

| 1                                                                            | 01                       | 1522                       |  |

| 1                                                                            | 00                       | 1518                       |  |

#### 3.5.10 MAC Control Frame Check

The length/type field is checked to detect whether the packet is a valid MAC Control frame. Refer to the MAC Control Frame section for more details on MAC Control frames.

#### 3.6 TRANSMIT FIFO

# 3.6.1 General

The transmit FIFO acts as a temporary buffer between the System Interface and transmit MAC section. The transmit FIFO size is 4K bytes. Data is clocked into the transmit FIFO with the 33-66 MHZ System Interface clock, SCLK. Data is automatically clocked out of the transmit FIFO with the 125 MHZ 8B10B PCS clock whenever (1) a full packet has been loaded into the FIFO (evidenced by an EOF being written into the FIFO on the System Interface), or (2) the FIFO data exceeds the transmit FIFO AutoSend threshold. There are two programmable watermark outputs, TXWM1 and TXWM2, which aid in managing the data flow into the transmit FIFO.

# 3.6.2 AutoSend

The AutoSend feature causes a packet in the transmit FIFO to be automatically transmitted once transmit FIFO data exceeds a certain threshold.

The transmit AutoSend threshold is programmable over the lower 2K byte of the transmit FIFO. The AutoSend threshold can be programmed with the six transmit

AutoSend threshold bits that reside in the Transmit FIFO Threshold register. Once the data in the FIFO exceeds this threshold, then the packet is automatically transmitted to the 8B10B PCS section and out the 10-Bit PHY Interface. A packet will also be automatically transmitted if an EOF is written into the transmit FIFO for that packet, regardless of the autosend threshold setting.

All of the bit settings for the transmit autosend threshold are evenly distributed over the lower 1/2 of the transmit FIFO range, except for the 000000 setting. The 000000 setting automatically starts transmission when the transmit FIFO is full, thus facilitating the transmission of oversize packets. Refer to the Transmit FIFO Threshold Register description for more details on the autosend bit settings.

# 3.6.3 Watermarks

There are two transmit watermarks for the transmit FIFO. These two watermarks are output on the TXWM1 and TXWM2 pins. These watermarks are asserted when the transmit FIFO data exceeds the thresholds associated with the watermarks.

The transmit watermark thresholds for TXWM1 and TXWM2 can be programmed over the entire 4K FIFO range. Each of the watermark thresholds are independently programmed with five bits that reside in the Transmit FIFO Threshold register. Once the data in the FIFO exceeds the threshold of either watermark, then the respective watermark pin on either TXWM1 or TXWM2 is asserted active low. The watermarks stay asserted until the data in the FIFO goes below the respective thresholds.

# 3.6.4 TX Underflow

The transmit FIFO underflow condition occurs when the TX FIFO is empty but the MAC still is requesting data to complete the transmission of a packet. If the transmit FIFO underflows, then (1) packet transmission to the 8B10B PCS is halted, (2) a /V/code is appended to the end of the partially transmitted packet, and (3) any new data for the partially transmitted packet is discarded. Refer to the Packet Discard section for more information about discards.

# 3.6.5 TX Overflow