# Omme siston.

#### Features

- Single chip 1/4" video image sensor

- Progressive scan

- Built-in analog-to-digital (A/D) 8-bit pixel resolution

- Programmable features

- Frame rate of 50 ~ 0.5 frames per second (fps)

- Exposure setting: 1 frame ~ 1/100 frame

- Image size: 4.2 mm x 3.2 mm

- AGC (auto gain control): 0 ~ 18 dB

- Gamma correction: 0.45/1.0

- Pixel elements 384 x 288

- Pixel dimension of 11 um x 11 um

- External frame sync capability

- Signal-to-noise (S/N) ratio > 42 dB

- Minimum illumination of 0.5 lux at f1.4 at 50 fps

- Single 5-volt supply operation for analog and 5/3.3 volts for digital

- Power consumption

- Active: less than 100 mW at 50 fps

- Standby: less than 100 μA

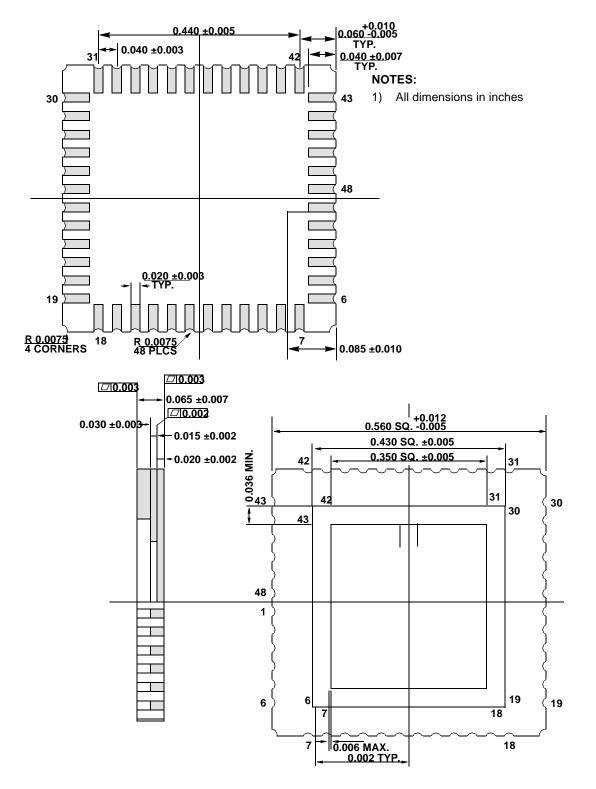

- 48-pin package

#### Overview

The OV5017 is a black and white digital camera chip that uses OmniVision's CMOS image core technology. Combining the CMOS sensor technology and an easy to use digital interface, the OV5017 offers a low cost solution for high-quality video image applications.

The digital video port supplies a continuous bytewide image data. On-chip programmable features include variable frame rate, exposure setting, and image size. All the camera features are register based, accessing the video data and configuring the chip is as easy as read/write of a static memory.

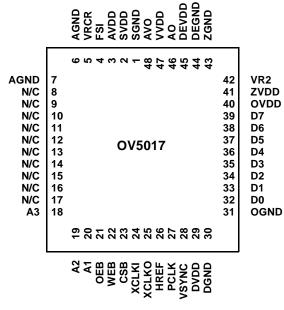

#### **OV5017 PIN ASSIGNMENTS**

OmniVision Technologies, Inc. reserves the right to make changes without further notice to any product herein to improve reliability, function, or design. OmniVision Technologies, Inc. does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. No part of this publication may be copied or reproduced, in any form without the prior written consent of OmniVision Technologies, Inc.

The Image Core is a complete analog video camera with 384 x 288 pixel size, which can run at full video speed. The analog video signal complies with CCIR standards. At 50 fps, it may be too fast for many applications; therefore, the frame rate or pixel rate can be programmed to match the external system requirements. The on-chip 8-bit A/D can convert the video signal at 50 fps, and the conversion is synchronized with the actual pixel rate.

The OV5017 also outputs standard timing reference signals such as VSYNC, HREF, PCLK. Databus is shared by negating OEB.

The exposure control can be set to auto or manual operation. Automatic exposure computation is based on full size image array and an exposure range over 100X. The AGC operation is tied to AEC in auto operation. Therefore, use automatic exposure control when selecting full image size. Manual exposure control allows individually adjusting exposure and gain based on actual application. Therefore, use manual exposure time if the window is smaller than full size or if the target object is brighter or darker than the average background.

The frame rate divider can achieve various frame rates on the fly without changing the input clock frequency.

Single frame operation provides one frame data transfer by controlling the assertion of HREF for one complete frame period. Setting FCTL(7) signals the control to assert the HREF in the next frame. Clearing this bit before the new frame cancels the assertion of HREF.

| Pin #             | Class | Pin Name | Description                                                                                                                                                                                                                                             |  |

|-------------------|-------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1                 | Bias  | SGND     | Sensor ground. Connect to supply common.                                                                                                                                                                                                                |  |

| 2                 | Bias  | SVDD     | Sensor power (+5V) connection.                                                                                                                                                                                                                          |  |

| 3                 | Bias  | AVDD     | Analog power (+5V) connection.                                                                                                                                                                                                                          |  |

| 4                 | I-0   | FSI      | External frame sync input. A rising edge on FSI sets the chip vertical sync timin<br>For proper operation, the frequency of FSI must be half of the programmed frar<br>rate. Internally pulled down with a 100k resistor. Leave open or ground if unuse |  |

| 5                 | Bias  | VrCR     | Internal reference voltage. Requires a 0.1uF external capacitor to AGND.                                                                                                                                                                                |  |

| 6                 | Bias  | AGND     | Analog ground. Connect to supply common.                                                                                                                                                                                                                |  |

| 7                 | Bias  | AGND     | Analog ground. Connect to supply common.                                                                                                                                                                                                                |  |

| 8-17              | FT    | N/C      | Factory test. Leave open.                                                                                                                                                                                                                               |  |

| 18, 19,<br>20, 46 | I     | A3-A0    | Address inputs for internal the registers. Requires CSB = 0 to access the registers.                                                                                                                                                                    |  |

| 21                | I     | OEB      | Output enable for the eight bit data bus. OEB = 0 enables the data bus drivers.<br>OEB = 1 puts the data bus in tristate.                                                                                                                               |  |

#### **Table 1. Pin Descriptions**

| Pin #  | Class | Pin Name        | Description                                                                                                                                                                                                                                                                                                      |

|--------|-------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22     | 1     | WEB             | Write enable input for the internal registers. When the chip is selected (CSB = 0), external data is latched into the registers with the rising edge of WEB.                                                                                                                                                     |

| 23     | 1     | CSB             | Chip select for the device. $CSB = 0$ selects the device.                                                                                                                                                                                                                                                        |

| 24, 25 | OD    | XCLKI,<br>XCLKO | Crystal oscillator in/out pins. Nominal clock frequency is 14.31MHz for CCIR 50 Hz timing. The maximum pixel rate is limited to one half of the clock frequency. To connect an external clock to XCLKI, leave XCLKO open.                                                                                        |

| 26     | OD    | HREF            | Horizontal timing reference output. Asserted high during every valid line for the duration of the valid window width. The window sizing function affects the number of valid lines in a frame as well as the number of valid pixels in a line. HREF and status(1), are identical valid pixel timing information. |

| 27     | OD    | PCLK            | Pixel clock output. Defaulted to be a continuous clock. Can be programmed via the internal register to be on during the valid pixel window only. Video data at output bus (D0-D7) is updated with the rising edge of PCLK and is guaranteed to be valid at the falling edge of PCLK.                             |

| 28     | OD    | VSYNC           | Vertical timing reference output. It is high once per frame for the duration of the vertical sync period. VSYNC and status (2) are identical vertical sync timing information.                                                                                                                                   |

| 29     | Bias  | DVDD            | Digital power (+5V) connection.                                                                                                                                                                                                                                                                                  |

| 30     | Bias  | DGND            | Digital ground. Connect to supply common                                                                                                                                                                                                                                                                         |

| 31     | Bias  | OGND            | Digital output ground. Connect to supply common                                                                                                                                                                                                                                                                  |

| 32-39  | OD    | D0-D7           | Bi-directional data bus for video output data and internal register read/write operations.                                                                                                                                                                                                                       |

| 40     | Bias  | OVDD            | Digital output power (+5V/+3.3V) connection.                                                                                                                                                                                                                                                                     |

| 41     | Bias  | ZVDD            | Analog power (+5V) connection.                                                                                                                                                                                                                                                                                   |

| 42     | Bias  | VR2             | Internal reference voltage. Requires a 0.1uF external capacitor to AGND.                                                                                                                                                                                                                                         |

| 43     | Bias  | ZGND            | Analog ground. Connect to supply common.                                                                                                                                                                                                                                                                         |

| 44     | Bias  | DEGND           | Decoder ground. Connect to supply common.                                                                                                                                                                                                                                                                        |

| 45     | Bias  | DEVDD           | Decoder power (+5V) connection.                                                                                                                                                                                                                                                                                  |

| 47     | Bias  | VVDD            | Video output power (+5V) connection.                                                                                                                                                                                                                                                                             |

| 48     | Q     | AVO             | Composite video output. It is capable of driving 150 $\Omega$ load, Vp-p is 2.0 V.                                                                                                                                                                                                                               |

# Table 1. Pin Descriptions (Continued)

#### Pin Type and Default Level:

I: digital input, floating, I-1: digital input, with 100k pull up, I-0: digital input, with 100k pull down, OD: digital CMOS level output, OA: analog CMOS, level output, XI/XO: xtal IO, K: analog input, Q:  $75\Omega$  output, FT: factory test, Bias: power supply bias

# 1. Video Data Bus

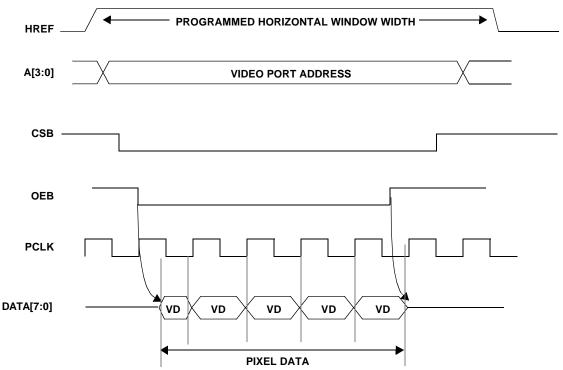

Figure 1. Video Data Timing Showing Continuous Pixel Reading

The eight bit video data from the A/D converter is synchronous to PCLK. The lowest level is 'h00' and the highest is 'hff', no reserved code for blanking or sync.

PCLK is the pixel clock that is either continuously on or present only during valid pixel window. If the continuous clock is used, HREF is often used to qualify the pixel data. HREF is asserted during the programmed horizontal and vertical window region. Video data is updated at the rising edge of PCLK and can be latched at the falling edge of PCLK.

As shown in Figure 1, reading of the video data is not different from reading other on-chip registers, it requires the assertion of OEB and CSB and the correct address. To maintain uninterrupted video data stream, OV5017 video data will be updated at each pixel clock as long as the OEB, CSB, and correct address are asserted as shown in Figure 1.

Since the video data is continuous during the active window, to prevent new data overruns the previous one, the host has to make sure at least one video data is read in every pixel clock period. The status register bit RDY and OV allows host to perform polling and error detection.

## 1.1 Register Control

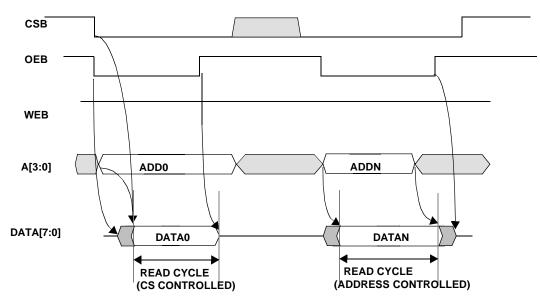

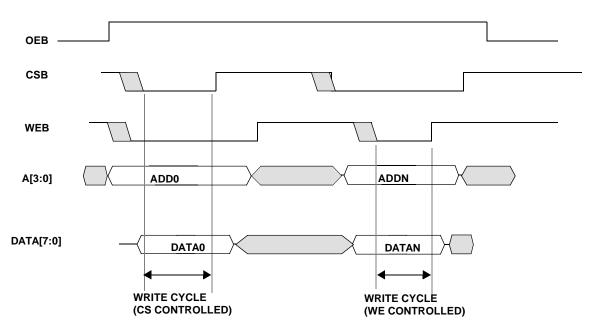

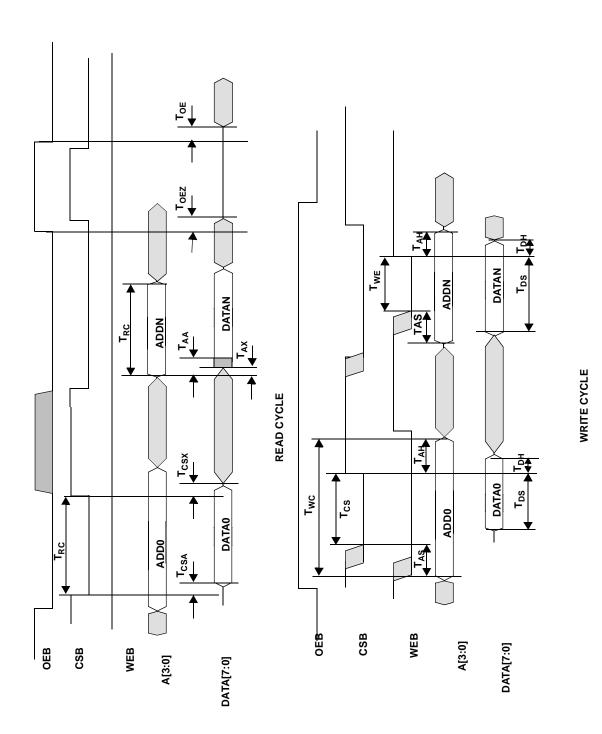

The register read/write is the same as normal memory access, using pins DATA[7:0], A[3:0], WEB, OEB, and CSB. As shown in Figure 2 and Figure 3, the read cycle can be chip select controlled or address controlled. The write cycle also can be chip select controlled or write enable controlled. The memory cycle is fully asynchronous to the frame or pixel timing. Write cycle affects only the registers which are writable, it does not affect read only registers such as video port status register. Since writing to certain

registers affects the basic camera operation, care must be taken when write occurs during the middle of active window. These effects are described in the individual register section. As a guide line, registers affects the frame rate, exposure time, window size, are better updated during the vertical sync

Figure 2. Register Access Showing a Single Byte Read

Figure 3. Register Access Showing Single Byte Write

# 2. Registers

#### Table 2. Register Sets

| A[3:0] | Register<br>Name | R/W | Bit Name                                           | Function                                    | Default<br>Value |

|--------|------------------|-----|----------------------------------------------------|---------------------------------------------|------------------|

| 10xx   | VPORT            | R   | VD[7:0]                                            | Video data                                  | XXXXXXXX         |

| 0000   | STATUS           | R   | TO2,TO1, , ,OV,<br>VSYNC, HREF, RDY                | Status register                             | 00xxxxxx         |

| 0001   | FCTL             | W   | SFR, FSET, , ,<br>SKIP, FBLC, STOP,<br>SRST        | Single frame flow control<br>system control | 00xx0000         |

| 0010   | EXCTL            | R/W | AUTO, EX[6:0]                                      | Auto or manual exposure<br>value            | 11111111         |

| 0011   | GCTL             | R/W | GN[2:0]                                            | Gain value                                  | xxxxx000         |

| 0100   | FRCTL            | R/W | FDIV[5:0]                                          | Frame rate divider                          | xx000000         |

| 0101   | MCTL             | R/W | GAMMA, MIR, DN,<br>BKL, FZEX, PCKS,<br>PCKI, BPSHP | Miscellaneous controls                      | 0000000          |

| 0110   | HWCTL            | R/W | HWS[3:0], HWE[3:0]                                 | Window control                              | 00000000         |

| 0111   | VWCTL            | R/W | VWS[3:0], VWE[3:0]                                 | Window control                              | 00000000         |

| 1110   | TST              | W   | TST[7:0]                                           | Reserved for test xxxxxxx                   |                  |

| 1111   | TOPT             | W   | TOPT[7:0]                                          | Reserved for test xxxxx                     |                  |

Note: Unimplemented bits in all the R/W registers return "0" in the read cycle, no effect in the write cycle.

# 2.1 Detailed Register Descriptions

The following table describes the function of each bit within a register:

#### Table 3. Bit descriptions

| Register<br>Name | Bit name | Range   | Function                                                                                                                                                                                       |

|------------------|----------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VPORT            | VD       | VD[7:0] | This register selects the video data port. The video data is not latched<br>in this VPORT, as long as VPORT remains selected. The video data<br>is updated as new pixel signals are converted. |

| STATUS           | TO2      | STA7    | Reserved bit.                                                                                                                                                                                  |

| Table 3. Bit descriptions | (Continued) |

|---------------------------|-------------|

|---------------------------|-------------|

| Register<br>Name | Bit name | Range   | Function                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | TO1      | STA6    | Reserved bit.                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                  | OV       | STA3    | Pixel data overrun flag. It is set each time pixel data is updated if STA0 has been set already. Reading of this register clears the bit.                                                                                                                                                                                                                                                                                      |

|                  | VSYNC    | STA2    | This bit duplicates the signal at pin VSYNC.                                                                                                                                                                                                                                                                                                                                                                                   |

|                  | HREF     | STA1    | This bit duplicates the signal at pin HREF.                                                                                                                                                                                                                                                                                                                                                                                    |

|                  | RDY      | STA0    | This bit is set each time pixel data is updated, and is cleared by read-<br>ing the VPORT register. This bit will not be set if the VPORT register<br>is being read while pixel data is updating.                                                                                                                                                                                                                              |

| FCTL             | FSET     | FCTL[7] | Set to initiate single frame transfer. This bit works only if FCTL[6] is<br>also set. If this bit is set in the middle of a frame, HREF will not be<br>asserted until the next new frame. This bit is cleared automatically at<br>the end of the new frame so that it can be set again.                                                                                                                                        |

|                  | SFR      | FCTL[6] | Set to enable single frame operation mode. Since the video data is a continuous non-stop byte stream, the validity of the data is qualified only by assertion of HREF. In a continuous frame operation, HREF is asserted in every frame. In a single frame operation, HREF is asserted only for the first frame immediately after setting the FCTL[7]. The actual duration of HREF assertion is programmed by the window size. |

|                  | SKIP     | FCTL[3] | Makes VSYNC and HREF to skip every other frame. This function does not alter the pixel rate; it simply blocks their assertion in every other frame.                                                                                                                                                                                                                                                                            |

|                  | FBLC     | FCTL[2] | Chooses how frequent the black level calibration is performed inter-<br>nally. It is set once every frame and cleared once every line. Line BLC<br>can set the BLC within a fraction of a frame time. This is useful to<br>speed up BLC process after power up or activation after standby<br>mode. However, frame BLC provides better image stability.                                                                        |

|                  | STOP     | FCTL[1] | Set to stop chip clock and enter low power standby mode. This func-<br>tion does not alter register content. The chip is put in default state and<br>all image data is lost. Setting this bit does not prevent further register<br>access. Upon clearing this bit, it generally takes about two frames for<br>the chip to become stable.                                                                                       |

|                  | SRST     | FCTL[0] | Software reset enable. Setting this bit resets all the on-chip registers<br>and puts the chip in default state. Upon clearing this bit, it generally<br>takes about two frames for the chip to become stable.                                                                                                                                                                                                                  |

## Table 3. Bit descriptions (Continued)

| Register<br>Name | Bit name | Range      | Function                                                                                                                                                                                                                                                                                                                                                         |  |  |

|------------------|----------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| EXCTL            | AUTO     | EXCTL[7]   | Enables auto exposure. To select auto exposure mode, set this bit. To select manual exposure mode, clear this bit.                                                                                                                                                                                                                                               |  |  |

|                  | EX       | EXCTL[6:0] | Sets the exposure time, where 7fh is the 1/50s, and 00h is the 1/<br>(50*128*2)s. This register is used in manual exposure mode only.<br>After updates are made to this register, it takes two frames for the<br>chip to become stable.                                                                                                                          |  |  |

| GCTL             | GN       | GCTL[2:0]  | Selects the post amplifier gain, where 111 is the 18dB gain and 000 is<br>the 0dB in a linear relationship. This register is used in manual expo-<br>sure mode only. After updates are made to this register, it takes two<br>frames for the chip to become stable.                                                                                              |  |  |

| FRCTL            | FDIV     | FRCTL[5:0] | Divides the frame rate by 1 to 64 in steps of 1 by using this formula:<br>Frame Rate = $F_0 / (FDIV+1)$<br>Pixel Rate = $f_{osc} / [(FDIV +1)^*2]$<br>where $f_{osc}$ is the main clock frequency of XCLKi<br>$F_0 = f_{osc} / (458^*625); F_0=50 @ 14.318Mhz$<br>After updates are made to this register, it takes two frames for the<br>chip to become stable. |  |  |

| MCTL             | GAMA     | MCTL[7]    | Set this bit to select gamma = 0.45, and clear this bit for gamma = 1.                                                                                                                                                                                                                                                                                           |  |  |

|                  | MIR      | MCTL[6]    | Set this bit to select mirror image.                                                                                                                                                                                                                                                                                                                             |  |  |

|                  | NSR      | MCTL[5]    | Set this bit to turn on indoor mode, and clear for outdoor mode.                                                                                                                                                                                                                                                                                                 |  |  |

|                  | BKL      | MCTL[4]    | Set this bit to turn on backlight compensation.                                                                                                                                                                                                                                                                                                                  |  |  |

|                  | FZEX     | MCTL[3]    | Set this bit to freeze the exposure setting. This works in auto expo-<br>sure mode; it has no effect in manual exposure mode.                                                                                                                                                                                                                                    |  |  |

|                  | PCKS     | MCTL[2]    | Clear this bit to output continuous pixel clock to PCLK; set to output pixel clock only during the valid pixel window                                                                                                                                                                                                                                            |  |  |

|                  | PCKI     | MCTL[1]    | Set this bit to inverse the polarity of PCLK.                                                                                                                                                                                                                                                                                                                    |  |  |

|                  | BPSHP    | MCTL[0]    | Set this bit to disable sharpness function.                                                                                                                                                                                                                                                                                                                      |  |  |

|                  | HWS      | HWCTL[7:4] | Selects the start of the horizontal window.                                                                                                                                                                                                                                                                                                                      |  |  |

| VWCTL            | HWE      | HWCTL[3:0] | Selects the end of the horizontal window.                                                                                                                                                                                                                                                                                                                        |  |  |

|                  | VWS      | VWCTL[7:4] | Selects the start of the vertical window.                                                                                                                                                                                                                                                                                                                        |  |  |

|                  | VWE      | VWCTL[3:0] | Selects the end of the vertical window.                                                                                                                                                                                                                                                                                                                          |  |  |

# Table 3. Bit descriptions (Continued)

| Register<br>Name                                                                                                                                                                                                                                                                                                       | Bit name                                                                                                                                                                                                                         | Range                                                                                                                                                                                           | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| The array is divide<br>shown in Figure 1.<br>The method for se<br>window region is the<br>eight-bit register. Elocation. Bit [3:0] se<br>example, to select<br>region, use HWCT<br>This window select<br>assertion time of H<br>pixel rate or the dat<br>equal to or less that<br>size is from start lot<br>most edge. | 1. each block is<br>lecting vertical a<br>he same. Each d<br>Bit [7:4] selects th<br>elects the end blut<br>the shaded area<br>TL=4cH,VWCTL=<br>tion feature char<br>IREF and does r<br>at rate. If the en<br>an the start locat | H24xV18 pixels.<br>nd horizontal<br>lirection uses an<br>ne start block<br>ock location. For<br>a as the active<br>=44H.<br>nges only the<br>not change the<br>d location is<br>ion, the window | HREF<br>HWS HWE<br>HWS HWE<br>HWS<br>HWE<br>HWS<br>HWE<br>HWS<br>HWE<br>HWS<br>HWE<br>HWS<br>HWE<br>HWS<br>HWE<br>HWS<br>HWE<br>HWS<br>HWE<br>HWS<br>HWE<br>HWS<br>HWE<br>HWS<br>HWE<br>HWS<br>HWE<br>HWS<br>HWE<br>HWS<br>HWE<br>HWS<br>HWE<br>HWS<br>HWE<br>HWS<br>HWE<br>HWS<br>HWE<br>HWS<br>HWE<br>HWS<br>HWE<br>HWS<br>HWE<br>HWS<br>HWE<br>HWS<br>HWE<br>HWS<br>HWE<br>HWS<br>HWE<br>HWS<br>HWE<br>HWS<br>HWE<br>HWS<br>HWE<br>HWS<br>HWE<br>HWS<br>HWE<br>HWS<br>HWE<br>HWS<br>HWE<br>HWS<br>HWE<br>HWS<br>HWE<br>HWS<br>HWE<br>HWS<br>HWE<br>HWS<br>HWE<br>HWS<br>HWE<br>HWS<br>HWE<br>HWS<br>HWE<br>HWS<br>HWE<br>HWS<br>HWS<br>HWS<br>HWS<br>HWS<br>HWS<br>HWS<br>HWS<br>HWS<br>HWS |

# 3. Electrical Specifications

This section provides the electrical parameters descriptions and timing diagrams.

# **3.1 Electrical Parameters**

| Table 4. | Electrical | parameters | $(0^{\circ}C \le TA \le 8)$ | 85 <sup>o</sup> C, voltages i | eferenced to GND) |

|----------|------------|------------|-----------------------------|-------------------------------|-------------------|

|----------|------------|------------|-----------------------------|-------------------------------|-------------------|

| Symbol                          | Descriptions                                                            | Мах        | Туре       | Min        | Units  |

|---------------------------------|-------------------------------------------------------------------------|------------|------------|------------|--------|

| Supply                          |                                                                         |            |            |            | •      |

| V <sub>DD1</sub>                | Supply voltage (digital/analog: DEVDD,<br>ZVDD, AVDD, SVDD, VVDD, DVDD) | 5.25       | 5.0        | 4.75       | V      |

| V <sub>DD2</sub>                | Supply voltage (OVDD)                                                   | 5.5<br>3.6 | 5.0<br>3.3 | 4.5<br>3.0 | V<br>V |

| I <sub>DD1</sub>                | Supply Current (@ 50fps, 50pf CMOS load on data bus)                    | 40         | -          | -          | mA     |

| I <sub>DD2</sub>                | Standby supply current                                                  | 100        | -          | -          | uA     |

| Inputs                          | 1                                                                       |            | 1          |            |        |

| V <sub>IL</sub>                 | Input voltage LOW                                                       | 0.8        | -          | -          | V      |

| V <sub>IH</sub>                 | Input voltage HIGH                                                      | -          | -          | 2.0        | V      |

| Cin                             | Input capacitor                                                         | 10         | -          | -          | pF     |

| t <sub>r</sub> , t <sub>r</sub> | Digital input rise/fall time                                            | 25         | -          | -          | ns     |

| Outputs - star                  | ndard load 25pf, 1.2k $\Omega$ to 3.0volts                              |            | 1          |            |        |

| V <sub>OH</sub>                 | Output voltage HIGH                                                     | -          | -          | 2.4        | V      |

| V <sub>OL</sub>                 | Output voltage LOW                                                      | 0.6        | -          | -          | V      |

| Clock input / 0                 | Crystal Oscillator                                                      |            | 1          |            |        |

| f <sub>osc</sub>                | Resonator frequency                                                     | -          | 14.31818   | -          | MHz    |

|                                 | Load capacitor                                                          | -          | 10         | -          | pF     |

|                                 | Parallel resistance                                                     |            | 1M         |            | W      |

|                                 | Clock input rise/fall time                                              | 5          | -          | 25         | ns     |

|                                 | Duty cycle if external clock input                                      | 60         |            | 40         | %      |

| Video timing                    |                                                                         |            | · · · ·    |            |        |

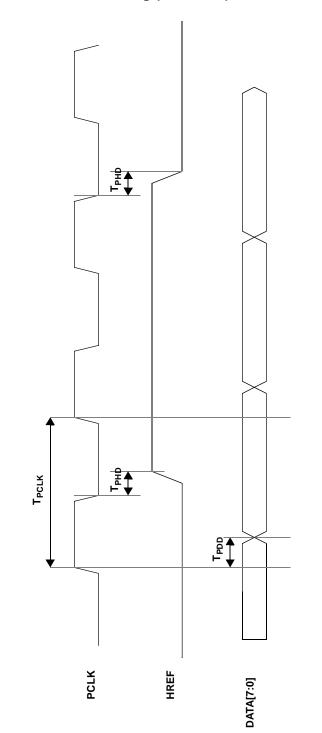

| t <sub>PCLK</sub>               | PCLK cycle time (@ 50Hz fps)                                            | -          | -          | 139        | ns     |

| t <sub>PHD</sub>                | PCLK to HREF delay                                                      | 25         | -          | -          | ns     |

| t <sub>PDD</sub>                | PCLK to DATA delay                                                      | 25         | -          | -          | ns     |

| Symbol             | Descriptions                     | Max      | Туре | Min | Units |

|--------------------|----------------------------------|----------|------|-----|-------|

| Interface timi     | ng                               | <b>i</b> |      |     |       |

| t <sub>OE</sub>    | Output enable access time        | 15       | -    | -   | ns    |

| t <sub>OEZ</sub>   | Output enable to Z delay         | 15       | -    | -   | ns    |

| t <sub>RC</sub>    | Register read cycle time         | -        | -    | 100 | ns    |

| t <sub>CS</sub>    | Chip select pulse width          | -        | -    | 50  | ns    |

| t <sub>CSA</sub>   | Chip select access time          | 30       |      |     | ns    |

| t <sub>CSX</sub>   | Chip select to data invalid time | 15       |      |     | ns    |

| t <sub>AA</sub>    | Address access time              | 30       |      |     | ns    |

| t <sub>AX</sub>    | Address data invalid time        | 15       | -    |     | ns    |

| t <sub>WC</sub>    | Register write cycle time        | -        | -    | 100 | ns    |

| t <sub>WE</sub>    | Write enable pulse width         | -        | -    | 50  | ns    |

| t <sub>AS</sub>    | Write cycle address set up time  | -        | -    | 0   | ns    |

| t <sub>AH</sub>    | Write cycle address hold time    | -        | -    | 0   | ns    |

| t <sub>DS</sub>    | Write cycle data set up time     | -        | -    | 20  | ns    |

| t <sub>DH</sub>    | Write cycle data hold time       | -        | -    | 0   | ns    |

| t <sub>SYNC</sub>  | External FSI cycle time          | -        | 2    | -   | frame |

| t <sub>PD</sub>    | Chip power up time               | 100      | -    | -   | us    |

| DIGIAL/Analo       | og video parameters              |          |      | 1   | 1     |

| AVO                | Composite video level (p-p)      | -        | 2.0  | -   | V     |

| AV <sub>SYNC</sub> | sync amplitude                   | 0.55     | -    | 0.6 | V     |

| Ravo               | Output load resistance           |          | 150  |     | Ohm   |

| t <sub>H</sub>     | horizontal line width            |          | 458  |     | pclk  |

| t <sub>HSYNC</sub> | horizontal sync width            |          | 32   |     | pclk  |

| t <sub>HF</sub>    | horizontal blank front porch     |          | 9    |     | pclk  |

| t <sub>HB</sub>    | horizontal blank back porch      |          | 33   |     | pclk  |

| t <sub>HACT</sub>  | active pixel in one scan line    |          | 384  |     | pclk  |

## Table 4. Electrical parameters ( $0^{\circ}C \le TA \le 85^{\circ}C$ , voltages referenced to GND) (Continued)

| Symbol             | Descriptions                             | Max | Туре  | Min | Units          |

|--------------------|------------------------------------------|-----|-------|-----|----------------|

| t <sub>VB1</sub>   | field 2 vertica back equaliztion width   |     | -     |     | t <sub>H</sub> |

| t <sub>V</sub>     | vertical field width                     |     | 312.5 |     | t <sub>H</sub> |

| t <sub>VSYNC</sub> | vertical sync width                      |     | 2.5   |     | t <sub>H</sub> |

| t <sub>VF1</sub>   | field 1 vertical front equlization width |     | 3     |     | t <sub>H</sub> |

| t <sub>VB1</sub>   | field 1 vertica back equaliztion width   |     | 19    |     | t <sub>H</sub> |

| t <sub>VF2</sub>   | field 2 vertical front equlization width |     | 2.5   |     | t <sub>H</sub> |

| t <sub>VB2</sub>   | field 2 vertica back equaliztion width   |     | 19.5  |     | t <sub>H</sub> |

| t <sub>VACT</sub>  | active line in a field                   |     | 288   |     | t <sub>H</sub> |

# **Table 4. Electrical parameters** ( $0^{\circ}C \le TA \le 85^{\circ}C$ , voltages referenced to GND) (Continued)

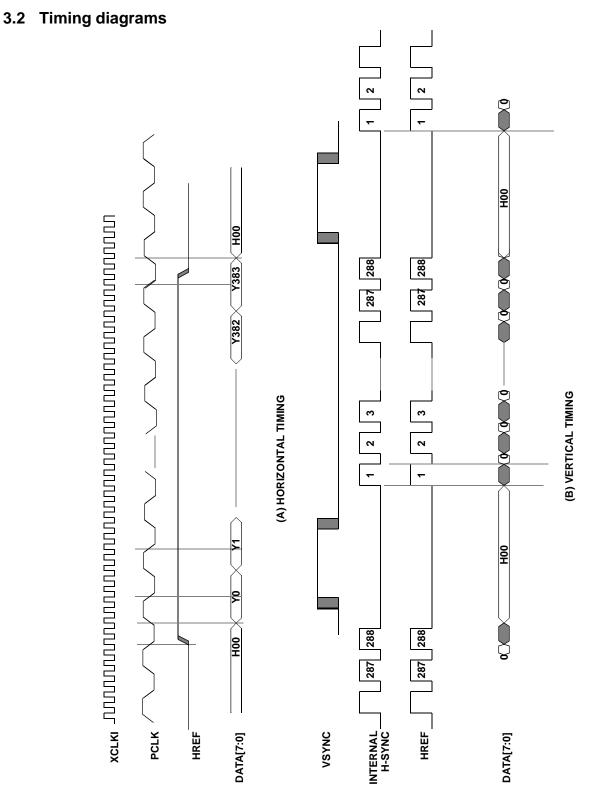

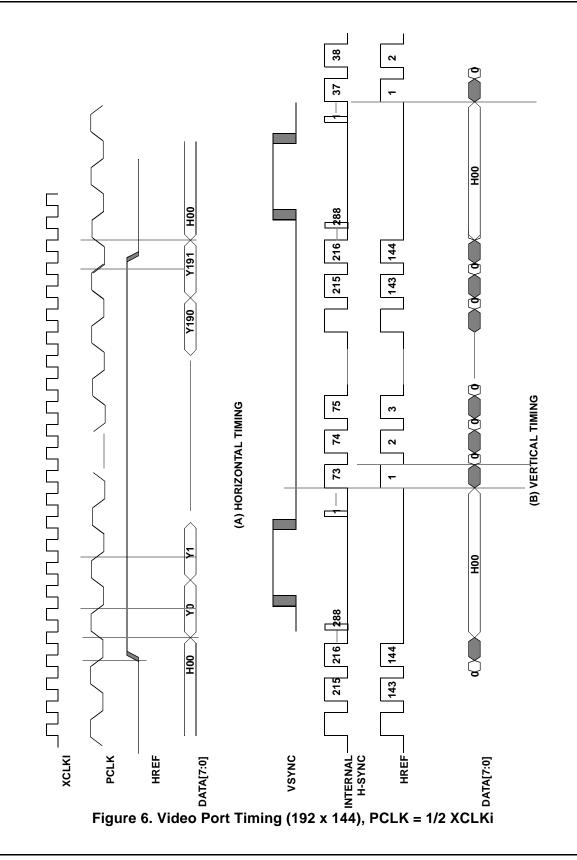

Figure 5. Video Data Timing (384 x 288), PCLK = 1/4 XCLKi

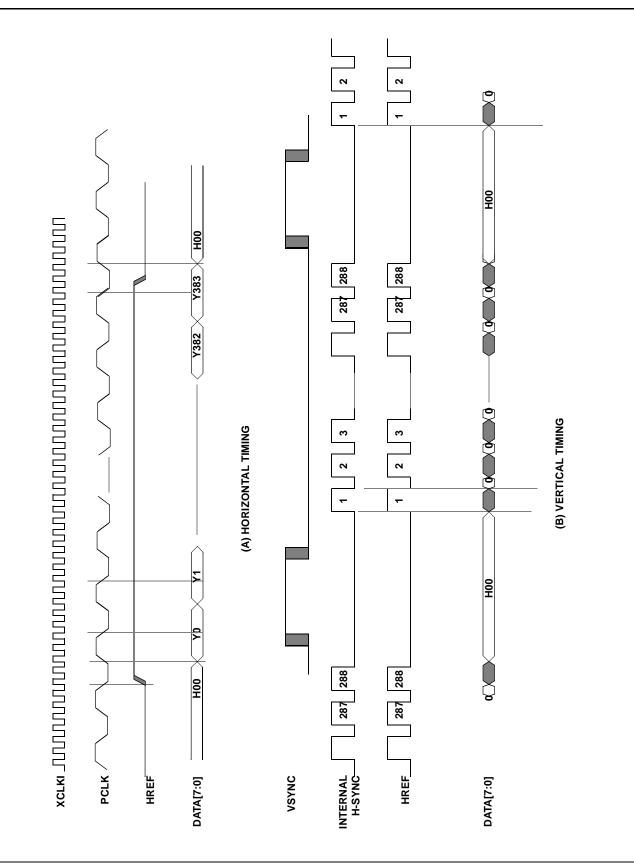

#### Figure 7. Video Port Timing (384 x 288), PCLK = 1/2 XCLKi

Figure 8. Pixel Timing

Figure 9. Register R/W Timing

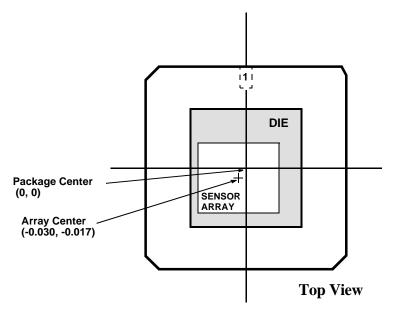

Figure 10. OV5017 Sensor Array Location Dimensions (in inches)

# <u>ERRATA</u>

<u>11/20/97</u>

- 1. In default mode, the video data changes on the falling edge of PCLK instead of on the rising edge. We recommand inverting the PCLK pin polarity by setting MCTL(1) so the video data can still be latched on the falling edge of PCLK. All the pclk timing parameters is applied to inverted PCLK.

- 2. OV5017 default active HREF window width has one extra pixel, 385 instead of 384, the back porch blanking is one less, that is:

$t_{HACT} = 385, t_{HB} = 32.$

<u>2/14/98</u>

- 3. A glitch (width 1/2 ~ 10 PCLKS) in HREF appears between VSYNC and the first valid HREF if programmed FRCTL(5:0) >= 9.

- 4. Intensity of lines (32,33,256,257) may be different from the rest of image if programmed FRCTL(5:0)= 4,5,9~11,13~15,17~22,24~63.