## W3030 3 V Dual-Mode IF Cellular Receiver

#### **Features**

- Proven double conversion architecture:

- First IF capability: 10 MHz to over 1000 MHz

- Second IF capability: 0.2 MHz to 2.0 MHz

- Dual second IF amplifiers and demodulators:

- Analog-mode limiting amplifier and FM quadrature detector

- Digital-mode linear AGC amplifiers with dual-mixer I & Q quadrature demodulator

- Accurate, onboard local oscillator phase splitter for digital quadrature demodulator

- Four enable/powerdown modes, selectable from two digital control pins, allow operation with minimal supply current

- Low supply current

- Analog received signal strength indicator (RSSI) available

- Analog AGC for digital-mode IF amplifiers

- Over 100 dB combined voltage gain

### **Applications**

- IS-136 (North American dual-mode) cellular radio portable and mobile terminals

- Cellular radio base stations

- Digital satellite communications

- Multisymbol signaling receivers

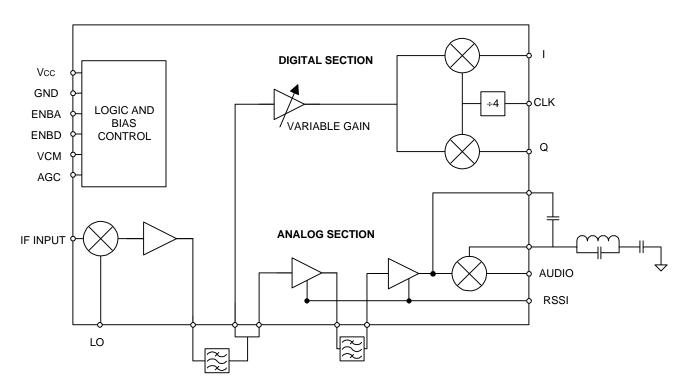

Figure 1. General Block Diagram

## **Table of Contents**

| Features                  |                |

|---------------------------|----------------|

| Applications              |                |

| Description               |                |

| Pin Information           | Ę              |

| Absolute Maximum Ratings  |                |

| Handling Precautions      |                |

| Operating Ranges          | 8              |

| Electrical Specifications |                |

| RSSI                      |                |

| Quadrature Detector       |                |

| Quad Tank S-Curves        | 12             |

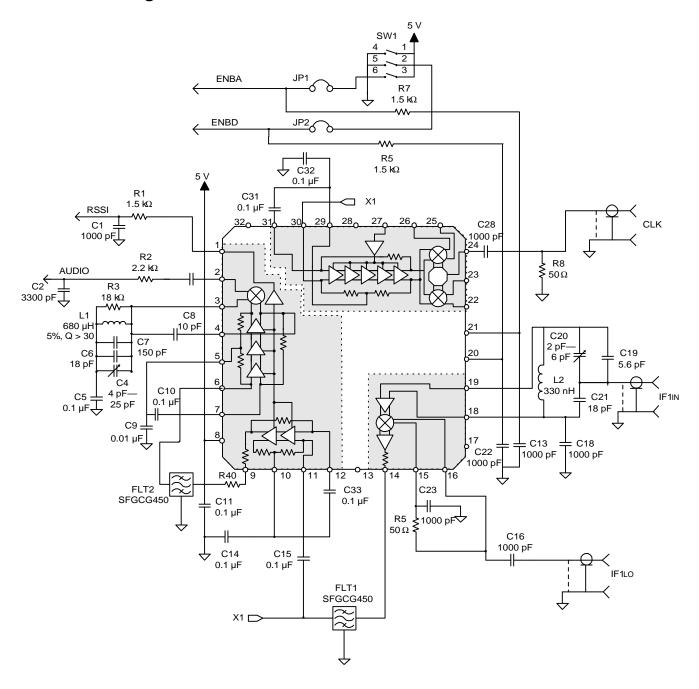

| Test Circuit Diagram      | 14             |

| Characteristic Curves     |                |

| Outline Diagram           |                |

| 32-Pin TQFP               | 20             |

| Manufacturing Information | 2 <sup>2</sup> |

| Ordering Information      |                |

### **Description**

The W3030 is a monolithic integrated circuit that provides most of the receive path functions required to meet the IS-136 (and IS-54) standard. The W3030 converts FM or digitally modulated IF carriers up to 200 MHz and provides required IF gain and separate baseband detectors for the two modulation modes.

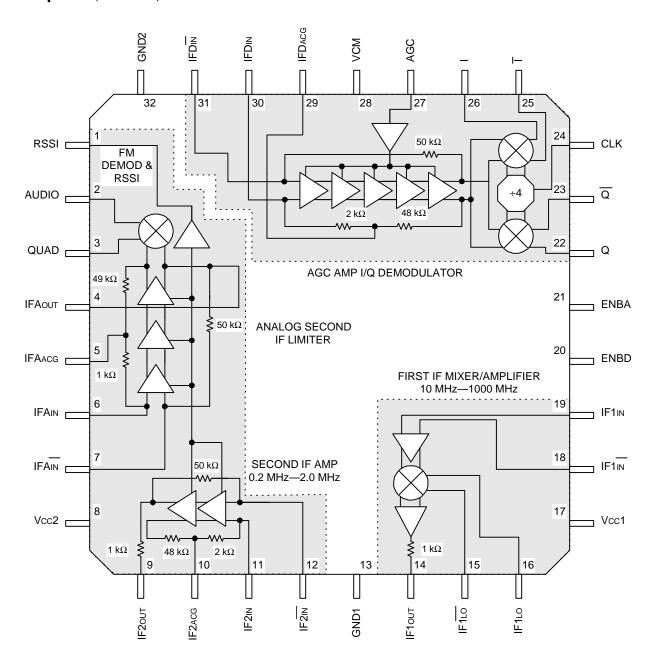

The W3030 is organized into three subfunctions (see Figure 2):

- 1. First IF mixer/amplifier

- 2. Analog second IF

- 3. Digital second IF sections

(Note that the electrical specification tables correspond to each subfunction.)

Each section has a buffered output to allow for external filtering, which also provides flexibility in system architecture selection. The first IF mixer section provides 30 dB of fixed voltage conversion gain (power gain = 17 dB). The first IF mixer also performs down-conversion to the 0.2 MHz—2.0 MHz range, which allows the use of inexpensive ceramic filters at two points in the signal path. In the second IF section, the signal path may be split between two

parallel amplifier/demodulator sections. In the analog second IF, there is a 40 dB amplifier followed by a 60 dB hard-limiting amplifier and an FM quadrature detector (noncoherent discriminator). The signal path between the 40 dB and 60 dB amplifier stages is brought off-chip for external filtering purposes. In digital mode, an AGC amplifier provides gain between 10 dB and 80 dB. The digital signal is demodulated in double-balanced mixers that are fed with an external local oscillator (LO) signal. The external LO passes through a divide-by-four counter to provide the final IF LO frequency. This architecture greatly reduces the possibility of feedback of the external LO signal to the IF input, which would cause dc offsets at the I & Q outputs. This circuit also provides a 90° phase shift of the LO that is independent of duty cycle. The resulting I & Q differential pairs can be level-shifted using the VCM input pin, providing flexibility in interfacing to digital processing ICs.

A pair of logic inputs allows the device to be put into a powerdown mode and one of two partially enabled modes (analog or digital only), or a fully enabled mode, allowing the use of analog RSSI while in digital receive mode.

## **Description** (continued)

Figure 2. Detailed Block Diagram with Pinout

## **Pin Information**

**Table 1. Pin Descriptions**

| Pin<br>Number | Pin Name         | Pin Description                                                                                                                                                                                                 |

|---------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | RSSI             | <b>Received Signal Strength Indicator.</b> Provides logarithmic (dB-linear) dc output voltage.                                                                                                                  |

| 2             | AUDIO            | Audio Output. Audio output of FM detector.                                                                                                                                                                      |

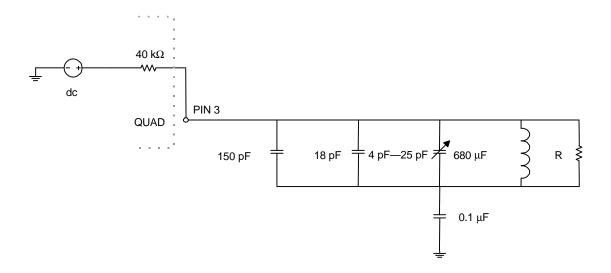

| 3             | QUAD             | Quad Input. Input to FM detector from parallel LC quad coil.                                                                                                                                                    |

| 4             | IFAout           | <b>Analog Output.</b> Output of analog section limiting amplifiers; couple to quad coil and pin 3 (QUAD) with 10 pF capacitor.                                                                                  |

| 5             | IFAACG           | <b>Analog Signal Ground.</b> Signal ground for analog section limiting amplifier; connect to ground with 0.1 µF capacitor.                                                                                      |

| 6             | IFAin            | Analog Mode Limiter Input. Differential input to analog IF limiting amplifier; to be directly coupled to dielectric sources such as ceramic filters. Pin 6 is approximately 1 $k\Omega$ with pin 5 ac-grounded. |

| 7             | IFAIN            | <b>Analog Mode Limiter Input (Inverting).</b> Differential input to analog IF limiting amplifier. To be ac-grounded.                                                                                            |

| 8             | Vcc2             | <b>Second IF Power Supply.</b> Positive power supply connection for both analog and digital second IF amplifiers and demodulators.                                                                              |

| 9             | IF2out           | <b>Second IF Output.</b> Output of 40 dB second IF amplifier; directly couple to dielectric loads such as ceramic filters. Includes internal 1 $k\Omega$ termination resistor.                                  |

| 10            | IF2ACG           | Second IF Signal Ground. Signal ground for 40 dB second IF amplifier; connect to ground with 0.1 µF capacitor.                                                                                                  |

| 11            | IF2IN            | <b>Second IF Input.</b> Differential input to 40 dB second IF amplifier; to be directly coupled to dielectric sources such as ceramic filters. Pin 11 is approximately 2 k $\Omega$ with pin 10 ac-grounded.    |

| 12            | IF2 IN           | <b>Second IF Input (Inverting).</b> Differential input to 40 dB second IF amplifier. To be ac-grounded.                                                                                                         |

| 13            | GND <sub>1</sub> | First IF Mixer Ground. Power supply (dc) ground for first IF mixer section.                                                                                                                                     |

| 14            | IF1out           | First IF Mixer Output. Output of first IF mixer/amplifier section; to be directly coupled to dielectric loads such as ceramic filters. Includes internal 1 $k\Omega$ termination resistor.                      |

| 15            | IF1 LO           | First IF Mixer Logical Input (Inverting). Differential input to first IF mixer local oscillator; to be capacitively coupled to sources with a dc level offset.                                                  |

| 16            | IF1LO            | First IF Mixer Logical Input. Differential input to first IF mixer local oscillator. To be ac-grounded.                                                                                                         |

| 17            | Vcc1             | First IF Mixer Power Supply. Positive power supply connection for first IF mixer/amplifier section.                                                                                                             |

| 18            | IF1 IN           | First IF Mixer Input (Inverting). Differential input to first IF mixer/amplifier section; to be ac-coupled to ground or source.                                                                                 |

| 19            | IF1IN            | First IF Mixer Input. Differential input to first IF mixer/amplifier section.                                                                                                                                   |

# Pin Information (continued)

Table 1. Pin Descriptions (continued)

| Pin<br>Number | Pin Name         | Pin Description                                                                                                                                                                                                         |

|---------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20            | ENBD             | Enable Digital Mode. Positive logic enable connection for digital mode operation.                                                                                                                                       |

| 21            | ENBA             | Enable Analog Mode. Positive logic enable connection for analog mode operation.                                                                                                                                         |

| 22            | Q                | Q Output. Differential output from Q mixer of quadrature demodulator.                                                                                                                                                   |

| 23            | Q                | Q Output (Inverting). Differential output from Q mixer of quadrature demodulator.                                                                                                                                       |

| 24            | CLK              | <b>Clock Input.</b> Local oscillator (clock) input to quadrature demodulator phase shifter; to be capacitively coupled. Input frequency must be four times second IF center frequency.                                  |

| 25            | Ī                | I Output (Inverting). Differential output from I mixer of quadrature demodulator.                                                                                                                                       |

| 26            | I                | I Output. Differential output from I mixer of quadrature demodulator.                                                                                                                                                   |

| 27            | AGC              | <b>Automatic Gain Control.</b> AGC control input; to be connected to dc source of 0.25 V—1.55 V.                                                                                                                        |

| 28            | VCM              | <b>Common-Mode Voltage.</b> Common-mode voltage dc offset set point for I & Q interface, typically Vcc/2.                                                                                                               |

| 29            | IFDACG           | <b>Digital Signal Ground.</b> Signal ground for digital section limiting amplifier; connect to ground with 0.1 µF capacitor.                                                                                            |

| 30            | IFDIN            | <b>Digital Second IF Input.</b> Differential input to digital section AGC amplifier; to be directly coupled to dielectric sources such as ceramic filters. Pin 30 is approximately 2 $k\Omega$ with pin 29 ac-grounded. |

| 31            | IFD IN           | Digital Second IF Input (Inverting). Differential input to digital section AGC amplifier. To be ac-grounded.                                                                                                            |

| 32            | GND <sub>2</sub> | <b>Second IF Ground.</b> Power supply ground for both analog and digital second IF amplifier and demodulator sections.                                                                                                  |

**Table 2. Digital Control Pin Truth Table**

| Control Pin |      | Mode/Function                                                                                                   |  |

|-------------|------|-----------------------------------------------------------------------------------------------------------------|--|

| ENBA        | ENBD |                                                                                                                 |  |

| LOW         | LOW  | All Sleep. All receive circuits powered down, supply current <10 μA.                                            |  |

| LOW         | HIGH | Digital Receive. First IF mixing stage, AGC amp and I/Q quadrature demodulators active.                         |  |

| HIGH        | LOW  | Analog/FM Receive. First IF mixing stage, 40 dB IF amp, 60 dB limiting amp, RSSI, and FM detector active.       |  |

| HIGH        | HIGH | <b>All Active.</b> All receive circuits functional, e.g., digital mode I & Q demodulator used with analog RSSI. |  |

## **Absolute Maximum Ratings**

Stresses in excess of the absolute maximum ratings can cause permanent damage to the device. These are absolute stress ratings only. Functional operation of the device is not implied at these or any other conditions in excess of those given in the operations sections of the data sheet. Exposure to absolute maximum ratings for extended periods can adversely affect device reliability.

| Parameter                          | Min  | Max       | Unit |

|------------------------------------|------|-----------|------|

| Ambient Operating Temperature      | -35  | 100       | °C   |

| Storage Temperature                | -65  | 150       | °C   |

| Lead Temperature (soldering, 10 s) | _    | 300       | °C   |

| Positive Supply Voltage            | 0    | 4.5       | Vdc  |

| Power Dissipation                  | _    | 650       | mW   |

| Output Current (continuous)        | _    | 160       | mA   |

| ac Peak-to-peak Input Voltage      | 0    | Vcc       | Vdc  |

| Enable Input Voltage               | -0.3 | Vcc + 0.4 | Vdc  |

| VCM, AGC Input Voltage             | -0.3 | Vcc + 0.4 | Vdc  |

## **Handling Precautions**

Although protection circuitry has been designed into this device, proper precautions should be taken to avoid exposure to electrostatic discharge (ESD) during handling and mounting. Lucent Technologies Microelectronics Group employs a human-body model (HBM) and a charged-device model (CDM) for ESD-susceptibility testing and protection design evaluation. ESD voltage thresholds are dependent on the circuit parameters used to define the model. No industry-wide standard has been adopted for CDM. However, a standard HBM (resistance =  $1500~\Omega$ , capacitance = 100~pF) is widely used and, therefore, can be used for comparison purposes. The HBM ESD threshold presented here was obtained by using these circuit parameters:

| W3030 ESD Threshold Voltage |         |  |  |  |

|-----------------------------|---------|--|--|--|

| ESD Model Rating            |         |  |  |  |

| НВМ                         | ≥1500 V |  |  |  |

| CDM ≥1500 V                 |         |  |  |  |

## **Operating Ranges**

Performance is not guaranteed over the full range of all conditions possible within this table. However, this table lists the ranges of external conditions in which the W3030 provides general functionality, which may be useful in specific applications, without risk of permanent damage. The conditions for guaranteed performance are described below.

**Table 3. W3030 Operating Ranges**

| Parameter                                                                                                                                                    | Min               | Max               | Unit                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|------------------------|

| Supply Voltage                                                                                                                                               | 2.7               | 4.1               | Vdc                    |

| First IF Mixer/Amplifier Section: Input Frequency Range LO Frequency LO Input Level Range                                                                    | 10<br>10<br>–10   | 1000<br>1000<br>6 | MHz<br>MHz<br>dBm/50 Ω |

| Digital Second IF Amplifier, AGC Quadrature Demodulator Section: Second IF Frequency Quadrature Demodulator LO (CLK) Frequency CLK Input Level (square wave) | 0.1<br>0.4<br>–10 | 4<br>16<br>6      | MHz<br>MHz<br>dBm/50 Ω |

| Analog Second IF Amplifier Frequency                                                                                                                         | 0.1               | 4                 | MHz                    |

| VCM Input Range                                                                                                                                              | 1.25              | Vcc - 0.8         | V                      |

## **Electrical Specifications**

The following apply to all specifications, unless otherwise listed: TA = 25 °C  $\pm$  3 °C; Vcc = 2.7 Vdc; PIF1LO = -3 dBm to +3 dBm/50  $\Omega$ ; IF1 = 10 MHz to 200 MHz; IF2 = 0.2 MHz to 2 MHz; ENBA = ENBD > 1.9 Vdc.

**Table 4. dc and Logic Parameters**

| Parameter                                  | Min | Тур | Max | Unit |

|--------------------------------------------|-----|-----|-----|------|

| Supply Current:                            |     |     |     |      |

| Fully Enable (Vcc = 3.3)                   | _   | 8   | 11  | mA   |

| Analog Only Mode (Vcc = 3.3)               |     | 5   | 8   | mA   |

| Digital Only Mode (Vcc = 3.3)              | _   | 5   | 8   | mA   |

| Sleep Mode (Vcc = 3.3)                     | _   | <1  | 10  | μΑ   |

| VIHMIN                                     | 1.9 | _   | _   | V    |

| VILMAX                                     | _   | _   | 0.7 | V    |

| IILMAX (VI = 0.7 V)                        | _   | 0   | 10  | μA   |

| IIHMAX (VI = VCC)                          | _   | 30  | 250 | μΑ   |

| Enable Time (external capacitor dependent) | _   | 30  | _   | μs   |

## **Electrical Specifications** (continued)

### Table 5. First IF Mixer/Amplifier Section

IF deviation =  $\leq 0.5$  MHz.

| Parameter                                                          | Min | Тур        | Max | Unit     |

|--------------------------------------------------------------------|-----|------------|-----|----------|

| Voltage Gain (with input matching network from 50 $\Omega$ source) | _   | 30         | _   | dB       |

| Power Gain                                                         | _   | 17         | _   | dB       |

| Gain Flatness within IF Deviation                                  | _   | ±0.2       |     | dB       |

| Noise Figure at IF Input (SSB)                                     | _   | 14         |     | dB       |

| 1 dB Compression Point at Input to Matching Network                | _   | -27        |     | dBm      |

| IP3 at First IF Matching Network Input                             | _   | -17        | _   | dBm      |

| IF Input Impedance @ 82 MHz                                        | _   | 1.7 II 1.8 | _   | kΩ II pF |

| LO Input Impedance @ 82 MHz                                        | _   | 4 II 1.5   | _   | kΩ II pF |

| IF Output Impedance                                                | _   | 1.0        | _   | kΩ       |

| LO Suppression at IF Input (relative to LO input level)            | _   | 40         |     | dB       |

### Table 6. Analog Second IF Amplifier, Limiter, RSSI, FM Detector Section

Filter  $ZIN = ZOUT = 1.0 \text{ k}\Omega$ ; 6 dB attenuation between 40 dB amplifier output and 60 dB limiting amplifier input; 1 kHz FM at 8 kHz deviation; IF filter bandwidth = 28 kHz. Quad tank Q = 10.

| Parameter                                                    | Min  | Тур  | Max  | Unit  |

|--------------------------------------------------------------|------|------|------|-------|

| IF Gain (net) IF2IN to Audio                                 | _    | 86   | _    | dB    |

| RSSI Range of Input Signal                                   | 65   | 90   | _    | dB    |

| RSSI Output Voltage with –20 dBm/50 Ω into IF1IN             | 1.75 | 2.1  | 2.6  | V     |

| RSSI Output Voltage with –110 dBm/50 Ω into IF1IN            | 0.4  | 0.7  | 0.92 | V     |

| RSSI Linearity over –100 dBm to –35 dBm into IF1IN           | _    | ±0.8 | ±2.5 | dB    |

| RSSI Transfer Function                                       | 13   | 17   | 25   | mV/dB |

| RSSI Current Capability                                      | _    | 100  | _    | μΑ    |

| IF Input Impedance (40 dB amplifier)                         | _    | 2    |      | kΩ    |

| IF Output Impedance (40 dB amplifier)                        | _    | 1    |      | kΩ    |

| IF Input Impedance (60 dB limiter)                           | _    | 1    | _    | kΩ    |

| IF Output Impedance (60 dB limiter)                          | _    | 1    | _    | kΩ    |

| IP3 of 40 dB Amplifier Section (at its output)               | _    | 3    |      | dBm   |

| FM Detector Input Impedance (quad, pin 3)                    | _    | 40   | _    | kΩ    |

| Audio Output Impedance                                       | _    | 500  |      | Ω     |

| Audio Output Amplitude (IF1IN = -35 dBm)                     | 150  | 220  | 270  | mVrms |

| Audio SINAD for IF1IN = -35 dBm (C-message weighting filter) | 32   |      |      | dB    |

## **Electrical Specifications** (continued)

Table 7. Digital Second IF Amplifier, AGC, Quadrature Demodulator Section

PCLK = 320 mVp-p to 640 mVp-p (square wave); IF deviation =  $\leq$ 0.5 MHz; VCM = 1.3 Vdc to Vcc - 0.8 Vdc.

| Parameter                                                                                                           | Min        | Тур        | Max        | Unit            |

|---------------------------------------------------------------------------------------------------------------------|------------|------------|------------|-----------------|

| IF Input Impedance                                                                                                  | _          | 2          | _          | kΩ              |

| CLK Input Impedance                                                                                                 | _          | 28 II 8.2  | _          | kΩ II pF        |

| Baseband: -3 dB Bandwidth                                                                                           | _          | 150        | _          | kHz             |

| AGC Control Input Resistance                                                                                        | _          | 500        | _          | kΩ              |

| AGC Control Voltage Range                                                                                           | _          | 0.9 ± 0.65 |            | Vdc             |

| AGC Transfer Function                                                                                               | 11         | 18         | 23         | mV/dB           |

| AGC Gain Linearity, VAGC = 0.3 to 1.1                                                                               | _          | ±1.5       | ±2.5       | dB              |

| I and Q Phase Accuracy                                                                                              | -2         | 0.4        | 2          | degrees         |

| I and Q ac Amplitude Mismatch                                                                                       | -0.3       | ±0.05      | 0.3        | dB              |

| I and Q Maximum Output Swing (differential, compressed)                                                             | _          | 2          | _          | Vp-p            |

| I and Q Common-mode Voltage as Function of VCM, i.e., $\frac{VI + V\bar{I}}{2} \text{ or } \frac{VQ + V\bar{Q}}{2}$ | VCM - 0.08 | VCM input  | VCM + 0.08 | Vdc             |

| I and Q Differential Offset Voltage                                                                                 | _          | 0          | 35         | mV              |

| I and Q Maximum Sink Current per Pin (sum of dc and peak ac)                                                        | _          | 100        | 1          | μА              |

| I and Q Maximum Source Current per Pin (sum of dc and peak ac)                                                      | _          | 1          |            | mA              |

| IP3 at Output (I or Q, differential)                                                                                | _          | 15         | _          | dBm/50 $\Omega$ |

| 1 dB Compression Point (at output, differential)                                                                    | _          | 7          | _          | dBm/50 $\Omega$ |

| Noise Figure @ IF Input, Differential I + jQ                                                                        | _          | 11         | _          | dB              |

| VCM Input Impedance                                                                                                 | _          | 400        | _          | kΩ              |

#### Table 8. Digital Gain and First IF Mixer Input to Baseband

PCLK = 320 mVp-p to 640 mVp-p (square wave); IF deviation =  $\leq$ 0.5 MHz; VCM = 1.3 Vdc to Vcc - 0.8 Vdc. Gain numbers include -1.5 dB filter loss.

| Parameter         | Min | Тур | Max | Unit |

|-------------------|-----|-----|-----|------|

| Gain VAGC = 1.1 V | 91  | 99  | 128 | dB   |

| Gain VAGC = 0.3 V | 36  | 54  | 60  | dB   |

#### RSSI

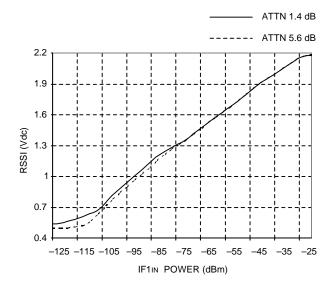

The RSSI output provides a voltage level that is proportional to the amount of signal present in the analog second IF section. This voltage level is generated internally by summing of the signal current at different points in the 40 dB and 60 dB IF chains. The amount of loss between the 40 dB and 60 dB sections will affect the RSSI linearity. Figure 3 contains two traces of RSSI voltage versus IF input power. One trace is with only the filter loss between the 40 dB and 60 dB amplifiers. The second trace is with a filter and a resistor, to give a total loss of 5.6 dB. The figure indicates a nonlinearity around the -75 dBm input level. This nonlinearity occurs because the 60 dB amplifier chain enters compression, causing less RSSI output. Eventually, as the input signal increases, the 40 dB amplifier will begin to contribute to the total RSSI.

It was determined that 6 dB of interstage loss produces the optimal RSSI response. Most ceramic filters have less than 6 dB insertion loss. Therefore, some additional loss must be inserted in addition to the filter. The simplest way is to use a resistor in series with the filter. This method will cause a mismatch to the filter and may distort its passband response. An L or T configuration may be necessary to provide the required loss without mismatching the filter.

Figure 3. RSSI Out vs. IF1IN Power: 1.4 dB and 5.6 dB Loss Between 40 dB and 60 dB Amplifiers

#### **Quadrature Detector**

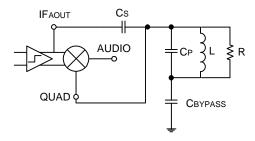

Figure 4 is a simplified schematic of the quadrature detector of the W3030. The quadrature detector circuit is similar to a mixer; but, instead of mixing two different frequencies, it multiplies two signals of the same frequency that are phase-shifted versions of each other. Multiplying the phase-shifted with the unshifted signals produces the audio portion of the FM signal.

Figure 4. Quadrature Detector

Before the IF signal is differentially applied to the multiplier, the signal is passed through a limiter stage to produce a constant amplitude signal. The same signal is brought out single-ended to pin 4, IFAOUT. The signal at IFAOUT is passed through a phase-shifting network (Cs + CP + L + R). The phase-shifted signal is applied back to the lower portion of the multiplier at pin 3, QUAD. The parallel L/C resonant circuit provides frequency selective filtering at the IF frequency. The L/C tank must be ac-grounded at the IF frequency through a dc blocking capacitor (CBYPASS).

Because information in an FM signal is contained in the deviation from the center frequency, the design of the resonant bandpass circuit is very important, particularly the load Q. A higher-loaded Q for a given deviation will produce a larger output signal than a lower Q circuit. However, a high Q circuit will permit only a limited amount of deviation from center frequency before distortion occurs.

Figure 5 illustrates an equivalent quad tank circuit including the W3030 40 k $\Omega$  input resistance. Equations 1 and 2 are used to calculate resonant frequency and tank circuit Q.

### **Quadrature Detector** (continued)

Figure 5. L/C Tank Equivalent Circuit

$$f1 = \frac{1}{2\pi\sqrt{LC}} = \frac{1}{2\pi\sqrt{\left(680 * 6^{-10}\right) * \left(184 * 10^{-12}\right)}} = 450 \text{ kHz}$$

Equation (1)

$$Q = 2\pi * f * RC = 2\pi * (450 * 10^{3}) * \frac{(40 * 10^{3} * 33 * 10^{3})}{(40 * 10^{3} + 33 * 10^{3})} * (184 * 10^{-12}) = 9.4$$

Equation (2)

The W3030 evaluation board is designed with a 450 kHz IF frequency, as shown in our example. The Q of the tank circuit is set to 10 by the external resistor.

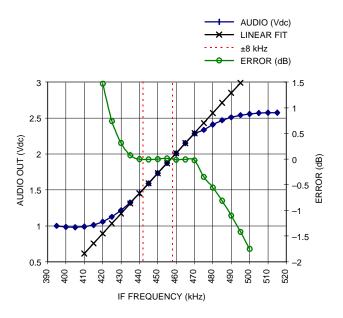

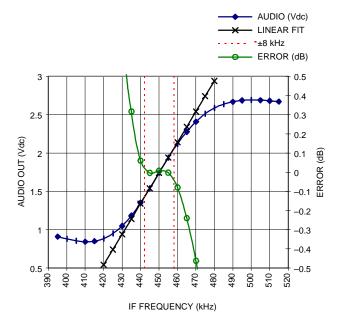

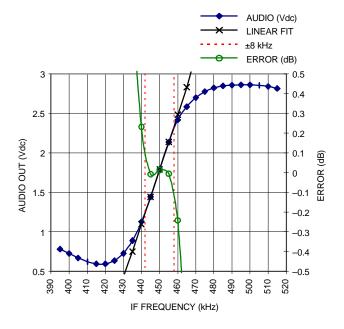

#### **Quad Tank S-Curves**

One method of determining if the Q of the tank is too large or too small is to produce an S-curve of the quad tank. An S-curve is a plot of the dc audio output voltage versus IF input frequency. With small deviations from center frequency, there is a proportional change in the dc audio output voltage. The overall linearity of the curve is determined by the Q of the tank circuit; therefore, the Q determines how much deviation is allowed before distortion of the audio signal occurs. The L/C tank circuit has a shunt resistor to set the Q of the tank. The procedure to produce these plots is as follows:

- 1. Remove the 450 kHz IF filter and drive the input of the limiting amplifier with a signal generator capable of FM modulation.

- 2. Apply FM modulation and adjust the tank capacitor for maximum audio out and minimal distortion.

- 3. Remove the FM modulation and sweep the IF frequency above and below center frequency while monitoring the dc voltage at the audio output.

The following S-curves were produced with the value of the quad tank resistor varied from 18 k $\Omega$ , to 30 k $\Omega$ , to removing the resistor. The resistor value of 33 k $\Omega$ , which corresponds to a Q of 10, was chosen as the optimal resistor value.

## **Quadrature Detector** (continued)

### **Quad Tank S-Curves** (continued)

Figure 6. Audio Output vs. IF Frequency, 18 k $\Omega$  Quad Tank Resistor

Figure 7. Audio Output vs. IF Frequency, 33  $k\Omega$  Quad Tank Resistor

Figure 8. Audio Output vs. IF Frequency, Quad Tank Resistor Removed

## **Test Circuit Diagram**

Figure 9. Test Circuit Diagram

#### **Characteristic Curves**

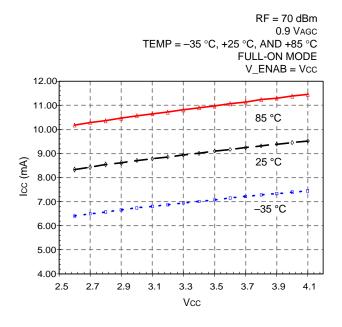

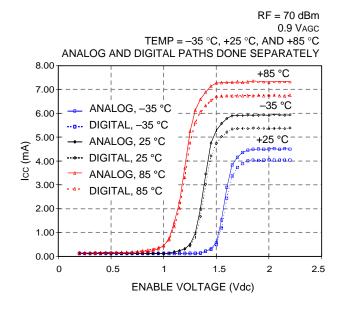

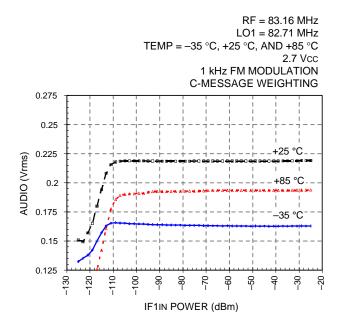

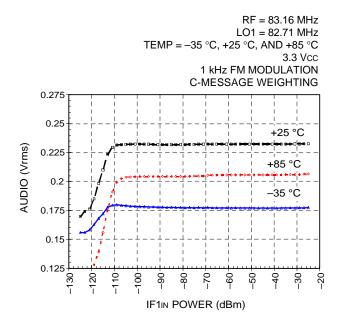

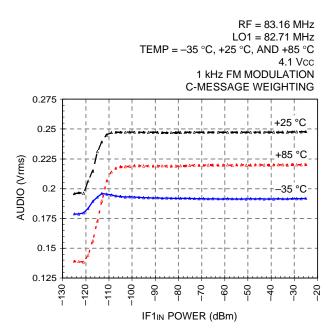

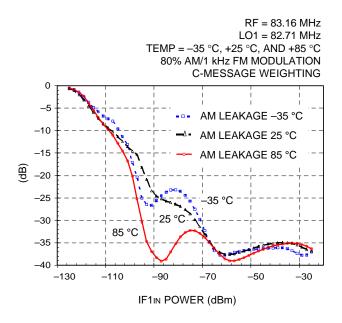

Unless otherwise specified, Vcc = 2.7 Vdc.

Figure 10. Icc vs. Vcc

Figure 11. Icc vs. Enable Voltage

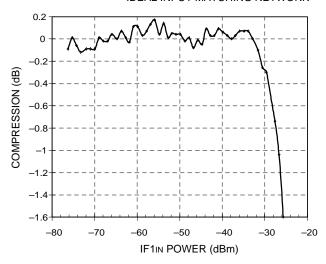

RF = 83.16 MHz LO1 = 82.71 MHz IDEAL INPUT MATCHING NETWORK

Figure 12. First IF Mixer Output Compression

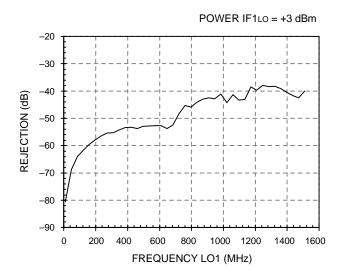

Figure 13. First IF Mixer: LO Rejection at IF Input vs. IF1Lo

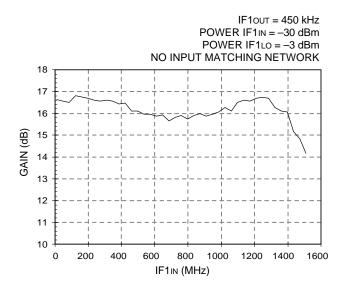

Figure 14. First IF Mixer: Conversion Voltage Gain vs. Frequency IF1IN

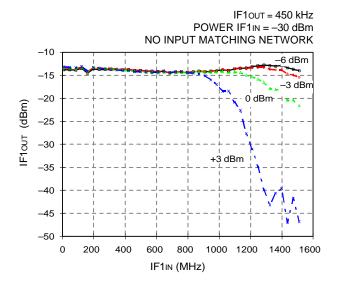

Figure 15. First IF Mixer: IF10UT vs. IF1IN (LO1 @ -6, -3, 0, +3 dBm)

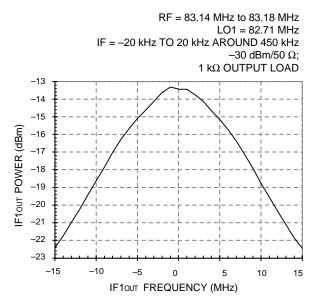

Figure 16. First IF Mixer Bandwidth

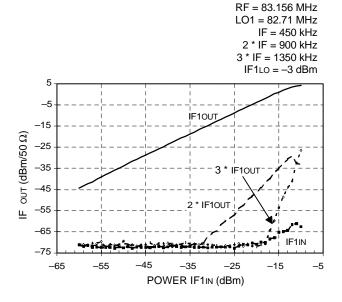

Figure 17. First IF Mixer: Significant Signals vs. Power IF1IN

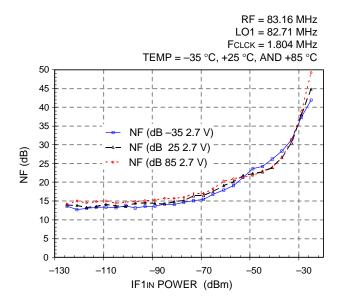

Figure 18. First Mixer and Digital Second IF

Section Noise Figure vs. IF1IN

Power

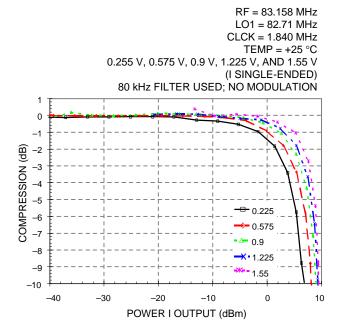

Figure 19. First Mixer and Digital Second IF Section Gain Compression vs. I Output (Single-Ended)

F1 = 83.158 MHz LO = 82.71 MHz CLCK = 1.840 MHz TEMP = -35 °C, +25 °C, AND +85 °C 0.9 VAGC (I SINGLE-ENDED) 80 kHz FILTER USED NO MODULATION 0 +85 °O COMPRESSION (dB) -2 -3 -4 -5 -35 °C -8 -25 -20 -105 10 15

Figure 20. First Mixer and Digital Second IF Section Gain Compression vs. I Output Power

I OUTPUT POWER (dBm/50  $\Omega$ )

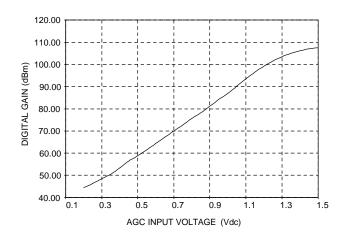

Figure 21. First Mixer and Digital Second IF Section Gain vs. AGC Input (-110 dBm)

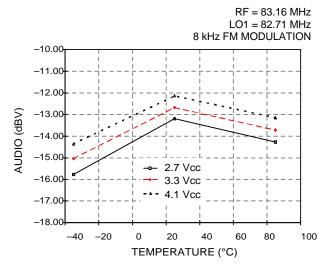

Figure 22. First Mixer and Analog Second IF Section Audio vs. IF1IN Power (2.7 Vcc)

Figure 23. First Mixer and Analog Second IF Section Audio vs. IF1IN Power (3.3 Vcc)

Figure 24. First Mixer and Analog Second IF Section Audio vs. IF1IN Power (4.1 Vcc)

TEMP = -35 °C, +25 °C, AND +85 °C

2.7 Vcc, 3.3 Vcc, AND 4.1 Vcc

1 kHz FM MODULATION

C-MESSAGE WEIGHTING

+25 °C

+85 °C

-35 °C

RF = 83.16 MHz LO1 = 82.71 MHz

Note: Minimum variation with voltage

-110

40

35

30

25

20

15

10

5

0

-130

SINAD (dB)

Figure 25. First Mixer and Analog Second IF Section SINAD vs. IF1IN Power

-70

IF1<sub>IN</sub> POWER (dBm)

-50

-30

-10

Figure 26. First Mixer and Analog Second IF Section AM Sensitivity (Relative Audio Out) vs. IF1IN Power

Figure 27. Audio Output vs. Temperature

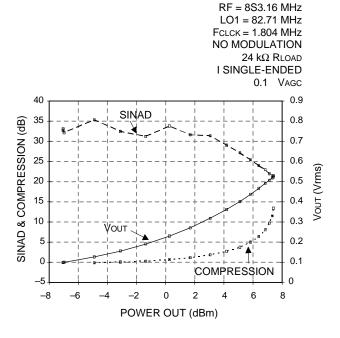

Figure 28. Digital Second IF Section SINAD, Output Voltage, and Compression vs. Output Power

Vcc = 3.0

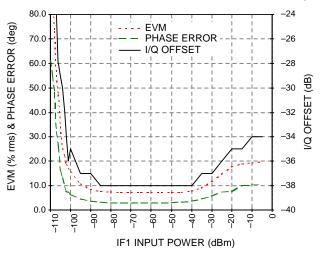

IS136 RANDOM-DATA DQPSK at 83.16 MHz IF1

IFLO 82.71 MHz @ 200 mVp-p

CLOCK 1.8 MHz @ 600 mVp-p

I & Q OUTPUT LEVELS HELD CONSTANT AT 0.5 Vp-p

SINGLE-ENDED USING AGC UNTIL LARGE INPUT EXCEEDS

RANGE

Figure 29. EVM/Phase/Offset vs. IF1 Input Level

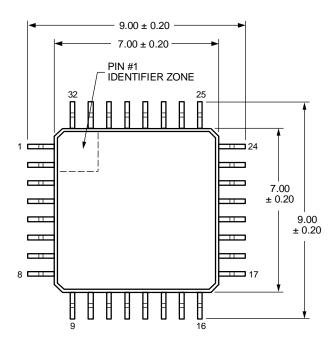

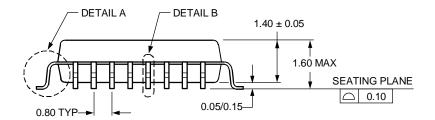

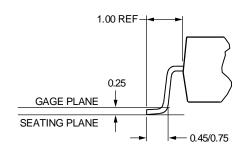

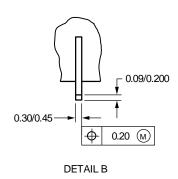

# **Outline Diagram**

### 32-Pin TQFP

Dimensions are in millimeters.

DETAIL A

12-3076

# **Manufacturing Information**

This device will be assembled in one of the following locations: assembly codes P, M, or T.

# **Ordering Information**

| Device Code    | Description      | Package | Comcode   |

|----------------|------------------|---------|-----------|

| LUCW3030ACA    | Bulk Tray        | 32TQFP  | 107841082 |

| LUCW3030ACA-DB | Dry Pack         | 32TQFP  | 107841090 |

| EVB3030A       | Evaluation Board | _       | 107739377 |

For additional information, contact your Microelectronics Group Account Manager or the following:

INTERNET: http://www.lucent.com/micro E-MAIL: docmaster@micro.lucent.com

Microelectronics Group, Lucent Technologies Inc., 555 Union Boulevard, Room 30L-15P-BA, Allentown, PA 18103 1-800-372-2447, FAX 610-712-4106 (In CANADA: 1-800-553-2448, FAX 610-712-4106) N. AMERICA

ASIA PACIFIC: Microelectronics Group, Lucent Technologies Singapore Pte. Ltd., 77 Science Park Drivé, #03-18 Cintech III, Singapore 118256 **Tel. (65) 778 8833**, FAX (65) 777 7495

CHINA: Microelectronics Group, Lucent Technologies (China) Co., Ltd., A-F2, 23/F, Zao Fong Universe Building, 1800 Zhong Shan Xi Road, Shanghai 200233 P.R. China Tel. (86) 21 6440 0468, ext. 316, FAX (86) 21 6440 0652

JAPAN: Microelectronics Group, Lucent Technologies Japan Ltd., 7-18, Higashi-Gotanda 2-chome, Shinagawa-ku, Tokyo 141, Japan

Tel. (81) 3 5421 1600, FAX (81) 3 5421 1700

Data Requests: MICROELECTRONICS GROUP DATALINE: Tel. (44) 1189 324 299, FAX (44) 1189 328 148 **EUROPE:**

Technical Inquiries: GERMANY: (49) 89 95086 0 (Munich), UNITED KINGDOM: (44) 1344 865 900 (Ascot), FRANCE: (33) 1 40 83 68 00 (Paris), SWEDEN: (46) 8 594 607 00 (Stockholm), FINLAND: (358) 9 4354 2800 (Helsinki), ITALY: (39) 02 6608131 (Milan), SPAIN: (34) 1 807 1441 (Madrid)

Lucent Technologies Inc. reserves the right to make changes to the product(s) or information contained herein without notice. No liability is assumed as a result of their use or application. No rights under any patent accompany the sale of any such product(s) or information.

Lucent Technologies

microelectronics group