# CE5037 Digital Satellite Tuner with RF Bypass

Data Sheet

## Features

- Direct conversion tuner for quadrature down conversion from L-band to Zero IF

- Symbol rate 1-45 MS/s

- High sensitivity < -83 dBm at 27.5 MS/s Code rate 7/8

- Independent RF AGC and baseband gain control

- Fifth order baseband filters with bandwidth adjustable from 6 to 43 MHz

- Fully integrated alignment-free low phase noise local oscillator

- Selectable RF Bypass

- Low power consumption 0.5W at 3.3V.

- 28 pin 5x5 mm QFN Package

# Applications

- DVB-S PayTV satellite receivers

- DSS satellite receivers

- DVB-S2 8PSK satellite receivers

January 2007

#### **Ordering Information**

WGCE5037 882557 28 Pin QFN\* Trays WGCE5037 S L9FV 882558 28 Pin QFN\* Tape & Reel \*Pb Free Matte Tin

-10°C to +85°C

## Description

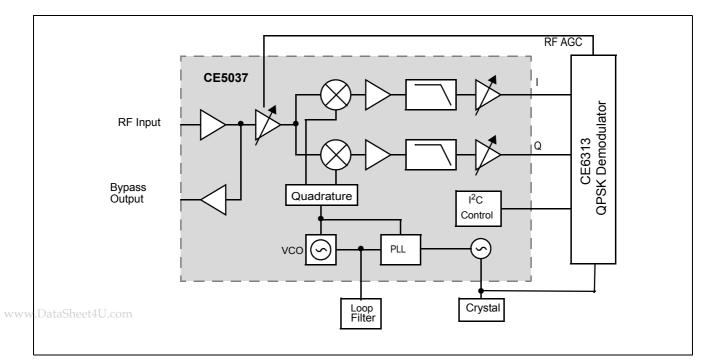

The CE5037 is a fully integrated direct conversion tuner for digital satellite receiver systems. It provides excellent immunity to composite undesired channels. The device also contains a RF Bypass for connecting to a second receiver module.

The CE5037 is simple to use, requiring no alignment or tuning algorithms and uses a minimum number of external components. The device is programmable via a  $I^2C$  compatible bus.

The CE5037 is qualified for DVB-S2 8PSK receiver applications

A complete reference design (CE9542) is available using CE6313 demodulator.

#### Figure 1 - Basic Block Diagram

1

# **Table of Contents**

| 1.0 Circuit Description                     | 5 |

|---------------------------------------------|---|

| 1.1 Functional Description                  |   |

| 1.2 Signal Path                             | 5 |

| 1.3 Local Oscillator Generation             |   |

| 1.4 I2C Interface                           | 7 |

| 2.0 Register Map and Programming            | 3 |

| 2.1 PLL Registers                           |   |

| 2.2 RF Control Register                     | ) |

| 2.3 Base Band Registers                     | I |

| 2.4 Local Oscillator Registers              | 2 |

| 2.5 General Control Register                | ŀ |

| 3.0 Applications Information                | 5 |

| 3.1 General Design Guidelines               | 3 |

| 3.2 DVB-S2 Applications                     | 3 |

| 3.3 Baseband Filter Bandwidth Calculation17 | 7 |

| 4.0 Pin Descriptions                        | 3 |

| 5.0 Absolute Maximum Ratings                |   |

| 6.0 Operating Conditions                    |   |

| 7.0 Electrical Characteristics              |   |

| 8.0 Typical Performance Data                |   |

Data Sheet

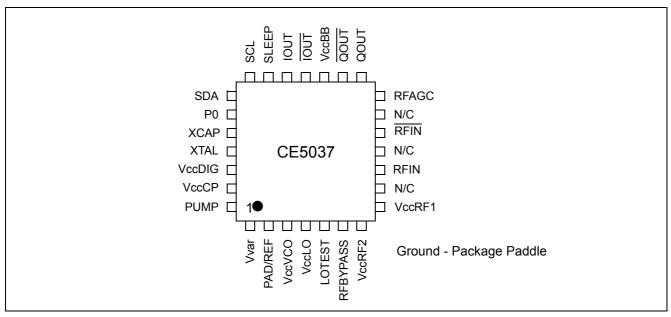

Figure 2 - Pin Diagram

| Pin # | Name     | Description                                | Pin # | Name   | Description                      |

|-------|----------|--------------------------------------------|-------|--------|----------------------------------|

| 1     | Vvar     | LO Tuning Voltage                          | 15    | QOUT   | Q Channel baseband output        |

| 2     | PAD/REF  | Vvar Reference Ground<br>/ Continuity Test | 16    | QOUT   | Q Channel baseband output        |

| 3     | VccVCO   | VCO Supply                                 | 17    | VccBB  | Baseband Supply                  |

| 4     | VccLO    | LO Supply                                  | 18    | IOUT   | I Channel baseband output        |

| 5     | LOTEST   | LO Test pin - do not connect               | 19    | IOUT   | I Channel baseband output        |

| 6     | RFBYPASS | RF Bypass output                           | 20    | SLEEP  | Hardware power down input        |

| 7     | VccRF2   | RF Supply                                  | 21    | SCL    | I <sup>2</sup> C Clock           |

| 8     | VccRF1   | RF Supply                                  | 22    | SDA    | I <sup>2</sup> C Data            |

| 9     | N/C      | Not connected                              | 23    | P0     | General purpose switching output |

| 10    | RFIN     | RF Input                                   | 24    | XCAP   | Crystal oscillator feedback      |

| 11    | N/C      | Not connected                              | 25    | XTAL   | Crystal oscillator crystal input |

| 12    | RFIN     | RF Complementary Input                     | 26    | VccDIG | Digital Supply                   |

| 13    | N/C      | Not connected                              | 27    | VccCP  | Varactor Tuning Supply           |

| 14    | RFAGC    | RF Gain control input                      | 28    | PUMP   | PLL charge pump output           |

#### Table 1 - Pin Names

Note: Ground contact is via underside of package. Pin 2 is connected to ground internally.

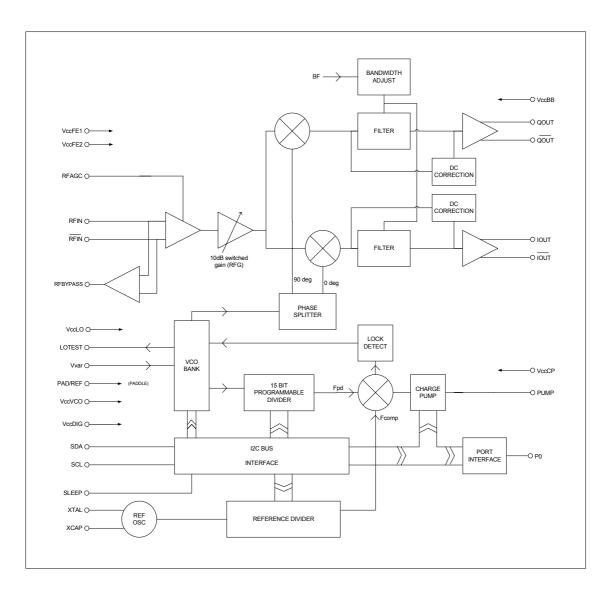

Figure 3 - Detailed Block Diagram

## **1.0 Circuit Description**

## 1.1 Functional Description

The CE5037 is a single chip wide band direct conversion tuner with integral RF bypass optimised for digital satellite receiver systems. It provides excellent signal handling capability in the presence of high composite signal levels.

The device offers a highly integrated solution for a satellite tuner incorporating a low phase noise PLL frequency synthesizer, the quadrature down converter, a fully integrated local oscillator, and programmable baseband channel filters. A minimal number of additional peripheral components are required. The crystal reference source can be also used as the reference for the demodulator.

An I<sup>2</sup>C compatible bus interface controls all of the tuner functionality.

The CE5037 contains both hardware and software power down modes.

## 1.2 Signal Path

#### 1.2.1 RF Input

The tuner RF input signal at a frequency of 950 – 2150 MHz is fed to the CE5037 RF input pre-amplifier stage.

The signal handling is designed such that no tracking filter is required to offer immunity to input signal composite overload.

The RF input amplifier feeds an AGC stage, which provides RF gain control. There is additional gain adjustment in the baseband section. The total AGC gain range will guarantee an operating dynamic range of –92 to –10 dBm.

The RF AGC in the CE5037 is divided into two stages. The first stage is a continually variable gain control stage, and provides the main system AGC set under control of the analogue AGC signal generated by the demodulator section. The second stage is a programmable gain stage to reduce RF gain by 10 dB. This would normally be used when an external LNA is being used to improve system sensitivity.

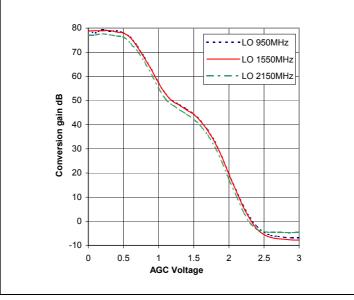

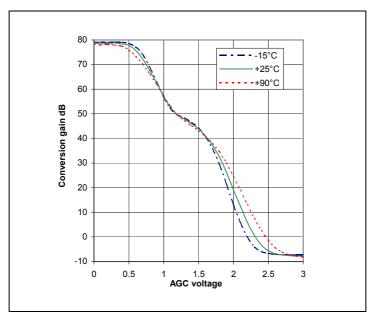

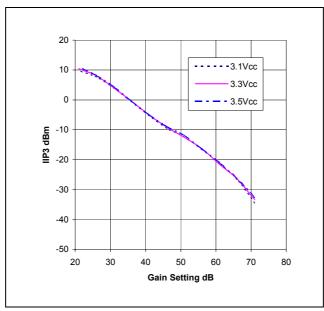

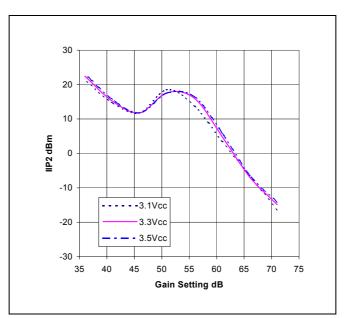

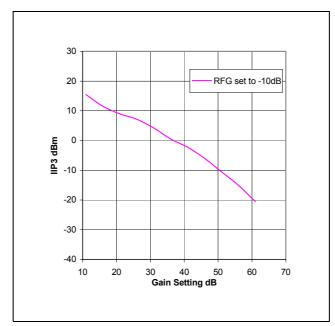

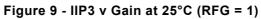

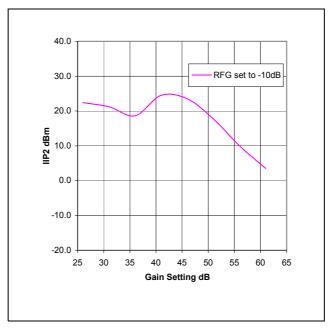

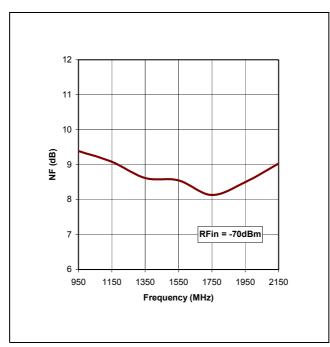

The analogue RF AGC is optimised for S/N and S/I performance across the full dynamic range. Typical RF AGC characteristic and variation of IIP3, IIP2 and NF are shown in Section 8 - Typical Performance Curves.

The output of the AGC stage is coupled to the quadrature mixer where the RF signal is mixed with quadrature local oscillator signals generated by the on-board local oscillator.

#### 1.2.2 Baseband

The outputs of the quadrature down converter are passed through the baseband filters followed by a programmable baseband gain stage.

The baseband paths are DC coupled. An integrated DC correction loop prevents saturation due to local oscillator self-mixing in the converter section. No external components are required for dc correction.

The baseband filters are 5<sup>th</sup> order Chebychev and provide excellent matching in both amplitude and phase between the I and Q channels. The filters are fully programmable for 3 dB bandwidths from 6 MHz to 43 MHz. The recommended filter bandwidth is related to the required symbol rate by the following equation.

$$-3dBFilterBandwidth \ fc = \frac{SymbolRate \times 1.35}{2 \times 0.8}$$

vww.DataSheet4U.com

This equation makes no allowance for LNB tuning offset at low symbol rates < 10 MS/s.

The baseband filter uses an automatic tuning algorithm to calibrate the filter bandwidth to the programmed requirement. This removes any variation due to operating conditions and process variations. The automatic tuning algorithm uses a frequency locked loop, which locks the filter bandwidth to a reference frequency derived from the crystal reference input frequency. Further details are provided in the programming section.

The filters are followed by a programmable gain stage. This provides twelve 1.5 dB gain steps. These can be used for optimising performance at different symbol rates and for adjusting the output level in applications not using CE6313.

The differential outputs of each channel stage are designed for low impedance drive capability and low intermodulation. The device can also be used in single-ended applications with unused outputs.

## 1.2.3 RF Bypass

The CE5037 provides a single ended bypass function, which can be used for driving a second receiver module. The electrical characteristics of the RF input are unchanged whether the RF bypass is enabled or disabled.

The RF Bypass powers up in the enabled state and can also operate with the remainder of the device in power down modes.

## 1.3 Local Oscillator Generation

## 1.3.1 On Chip VCO

The local oscillator on the CE5037 is fully integrated. It consists of three independently selectable oscillator stages with sub bands. The three oscillators and sub-bands are designed to provide optimum phase noise performance over the required tuning range of 950 to 2150 MHz, over operating conditions and process variations.

The local oscillators operate at a harmonic of the required local oscillator frequency and are divided down to the required LO frequency. The required divider ratio is automatically selected by the local oscillator control logic.

The oscillators are fully controlled by an on-chip automatic tuning algorithm. The user simply programs the required LO frequency. The control logic automatically selects the required VCO and sub band to give optimum performance. VCO settling time is minimized as different tuning algorithms are used, depending on the magnitude of the LO frequency change required. This choice of algorithm is also automatic and does not require user intervention.

The oscillator control logic tracks any changes in operating conditions and will retune the VCO if necessary, however hysteresis is built into this function to avoid unnecessary switching.

All oscillator components are included on the chip including the VCO varactor. An external loop filter is required as part of the PLL frequency synthesizer.

#### 1.3.2 PLL Frequency Synthesizer

The fully integrated PLL frequency synthesizer section controls the LO frequency. The only external requirements are crystal reference and simple second order loop filter. The PLL can be operated up to comparison frequencies of 2 MHz enabling a wide loop bandwidth for maximizing the close in phase noise performance.

The local oscillator input signal is multiplexed from the active oscillator to an internal preamplifier, which provides gain and reverse isolation from the divider signals. The output of the preamplifier provides the input to a 15-bit fully programmable divider with MN+A architecture incorporating a dual modulus 16/17 prescaler.

The output of the programmable divider is fed to the phase comparator where it is compared in both phase and frequency domain with the comparison frequency. This frequency is derived either from the on-board crystal controlled oscillator or from an external reference source. In both cases the reference frequency is divided down to the comparison frequency by the reference divider, which is programmable into 1 of 15 ratios.

The output of the phase detector feeds a charge pump which combined with an external loop filter integrates the current pulses to control the varactor voltage. The charge pump current is automatically varied by the VCO control logic to compensate for VCO gain variations that are dependent on selected sub band. The varactor control voltage is externally coupled to the oscillator section through the input pin Vvar.

# 1.4 I<sup>2</sup>C Interface

All programming for the CE5037 is controlled by an  $I^2C$  data bus and is compatible with 3V3 standard mode formats.

Data and Clock are fed in on the SDA and SCL lines respectively as defined by  $I^2C$  bus format. The device can either accept data (write mode), or send data (read mode). The LSB of the address byte (R/W) sets the device into write mode if it is logic '0', and read mode if it is logic '1'. The  $I^2C$  address is fixed at C0 (Write)/C1(Read) in hex format.

The CE5037 contains 16 control registers. These registers are read/write registers. These registers are addressed as sub-addresses on the I<sup>2</sup>C bus. Registers can be addressed as random access single write/read or random access sequential write and read as shown below.

#### Random Access Single Write

| Stop | Start | Device<br>Address | W | A | Register<br>Address | A | Register<br>Data | A | Stop |

|------|-------|-------------------|---|---|---------------------|---|------------------|---|------|

|      |       |                   |   |   | N                   |   | N                |   |      |

#### Random Access Sequential Write

| Stop | Start | Device<br>Address | W | A | Register<br>Address<br>N | A | Register<br>Data<br>N | A | Register<br>Data<br>N+1 |  | Register<br>Data<br>N+M | A | Stop |  |

|------|-------|-------------------|---|---|--------------------------|---|-----------------------|---|-------------------------|--|-------------------------|---|------|--|

|------|-------|-------------------|---|---|--------------------------|---|-----------------------|---|-------------------------|--|-------------------------|---|------|--|

#### **Random Access Single Read**

|  |  | Stop | Start | Device<br>Address | W | A | Register<br>Address | A | Start | Device<br>Address | R | A | Register<br>Data<br>N | N | Stop |

|--|--|------|-------|-------------------|---|---|---------------------|---|-------|-------------------|---|---|-----------------------|---|------|

|--|--|------|-------|-------------------|---|---|---------------------|---|-------|-------------------|---|---|-----------------------|---|------|

#### Random Access Sequential Read

| Stop S | Start | Device<br>Address | W | A | Register<br>Address<br>N | A | Start | Device<br>Address | R | A | Register<br>Data<br>N | A |  | Register<br>Data<br>N+M | N | Stop |  |

|--------|-------|-------------------|---|---|--------------------------|---|-------|-------------------|---|---|-----------------------|---|--|-------------------------|---|------|--|

|--------|-------|-------------------|---|---|--------------------------|---|-------|-------------------|---|---|-----------------------|---|--|-------------------------|---|------|--|

W Write bit

#### A Acknowledge Bit

N Not Acknowledge

A SLEEP pin is provided. This powers down all sections of the chip including the crystal oscillator and  $I^2C$  interface. The RF bypass function will be operational in this mode providing it has been previously enabled through the  $I^2C$  interface.

## 2.0 Register Map and Programming

The register map is arranged as 16 byte-wide read/write registers grouped by functional block. The registers may be written to and read-back from either sequentially (for lowest overhead) or specifically (for maximum flexibility).

A significant number of bits are used for test and evaluation purposes only and are fixed at logic '0' or '1'. The correct programming for these test bits is shown in the table below. It is essential that these values are programmed for correct operation. When the contents of the registers are read back the value of some bits may have changed from their programmed value. This is due to the internal automatic control which can update registers. Any changes can be ignored.

Read only bits are marked with an asterisk (\*). Any data written to these bits will be ignored.

Registers are set to default settings on applying power. These conditions are shown below and in the applicable tables.

| Register | Block            |                |                 |                 | Fund            | ction           |                 |                |                |

|----------|------------------|----------------|-----------------|-----------------|-----------------|-----------------|-----------------|----------------|----------------|

| 0        | PLL              | PLF            | 2 <sup>14</sup> | 2 <sup>13</sup> | 2 <sup>12</sup> | 2 <sup>11</sup> | 2 <sup>10</sup> | 2 <sup>9</sup> | 2 <sup>8</sup> |

| 1        | PLL              | 2 <sup>7</sup> | 2 <sup>6</sup>  | 2 <sup>5</sup>  | 2 <sup>4</sup>  | 2 <sup>3</sup>  | 2 <sup>2</sup>  | 2 <sup>1</sup> | 2 <sup>0</sup> |

| 2        | PLL              | 0              | 0               | C1              | C0              | R3              | R2              | R1             | R0             |

| 3        | PLL              | X*             | 1               | 0               | 0               | 0               | 0               | 0              | 0              |

| 4        | RF Front End     | X*             | 1               | 1               | 0               | 1               | 1               | LEN            | RFG            |

| 5        | Base Band        | BF7            | BF6             | BF5             | BF4             | BF3             | BF2             | BF1            | BF0            |

| 6        | Base Band        | 0              | LF              | SF              | BR4             | BR3             | BR2             | BR1            | BR0            |

| 7        | Base Band        | BLF*           | BG3             | BG2             | BG1             | BG0             | 0               | 0              | 0              |

| 8        | Local Oscillator | FLF*           | 0               | 1               | 0               | 0               | 0               | 0              | 0              |

| 9        | Local Oscillator | 1              | 0               | 1               | 0               | 0               | 0               | 1              | 0              |

| А        | Local Oscillator | 1              | 1               | 1               | 1               | 0               | 0               | 0              | 1              |

| В        | Local Oscillator | Х*             | Х*              | 1               | 1               | 1               | 0               | 0              | 0              |

| С        | Local Oscillator | 1              | 1               | 0               | 1               | 0               | 0               | 0              | 0              |

| D        | Local Oscillator | X*             | Х*              | Х*              | 1               | 0               | 0               | 0              | 0              |

| E        | Local Oscillator | X*             | X*              | 1               | 1               | 0               | 0               | 0              | 0              |

| F        | General          | PD             | CLR             | P0              | 0               | Х*              | Х*              | Х*             | Х*             |

Table 2 - Register Map

X\* denotes a read only test bit

## 2.1 PLL Registers

There are four registers that control the PLL:

| Bit Field | Name                | Default | Туре | Description                     |

|-----------|---------------------|---------|------|---------------------------------|

| 7         | PLF                 | -       | R    | PLL Lock Flag                   |

| 6:0       | 2 <sup>[14:8]</sup> | 0       | R/W  | MSB bits of LO Divider register |

#### Table 3 - Register 0

The PLF bit is the PLL lock detect circuit output. The PLF bit is set after 64 consecutive comparison cycles in lock. A chip-wide reset initializes the lock detect output to 0.

The 2[<sup>14:8</sup>] bits are the MSB bits of the LO Divider divide value.

| 7:0     2 <sup>[7:0]</sup> 0     R/W     LSB bits of LO Divider register | ſ | Bit Field | Name               | Default | Туре | Description                     |

|--------------------------------------------------------------------------|---|-----------|--------------------|---------|------|---------------------------------|

|                                                                          |   | 7:0       | 2 <sup>[7:0]</sup> | 0       | R/W  | LSB bits of LO Divider register |

#### Table 4 - Register 1

The 2[<sup>7:0</sup>] bits are the LSB bits of the LO Divider divide value. The division ratio of the LO divider is fully programmable to integer values within the range of 240 to 32767.

**Note** that when the LO Divider divide value is to be changed, the new value is not actually presented to the LO Divider until all of the 15-bit control word  $2[^{14:0}]$  has been programmed. Register 0 and 1 must be therefore be programmed (in any order) before the LO divider is updated even if the only data change is in one of the registers.

| Bit Field | Name   | Default | Туре | Description             |

|-----------|--------|---------|------|-------------------------|

| 7:6       | -      | 0       | R/W  | Test modes              |

| 5:4       | C[1:0] | 0       | R/W  | Charge pump current     |

| 3:0       | R[3:0] | 0       | R/W  | Reference divider ratio |

#### Table 5 - Register 2

The C[1:0] bits set the programmed charge pump current

| C[1] | C[0] | Тур  | Units |

|------|------|------|-------|

| 0    | 0    | 400  | uA    |

| 0    | 1    | 550  | uA    |

| 1    | 0    | 750  | uA    |

| 1    | 1    | 1000 | uA    |

#### Table 6 - Charge Pump Currents

The charge pump current is automatically increased to the next setting dependent on the VCO sub band that has been selected by the VCO tuning algorithm. This is to compensate for changes in VCO gain and so provide <sup>ww</sup> consistent PLL performance across all sub bands. Programming the highest charge pump value will not allow the value to be incremented, therefore this value should not be programmed.

The value read back for the charge pump current is the actual value in use for the selected sub band.

| R3 | R2 | R1 | R0 | Division<br>Ratio |

|----|----|----|----|-------------------|

| 0  | 0  | 0  | 0  | 2                 |

| 0  | 0  | 0  | 1  | 4                 |

| 0  | 0  | 1  | 0  | 8                 |

| 0  | 0  | 1  | 1  | 16                |

| 0  | 1  | 0  | 0  | 32                |

| 0  | 1  | 0  | 1  | 64                |

| 0  | 1  | 1  | 0  | 128               |

| 0  | 1  | 1  | 1  | 256               |

| 1  | 0  | 0  | 0  | 3                 |

| 1  | 0  | 0  | 1  | 5                 |

| 1  | 0  | 1  | 0  | 10                |

| 1  | 0  | 1  | 1  | 20                |

| 1  | 1  | 0  | 0  | 40                |

| 1  | 1  | 0  | 1  | 80                |

| 1  | 1  | 1  | 0  | 160               |

| 1  | 1  | 1  | 1  | 320               |

The R[3:0] bits select the Reference Divider divide ratio. The ratio selected is not a simple binary power-of-two value but through a lookup table, see Table 7- PLL Reference Divider Ratios.

Table 7 - PLL Reference Divider Ratios

| Bit Field | Name | Default | Туре | Description |

|-----------|------|---------|------|-------------|

| 7:0       | -    | 0X40    | R/W  | Test Modes  |

#### Table 8 - Register 3

This register controls test modes within the PLL. This should be programmed with the default settings.

## 2.2 RF Control Register

A single register controls RF programmability.

|     | Bit Field        | Name | Default | Туре | Description    |

|-----|------------------|------|---------|------|----------------|

|     | 7                | -    | -       | R    | Test Modes     |

|     | 6:2              | -    | 11011   | R/W  | Test Modes     |

| vww | .DataSheet4U.con | LEN  | 1       | R/W  | Bypass Enable  |

|     | 0                | RFG  | 0       | R/W  | RF Gain Adjust |

#### Table 9 - Register 4

The LEN bit enables the RFBYPASS output. With this bit set, the RF Bypass is active even if 'software' or 'hardware' power down has been selected.

The RFG bit controls the gain of the second section of RF gain control. With this bit set, the RF gain is reduced by 10dB. This setting would normally used when an external LNA is being used.

## 2.3 Base Band Registers

There are three registers that control the Base Band:

| Bit Field | Name    | Default | Туре | Description                        |

|-----------|---------|---------|------|------------------------------------|

| 7:0       | BF[7:0] | 0X3C    | R/W  | Base Band Filter Cut-Off Frequency |

#### Table 10 - Register 5

The bits BF[7:0] control the bandwidth of the baseband filter. An automatic adjustment routine synchronizes the filter bandwidth to a reference frequency derived from the crystal.

| Bit Field | Name    | Default | Туре | Description                        |

|-----------|---------|---------|------|------------------------------------|

| 7         | -       | 0       | R/W  | Test Mode                          |

| 6         | LF      | 0       | R/W  | Baseband Filter Adjust Disable     |

| 5         | SF      | 0       | R/W  | Baseband Filter Adjust Disable     |

| 4:0       | BR[4:0] | 1000    | R/W  | Base Band Reference Division Ratio |

#### Table 11 - Register 6

The LF and SF bits disable the baseband filter adjustment. It is recommended that these bits are set after programming the filter bandwidth to prevent interactions within the circuit. These bits must be reset to enable the baseband filter bandwidth to be reprogrammed.

The BR[4:0] bits set the crystal reference divide ratio. This effectively determines the resolution setting of the baseband filters. The baseband filter settings (BF[7:0]) can be calculated from the following equation.

# $BF[7:0] = \frac{(Filter bandwidth(MHz)*5.088*BR[4:0])}{CrystalFrequency(MHz)} - 1$

See Section 3 Applications Information, for a typical programming example.

BR[4:0] = 0 is invalid

| Bit Field | Name    | Default | Туре | Description           |

|-----------|---------|---------|------|-----------------------|

| 7         | BLF     | -       | R    | Base Band Lock Flag   |

| 6:3       | BG[3:0] | 0111    | R/W  | Base Band Gain Select |

| 2:0       | -       | 000     | R/W  | Test Modes            |

#### Table 12 - Register 7

The BLF bit indicates that the baseband adjustment has completed and locked.

The control bits BG[3:0] define the gain of the Base Band post-filter amplifier. The following table shows the gain - note this is relative gain. The 1.5 dB gain steps enable the baseband output level to be adjusted and optimise gain distribution for different symbol rates.

| BG[3] | BG[2] | BG[1] | BG[0] | Gain (dB) |

|-------|-------|-------|-------|-----------|

| 0     | 0     | 0     | 0     | 0         |

| 0     | 0     | 0     | 1     | 1.5       |

| 0     | 0     | 1     | 0     | 3.0       |

| 0     | 0     | 1     | 1     | 4.5       |

| 0     | 1     | 0     | 0     | 6.0       |

| 0     | 1     | 0     | 1     | 7.5       |

| 0     | 1     | 1     | 0     | 9.0       |

| 0     | 1     | 1     | 1     | 10.5      |

| 1     | 0     | 0     | 0     | 12.0      |

| 1     | 0     | 0     | 1     | 13.5      |

| 1     | 0     | 1     | 0     | 15.0      |

| 1     | 0     | 1     | 1     | 16.5      |

Table 13 - BG[3:0] Control of Base Band Post Filter Gain

## 2.4 Local Oscillator Registers

There are seven registers that control the Local Oscillator: These are used primarily for test and evaluation by Intel Corporation. Although VCO's can be manually programmed, the user is recommended to use the default automatic settings as these provide optimum performance.

| Bit Field | Name | Default | Туре | Description    |

|-----------|------|---------|------|----------------|

| 7         | FLF  | -       | R    | Full Lock Flag |

| 6:0       | -    | 0X20    | R/W  | Test Modes     |

The FLF bit is the VCO tuning controller lock output and is set when PLL is locked and the automatic VCO tuning is optimised and complete.

Register 9 to Register E are for test modes only. It is however important that these registers are programmed with the values shown.

| Bit Field | Name | Default | Туре | Description |  |  |  |

|-----------|------|---------|------|-------------|--|--|--|

| 7:0       | -    | 0XA2    | R/W  | Test Modes  |  |  |  |

|           |      |         |      |             |  |  |  |

## Table 15 - Register 9

| Bit Field | Name | Default | Туре | Description |

|-----------|------|---------|------|-------------|

| 7:0       | -    | 0XF1    | R/W  | Test Modes  |

## Table 16 - Register A

| Bit Field | Name | Default | Туре | Description            |

|-----------|------|---------|------|------------------------|

| 7:6       | -    | -       | R    | Test Modes (read only) |

| 5:0       | -    | 0X38    | R/W  | Test Modes             |

#### Table 17 - Register B

| Bit Field | Name | Default | Туре | Description |

|-----------|------|---------|------|-------------|

| 7:0       | -    | 0XD0    | R/W  | Test Modes  |

## Table 18 - Register C

| Bit Field | Name | Default | Туре | Description            |

|-----------|------|---------|------|------------------------|

| 7:5       | -    | -       | R    | Test Modes (read only) |

| 4:0       | -    | 0X10    | R/W  | Test Modes             |

## Table 19 - Register D

| Bit Field | Name | Default | Туре | Description            |

|-----------|------|---------|------|------------------------|

| 7:6       | -    | -       | R    | Test Modes (read only) |

| 5:0       | -    | 0X30    | R/W  | Test Modes             |

Table 20 - Register E

#### 2.5 General Control Register

This register controls powerdown and general control functions:

| Bit Field | Name | Default | Туре | Description            |

|-----------|------|---------|------|------------------------|

| 7         | PD   | 1       | R/W  | Power Down             |

| 6         | CLR  | 0       | R/W  | Clear and reset logic  |

| 5         | P0   | 0       | R/W  | Port 0 control         |

| 4         | -    | 0       | R/W  | Test Mode              |

| 3:0       | -    | -       | R    | Test Modes (Read only) |

#### Table 21 - Register F

The PD bit is the 'software' power down control. When this bit is set to 1, all the analogue blocks are powered down with the exception of the Crystal Oscillator. The I<sup>2</sup>C interface will remain active and can still be used to enable the RF Bypass.

Setting the SLEEP input pin high also invokes 'software' power down with the addition of powering down the Crystal Oscillator to produce 'hardware' power down. The RF Bypass will remain active if it has been previously programmed on the I<sup>2</sup>C bus. Note that in 'hardware' power down, the I<sup>2</sup>C interface does not operate.

The CLR bit re-triggers the power-on-reset function. This resets all register values to their power-on reset default value. The CLR bit is itself cleared. Note that the chip-wide reset will reset the  $I^2C$  Interface and the current write sequence used to set this bit will not be acknowledged.

The P0 bit controls the state of the output port according to Table 22.

| P0 | Output Port State   |  |  |  |

|----|---------------------|--|--|--|

| 0  | Off, high impedance |  |  |  |

| 1  | On, current sinking |  |  |  |

Table 22 - Output Port States

## Data Sheet

# 3.0 Applications Information

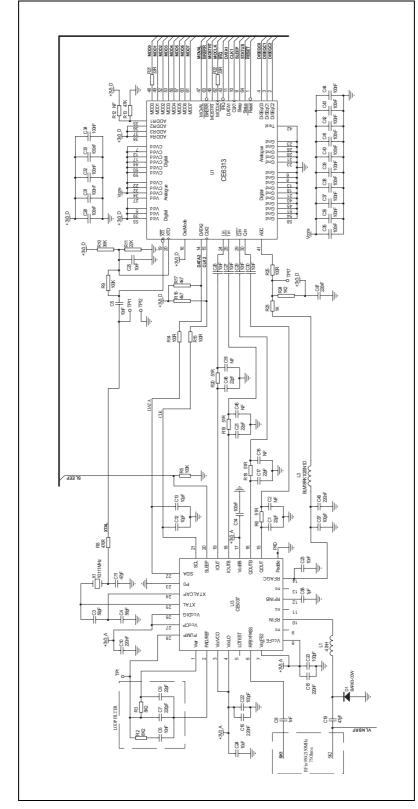

Figure 4 - Typical Application with CE6313 Demodulator

#### 3.1 General Design Guidelines

Figure 4 shows a typical application using a CE6313 as a demodulator. This is available as a reference design (CE9542) from Intel Corporation.

The design uses a standard two layer board. All components are mounted on the upper surface with the lower surface as a ground plane. The RF input requires a coupling capacitor and series inductor for optimum matching. The RF bypass output requires a coupling capacitor. Good decoupling should be used - these components should be mounted as close to the device as practicable.

All ground contact to the CE5037 is to the ground 'paddle' on the underside of the package. This must be soldered fully to the board to achieve best thermal and electrical contact. It is recommended that an array of vias (4 x 4) is used to achieve good contact to the ground plane underneath the device

A common crystal reference can be used for the tuner and demodulator. The crystal oscillator capacitors are optimised for a 10.111 MHz reference.

Sensitivity is optimised by minimizing interaction from digital signal activity in the demodulator. This is achieved by filtering in the agc control, and filter networks in the baseband I and Q signals between the demodulator and CE5037. These networks should be mounted as close to the CE5037 as possible.

| Parameter                                                                     | Тур.                 | Units                | Notes                                         |

|-------------------------------------------------------------------------------|----------------------|----------------------|-----------------------------------------------|

| Sensitivity                                                                   | -83                  | dBm                  | QEF 27.5MS/s rate 7/8<br>No added noise       |

| C/N 27.5MS/s rate 7/8<br>2e-4 post Viterbi BER                                | 8.3<br>8.1<br>8.1    | dB<br>dB<br>dB       | Input = -69 dBm<br>-45 dBm<br>-23 dBm         |

| C/N 2MS/s rate 7/8<br>2e-4 post Viterbi BER                                   | 8.2<br>8.0<br>8.0    | dB<br>dB<br>dB       | Input = -81dBm<br>-45 dBm<br>-23 dBm          |

| Interference Rejection Ratio<br>27.5 MS/s rate 7/8.<br>Interferers at -25 dBm | 32<br>35<br>45<br>35 | dB<br>dB<br>dB<br>dB | N+1<br>N+4<br>N+10<br>2 Interferers at -25dBm |

The typical performance from the reference design is shown in the table below:

Table 23 - Typical Performance using CE5037 and CE6313

Further information is provided in CE9542 user guides.

The CE5037 can also be used with other demodulators. If the demodulator has a single-ended input then the CE5037 can be used with a single-ended outputs ie IOUT and QOUT. The unused outputs should be loaded with an equivalent load to the demodulator input to maintain a good balanced configuration. The optimum output level for the demodulator can be achieved by adjusting the post filter baseband gain.

## 3.2 DVB-S2 Applications

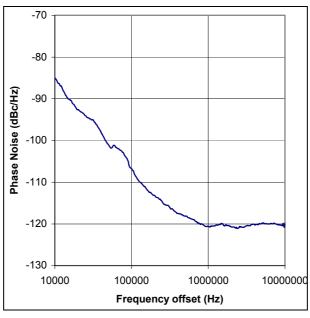

The excellent performance of the CE5037 makes the device also suitable for the higher level modulation schemes (8PSK) used for DVB-S2. In the critical areas of quadrature accuracy and phase noise, typical performance is shown in the following table.

| Parameter                           | Value     | Notes                                         |

|-------------------------------------|-----------|-----------------------------------------------|

| Quadrature Amplitude Matching       | < 0.5 dB  | Filter bandwidth = 26.5 MHz                   |

| Quadrature Phase Matching           | < 2 °     |                                               |

| Integrated Phase Noise LO = 950MHz  | 0.40 °rms | PLL Loop Bandwidth = 10kHz                    |

| Integrated Phase Noise LO = 1500MHz | 0.62 °rms | Phase noise integrated over<br>1kHz to 10 MHz |

| Integrated Phase Noise LO = 2150MHz | 0.83 °rms | 1kHz to 10 MHz                                |

Table 24 - Typical Performance for DVB-S2 Applications

#### 3.3 Baseband Filter Bandwidth Calculation

The bandwidth of the baseband filter is given by the following expression:

$$fbw = \frac{fxtal}{BR x 5.088} x (BF + 1)$$

Equation 1

where:

fbw=the filter bandwidth in MHz within the range 8 MHz to 43 MHz.fxtal=crystal oscillator frequency in MHz.BR=decimal value of the bits BR[4:0], range 1-31.

(BR = 0 is not allowed)

BF = decimal value of the register bits BF[7:0], range 0 - 255.

The above equation can be re-arranged as follows

$BF = \left[fbw \ x \ 5.088 \ x \ \frac{BR}{fxtal}\right] - 1 \quad Equation \ 2$

It is recommended that BR should be set so that  $\frac{fxtal}{BR}$  is approximately 1 MHz

This sets the bandwidth resolution to approximately 200kHz

The value of BF can now be calculated from Equation 2 and rounded to the nearest integer:

Example

Conditions: fxtal = 10.111 MHz, fbw = 26.5 MHz

Choose BR = 10

$$\mathsf{BF} = \frac{26.5 \times 5.088 \times 10}{10.111} - 1 = 132.35$$

BF = 132

The actual filter bandwidth is therefore given by:

$$fbw = \frac{101111}{10} x (132 + 1) x \frac{1}{5.088} = 26.43 \text{ MHz}$$

# 4.0 Pin Descriptions

| Pin#     | Name         | Description                                                                                                                                                   | Schematic                      |

|----------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| 1        | Vvar         | LO voltage tuning input.                                                                                                                                      | Vvar 100<br>Components per VCO |

| 2        | PAD/REF      | Bonded to paddle. Production<br>continuity test for paddle soldering<br>and also ground reference for loop<br>filter.                                         |                                |

| 3        | VccVCO       | +3.3 V voltage supply for VCO's.                                                                                                                              |                                |

| 4        | VccLO        | +3.3 V voltage supply for LO circuits.                                                                                                                        |                                |

| 5        | LOTEST       | For Intel testing only.<br>Must not connect.                                                                                                                  |                                |

| 6        | RFBYPASS     | RF bypass output. AC couple.<br>Matching circuitry as shown in<br>applications diagram.<br>Do not connect in applications where<br>RF bypass is not required. | Vcc<br>RFBYPASS                |

| 7        | VccRF2       | +3.3 V voltage supply for RF.                                                                                                                                 |                                |

| 8        | VccRF1       | +3.3 V voltage supply for RF.                                                                                                                                 |                                |

| 9        | N/C          | Not connected.                                                                                                                                                |                                |

| 10<br>12 | RFIN<br>RFIN | RF input. AC couple.<br>See applications diagram.                                                                                                             |                                |

| 11       | N/C          | Not connected.                                                                                                                                                | -                              |

|          | N/C          | Not connected.                                                                                                                                                |                                |

| Pin#     | Name         | Description                                                                                                                              | Schematic                                                            |

|----------|--------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 14       | RFAGC        | RF analog gain control input.                                                                                                            | Vref<br>10k<br>RFAGC 30k                                             |

| 15<br>16 | QOUT<br>QOUT | Q channel baseband differential<br>outputs.<br>AC couple as shown in application<br>diagram.                                             | Vcc<br>Output<br>Ucc<br>Ucc<br>Ucc<br>Ucc<br>Ucc<br>Ucc<br>Ucc<br>Uc |

| 17       | VccBB        | +3.3 V voltage supply for Baseband.                                                                                                      |                                                                      |

| 18<br>19 | IOUT<br>IOUT | I channel baseband differential<br>outputs.<br>AC couple as shown in application<br>diagram.                                             | Same as pin 15,16                                                    |

| 20       | SLEEP        | Hardware power down input.<br>Logic '0' normal mode.<br>Logic '1' - analog sections are<br>powered down including crystal<br>oscillator. | SLEEP<br>CMOS Digital input                                          |

| 21       | SCL          | I <sup>2</sup> C serial clock input                                                                                                      | SCL<br>CMOS Digital input                                            |

| Pin#     | Name         | Description                                                                                                                                                                                   | Schematic                               |

|----------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| 22       | SDA          | I <sup>2</sup> C serial data input/output                                                                                                                                                     | SDA<br>SDA<br>CMOS Digital input/output |

| 23       | P0           | Switching port output.<br>Open Drain<br>'0' = disabled (high impedance)<br>'1' = enabled.                                                                                                     | P0<br>CMOS Digital output               |

| 24<br>25 | XCAP<br>XTAL | Reference oscillator crystal inputs.<br>XTAL pin can be used for external<br>reference via 10nF capacitor.<br>See applications diagram for<br>recommended external components<br>(10.111 MHz) | Vcc<br>100 XTAL<br>XCAP<br>0.2 mA       |

| 26       | VccDIG       | +3.3 V voltage supply for digital logic.                                                                                                                                                      |                                         |

| 27       | VccCP        | +3.3 V voltage supply for varactor tuning.                                                                                                                                                    |                                         |

| 28       | PUMP         | Charge pump output.                                                                                                                                                                           |                                         |

# 5.0 Absolute Maximum Ratings

| Parameter                                   | Min. | Max.      | Units | Notes                                        |

|---------------------------------------------|------|-----------|-------|----------------------------------------------|

| Maximum voltage on any Vcc pin              | -0.3 | 3.6       | V     |                                              |

| Maximum voltage between<br>any two Vcc pins |      | 0.3       | V     |                                              |

| Maximum voltage on any other pin            | -0.3 | Vcc + 0.3 | V     | The voltage on any pin must not exceed 3.6 V |

| Maximum voltage between<br>RFIN and RFIN    | -1   | 1         | V     |                                              |

| P0 Output current                           |      | 20        | mA    |                                              |

| Maximum RF Input                            |      | 10        | dBm   |                                              |

| Storage temperature                         | -55  | 150       | °C    |                                              |

| Junction temperature                        |      | 125       | °C    |                                              |

| Package thermal resistance                  |      | 34        | °C/W  | Package ground paddle soldered to ground     |

| ESD Protection - all pins<br>except 10,12   |      | 1.75      | kV    | Mil std 883B method 3015<br>cat1             |

| ESD Protection - pins 10,12<br>RFIN, RFIN   |      | 0.75      | kV    | Mil std 883B method 3015<br>cat1             |

# 6.0 Operating Conditions

| Parameter                | Min. | Max. | Units    | Notes |

|--------------------------|------|------|----------|-------|

| Supply Voltage           | 3.15 | 3.45 | V        |       |

| Operating Temperature    | -10  | +85  | °C       |       |

| RF Input Frequency       | 950  | 2150 | MHz      |       |

| Baseband I/Q Output load | 4.7  | 15   | kΩ<br>pF |       |

# 7.0 Electrical Characteristics

Test conditions (unless otherwise stated)

$T_{amb}$  = 25°C, Vee= 0V, All Vcc supplies = 3.3 V+-5%

Baseband Gain = 9 dB, RFG = 0

Baseband filter bandwidth 26.5 MHz

All power levels are referred to 75  $\Omega$  (0 dBm = 109 dB $\mu$ V) Specifications refer to total cascaded system of converter/AGC stage and baseband amplifier/filter stage.

Output amplitude of 0.5 Vp-p differential.

| Characteristic          | Min. | Тур. | Max. | Units | Conditions                               |

|-------------------------|------|------|------|-------|------------------------------------------|

| Supply Current          |      |      |      |       | Outputs unloaded. Max Filter bandwidth   |

|                         |      | 145  | 200  | mA    | RF Bypass disabled                       |

|                         |      | 155  | 215  | mA    | RF Bypass enabled                        |

| Hardware Power Down     |      | 0.2  |      | mA    |                                          |

| Software Power Down     |      | 1.7  | 3    | mA    | No RF input.                             |

|                         |      |      |      |       | Crystal oscillator remains operational   |

| System                  |      |      |      |       |                                          |

| Input Return Loss       |      | 9    |      | dB    | Zo = 75 $\Omega$ with external matching. |

|                         |      |      |      |       | Bypass enabled or disabled               |

| Noise Figure DSB        |      | 8    | 10   | dB    | At max gain                              |

|                         |      | 8.5  | 10   | dB    | At -70 dBm operating level               |

|                         |      |      | 13   | dB    | At -60 dBm operating level               |

| Variation in NF with RF |      |      | -1   | dB/dB | Above -60dBm operating level             |

| gain adjust             |      |      |      |       |                                          |

| Operating dynamic range |      | -92  | -10  | dBm   | 1MS/s                                    |

| Operating dynamic range |      | -84  | -10  | dBm   | 27.5MS/s                                 |

| Conversion Gain         |      |      |      |       |                                          |

| Max                     | 72   | 78   |      | dB    | RFagc = 0.2V                             |

| Min                     |      | -6   | 10   | dB    | RFagc = 2.8V                             |

| AGC Control Range       | 68   | 72   |      | dB    | AGC monotonic for RFagc from Vee to      |

|                         |      |      |      |       | Vcc                                      |

| RFAGC input current     | -150 |      | 150  | μA    | Vee <= RFagc<= Vcc                       |

|                         |      |      |      |       |                                          |

| System IM2              |      |      | -28  | dBc   | Baseband defined, note 1                 |

|                         |      |      | -40  | dBc   | RF front-end defined, note 2             |

| System IM3              |      |      | -24  | dBc   | Note 3                                   |

| .DataSheet4U.com        |      |      | -30  | dBc   | Note 4                                   |

| IIP2                    | 15   | 22   |      | dBm   | At -40 dBm input, note 2                 |

| IIP3                    | 5    | 13   |      | dBm   | At -25 dBm input, note 3                 |

Data Sheet

| Characteristic                                    | Min.     | Тур. | Max.               | Units                      | Conditions                                                        |

|---------------------------------------------------|----------|------|--------------------|----------------------------|-------------------------------------------------------------------|

| LO second harmonic<br>interference level          |          |      | -35                | dBc                        | Note 5, all gain settings                                         |

| LNA second harmonic<br>interference level         |          |      | -20                | dBc                        | Note 6                                                            |

| Quadrature gain match                             | -1       |      | 1                  | dB                         | 1.5 to 18 MHz                                                     |

| Quadrature phase match                            | -3<br>-5 |      | 3<br>5             | deg<br>deg                 | Baseband Signal = 1.5 MHz<br>Baseband Signal = 18 MHz             |

| I & Q channel in band ripple                      |          |      | 1                  | dB                         | 1.5 to 18 MHz                                                     |

| LO reference sideband spur level on I & Q outputs |          |      | -40                | dBc                        | synthesizer phase detector comparison<br>frequency 500 - 2000 kHz |

| In band local oscillator leakage to RF input      |          |      | -65<br>-55         | dBm<br>dBm                 | 950 - 2150 MHz<br>30 - 950 MHz                                    |

| Channel lock time                                 |          |      | 50                 | ms                         | Worst case channels                                               |

| Local Oscillator                                  |          |      |                    |                            |                                                                   |

| VCO Gain                                          |          | 27   |                    | MHz/V                      | LO = 2 GHz. Note 7                                                |

| SSB Phase Noise                                   |          | -83  | -76<br>-96<br>-110 | dBc/Hz<br>dBc/Hz<br>dBc/Hz | 10 kHz offset<br>100 kHz offset<br>1 MHz offset                   |

| Phase Noise floor                                 |          |      | -132               | dBc/Hz                     |                                                                   |

| Integrated phase jitter                           |          |      | 3                  | deg                        | 10 kHz to 15 MHz                                                  |

| Varactor input current                            | -10      |      | 10                 | nA                         | Vvar = 0.5 to 1.3 V                                               |

| Baseband Filters                                  |          |      |                    |                            |                                                                   |

| Bandwidth                                         | 6        |      | 43                 | MHz                        | Max specified load                                                |

| Bandwidth Tolerance                               | -1       |      | +1                 | MHz                        | All bandwidth settings                                            |

| Time to change filter bandwidth                   |          |      | 10                 | ms                         |                                                                   |

| Total Harmonic Distortion                         |          |      | -30                | dBc                        | 1 Vpp differential output at 43 MHz filter bandwidth              |

| RF Bypass                                         |          |      |                    |                            | Output load = 75 ohms                                             |

| Gain                                              | -2       | 1.5  | 4                  | dB                         |                                                                   |

| Noise Figure                                      |          | 8.5  | 10                 | dB                         |                                                                   |

| OPIP3                                             |          | 9    |                    | dB                         | Note 8                                                            |

| OPIP2                                             | 20       |      |                    | dBm                        | Note 9                                                            |

| Output return loss                                | 9        |      |                    | dB                         |                                                                   |

| Forward Isolation                                 |          | 30   |                    | dB                         | 950-2150 MHz. Bypass disabled                                     |

| Characteristic                                                                     | Min.                     | Тур.                      | Max.                       | Units                | Conditions                                   |

|------------------------------------------------------------------------------------|--------------------------|---------------------------|----------------------------|----------------------|----------------------------------------------|

| Reverse Isolation                                                                  |                          | 30                        |                            | dB                   | 950-2150 MHz. Bypass enabled or disabled     |

| In band LO leakage                                                                 |                          |                           | -65                        | dBm                  | 950-2150 MHz. Bypass enabled or disabled     |

| synthesizer                                                                        |                          |                           |                            |                      |                                              |

| Charge Pump Current                                                                | 304<br>422<br>578<br>762 | 400<br>550<br>750<br>1000 | 552<br>759<br>1035<br>1380 | μΑ<br>μΑ<br>μΑ<br>μΑ |                                              |

| Charge Pump Matching                                                               |                          | 2                         |                            | %                    | Vpin = 0.5 to 1.3 V                          |

| Charge Pump Leakage                                                                | -10                      | +/-3                      | +10                        | nA                   | Vpin = 0.5 to 1.3 V                          |

| Charge Pump Compliance                                                             | 0.4                      |                           | Vcc<br>- 0.4               | V                    |                                              |

| Crystal Frequency                                                                  | 4                        |                           | 20                         | MHz                  |                                              |

| Recommended crystal series resistance                                              | 12                       | 25                        | 50                         | ohms                 | 10 MHz crystal                               |

| Crystal power dissipation                                                          |                          | 100                       | 500                        | μW                   | Note 10                                      |

| Crystal load capacitance                                                           |                          | 16                        |                            | pF                   | Note 10                                      |

| Crystal oscillator startup time                                                    |                          |                           | 10                         | ms                   |                                              |

| External reference input frequency                                                 | 4                        |                           | 20                         | MHz                  | ac coupled sinewave                          |

| External reference drive level                                                     | 0.5                      |                           | 2.0                        | Vpp                  | ac coupled sinewave                          |

| Phase detector<br>comparison frequency                                             | 0.5                      |                           | 2                          | MHz                  |                                              |

| Equivalent phase noise at phase detector                                           |                          | -148                      |                            | dBc/Hz               | 10 MHz crystal SSB within PLL loop bandwidth |

| Interface                                                                          |                          |                           |                            |                      |                                              |

| SDA, SCL<br>Input high voltage<br>Input low voltage<br>Hysteresis<br>Input current | 2.3<br>0<br>-10          | 0.4                       | 3.6<br>1<br>10             | ν<br>ν<br>μΑ         | Input = Vee to VccDIG +0.3 V                 |

| SDA Output Voltage                                                                 | 10                       |                           | 0.4                        | μA<br>V              | Isink = 3 mA                                 |

| SCL clock ratem                                                                    |                          |                           | 100                        | kHz                  |                                              |

| Characteristic                                         | Min.       | Тур. | Max.       | Units  | Conditions          |

|--------------------------------------------------------|------------|------|------------|--------|---------------------|

| External Port P0<br>Sink Current                       | 3          |      |            | mA     | Vo = 0.7 V          |

| Leakage Current                                        |            |      | 10         | μA     | Vo = Vcc            |

| SLEEP Input<br>Input high voltage<br>Input low voltage | 1.9<br>Vee |      | 3.6<br>1.0 | V<br>V |                     |

| Input Current                                          |            |      | 10         | μA     | Vin = Vee to VccDIG |

Note 1: AGC set to deliver an output of 0.5Vp-p with an input CW @ frequency fc of -30 dBm, undesired tones at fc+146 and fc+155 MHz @ -15 dBm, generating output IM spur at 9 MHz. Measured relative to unwanted signal.

Note 2: LO set to 2145 MHz and AGC set to deliver a 5 MHz output of 0.5Vp-p with an input CW @ frequency 2150 MHz of -40 dBm. Undesired tones at 1.05 and 1.1 GHz at -25 dBm generating IM spur at 5 MHz baseband. Measured relative to unwanted signal.

Note 3: AGC set to deliver an output of 0.5Vp-p with an input CW @ frequency fc of -30 dBm. Two undesired tones at fc+205 and fc+405 MHz at -12 dBm, generating output IM spur at 5 MHz.

Note 4: AGC set to deliver an output of 0.5Vp-p with an input CW @ frequency fc of -30 dBm. Two undesired tones at fc+55 and fc+105 MHz at -15 dBm, generating output IM spur at 5 MHz.

Note 5: The level of 2.01 GHz down converted to baseband relative to 1.01 GHz with the oscillator tuned to 1 GHz.

Note 6: The level of second harmonic of 1.01 GHz at -20dBm downconverted to baseband relative to 2.01 GHz desired signal at -35dBm with agc set to give 0.5Vp-p output. LO frequency = 2 GHz.

Note 7: Reference VCO gain value for loop filter calculations. Using this recommended value then takes into account VCO switching and automatic charge pump current variations.

Note 8: Two input tones at fc+50 and fc+100 MHz at -12 dBm, generating output IM product at fc.

Note 9: IM2 product from two input tones at 1.05 and 1.1 GHz at -16 dBm, generating IM product at 2150 MHz.

Note 10: Crystal specifications vary considerably and significantly effect the choice of external oscillator capacitor values. Each application may require separate consideration for optimum performance.

# 8.0 Typical Performance Data

Figure 5 - Gain v. RFAGC at 25°C

Figure 6 - Gain v RFAGC v. Temperature

Figure 7 - IIP3 v Gain at 25°C

Figure 8 - IIP2 v Gain at 25°C

Figure 10 - IIP2 v Gain at 25°C (RFG = 1

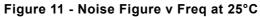

Figure 12 - Noise Figure v RFin v Temperature

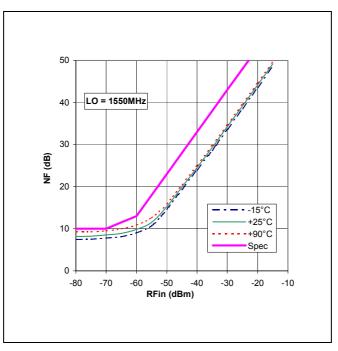

Figure 13 - LO Phase Noise at 25°C

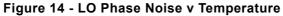

Figure 15 - RF Bypass Gain v Temperature

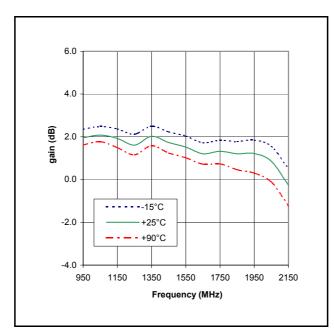

Figure 16 - Baseband Filter Response 26.5 MHz