# Features

- Four Independent Receivers

- OneTransmitter in A Mode

- Direct 6800 Microprocessor Interface

- 8-bit Data Bus

- ARINC Interface: "1" and "0" Lines, RZ Code

- Software Label Control in A Mode

- Parity Control: Odd or No Parity

- Interrupt Capability in A Mode

- Test Mode Capability

# Description

The EF4442 is a reception interface for 4 ARINC 429 channels.

Two models of operation are provided:

- When in A mode, the circuit can be considered as a peripheral of an EF 6800 or EF6802 microprocessor and is totally software programmable (for example, for test purposes).

- When in B mode, the parameters are hardware programmed. Reading the registers which contain messages is only possible (max. scan frequency: 2 MHz).

# **Screening Quality**

This product is manufactured in full compliance with either:

- NFC 96883 class G

- MIL-STD-883 class B

- According to Atmel standards

# **Application Note**

Ask for application note: "General application principles EF4442(RTA)"

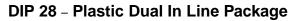

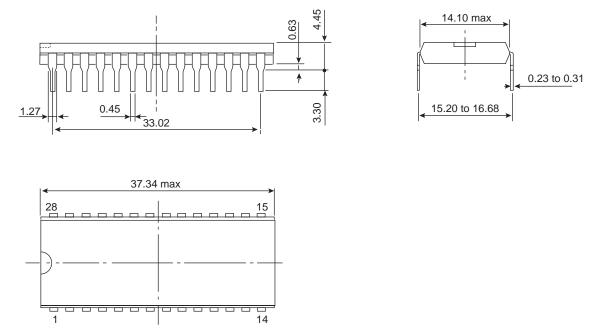

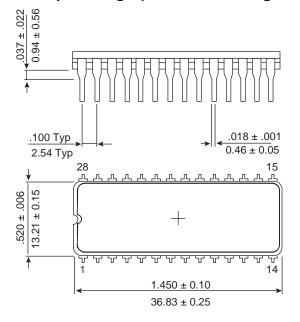

C Suffix DIL 28 Ceramic Side Brazed package

P Suffix DIP 28 Plastic Package

ARINC 429 Multi-channel Buffer Receiver (RTA) (N Channel, Silicon Gate)

# EF4442

Rev. 2112A-HIREL-11/02

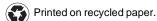

## Figure 1. Block Diagram

| Name<br>Number  | Description                                                                                                                                                                                                                                                                                                                                                      |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>SS</sub> | This pin is connected to the negative side of the power supply (ground).                                                                                                                                                                                                                                                                                         |

| R₩/INH          | This input selects the direction of transfer (write or read) of data between the circuit and the microprocessor when the circuit is programmed in mode A (cf. Pin 28).<br>In B mode, this input is used to disable the channel scanning divide by 4 counter. In A mode, this output has a transmit function. The signal corresponding to the result of ANDing.   |

| NO              | In A mode, this output has a transmit function. The signal corresponding to the result of ANDing the ARINC transmit clock and the complemented output signal of the transmit shift register (logic "0" clock output) is available on this pin. In B mode, the value of the least significant bit of the address of the scanned channel is available on this pin. |

| N1              | In A mode, this output has a transmit function. The signal corresponding to the result of ANDing the ARINC transmit clock and the output signal of the transmit shift register (logic "1" clock available on this pin). In B mode, the value of the least significant bit of the address of the scanned channel is available on this pin.                        |

| CS              | In A mode, this input (active when low) selects the chip for a microprocessor access.                                                                                                                                                                                                                                                                            |

| A0              | In A mode, this input corresponds to the most significant bit of the circuit function address.<br>In B mode, this input corresponds to the least significant bit of the address of the data byte in the message.                                                                                                                                                 |

| A1              | In A mode, this input corresponds to the most significant bit of the circuit function address.<br>In B mode, this input corresponds to the most significant bit of the address of the data byte in the message.                                                                                                                                                  |

| RESET           | This input (active when low) initializes the circuit by resetting some registers.                                                                                                                                                                                                                                                                                |

EF4442

## Table 1. Pin Description (Continued)

| Name<br>Number  | Description                                                                                                                       |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Ø               | This input receives the clock signal from the circuit which corresponds to the phase Ø2 of the microprocessor clock.              |

| D7              | This tristate input/output is connected to the eighth line of the data bus.                                                       |

| D6              | This tristate input/output is connected to the seventh line of the data bus.                                                      |

| D5              | This tristate input/output is connected to the sixth line of the data bus.                                                        |

| D4              | This tristate input/output is connected to the fifth line of the data bus.                                                        |

| V <sub>CC</sub> | This pin is connected to the positive side of the power supply (+5V).                                                             |

| D3              | This tristate input/output is connected to the fourth line of the data bus.                                                       |

| D2              | This tristate input/output is connected to the third line of the data bus.                                                        |

| D1              | This tristate input/output is connected to the second line of the data bus.                                                       |

| D0              | This tristate input/output is connected to the first line of the data bus.                                                        |

| L0              | This input receives the logic "0" clock from the signal shaping/separation subsystem of the first ARINC channel.                  |

| HO              | This input receives the logic "1" clock from the signal shaping/separation subsystem of the first ARINC channel.                  |

| L1              | This input receives the logic "0" clock from the signal shaping/separation subsystem of the second ARINC channel.                 |

| H1              | This input receives the logic "1" clock from the signal shaping/separation subsystem of the second ARINC channel.                 |

| L2              | This input receives the logic "0" clock from the signal shaping/separation subsystem of the third ARINC channel.                  |

| H2              | This input receives the logic "1" clock from the signal shaping/separation subsystem of the third ARINC channel.                  |

| L3              | This input receives the logic "0" clock from the signal shaping/separation subsystem of the fourth ARINC channel.                 |

| H3              | This input receives the logic "1" clock from the signal shaping/separation subsystem of the fourth ARINC channel.                 |

| ĪRQ/V           | In A mode, this pin (active when low) constitutes an open drain output delivering the signal for interrupting the microprocessor. |

|                 | In B mode, this pin is an input used to program the number of high speed channels.                                                |

| Mode            | This input is used to program the operating mode (A or B) of the circuit and also to enable or disable this parity check.         |

Description of Registers

The EF4442 circuit features three types of internal register:

- Registers concerned with general circuit operation,

- Registers specific to the transmit channel,

- Registers specific to each receive channel.

# **General Registers**

Status Register

This register is used only when the circuit is programmed in A mode. Its contents inform the microprocessor about the status of the circuit functions. Bits S0 and S4 activate output IRQ when at 1 (except S4 which is maskable - cf. description of control register).

Bits S0 and S3 at 1 indicate that the channel with the address which corresponds to the rank of the bit has received a correct message (label recognized and correct parity in the case of a circuit programmed to check the parity of messages).

Each bit is reset to 0 on reading the registers of the corresponding channel.

In transmit mode, bit S4 of the status register is set to 1 when transmission of the message is terminated.

|                                             | Bit S4 is reset to 0 when control bit C4 (see below) is a 1.<br>Bits S5 and S6 are not used.                                                                                                                                                                                                                                                       |  |  |  |  |  |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                                             |                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|                                             | Bit S7 is at 1 throughout transmission.                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| Control Register                            | This eight-bit register (C0-C7) monitors operation of the circuit in A mode.                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|                                             | In receive mode, bits C0-C3 select the corresponding channels for writing or reading when set to 1 by the microprocessor.                                                                                                                                                                                                                          |  |  |  |  |  |

|                                             | Bit C4 at 1 enables programming of the transmit channel (data to send and transmission speed). The setting of bit C4 to 1 resets to 0 the index of the four-byte stack constituting the message to send.                                                                                                                                           |  |  |  |  |  |

|                                             | Bit C5 at 1 is used to initiate transmission of the message. It is set to 0 when transmis-<br>sion is terminated.                                                                                                                                                                                                                                  |  |  |  |  |  |

|                                             | Bit C6 at 1 simultaneously with bit C5 at 1 loops back the transmitted data to the input of the receive channel selected by bits C0-C3, for test purposes. It is set to 0 by any control register access.                                                                                                                                          |  |  |  |  |  |

|                                             | Bit C7 at 1 masks status bit S4 and thus prevents activation of output $\overline{IRQ}$ .                                                                                                                                                                                                                                                          |  |  |  |  |  |

| Transmit Channel<br>Registers (A mode only) |                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| Programmable Divider<br>Register            | This eight-bit register is programmed by the microprocessor and contains the value n of the division ratio (the least significant bit is always considered to be at 0).                                                                                                                                                                            |  |  |  |  |  |

|                                             | The programmable divider generates a clock signal at a frequency equal to clock $\emptyset$ divided by n.                                                                                                                                                                                                                                          |  |  |  |  |  |

| Transmit Register                           | This 32-bit shift register may be programmed in four phases by the microprocessor. This writing must be effected immediately after the setting to 1 of control bit C4 (cf. description of control register). This resets to zero the index of the 4-byte stack.                                                                                    |  |  |  |  |  |

|                                             | The transmit register shifts the data present in it to the outputs in accordance with the states of the bits in the control register.                                                                                                                                                                                                              |  |  |  |  |  |

| Receive Channel<br>Registers                | Each receive channel comprises the following registers:                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| Synchronization/Enable                      | This eight-bit register is programmable by the microprocessor.                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| Register                                    | The most significant bit (bit 7) is used, in A mode only, to disable the transfer of data at the input into the buffer register (cf. description of these two registers). The channel affected is then seen as being out of service.                                                                                                               |  |  |  |  |  |

|                                             | The other seven bits (bits 0 - 6) select the value of the time-delay used to detect the presence of a "gap". This is the space between two consecutive messages, the minimum duration of which is four periods of the transmit clock. This value is loaded into the register by the microprocessor, in A mode, at the same time as the enable bit. |  |  |  |  |  |

|                                             | In B mode, this value is selected from two hardwired values, according to the state on pin IRQ/V.                                                                                                                                                                                                                                                  |  |  |  |  |  |

|                                             | If n is the programmed value, the gap detection time-delay will be $(8n - 4) \pm 4$ period of clock Ø.                                                                                                                                                                                                                                             |  |  |  |  |  |

| Input Register           | <ul> <li>This 32-bit shift register receives the data corresponding to the messages. The message received is transferred into the registers on its output side if:</li> <li>a gap detection signal has previously occurred,</li> <li>the registers which will receive the transferred data are not being read,</li> <li>the parity of the received message is correct if the circuit is programmed with the parity check enabled,</li> <li>the enable bit of the synchronization/enable register is set to 1 (A mode only),</li> <li>in A mode, the first eight bits received correspond to the programmed label (cf. description of label register).</li> </ul> |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Label Register           | In A mode, this eight-bit register is programmed by the microprocessor. It contains the label to be recognized.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                          | In B mode, this register receives the first eight bits of the received message transferred from the input register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                          | In this case, this register may be read by the external automatic scanning device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Buffer Register          | This 24-bit register receives data transferred from the input register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                          | It may be read by the microprocessor in A mode or by the external automatic scanning device in B mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| <b>Circuit Operation</b> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

Logic Convention "1" (high state) = most positive level "0" (low state) = most negative level

# Operation of a Receive Channel

**Data Acquisition**

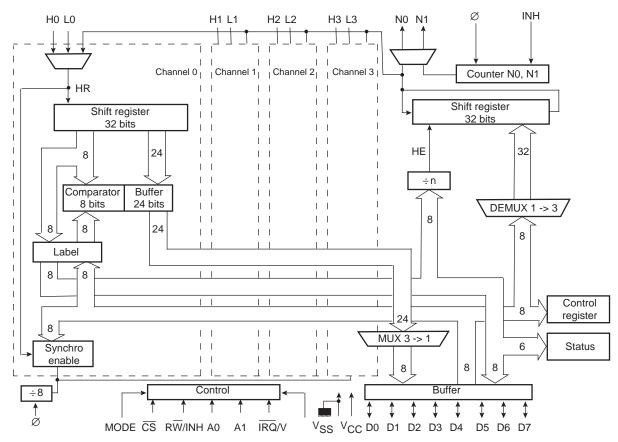

Serial data is received on the "low" and the "high" lines (Hi and Li inputs). The Clock is reconstructed by OR-ing these inputs. Data is then directed towards a 32-bit shift register. Parity is computed. The reconstructed clock fall edge resets the message synchronization counter. This counter is incremented on each Ø: 8 clock period and delivers a word synchronization signal (gap) as described below (Figure 2) when reading a programmed value.

## Figure 2. Gap Detection

The predetermined value together with an enable bit is loaded in the internal synchro/validation register when in A mode; it is chosen between two hardware programmed values when in B mode, according to the IRQ/V pin.

Then:

#### • When in A Mode

The first 8 bits (M0-M7) that are received, are bits compared to a programmed word (label), this for each channel. If identical, the 24 other bits of the shift register are transferred in a 24-bit buffer register. The corresponding status bit is switched to 1 and the  $\overline{IRQ}$  line is activated ( $\overline{IRQ} = 0$ ).

If the channel enable bit is in the low state, transfer is not executed and the  $\overline{IRQ}$  line is not activated.

#### • When in B Mode

All the shift register bits are transferred in the label and the 24-bit buffer register.

Transfers are inhibited if the message parity is wrong in either mode (even number of bits in the high state) and if the circuit is programmed for parity check (Mode pin).

This last one generates a  $\emptyset$  + n frequency square wave, n being the programmed value (the least significant bit being always set to 0).

Then successively addresses the 8-bit bytes of the 24-bit buffer which are then available on the bus (D0-D7).

Reading the last byte resets the corresponding status byte to the low state.

The transfer from the receive register to the buffer register is inhibited from the "read" addressing of the channel (first or second byte) to the end of the last byte reading.

#### • When in B Mode

A divide by 4 counter is incremented on each  $\emptyset$  clock period and successively addresses the 4 channels. When the circuit is selected ( $\overline{CS} = 0$ ) and when A0 - A1 = 11, the label of the addressed channel is available on the bus (D0 - D7), as well as the channel number on the N0-N1 outputs.

Counting is inhibited when RW/INH is in the high state. If the circuit is selected, the three bytes of the buffer register are then available on the bus when addressed through A0 - A1 in the same way as A mode.

The transfer from the receive register to the buffer register is done in the same way as A mode.

In order to read the message corresponding to label received,  $\overline{CS}$  has to stay activated to 0 during the reading of label and message  $RT_1 - RT_3$  (minimum  $\overline{CS} = 0$  during the reading of the label and  $RT_1$ ).

However  $\overline{\text{CS}}$  has to stay activated to 0 during less than 30 clock periods of PHI (Ø).

| Operation of the<br>Transmit Channel |                                     | smit channel is composed of a 32-bit shift register and a programmable divider. ration of this channel is controlled by the control register (C0 - C7).                                                                                                                                                                                                                        |

|--------------------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (only in A mode)                     | 0)" on pa                           | ets the program of the transmit channel (see "Programming In A Mode (MODE = age 7). The 4 bytes of the shift register are loaded (including the microprocessor d parity bit). So is the divider by n register byte.                                                                                                                                                            |

|                                      |                                     | er generates a divided by n frequency square wave, n being the programmed e least significant bit being always set to 0).                                                                                                                                                                                                                                                      |

|                                      |                                     | ssion starts when C5 is set to 1. The data of the shift register is then available and 1 lines of the channel and is clocked out at the chosen frequency.                                                                                                                                                                                                                      |

|                                      |                                     | register is also feed forwarded so that data should not be lost. After the trans-<br>of the 32nd bit, C5 is reset. The S4 bit is set to 1. It will be reset when C4 will be<br>ed to 1.                                                                                                                                                                                        |

|                                      | The S7 b                            | pit of the status register is set to 1 during the transmission time.                                                                                                                                                                                                                                                                                                           |

|                                      |                                     | set to 1 after transmission of the 32nd bit, the message is retransmitted after 4 clock periods. The S4 status bit will also be reset when control bit C4 is set to 1.                                                                                                                                                                                                         |

|                                      | reception                           | ed for starting the receive channel testing. This test cannot be done during the n of a message. If $C6 = 1$ the transmission channel signals are switched to the the control register selected receive channel. C6 is reset by any access to the egister.                                                                                                                     |

|                                      |                                     | nask bit of the S4 bit of the status register. If C7 = 0 and S4 = 1, the $\overline{IRQ}$ line will ated. If C7 = 1, the $\overline{IRQ}$ line will not be activated by S4.                                                                                                                                                                                                    |

|                                      |                                     | C5 and C6 should be programmed at the same time in order to avoid transmission or test errors.                                                                                                                                                                                                                                                                                 |

| Programming In A Mode<br>(MODE = 0)  | When se<br>"write").                | een from the microprocessor, the circuit looks like 4 addresses ("read" or                                                                                                                                                                                                                                                                                                     |

|                                      | char                                | ing any register of a channel is done in two steps:<br>anel addressing by the control register<br>of the selected channel addressing                                                                                                                                                                                                                                           |

|                                      |                                     | ogramming of the synchro registers or the labels and reading of the 24-bit buff-<br>e status register are possible.                                                                                                                                                                                                                                                            |

|                                      | bytes, th<br>generate<br>trol regis | of the transmit channel shift register is done through successive writing of the 4 be first being the label then $RT_1$ , $RT_2$ , $RT_3$ . The addresses of the 4 bytes are ed by an internal modulo-4 counter which is reset by any addressing of the conster (see Table 2 - Addressing with $\overline{CS} = 0$ and Table 3 - Addressing of the s by the control register). |

| Table 2. | Addressing w | with $\overline{CS} = 0$ |

|----------|--------------|--------------------------|

|----------|--------------|--------------------------|

| RW/INH | A1 | A0 | Direct Addressing | Channel Addressing With<br>the Control Register |

|--------|----|----|-------------------|-------------------------------------------------|

|        | 0  | 0  | _                 | RT1                                             |

| Read   | 0  | 1  |                   | RT2                                             |

| 1      | 1  | 0  |                   | RT3                                             |

|        | 1  | 1  | Status            | _                                               |

|        | 0  | 0  |                   | Synchro and divider by n                        |

| Write  | 0  | 1  | Control           | _                                               |

| 0      | 1  | 0  | Not used          | _                                               |

|        | 1  | 1  |                   | Label                                           |

| Table 3. | Channel | Addressing | by the | Control | Register |

|----------|---------|------------|--------|---------|----------|

|----------|---------|------------|--------|---------|----------|

| C0 | C1 | C2 | C3 | Channel Number |

|----|----|----|----|----------------|

| 1  | х  | х  | х  | channel 0      |

| 0  | 1  | х  | х  | channel 1      |

| 0  | 0  | 1  | Х  | channel 2      |

| 0  | 0  | 0  | 1  | channel 3      |

The gap detection counters are incremented on each  $\emptyset$  divided by 8 clock period, if n is the synchro register value, the minimum detected gap length is  $(8n - 4) \pm 4 \emptyset$  clock periods.

C4 to C7 bits are independently interpreted.

C4: Pile loading if A0 - A1 = 11 and divider by n if A0 - A1 = 00.

The loading of the 4 bytes to be transmitted should be done immediately after positioning C4 to 1, this operation resetting the pile index at the level of the label byte.

C5:Transmission start

C6: Test mode

C7: Transmit channel interrupt mask

## Figure 3. Bit Correspondence

|                      |    | Acquis | ition o | r trans | smission | flow   |        | <b>&gt;</b> |   |     |       |     |

|----------------------|----|--------|---------|---------|----------|--------|--------|-------------|---|-----|-------|-----|

| Acquisition register | 31 |        |         |         |          |        |        |             |   |     |       |     |

| Buffer register      | 7  | RT3    | 0       | 7       | RT2      | 0      | 7      | RT1         | 0 | 7   | LABEL | 0   |

|                      |    |        |         |         |          |        | Bus    | 5 D (0:7)   |   | 7   |       | 0   |

|                      |    |        |         |         |          | С      | ontro  | l C (0:7)   |   | 7   |       | 0   |

|                      |    |        |         |         |          | 5      | Status | s S (0:7)   |   | 7 Ø | ø ø 4 | 0   |

|                      |    |        |         |         |          |        |        |             |   |     | RT3   |     |

|                      |    |        |         |         |          | ٦      | Frans  | mit shift   |   |     | RT2   |     |

|                      |    |        |         |         |          |        | F      | Register    |   |     | RT1   |     |

|                      |    |        |         |         |          |        |        |             | ¥ |     | LABEL |     |

|                      |    |        |         | E       | nable ar | nd syr | nchro  | register    |   | V 6 | 6     | 0   |

|                      |    |        |         |         |          |        | Divid  | der by n    |   | 7   |       | 1 Ø |

## Programming in B Mode (MODE = 1)

When in B mode, programming is done by hardware. The number of high speed channels is programmed on  $\overline{IRQ}/V$  pin (see Table 4).

The synchro register is set to 5 for high speed channels and to 32 for low speed channels. This corresponds to a nominal  $\emptyset$  clock frequency of 2 MHz and transmission frequencies of 12 to 14.5 kHz for low speed and of 99 to 101 kHz for high speed.

#### Table 4. Programming of the IRQ/Vpin

| IRQ/V             | High Speed Channel Numbers |

|-------------------|----------------------------|

| 0: Low impedance  | -                          |

| 0: High impedance | 0                          |

| 1: Low impedance  | 0, 1                       |

| 1: High impedance | 0, 1, 2                    |

## **Parity Check**

If the MODE pin senses a high impedance (typ. > 10 k $\Omega$ ) the circuit checks the parity of the messages for each receive channel. If the number of received 1's in a message is even, the transfer is not done and the message is discarded (odd parity).

When transmitting, the parity bit value is computed and loaded by the microprocessor or is the value of the received test message.

If the MODE pin is directly strapped to  $V_{CC}$  or  $V_{SS}$ , parity check is not done.

### Initialization

On power-on or when the RESET pin is set to 0, the following registers are reset to 0:

- control register

- status register

- the 4 label registers of the receive channels

- the 4 synchro registers.

The first gap after initialization is also ignored for each channel because acquired data could not be error-free.

# Electrical **Characteristics**

# Maximum Ratings

| Symbol           | Rating                   |                             | Value       | Unit            |

|------------------|--------------------------|-----------------------------|-------------|-----------------|

| V <sub>cc</sub>  | Supply Voltage           |                             | -0.3 to +7  | V <sub>dc</sub> |

| V <sub>IN</sub>  | Input Voltage            | Input Voltage               |             | V <sub>dc</sub> |

| Τ <sub>C</sub>   | Operating Temperature Ra | Operating Temperature Range |             | °C              |

| T <sub>stg</sub> | Storage Temperature Rang | je                          | -55 to +150 | °C              |

| Pd               | Power Dissipation        | Tc = 125°C                  | 300         | mW              |

|                  |                          | $Tc = 25^{\circ}C$          | 350         | mW              |

|                  |                          | Tc = -55°C                  | 550         | mW              |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields: however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit.

Table 5. Thermal Characteristics (at 25°C)

| Package | Symbol                                                       | Parameter                              | Value | Unit |

|---------|--------------------------------------------------------------|----------------------------------------|-------|------|

|         | DIL 28 $\theta_{J-A}$ Thermal Resistance Junction-to-ambient |                                        | 50    | °C/W |

| DIL 20  | $\theta_{J-C}$                                               | Thermal Resistance Junction-to-case    | 10    | °C/W |

| 1000.00 | $\theta_{J-A}$                                               | Thermal Resistance Junction-to-ambient | 45    | °C/W |

| LCCC 32 | $\theta_{J-C}$                                               | Thermal Resistance Junction-to-case    | 9     | °C/W |

## **Power Considerations**

The average chip-junction temperature, TJ, in °C can be obtained from:

$T_{J=}T_{A} + (P_{D} \cdot \theta_{JA})$

(1)

T<sub>A</sub> = Ambient Temperature,°C

$\theta_{JA}$  = Package Thermal Resistance,

Junction-to-Ambient,°C/W

$$P_{\rm D} = P_{\rm INT} + P_{\rm I/O}$$

$P_{INT} = I_{CC} \times V_{CC}$ , Watts – Chip Internal Power  $P_{I/O}$  = Power Dissipation on Input and Output Pins – User Determined

For most applications  $P_{I/O} < P_{INT}$  and can be neglected.

An approximate relationship between  $P_D$  and  $T_J$  (if  $P_{I/O}$  is neglected) is:

$$P_{D} = K: (T_{J} + 273)$$

Solving equations (1) and (2) for K gives:

$$K = P_{D} \cdot (T_{A} + 273) + \theta_{JA} \cdot P_{D}^{2}$$

(3)

where K is a constant pertaining to the particular part K can be determined from equation (3) by measuring P<sub>D</sub> (at equilibrium) for a know T<sub>A</sub>. Using this value of K, the values of  $P_D$  and  $T_J$  can be obtained by solving equations (1) and (2) iteratively for any value of T<sub>A</sub>.

(2)

The total thermal resistance of a package  $(\theta_{JA})$  can be separated into two components,  $\theta_{JC}$  and  $\theta_{CA}$ , representing the barrier to heat flow from the semiconductor junction to the package (case), surface  $(\theta_{JC})$  and from the case to the outside ambient  $(\theta_{CA})$ . These terms are related by the equation:

$$\theta_{JA} = \theta_{JC} + \theta_{CA}$$

(4)

$\theta_{JC}$  is device related and cannot be influenced by the user. However,  $\theta_{CA}$  is user dependent and can be minimized by such thermal management techniques as heat sinks, ambient air cooling and thermal convection. Thus, good thermal management on the part of the user can significantly reduce  $\theta_{CA}$  so that  $\theta_{JA}$  approximately equals  $\theta_{JC}$ . Substitution of  $\theta_{JC}$  for  $\theta_{JA}$  in equation (1) will result in a lower semiconductor junction temperature.

Table 6. Recommended Static Operating Conditions

| Symbol          | Parameter          | Min  | Мах  | Unit |

|-----------------|--------------------|------|------|------|

| V <sub>IH</sub> | Input High Voltage | 2.0  | 5.25 | V    |

| V <sub>IL</sub> | Input Low Voltage  | -0.3 | 0.8  | V    |

| V <sub>CC</sub> | Supply Voltage     | 4.75 | 5.25 | V    |

## Table 7. Static Characteristics

$(V_{CC} = 5.0V \pm 5\%; V_{SS} = 0V; -55^{\circ}C < TC < + 125^{\circ}C)$

| Symbol           | Characteristics                                                                                                                   | Min        | Тур | Мах                                | Unit |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------|-----|------------------------------------|------|

| V <sub>IH</sub>  | Input high voltage (except MODE, IRQ/V)                                                                                           | 2.2        |     | V <sub>CC</sub>                    | V    |

| V <sub>IL</sub>  | Input low voltage (except MODE, IRQ/V)                                                                                            | -0.3       |     | 0.8                                | V    |

| l <sub>in</sub>  | Input state leakage current (except MODE, $\overline{IRQ}/V$ )<br>(V <sub>IN</sub> = 0.4 to 5.25V)                                | -10        |     |                                    | μΑ   |

| I <sub>TSI</sub> | Three state leakage current N0-N1, D0-D7 $(V_{IN} = 0.4 \text{ to } 2.4 \text{V})$                                                | -10        |     | 10                                 | μA   |

| V <sub>OH</sub>  | Output high voltage<br>$(I_{Load} = -250 \ \mu\text{A})$ N0-N1, D0-D7<br>$(I_{Load} = +10 \ \mu\text{A})$ $\overline{IRQ}/V$      | 2.4<br>2.4 |     | V <sub>cc</sub><br>V <sub>cc</sub> | V    |

| V <sub>OL</sub>  | Output high voltage $(I_{Load} = 1.6 \text{ mA})$ N0-N1, D0-D7 $(I_{Load} = 3.2 \text{ mA})$ $\overline{IRQ}/V$                   |            |     | 0.4                                | V    |

| C <sub>in</sub>  | Capacitance<br>( $V_{in}$ = 0, TC = 25°C, f = 1 MHz)<br>(except MODE, $\overline{IRQ}/V$ )                                        |            |     | 10                                 | pF   |

| R <sub>H</sub>   | External high programming impedance<br>MODE, $\overline{IRQ}/V$ , (C <sub>load</sub> $\leq$ 20pF)<br>Scan frequency = f clock: 8) | 10 K       |     |                                    | Ω    |

| RL               | External low programming impedance<br>Mode, $\overline{IRQ}/V$ (C <sub>load</sub> $\leq$ 20 pF)<br>Scan frequency = f clock: 8)   |            |     | 10                                 | Ω    |

## **Table 7.** Static Characteristics (Continued)

$(V_{CC} = 5.0V \pm 5\%; V_{SS} = 0V; -55^{\circ}C < TC < + 125^{\circ}C)$

| Symbol         | Characteristics                       | Min  | Тур | Max  | Unit |

|----------------|---------------------------------------|------|-----|------|------|

| P <sub>D</sub> | Power dissipation                     |      | 310 | 550  | mW   |

| f              | Maximum operating frequency in A mode | 500  |     | 2000 | kHz  |

| F              | Maximum operating frequency in B mode | 1000 |     | 2000 | kHz  |

# **Dynamic Characteristics**

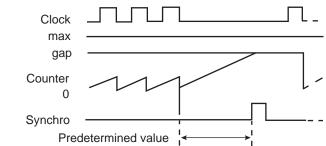

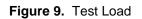

Table 8. Bus Timing Characteristics (Load Conditions, see Figure 9) (V<sub>CC</sub> = 5.0V  $\pm$  5%; V<sub>SS</sub> = 0V; -55°C < TC < +125°C)

| Symbol                  | Characteristic                  |                                              | Min | Max | Unit |

|-------------------------|---------------------------------|----------------------------------------------|-----|-----|------|

| Read – A Mode           | e (Figure 4)                    |                                              |     |     |      |

| t <sub>AH</sub>         | Address Input Hold Time         | A0-A1, $R\overline{W}/INH$ , $\overline{CS}$ | 10  |     | ns   |

| T <sub>ACC</sub>        | Data Access Time <sup>(1)</sup> | D0-D7                                        |     | 300 | ns   |

| t <sub>DH</sub>         | Data Output Hold Time           | D0-D7                                        | 10  |     | ns   |

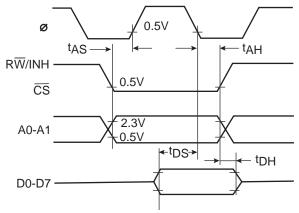

| Write – A Mod           | e (Figure 5)                    |                                              |     |     |      |

| t <sub>AS</sub> A0-A1ns | Address Input Setup Time        | A0-A1, $R\overline{W}/INH$ , $\overline{CS}$ | 50  |     | ns   |

| t <sub>AH</sub>         | Address Input Hold Time         | A0-A1, RW/INH, CS                            | 10  |     | ns   |

| t <sub>DS</sub>         | Data Set Up Time                | D0-D7                                        | 100 |     | ns   |

| t <sub>DH</sub>         | Data Input Hold Time            | D0-D7                                        | 50  |     | ns   |

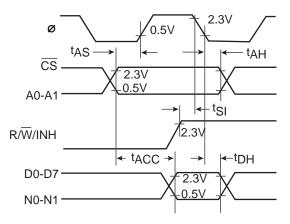

| Read – B Mode           | e (Figure 6)                    |                                              |     |     |      |

| t <sub>AS</sub>         | Address Setup Time              | A0-A1, $R\overline{W}/INH$ , $\overline{CS}$ | 50  |     | ns   |

| t <sub>AH</sub>         | Address Input Hold Time         | A0-A1, $R\overline{W}/INH$ , $\overline{CS}$ | 10  |     | ns   |

| t <sub>DH</sub>         | Data Output Hold Time           | 0-N1, D0-D7                                  | 10  |     | ns   |

| t <sub>ACC</sub>        | Data Access Time                | N0-N1, D0-D7                                 |     | 300 | ns   |

| t <sub>SI</sub>         | RW/INH Setup Time               |                                              | 50  |     | ns   |

Note: 1. See condition of validity for the access time of EF4442 status register at high temperature (Tc ≥ +85°C) in "Annexe 1: EF4442 ARINC Controller/Bug Description:" on page 20.

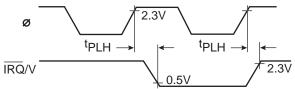

Table 9.

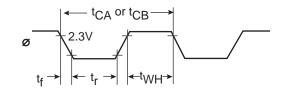

Clock Timing Characteristics (see Figure 8)

| Symbol           | Characteristic         | Min | Мах  | Unit |

|------------------|------------------------|-----|------|------|

| t <sub>CA</sub>  | A Mode Cycle Time      | 500 | 2000 | ns   |

| t <sub>CB</sub>  | B Mode Cycle Time      | 500 | 1000 | ns   |

| t <sub>WH</sub>  | Pulse Width – Low 2000 | 180 | 2000 | ns   |

| t <sub>vvL</sub> | Pulse Width – High     | 180 | 2000 | ns   |

| tr, tf           | Rise Time, Fall Time   |     | 15   | ns   |

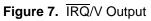

| Table 10. | IRQ/V Output | Timing Char | acteristics | (see Figure 7 | 7) |

|-----------|--------------|-------------|-------------|---------------|----|

|-----------|--------------|-------------|-------------|---------------|----|

| Symbol           | Characteristic                 | Мах  | Unit |

|------------------|--------------------------------|------|------|

| t <sub>PHL</sub> | Delay Time – Low To High State | 1600 | ns   |

| t <sub>PHL</sub> | Delay Time – High To Low State | 1000 | ns   |

# **Timing Diagrams**

# Figure 4. Read A Mode

# Figure 5. Write A Mode

# Figure 6. Read B Mode

Figure 8. Clock

# Preparation For Delivery

| Packaging                 | The microcircuits are packaged in a hermetically sealed package which is conformed to case outlines of MIL-STD-883 28 lead DIL/SB                                                                                                                                                 |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Certificate of Compliance | Atmel offers a certificate of compliance with each shipment of parts, affirming the prod-<br>ucts are in compliance either with MIL-STD-883 or Atmel standard and guaranteeing the<br>parameters are tested at extreme temperatures for the entire temperature range.             |

| Handling                  | Devices must be handled with certain precautions to avoid damage due to accumulation<br>of static charge. Input protection devices have been designed in the chip to minimize the<br>effect of this static buildup. However, the following handling practices are<br>recommended: |

|                           | 1. Device should be handled on benches with conductive and grounded surface.                                                                                                                                                                                                      |

|                           | <ol><li>Ground test equipment, tools and operator.</li></ol>                                                                                                                                                                                                                      |

|                           | 3. Do not handle devices by the leads.                                                                                                                                                                                                                                            |

|                           | 4. Store devices in conductive foam or carriers.                                                                                                                                                                                                                                  |

|                           | 5. Avoid use of plastic, rubber, or silk.                                                                                                                                                                                                                                         |

|                           | 6. Maintain relative humidity above 50%, if practical.                                                                                                                                                                                                                            |

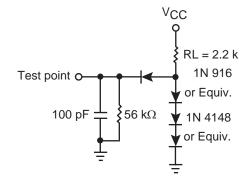

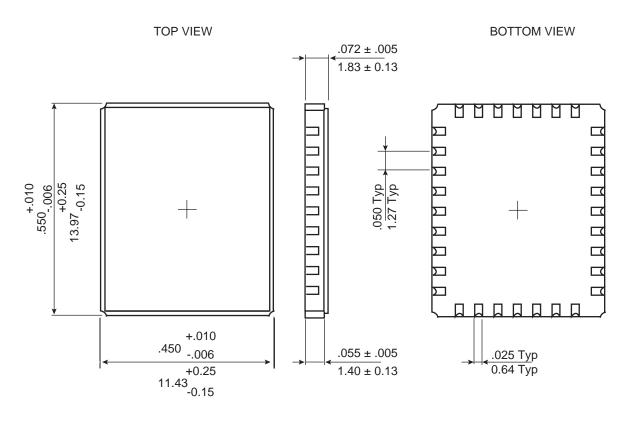

# Package Mechanical Data

DIL 28 – Ceramic Side Brazed Package

DIL 28 - Cerdip Package (Obsolete Package, for Traceability Purpose Only)

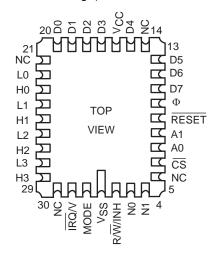

# LCCC32 – Leadless Ceramic Chip Carrier package (Obsolete Package, for Traceability Purpose Only) To Be Confirmed

# **Terminal Designation**

Figure 10. DIL 28/DIP 28

|                   | <b></b> |            |    | 1      |

|-------------------|---------|------------|----|--------|

|                   |         | $\bigcirc$ |    |        |

| V <sub>SS</sub> □ | 1•      |            | 28 | 🗆 MODE |

| R/₩/INH [         | 2       |            | 27 |        |

| N0 🗆              | 3       |            | 26 | 🗆 НЗ   |

| N1 🗆              | 4       |            | 25 | 🗆 L3   |

| CS 🗆              | 5       |            | 24 | □ H2   |

| A0 🗆              | 6       | TOD        | 23 | □ L2   |

| A1 🗆              | 7       | TOP        | 22 | □ H1   |

| RESET 🗆           | 8       | VIEW       | 21 | □ L1   |

| $\Phi$            | 9       |            | 20 | 🗆 но   |

| D7 🗆              | 10      |            | 19 |        |

| D6 🗆              | 11      |            | 18 | D0 🗆   |

| D5 🗆              | 12      |            | 17 | 🗆 D1   |

| D4 🗆              | 13      |            | 16 | D2     |

| Vcc □             | 14      |            | 15 | _ D3   |

|                   |         |            |    |        |

EF4442

Figure 11. LCCC 32 (Obsolete Package)

# **Ordering Information**

## Table 11. Hi-REL Product

| Commercial Atmel<br>Part-Number | Norms                    | Package            | Temperature Range<br>Tc (C) | Class | Drawing<br>Number |

|---------------------------------|--------------------------|--------------------|-----------------------------|-------|-------------------|

| EF4442CMG/BZ63                  | NFC 96883                | DIL 28 Side Brazed | -55/ +125                   | G     | Data sheet        |

| EF4442CMB/TZ63                  | According to MIL-STD-883 | DIL 28 Side Brazed | -55/ +125                   | В     | Data sheet        |

| EF4442PVZ63                     | Atmel Standard           | DIP 28             | -40/ +85                    |       | Data sheet        |

# Annexe 1: EF4442 ARINC Controller/Bug Description:

Condition of Validity for the Access Time in A mode (Tacc) of EF4442 Status Register at High Temperature ( $T_{CASE} \ge 85^{\circ}C$ ).

| Description  | In a particular condition described here after, the access time (Tacc) of EF4442 status register is above the maximum value specified in Table 8.                                                                                                                                       |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Conditions   | The defect appears for high temperature 85°C and +125°C.                                                                                                                                                                                                                                |

|              | When the $R_{TA}$ starts a new transmission in A mode, the S7 bit of the status register is set to 1 after 4 transmit clock periods. If this S7 bit is read before it has risen to 1 (i.e. S7 = 0), then the first access time (Tacc) for S7 = 1 will be longer than the specification: |

|              | <ul> <li>maximum value up to 400 ns for military range part number (M),</li> </ul>                                                                                                                                                                                                      |

|              | <ul> <li>maximum value up to 330 ns for industrial range part number (V).</li> </ul>                                                                                                                                                                                                    |

|              | If a second read is performed to the S7 bit, the access time (Tacc) will be compliant with the specification (max value = 300 ns).                                                                                                                                                      |

| Workaround 1 | After a new transmission start in A mode (bit C5 of control register = 1), the status register does not have to be read before the S7 bit is set to 1. In that case the access time would be correct.                                                                                   |

| Workaround 2 | Perform two successive read access to the Status register. The second access time would be correct.                                                                                                                                                                                     |

## **Atmel Headquarters**

Corporate Headquarters 2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 487-2600

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland TEL (41) 26-426-5555 FAX (41) 26-426-5500

## Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimhatsui East Kowloon Hong Kong TEL (852) 2721-9778 FAX (852) 2722-1369

#### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan TEL (81) 3-3523-3551 FAX (81) 3-3523-7581

## **Atmel Operations**

Memory

2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 436-4314

#### Microcontrollers

2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France TEL (33) 2-40-18-18-18 FAX (33) 2-40-18-19-60

#### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France TEL (33) 4-42-53-60-00 FAX (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL 1(719) 576-3300 FAX 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland TEL (44) 1355-803-000 FAX (44) 1355-242-743

#### **RF**/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany TEL (49) 71-31-67-0 FAX (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL 1(719) 576-3300 FAX 1(719) 540-1759

# Biometrics/Imaging/Hi-Rel MPU/

High Speed Converters/RF Datacom Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France TEL (33) 4-76-58-30-00 FAX (33) 4-76-58-34-80

# e-mail

literature@atmel.com

Web Site http://www.atmel.com

#### © Atmel Corporation 2002.

Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

ATMEL<sup>®</sup> is the registered trademark of Atmel.

Other terms and product names may be the trademarks of others.