# HDAS-16, HDAS-8

### 12-Bit, 50kHz, Complete Data Acquisition Systems

### **FEATURES**

- Miniature 62-pin cermanic package

- 12-Bit resolution, 50kHz throughput

- Full-scale input range from 50mV to 10V

- Three-state outputs

- 16 S.E. or 8 differential input channels

- Auto-sequencing channel addressing

- MIL-STD-883 versions

- No missing codes

### **GENERAL DESCRIPTION**

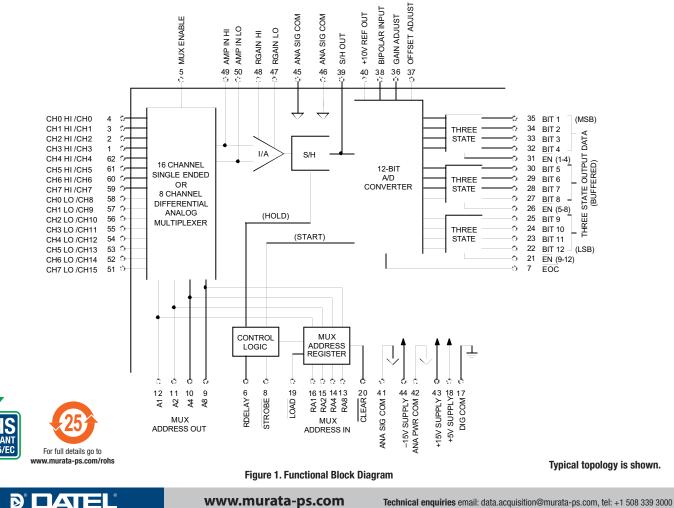

Using thin and thick-film hybrid technology, Murata Power Solutions offers complete low-cost data acquisition systems with superior performance and reliability.

The HDAS-8 (with 8 differential input channels) and the HDAS-16 (with 16 single-ended input channels) are complete, high-performance, 12-bit data acquisition systems in 62-pin packages. Each HDAS may be expanded up to 32 single-ended or 16 differential channels by adding externalmultiplexers.

Internal channel address sequencing is automatic after each conversion, or the user may supply external channel addresses.

### Internal HDAS circuitry includes:

- Analog input multiplexer (16 S.E. or 8 diff.)

- Resistor-programmable instrumentation amplifier

- Sample-and-hold circuit complete with MOS hold capacitor

- 10 Volt buffered reference

- 12-bit A/D converter with three-state outputs and control logic

| ABSOLUTE MAXIMUM RATINGS |      |      |      |         |

|--------------------------|------|------|------|---------|

| PARAMETERS               | MIN. | TYP. | MAX. | UNITS   |

| +15V Supply (pin 43)     | -0.5 | —    | +18  | Volts   |

| –15V Supply (pin 44)     | +0.5 | —    | -18  | Volts   |

| +5V Supply (pin 18)      | -0.5 | —    | +7   | Volts   |

| Analog Inputs ①          | -35  | —    | +35  | Volts   |

| Digital Inputs           | -0.5 | —    | +7   | Volts   |

| Thermal Resistances:     |      |      |      |         |

| Junction-Case            | —    | _    | 15   | °C/Watt |

| Case-Ambient             | —    | —    | 15   | °C/Watt |

| Junction-Ambient         | —    | _    | 30   | °C/Watt |

| Lead Temp. (10 seconds)  | _    | _    | 300  | °C      |

### FUNCTIONAL SPECIFICATIONS

(The following specifications apply over the operating temperature range and power supply range unless otherwise indicated.)

| ANALOG INPUTS                 | MIN.            | TYP.             | MAX.        | UNITS    |

|-------------------------------|-----------------|------------------|-------------|----------|

| Signal Range, Unipolar        |                 |                  |             |          |

| Gain = 1                      | 0               | _                | +10         | Volts    |

| Gain = 200                    |                 | _                | +50         | mV       |

| Signal Range, Bipolar         |                 |                  |             |          |

| Gain = 1                      | -10             | _                | +10         | Volts    |

| Gain = 200                    | -50             | _                | +50         | mV       |

| Input Gain Equation ②         | 6               | Gain = 1 + (     | 20kΩ/RGAI   | N)       |

| Gain Equation Error           | _               | _                | ±0.1        | %        |

| Instrumentation Amplifier     |                 |                  |             |          |

| Input Impedance               | 10 <sup>8</sup> | 10 <sup>12</sup> | _           | Ohms     |

| Input Bias Current:           |                 |                  |             |          |

| +25°C                         | _               | _                | ±250        | pА       |

| –55 to +125°C                 |                 | Doubles e        | very 10°C   |          |

| Input Offset Current:         |                 |                  |             |          |

| +25°C                         | _               | _                | ±1          | nA       |

| –55 to +125°C                 |                 | Doubles e        | very 10°C   |          |

| Multiplexer                   |                 |                  |             |          |

| Channel ON Resistance         | _               | _                | 2           | kΩ       |

| Channel OFF Input Leakage     | _               | ±30              | _           | pА       |

| Channel OFF Output Leakage    | _               | ±1               | _           | nA       |

| Channel ON Leakage            | _               | ±100             | _           | pА       |

| Input Capacitance             |                 |                  | ĺ           |          |

| HDAS-16, Channel ON           | _               | 100              | _           | pF       |

| HDAS-8, Channel ON            | _               | 50               | _           | pF       |

| +25°C, Channel OFF            | _               | 5                | _           | pF       |

| Input Offset Voltage          |                 |                  |             |          |

| Gain = 1, +25°C               | —               |                  | ±2          | mV       |

| –55 to +125°C (max.)          | (±3)            | opm/°C x G       | ain) ±20ppı | n/°C     |

| <b>Gain = 200,</b> +25°C      |                 |                  | ±100        | mV       |

| –55 to +125°C (max.)          | (±3)            | opm/°C x G       | ain) ±20ppı | n/°C     |

| Common Mode Range             | ±10             | _                | —           | Volts    |

| CMRR, Gain = 1, at 60Hz       | 70              | 82               | —           | dB       |

| Input Voltage Noise, Gain = 1 |                 |                  |             |          |

| (Referred to input)           |                 | 150              | 200         | μVrms    |

| Channel Crosstalk             |                 | _                | -80         | dB       |

| PERFORMANCE                   |                 |                  |             |          |

| Resolution                    | 12              | _                | —           | Bits     |

| Integral Nonlinearity         |                 |                  |             |          |

| 0 to +70°C                    |                 |                  | ±1          | LSB      |

| –55 to +125°C                 |                 | _                | ±1          | LSB      |

| Differential Nonlinearity     |                 |                  |             |          |

| 0 to +70°C                    |                 | _                | ±1          | LSB      |

| –55 to +125°C                 |                 | _                | ±1          | LSB      |

| No Missing Codes              | Over th         | e operating      | temperatu   | re range |

# HDAS-16, HDAS-8

12-Bit, 50kHz, Complete Data Acquisition Systems

| PERFORMANCE (CONT.)               | MIN.         | TYP.            | MAX.   | UNITS         |

|-----------------------------------|--------------|-----------------|--------|---------------|

| Unipolar Zero Error               |              |                 |        |               |

| +25°C 3                           |              |                 | ±0.1   | %FSR          |

| –55 to +125°C                     |              | -               | ±0.3   | %FSR          |

| Bipolar Zero Error                |              |                 |        |               |

| +25°C 3                           | —            | —               | ±0.1   | %FSR          |

| –55 to +125°C                     |              | —               | ±0.3   | %FSR          |

| Bipolar Offset Error              |              |                 |        |               |

| +25°C ③                           |              | _               | ±0.1   | %FSR          |

| –55 to +125°C                     |              | _               | ±0.3   | %FSR          |

| Gain Error                        |              | 1               |        | 1             |

| +25°C ③                           |              | _               | ±0.2   | %             |

| –55 to +125°C                     |              | _               | ±0.3   | %             |

| DYNAMIC CHARACTERISTICS           |              |                 |        |               |

| Acquisition Time, Gain = 1        |              |                 |        |               |

| +25°C                             |              | 9               | 10     | μs            |

| -55 to +125°C                     |              | 5               | 15     | μs<br>μs      |

| Aperture Delay Time               |              |                 | 500    | · ·           |

|                                   |              |                 |        | ns            |

| Aperture Uncertainty              |              |                 | 1      | ns<br>uV/uo   |

| S/H Droop Rate                    |              |                 | ±1     | μV/μs         |

| Feedthrough                       |              | _               | ±0.01  | %             |

| A/D Conversion Time               | 1            |                 |        | 1             |

| +25°C                             |              | 6               | 8      | μs            |

| –55 to +125°C                     |              | -               | 10     | μs            |

| Throughput Rate                   |              |                 |        | ,             |

| +25°C                             | 50           | 66              |        | kHz           |

| –55 to +125°C                     | 33           | —               | —      | kHz           |

| DIGITAL INPUTS                    |              |                 |        |               |

| Logic Levels                      |              |                 |        |               |

| (Pins 8, 13-16, 19-21, 26, 31)    |              |                 |        |               |

| Logic 1                           | +2.0         | —               | +5.5   | Volts         |

| Logic O                           | 0            | _               | +0.8   | Volts         |

| (Pin 5)                           |              |                 |        |               |

| Logic 1                           | +4.0         | _               | +5.5   | Volts         |

| Logic 0                           | 0            | _               | +0.8   | Volts         |

| Logic Loading                     | I            | 1               | 1      |               |

| (Pins 5, 8, 13–16, 19–21, 26, 31) |              |                 |        |               |

| Logic 1                           |              | _               | ±10    | μA            |

| Logic 0                           |              | _               | ±10    | μA            |

| Multiplexer Address Set-upTime    | 20           | _               |        | ns            |

| ENABLE to Data Valid Delay        |              | 20              | 30     | ns            |

| STROBE @                          | 40           |                 |        | n             |

| OUTPUTS                           | 40           |                 |        |               |

| Logic Levels (Output Data)        |              |                 |        |               |

| Logic 1                           | +2.4         | 1               |        | Volts         |

|                                   |              |                 |        |               |

| Logic 1 (pin 7)                   | +2.5         |                 |        | Volts         |

| Logic 0                           |              | -               | +0.4   | Volts         |

| (Pins 9, 10, 11, and 12)          |              | 1               |        |               |

| Logic 1                           | +2.5         |                 | —      | Volts         |

| Logic O                           | —            | -               | +0.4   | Volts         |

| Logic Loading                     |              |                 |        | ,             |

| Logic 1                           |              | -               | -400   | μA            |

| Logic 0                           | _            |                 | +4     | mA            |

| Internal Reference:               |              |                 |        |               |

| Voltage, +25°C                    | +9.99        | +10.00          | +10.01 | Volts         |

| Drift                             | _            | —               | ±20    | ppm/°C        |

| External Current                  |              | _               | 1      | mA            |

| Output Data Coding                | Straight hir | nary (unipolar) |        | 1             |

| Calput Data County                | Satugit bil  |                 |        | ~ J (pipoidi) |

www.murata-ps.com

## HDAS-16, HDAS-8

### 12-Bit, 50kHz, Complete Data Acquisition Systems

| POWER REQUIREMENTS MIN. TYP. MAX. UNI |                     |                         |        |       |  |

|---------------------------------------|---------------------|-------------------------|--------|-------|--|

| Power Supply Ranges                   |                     |                         |        |       |  |

| +15V Supply                           | +14.25              | +15.0                   | +15.75 | Volts |  |

| -15V Supply                           | -14.25              | -15.0                   | -15.75 | Volts |  |

| +5V Supply                            | +4.75               | +5.0                    | +5.25  | Volts |  |

| Power Supply Currents                 |                     |                         |        |       |  |

| +15V Supply                           | —                   | —                       | +33    | mA    |  |

| –15V Supply                           | —                   | —                       | -30    | mA    |  |

| +5V Suppy                             | —                   | —                       | +15    | mA    |  |

| Power Dissipation                     | —                   | —                       | 1.25   | Watts |  |

| PHYSICAL/ENVIRONMENTAL                |                     |                         |        |       |  |

| Operating Temp. Range, Case           |                     |                         |        |       |  |

| MC Models                             | 0                   | —                       | +70    | °C    |  |

| MM/883 Models                         | -55                 | —                       | +125   | °C    |  |

| Storage Temperature Range             | -65                 | _                       | +150   | °C    |  |

| Weight                                | 1                   | 1.4 ounces (39.7 grams) |        |       |  |

| Package Type                          | 62-pin cermanic DIP |                         |        |       |  |

Footnotes:

- ① Analog inputs will withstand ±35V with power on. If the power is off, the maximum safe input (no damage) is ±20V.

- ② The gain equation error is guaranteed before external trimming and applies at gains less than 50. This error increases at gains over 50.

Adjustable to zero.

④ STROBE pulse width must be less than EOC period to achieve maximum throughput rate.

### **TECHNICAL NOTES**

- 1. Input channels are protected to 20 Volts beyond the powersupplies. All digital output pins have one second short-circuit protection.

- To retain high system throughput rates while digitizing low-level signals, apply external high-gain amplifiers foreach channel. MPS's AM-551 is suggested for such amplifier-per-channel applications.

- The HDAS devices have self-starting circuits for free-running sequential operation. If, however, in a power-upcondition the supply voltage slew rate is less than 3V per microsecond, the free running state might not be initialized. Apply a negative pulse to the STROBE, to eliminate this condition.

- 4. For unipolar operation, connect BIPOLAR INPUT (pin 38) to S/H OUT (pin 39). For bipolar operation, connect BIPOLAR INPUT (pin 38) to +10V REFERENCE OUT (pin 40).

- 5. RDELAY may be a standard value 5% carbon composition or film-type resistor.

- RGAIN must be very accurate with low temperature coefficients. If necessary, fabricate the gain resistor from a precision metal-film type in series with a low value trim resistor or potentiometer. The total resistor temperature coefficient must be no greater than ±10ppm/°C.

- ANALOG SIGNAL COMMON, POWER COMMON and DIGITAL COMMON are connected internally. For optimal performance, tie all ground pins (17, 41, 42, 45, 46) directly to a large analog ground plane beneath the package.

- 8. For HDAS-16, tie pin 50 to a "signal source common" if possible. Otherwise tie pin 50 to pin 41 (ANA SIG COM).

| PIN NO.<br>1                           | HDAS-16                                         | HDAS-8                                                               |

|----------------------------------------|-------------------------------------------------|----------------------------------------------------------------------|

|                                        | CH3 IN                                          | CH3 HIGH IN                                                          |

| 2                                      | CH3 IN<br>CH2 IN                                | CH3 HIGH IN                                                          |

| 3                                      | CH2 IN<br>CH1 IN                                | CH2 HIGH IN<br>CH1 HIGH IN                                           |

| 4                                      |                                                 | CHI HIGH IN<br>CHO HIGH IN                                           |

|                                        | CHO IN                                          | CHU HIGH IN                                                          |

| 5                                      | MUX ENABLE                                      | *                                                                    |

| 6                                      | RDELAY                                          | *                                                                    |

| 7                                      | EOC                                             | *                                                                    |

| 8                                      | STROBE                                          | *                                                                    |

| 9                                      | A8 MULTIPLEXER                                  |                                                                      |

| 10                                     | A4 ADDRESS                                      | *                                                                    |

| 11                                     | A2 OUT                                          | *                                                                    |

| 12                                     | A1                                              | *                                                                    |

| 13                                     | RA8 MULTIPLEXER                                 | *                                                                    |

| 14                                     | RA4 ADDRESS                                     | *                                                                    |

| 15                                     | RA2 IN                                          | *                                                                    |

| 16                                     | RA1                                             | *                                                                    |

| 17                                     | DIGITAL COMMON                                  | *                                                                    |

| 18                                     | +5V SUPPLY                                      | *                                                                    |

| 19                                     | LOAD                                            | *                                                                    |

| 20                                     | CLEAR                                           | *                                                                    |

| 21                                     | ENABLE (Bits 9–12)                              | *                                                                    |

| 22                                     | BIT 12 (LSB)                                    | *                                                                    |

| 23                                     | BIT 11                                          | *                                                                    |

| 24                                     | BIT 10                                          | *                                                                    |

| 25                                     | BIT 9                                           | *                                                                    |

| 26                                     | ENABLE (Bits 5–8)                               | *                                                                    |

| 27                                     | BIT 8                                           | *                                                                    |

| 28                                     | BIT 7                                           | *                                                                    |

| 29                                     | BIT 6                                           | *                                                                    |

| 30                                     | BIT 5                                           | *                                                                    |

| 31                                     | ENABLE (Bits 1–4)                               | *                                                                    |

| 32                                     | BIT 4                                           | *                                                                    |

| 33                                     | BIT 3                                           | *                                                                    |

| 34                                     | BIT 2                                           | *                                                                    |

| 35                                     | BIT 1 (MSB)                                     | *                                                                    |

| 36                                     | GAIN ADJUST                                     | *                                                                    |

| 37                                     | OFFSET ADJUST                                   | *                                                                    |

| 38                                     | BIPOLAR INPUT                                   | *                                                                    |

| 39                                     | SAMPLE/HOLD OUT                                 | *                                                                    |

| 40                                     | +10V REFERENCE OUT                              | *                                                                    |

| 40                                     | ANALOG SIGNAL COMMON                            | *                                                                    |

| 41                                     | ANALOG POWER COMMON                             | *                                                                    |

| 42                                     | +15V SUPPLY                                     |                                                                      |

| 43                                     | -15V SUPPLY                                     | *                                                                    |

| 44                                     | ANALOG SIGNAL COMMON                            | *                                                                    |

| 45                                     | ANALOG SIGNAL COMMON                            | *                                                                    |

| 46                                     | RGAIN LOW                                       | *                                                                    |

| 47                                     | RGAIN LOW                                       | *                                                                    |

|                                        |                                                 | *                                                                    |

| 49                                     | AMP. IN HIGH                                    | *                                                                    |

| 50                                     | AMP. IN LOW                                     |                                                                      |

| 51                                     | CH15 IN                                         | CH7 LOW IN                                                           |

| 52                                     | CH14 IN                                         | CH6 LOW IN                                                           |

| 50                                     | CH13 IN                                         | CH5 LOW IN                                                           |

| 53                                     | CH12 IN                                         | CH4 LOW IN                                                           |

| 54                                     |                                                 |                                                                      |

| 54<br>55                               | CH11 IN                                         | CH3 LOW IN                                                           |

| 54<br>55<br>56                         | CH10 IN                                         | CH2 LOW IN                                                           |

| 54<br>55<br>56<br>57                   | CH10 IN<br>CH9 IN                               | CH2 LOW IN<br>CH1 LOW IN                                             |

| 54<br>55<br>56<br>57<br>58             | CH10 IN<br>CH9 IN<br>CH8 IN                     | CH2 LOW IN<br>CH1 LOW IN<br>CH0 LOW IN                               |

| 54<br>55<br>56<br>57<br>58<br>59       | CH10 IN<br>CH9 IN<br>CH8 IN<br>CH7 IN           | CH2 LOW IN<br>CH1 LOW IN<br>CH0 LOW IN<br>CH7 HIGH IN                |

| 54<br>55<br>56<br>57<br>58<br>59<br>60 | CH10 IN<br>CH9 IN<br>CH8 IN<br>CH7 IN<br>CH6 IN | CH2 LOW IN<br>CH1 LOW IN<br>CH0 LOW IN<br>CH7 HIGH IN<br>CH6 HIGH IN |

| 54<br>55<br>56<br>57<br>58<br>59       | CH10 IN<br>CH9 IN<br>CH8 IN<br>CH7 IN           | CH2 LOW IN<br>CH1 LOW IN<br>CH0 LOW IN<br>CH7 HIGH IN                |

\*Same as HDAS-16

Caution: Pins 49 and 50 do not have overvoltage protection; therefore, protected multiplexers, such as MPS's MX-1606 and MX-808 are recommended. See the General Operation description.

# HDAS-16, HDAS-8

12-Bit, 50kHz, Complete Data Acquisition Systems

#### **Table 1. Description of Pin Functions**

| FUNCTION                    | LOGIC STATE                                                                                                                                                 | DESCRIPTION                                                                                  |  |  |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--|--|

| DIGITAL INPUTS              |                                                                                                                                                             |                                                                                              |  |  |

| STROBE                      | 1 to 0                                                                                                                                                      | Initiates acquisition and conversion of<br>analog signal                                     |  |  |

| LOAD                        | 0                                                                                                                                                           | Random address mode initiated on falling edge of STROBE                                      |  |  |

|                             | 1                                                                                                                                                           | Sequential address mode                                                                      |  |  |

| CLEAR                       | 0                                                                                                                                                           | Allows next STROBE pulse to reset<br>MULTIPLEXER ADDRESS to CHO overrid-<br>ing LOAD COMMAND |  |  |

| MUX ENABLE                  | 0                                                                                                                                                           | Disables internal multiplexer                                                                |  |  |

|                             | 1                                                                                                                                                           | Enables internal multiplexer                                                                 |  |  |

| MUX ADDRESS IN              |                                                                                                                                                             | Selects channel for random address mode 8, 4, 2, 1 natural binary coding                     |  |  |

| DIGITAL OUTPUTS             |                                                                                                                                                             |                                                                                              |  |  |

| EOC (STATUS)                | 0                                                                                                                                                           | Conversion complete                                                                          |  |  |

|                             | 1                                                                                                                                                           | Conversion in process                                                                        |  |  |

| ENABLE (1-4)                | 0                                                                                                                                                           | Enables three-state outputs bits 1-4                                                         |  |  |

|                             | 1                                                                                                                                                           | Disables three-state outputs bits 1-4                                                        |  |  |

| ENABLE (5-8)                | 0                                                                                                                                                           | Enables three-state outputs bits 5-8                                                         |  |  |

|                             | 1                                                                                                                                                           | Disables three-state outputs bits 5-8                                                        |  |  |

| ENABLE (9–12)               | 0                                                                                                                                                           | Enables three-state outputs bits 9-12                                                        |  |  |

|                             | 1                                                                                                                                                           | Disables three-state outputs bits 9-12                                                       |  |  |

| MUX ADDRESS OUT             |                                                                                                                                                             | Output of multiplexer address register<br>8, 4, 2, 1 natural binary coding                   |  |  |

| ANALOG INPUTS               |                                                                                                                                                             | DESCRIPTION                                                                                  |  |  |

| CHANNEL INPUTS              | Limit voltage to                                                                                                                                            | o $\pm 20V$ beyond power supplies                                                            |  |  |

| BIPOLAR INPUT               |                                                                                                                                                             | peration, connect to pin 39 (S/H OUT). For<br>on, connect to in 40 (+10V OUT)                |  |  |

| amp. In Low<br>Amp. In High |                                                                                                                                                             | direct inputs to the instrumentation<br>(ternal channel expansion beyond 16SE<br>S.          |  |  |

| ANALOG OUTPUTS              |                                                                                                                                                             |                                                                                              |  |  |

| S/H OUT                     | Sample/hold o                                                                                                                                               | utput                                                                                        |  |  |

| +10V REFERENCE OUT          | Buffered +10V                                                                                                                                               | reference output                                                                             |  |  |

| ADJUSTMENT PINS             |                                                                                                                                                             |                                                                                              |  |  |

| ANALOG SIGNAL COMMON        | Low level anal                                                                                                                                              | og signal return                                                                             |  |  |

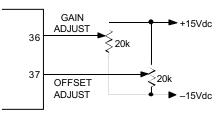

| GAIN ADJUSTMENT             | External gain a                                                                                                                                             | djustment. See calibration instructions.                                                     |  |  |

| OFFSET ADJUSTMENT           | External offset                                                                                                                                             | adjustment. See calibration instructions.                                                    |  |  |

| RGAIN                       | Optional gain s<br>when left open                                                                                                                           | selection point. Factory adjusted for $G = 1$ h.                                             |  |  |

| RDELAY                      | Optional acquisition time adjustment when connected<br>to +5V. Factory adjusted for 9µs. Must be connected to<br>+5V either directly or through a resistor. |                                                                                              |  |  |

### **Table 2. Calibration Table**

| UNIPOLAR RANGE | ADJUST         | INPUT VOLTAGE        |

|----------------|----------------|----------------------|

| 0 to +5V       | ZERO<br>GAIN   | +0.6mV<br>+4.9982V   |

| 0 to +10V      | ZERO<br>GAIN   | +1.2mV<br>+9.9963V   |

| BIPOLAR RANGE  |                |                      |

| ±2.5V          | OFFSET<br>GAIN | -2.4994V<br>+2.4982V |

| ±5V            | OFFSET<br>GAIN | -4.9988V<br>+4.9963V |

| ±10V           | OFFSET<br>GAIN | -9.9976V<br>+9.9927V |

### **Calibration Procedures**

- 1. Offset and gain adjustments are made by connecting two 20k trim potentiometers as shown in Figure 2.

- Connect a precision voltage source to pin 4 (CH0 IN). If the HDAS-8 is used, connect pin 58 (CH0 LOW IN) to analog ground. Ground pin 20 (CLEAR) and momentarily short pin8 (STROBE). Trigger the A/D by connecting pin 7 (EOC) to pin 8 (STROBE). Select proper value for RGAIN and RDELAY by referring to Table 3.

- 3. Adjust the precision voltage source to the value shown in Table 2 for the unipolar zero adjustment (ZERO + 1/2LSB)or the bipolar offset adjustment (-FS + 1/2LSB). Adjust the offset trim potentiometer so that the output code flickers equally between 0000 0000 0000 and 0000 0000 0001.

- 4. Change the output of the precision voltage source to the value shown in Table 2 for the unipolar or bipolar gain adjustment (+FS – 1 1/2LSB). Adjust the gain trim potentiometer so that the output flickers equally between 1111 1111 1110 and 1111 1111 1111.

Figure 2. External Adjustment

#### **GENERAL OPERATION**

The HDAS devices accept either 16 single-ended or 8 differential input signals. For single-ended circuits, the AMP INLOW (pin 50) input to the instrumentation amplifier must terminate at ANALOG SIGNAL COMMON (pin 41). For differential circuits, both the HIGH and LOW signal inputs must terminate externally for each channel. Tie unused channels to the ANALOG SIGNAL COMMON (pin 41). To obtain additional channels, connect external multiplexers to the AMP IN HIGH (pin 49) and AMP IN LOW (pin 50). Using this scheme, the HDAS-16 can provide 32 single-ended expansion channels. MPS's MX Series multiplexers are recommended.

# HDAS-16, HDAS-8

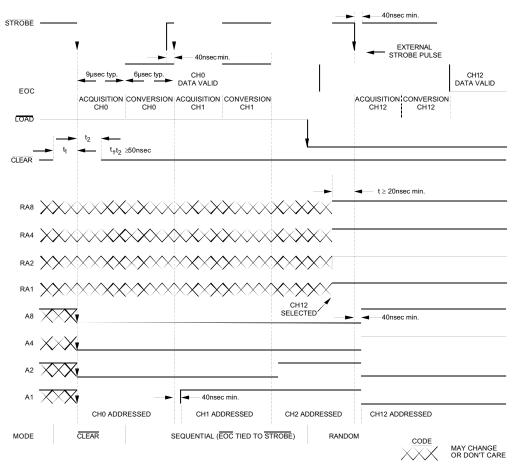

The acquisition time is the amount of time the multiplexer, instrumentation amplifier, and sample/hold require to settle within a specified range of accuracy after  $\overline{STROBE}$  (pin 8)goes low. The acquisition time period can be observed by measuring how long  $\overline{EOC}$  is low after the falling edge of  $\overline{STROBE}$  (see Figure 4). For higher gains, increase the acquisition time. Do this by connecting a resistor from RDELAY (pin 6) to +5V (pin 18). An external resistor, RGAIN, can be added to increase the gain value. The gain is equal to 1 without an RGAIN resistor. Table 3 refers to the appropriate RDELAY and RGAIN resistors required for various gains.

The HDAS devices enter the hold mode and are ready for conversion as soon as the one-shot (controling acquisition time) times out. An internal clock is gated ON, and a start-convert pulse is sent to the 12-bit A/D converter,

### 12-Bit, 50kHz, Complete Data Acquisition Systems

driving the EOC output high. The HDAS devices can be configured for either bipolar or unipolar operation (see Table 2). The conversion is complete within a maximum of 10 microseconds. The EOC now returns low, the data is valid and sent to the three-state output buffers. The sample/hold amplifier is now ready to acquire new data. The next falling edge of the STROBE pulse repeats the process for the next conversion.

### **Multiplexer Addressing**

The HDAS devices can be configured in either random orsequential addressing modes. Refer to Table 5 and the subsequent descriptions. The number of channels sequentially addressed can be truncated using the MUX ADDRESS OUT(pins 9, 10, 11 and 12) and appropriate decoding circuitry forthe highest channel desired. The decoding circuit can drive the CLEAR (pin 20) function low to reset the addressing to channel 0.

### Table 3. Input Range Parameters (Typical)

| INPUT<br>Range ① ② | GAIN | RGAIN (Ω) | RDELAY (Ω) ③ | THROUGHPUT @ | SYSTEM ACCURACY<br>(% OF FSR) |

|--------------------|------|-----------|--------------|--------------|-------------------------------|

| ±10V               | 1    | OPEN      | 0 (SHORT)    | 66.6kHz      | ±0.009                        |

| ±5V                | 2    | 20.0k     | 0 (SHORT)    | 66.6kHz      | ±0.009                        |

| ±2.5V              | 4    | 6.667k    | 0 (SHORT)    | 66.6kHz      | ±0.009                        |

| ±1V                | 10   | 2.222k    | 0 (SHORT)    | 66.6kHz      | ±0.009                        |

| ±200mV             | 50   | 408.2     | 7k           | 40.0kHz      | ±0.010                        |

| ±100mV             | 100  | 202.0     | 21k          | 25.6kHz      | ±0.011                        |

| ±50mV              | 200  | 100.5     | 51k          | 14.5kHz      | ±0.016                        |

Notes

$\begin{array}{l} \text{RGAIN} \left(\Omega\right) = \underbrace{20,000}_{\text{(GAIN}-1)} \\ \text{RDELAY} \left(\Omega\right) = \left[\text{Total Acquisition Delay (µs) x 1000}\right] - 9000 \end{array}$

① The analog input range to the A/D converter is 0 to +10V for unipolar signals and ±10V for bipolar signals.

0 Full scale can be accommodated for analog signal ranges of  $\pm 50 mV$  to  $\pm 10 V.$

③ For gains between 1 and 10, RDELAY (pin 6) must be shorted to +5V (pin 18).

④ Throughput period equals acquisition and settling delay, plus A/D conversion period (10 microseconds maximum).

#### Table 5. Mux Channel Addressing

|               | PIN |        |        |     |               |                    |

|---------------|-----|--------|--------|-----|---------------|--------------------|

|               |     | MUX AI | DDRESS | Ę   |               |                    |

| 5             | 13  | 14     | 15     | 16  | ON<br>Channel |                    |

| MUX<br>Enable | RA8 | RA4    | RA2    | RA1 | ΉÐ            |                    |

| 0             | Х   | Х      | Х      | Х   | NONE          |                    |

| 1             | 0   | 0      | 0      | 0   | 0             |                    |

| 1             | 0   | 0      | 0      | 1   | 1             |                    |

| 1             | 0   | 0      | 1      | 0   | 2             | HDAS-8             |

| 1             | 0   | 0      | 1      | 1   | 3             | (3-BIT             |

| 1             | 0   | 1      | 0      | 0   | 4             | ADDRESS)           |

| 1             | 0   | 1      | 0      | 1   | 5             |                    |

| 1             | 0   | 1      | 1      | 0   | 6             |                    |

| 1             | 0   | 1      | 1      | 1   | 7             |                    |

| 1             | 1   | 0      | 0      | 0   | 8             |                    |

| 1             | 1   | 0      | 0      | 1   | 9             |                    |

| 1             | 1   | 0      | 1      | 0   | 10            |                    |

| 1             | 1   | 0      | 1      | 1   | 11            | HDAS-16            |

| 1             | 1   | 1      | 0      | 0   | 12            | (4-BIT<br>ADDRESS) |

| 1             | 1   | 1      | 0      | 1   | 13            |                    |

| 1             | 1   | 1      | 1      | 0   | 14            |                    |

| 1             | 1   | 1      | 1      | 1   | 15            |                    |

### **Table 4. Output Coding**

|            | STI       | RAIGHT BIN/ | ARY  |            |      |

|------------|-----------|-------------|------|------------|------|

| INPUT      | 0 to +10V | 0 to +5V    | MSB  |            | LSB  |

| +FS – 1LSB | +9.9976   | +4.9988     | 1111 | 1111       | 1111 |

| +1/2FS     | +5.0000   | +2.5000     | 1000 | 0000       | 0000 |

| +1LSB      | +0.0024   | +0.0012     | 0000 | 0000       | 0001 |

| ZERO       | 0.0000    | 0.0000      | 0000 | 0000       | 0000 |

|            | BIPOLAR   |             | OF   | FSET BINAR | Y*   |

| INPUT      | ±10V      | ±5V         | MSB  |            | LSB  |

| +FS – 1LSB | +9.9951   | +4.9976     | 1111 | 1111       | 1111 |

| +1/2FS     | +5.0000   | +2.5000     | 1100 | 0000       | 0000 |

| +1LSB      | +0.0049   | +0.0024     | 1000 | 0000       | 0001 |

| ZERO       | 0.0000    | 0.0000      | 1000 | 0000       | 0000 |

| –FS + 1LSB | -9.9951   | -4.9976     | 0000 | 0000       | 0001 |

| –FS        | -10.000   | -5.0000     | 0000 | 0000       | 0000 |

\* For 2's complement coding, add an inverter to the MSB line.

# HDAS-16, HDAS-8

### **Random Addressing**

Set pin 19 (LOAD) to logic 0. The next falling edge of STROBE will load the MUX CHANNEL ADDRESS present on pin 13 to pin 16. Digital address inputs must be stable 20ns before andafter falling edge of the STROBE pulse.

### Free Running Sequential Addressing

Set pin 19 ( $\overline{\text{LOAD}}$ ) and pin 20 ( $\overline{\text{CLEAR}}$ ) to logic 1 or leave open. Connect pin 7 ( $\overline{\text{EOC}}$ ) to pin 8 ( $\overline{\text{STROBE}}$ ). The fallingedge of  $\overline{\text{EOC}}$  will increment channel address. This means thatwhen the  $\overline{\text{EOC}}$  is low, the digital output data is valid for theprevious channel (CHn – 1) rather than the channel indicated on MUX ADDRESS OUTPUT. The HDAS will continually scan all channels.

Example: CH4 has been addressed and a conversion takes place. The  $\overline{EOC}$  goes low. That channel's (CH4's) data becomes valid, but MUX ADDRESS OUTPUT is now CH5.

### **Triggered Sequential Addressing**

Set pin 19 (LOAD) and pin 20 (CLEAR) to logic 1 or leaveopen. Apply a falling edge trigger pulse to pin 8 (STROBE). This negative transition causes the con-

12-Bit, 50kHz, Complete Data Acquisition Systems tents of the address counter to be incremented by one, followed by an A/D conversion in 9 microseconds.

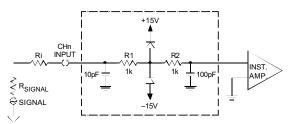

#### **Input Voltage Protection**

As shown in Figure 3, the multiplexer has reversed biased diodes which protect the input channels from being damaged by overvoltage signals. The HDAS input channels areprotected up to 20V beyond the supplies and can be increasedby adding series resistors (Ri) to each channel. The input resistor must limit the current flowing through the protection diodes to 10mA.

The value of Ri for a specific voltage protection range (Vp) can be calculated by the following formula:

Vp = (Rsignal + Ri + Ron) (10mA) where Ron = 2k

NOTE: Increased input series resistance will increase multiplexer settling time significantly.

Figure 3. Multiplexer Equivalent Circuit

Figure 4. HDAS Timing Diagram

www.murata-ps.com

## HDAS-16, HDAS-8

### 12-Bit, 50kHz, Complete Data Acquisition Systems

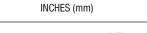

Mechnical Dimensions

| ORDERING INFORMATION                                                                                                                                                                                         |                       |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|--|--|

| Model No. *                                                                                                                                                                                                  | Operating Temp. Range |  |  |  |

| HDAS-16MC                                                                                                                                                                                                    | 0 to +70°C            |  |  |  |

| HDAS-16MM                                                                                                                                                                                                    | -55 to +125°C         |  |  |  |

| HDAS-16/883                                                                                                                                                                                                  | -55 to +125°C         |  |  |  |

| [                                                                                                                                                                                                            |                       |  |  |  |

| HDAS-8MC                                                                                                                                                                                                     | 0 to +70°C            |  |  |  |

| HDAS-8MM                                                                                                                                                                                                     | -55 to +125°C         |  |  |  |

| HDAS-8/883                                                                                                                                                                                                   | -55 to +125°C         |  |  |  |

| Receptacle for PC board mounting can be ordered through AMP Inc.,<br>Part #3-331272-4 (Component Lead Spring Socket), 62 required.<br>Contact Murata Power Solutions for MIL-STD-883 product specifications. |                       |  |  |  |

110 .

\*For RoHS compliance a "-C" is added to model numbers above.

## muRata Ps Murata Power Solutions

Murata Power Solutions, Inc.

11 Cabot Boulevard, Mansfield, MA 02048-1151 U.S.A.

Tel: (508) 339-3000 (800) 233-2765 Fax: (508) 339-6356

www.murata-ps.com email:sales@murata-ps.com ISO 9001 and 14001 REGISTERED 07/29/09

Murata Power Solutions, Inc. makes no representation that the use of its products in the circuits described herein, or the use of other technical information contained herein, will not infringe upon existing or future patent rights. The descriptions contained herein do not imply the granting of licenses to make, use, or sell equipment constructed in accordance therewith. Specifications are subject to change without notice.

| L | USA:       | Manstield (MA), Iel: (508) 339-3000, email: sales@murata-ps.com                                                                    |

|---|------------|------------------------------------------------------------------------------------------------------------------------------------|

| L | Canada:    | Toronto, Tel: (866) 740-1232, email: toronto@murata-ps.com                                                                         |

| L | UK:        | Milton Keynes, Tel: +44 (0)1908 615232, email: mk@murata-ps.com                                                                    |

| L | France:    | Montigny Le Bretonneux, Tel: +33 (0)1 34 60 01 01, email: france@murata-ps.com                                                     |

| L | Germany:   | München, Tel: +49 (0)89-544334-0, email: munich@murata-ps.com                                                                      |

|   | Japan:     | Tokyo, Tel: 81-3-3779-1031, email: japan@murata-ps.com<br>Kyoto, Tel: 81-75-955-7269, email: japan@murata-ps.com                   |

|   | China:     | Shanghai, Tel: +86 215 027 3678, email: shanghai@murata-ps.com<br>Guangzhou, Tel: +86 208 221 8066, email: guangzhou@murata-ps.com |

|   | Singapore: | Parkway Centre, Tel: +65 6348 9096, email: singapore@murata-ps.com                                                                 |

|   |            | ······································                                                                                             |

Manafield (MA) Tal. (E00) 220, 2000, amail, aplan@murata no apr

www.murata-ps.com