### INTEGRATED CIRCUITS

# DATA SHEET

# PCA9500 8-bit I<sup>2</sup>C and SMBus I/O port with 2-kbit EEPROM

Product data sheet Supersedes data of 27 Jun 2003

### 8-bit I<sup>2</sup>C and SMBus I/O port with 2-kbit EEPROM

**PCA9500**

#### **FEATURES**

- 8 general purpose input/output expander/collector

- Drop in replacement for PCF8574 with integrated 2-kbit EEPROM

- Internal 256 × 8 EEPROM

- Self timed write cycle

- 4 byte page write operation

- I2C and SMBus interface logic

- Internal power-on reset

- Noise filter on SCL/SDA inputs

- 3 address pins allowing up to 8 devices on the I<sup>2</sup>C/SMBus

- No glitch on power-up

- Supports hot insertion

- Power-up with all channels configured as inputs

- Low standby current

- Operating power supply voltage range of 2.5 V to 3.6 V

- 5 V tolerant inputs/outputs

- 0 kHz to 400 kHz clock frequency

- ESD protection exceeds 2000 V HBM per JESD22-A114, 200 V MM per JESD22-A115 and 1000 V CDM per JESD22-C101

- Latch-up testing is done to JESDEC Standard JESD78 which exceeds 100 mA

- Package offerred: SO16, TSSOP16, HVQFN16

#### **DESCRIPTION**

The PCA9500 is an 8-bit I/O expander with an on-board 2-kbit EEPROM.

The I/O expander's eight quasi bidirectional data pins can be independently assigned as inputs or outputs to monitor board level status or activate indicator devices such as LEDs. The system master writes to the I/O configuation bits in the same way as for the PCF8574. The data for each Input or Output is kept in the corresponding Input or Output register. The system master can read all registers.

The EEPROM can be used to store error codes or board manufacturing data for read-back by application software for diagnostic purposes and is included in the I/O expander package.

The PCA9500 has three address pins with internal pull-up resistors allowing up to 8 devices to share the common two-wire I<sup>2</sup>C software protocol serial data bus. The fixed GPIO I<sup>2</sup>C address is the same as the PCF8574 and the fixed EEPROM I<sup>2</sup>C address is the same as the PCF8582C-2, so the PCA9500 appears as two separate devices to the bus master.

The PCA9500 supports hot insertion to facilitate usage in removable cards on backplane systems.

The PCA9501 is an alternative to the functionally similar PCA9500 for systems where a higher number of devices are required to share the same  $I^2$ C-bus or an interrupt output is required.

#### ORDERING INFORMATION

| PACKAGES                 | TEMPERATURE RANGE | ORDER CODE | TOPSIDE MARK | DRAWING NUMBER |

|--------------------------|-------------------|------------|--------------|----------------|

| 16-Pin Plastic SO (wide) | –40 °C to +85 °C  | PCA9500D   | PCA9500D     | SOT162-1       |

| 16-Pin Plastic TSSOP     | –40 °C to +85 °C  | PCA9500PW  | PCA9500      | SOT403-1       |

| 16-Pin Plastic HVQFN     | -40 °C to +85 °C  | PCA9500BS  | 9500         | SOT629-1       |

Standard packing quantities and other packaging data are available at www.standardproducts.philips.com/packaging. SMBus as specified by the Smart Battery System Implementers Forum is a derivative of the Philips I<sup>2</sup>C patent. I<sup>2</sup>C is a trademark of Philips Semiconductors Corporation.

### 8-bit I<sup>2</sup>C and SMBus I/O port with 2-kbit EEPROM

PCA9500

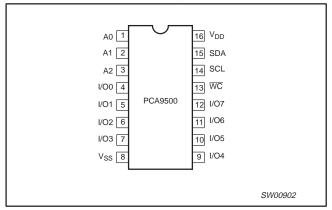

#### PIN CONFIGURATION - SO, TSSOP

Figure 1. Pin configuration - SO, TSSOP

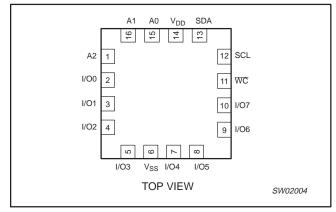

#### **PIN CONFIGURATION – HVQFN**

Figure 2. Pin configuration – HVQFN

#### **PIN DESCRIPTION**

| SO, TSSOP<br>PIN NUMBER | HVQFN<br>PIN NUMBER | SYMBOL          | NAME AND FUNCTION                |

|-------------------------|---------------------|-----------------|----------------------------------|

| 1,2,3                   | 15, 16, 1           | A0-2            | Address lines (internal pull-up) |

| 4,5,6,7                 | 2, 3, 4, 5          | I/O0 to I/O3    | Quasi-bidirectional I/O pins     |

| 8                       | 6                   | V <sub>SS</sub> | Supply ground                    |

| 9,10,11,12              | 7, 8, 9, 10         | I/O4 to I/O7    | Quasi-bidirectional I/O pins     |

| 13                      | 11                  | WC              | Active LOW write control pin     |

| 14                      | 12                  | SCL             | I <sup>2</sup> C Serial Clock    |

| 15                      | 13                  | SDA             | I <sup>2</sup> C Serial Data     |

| 16                      | 14                  | $V_{DD}$        | Supply Voltage                   |

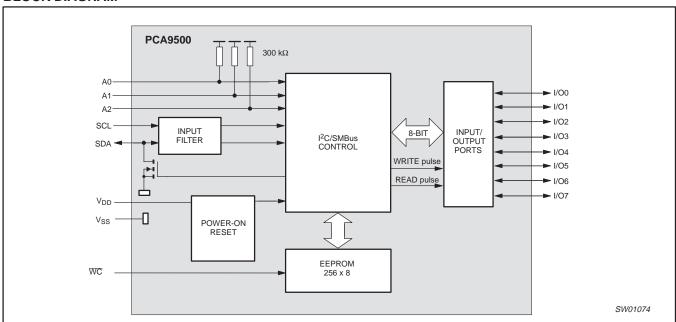

#### **BLOCK DIAGRAM**

Figure 3. Block diagram

# 8-bit I<sup>2</sup>C and SMBus I/O port with 2-kbit EEPROM

PCA9500

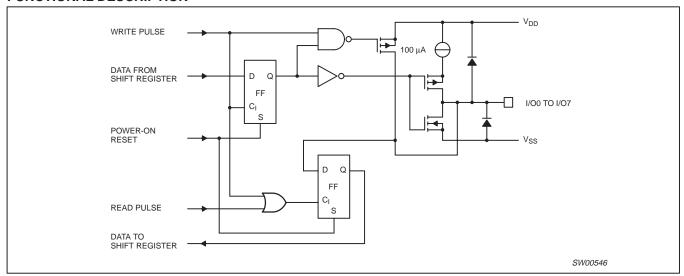

#### **FUNCTIONAL DESCRIPTION**

Figure 4. Simplified schematic diagram of each I/O

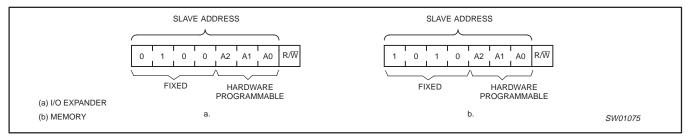

#### **DEVICE ADDRESSING**

Following a START condition the bus master must output the address of the slave it is accessing. The address of the PCA9500 is shown in Figure 5. Internal pullup resistors are incorporated on the hardware selectable address pins.

Figure 5. PCA9500 slave addresses

The last bit of the address byte defines the operation to be performed. When set to logic 1 a read is selected while a logic 0 selects a write operation.

### 8-bit I<sup>2</sup>C and SMBus I/O port with 2-kbit EEPROM

PCA9500

#### **CONTROL REGISTER**

The PCA9500 contains a single 8-bit register called the Control Register, which can be written and read via the I<sup>2</sup>C-bus. This register is sent after a successful acknowledgment of the slave address.

It contains the I/O operation information.

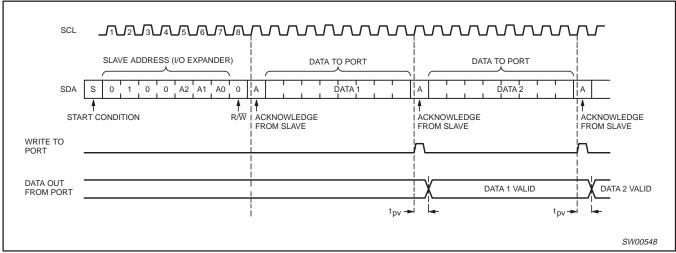

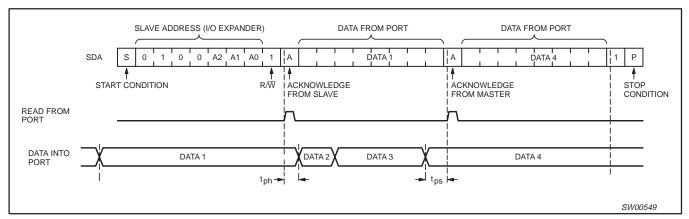

#### I/O OPERATIONS (see also Figure 4)

Each of the PCA9500's eight I/Os can be independently used as an input or output. Output data is transmitted to the port by the I/O WRITE mode (see Figure 6). Input I/O data is transferred from the port to the microcontroller by the READ mode (See Figure 7).

Figure 6. I/O WRITE mode (output)

Figure 7. I/O READ mode (input)

### 8-bit I<sup>2</sup>C and SMBus I/O port with 2-kbit EEPROM

PCA9500

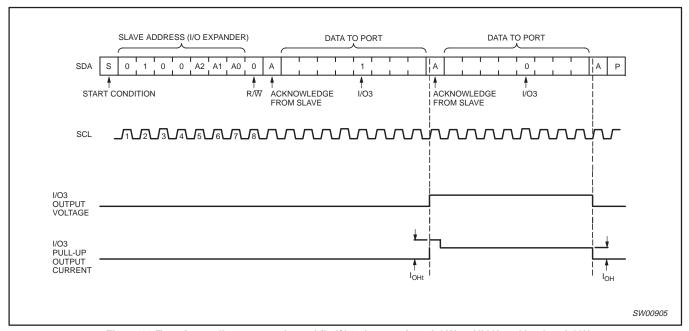

#### Quasi-bidirectional I/Os (see Figure 8)

A quasi-bidirectional I/O can be used as an input or output without the use of a control signal for data direction. At power-on the I/Os are HIGH. In this mode, only a current source to  $V_{DD}$  is active. An additional strong pull-up to  $V_{DD}$  allows fast rising edges into heavily loaded outputs. These devices turn on when an output is written HIGH, and are switched off by the negative edge of SCL. The I/Os should be HIGH before being used as inputs.

Figure 8. Transient pull-up current  $I_{OHt}$  while I/O3 changes from LOW-to-HIGH and back to LOW

### 8-bit I<sup>2</sup>C and SMBus I/O port with 2-kbit EEPROM

PCA9500

#### **MEMORY OPERATIONS**

#### Write operations

Write operations require an additional address field to indicate the memory address location to be written. The address field is eight bits long, providing access to any one of the 256 words of memory. There are two types of write operations, byte write and page write.

Write operation is possible when  $\overline{WC}$  control pin put at a low logic level (0). When this control signal is set at 1, write operation is not possible and data in the memory is protected.

Byte Write and Page Write explained below assume that Write Control pin  $(\overline{WC})$  is set to 0.

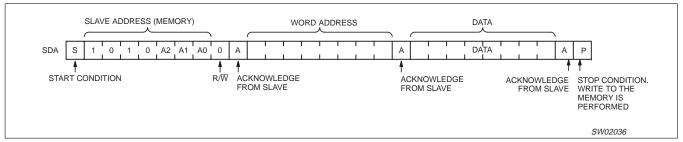

#### Byte Write (see Figure 9)

To perform a byte write the start condition is followed by the memory slave address and the  $R/\overline{W}$  bit set to 0. The PCA9500 will respond with an acknowledge and then consider the next eight bits sent as

the word address and the eight bits after the word address as the data. The PCA9500 will issue an acknowledge after the receipt of both the word address and the data. To terminate the data transfer the master issues the stop condition, initiating the internal write cycle to the non-volatile memory. Only write and read operations to the Quasi-bidirectional I/O are allowed during the internal write cycle.

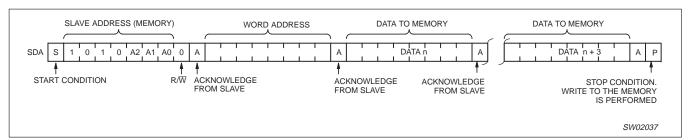

#### Page Write (see Figure 10)

A page write is initiated in the same way as the byte write. If after sending the first word of data, the stop condition is not received the PCA9500 considers subsequent words as data. After each data word the PCA9500 responds with an acknowledge and the two least significant bits of the memory address field are incremented. Should the master not send a stop condition after four data words the address counter will return to its initial value and overwrite the data previously written. After the receipt of the stop condition the inputs will behave as with the byte write during the internal write cycle.

Figure 9. Byte write

Figure 10. Page Write

### 8-bit I<sup>2</sup>C and SMBus I/O port with 2-kbit EEPROM

PCA9500

#### Read operations

PCA9500 read operations are initiated in an identical manner to write operations with the exception that the memory slave address'  $R/\overline{W}$  bit is set to a one. There are three types of read operations; current address, random and sequential.

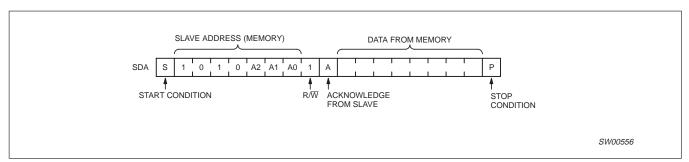

#### **Current Address Read (see Figure 11)**

The PCA9500 contains an internal address counter that increments after each read or write access, as a result if the last word accessed was at address n then the address counter contains the address n+1

When the PCA9500 receives its memory slave address with the  $R/\overline{W}$  bit set to one it issues an acknowledge and uses the next eight clocks to transmit the data contained at the address stored in the address counter. The master ceases the transmission by issuing the stop condition after the eighth bit. There is no ninth clock cycle for the acknowledge.

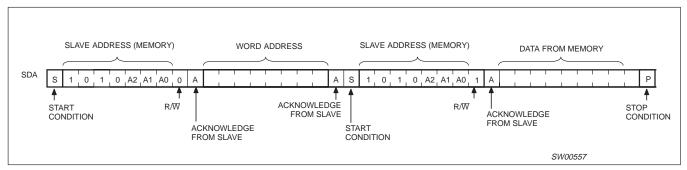

#### Random Read (see Figure 12)

The PCA9500's random read mode allows the address to be read from to be specified by the master. This is done by performing a dummy write to set the address counter to the location to be read.

The master must perform a byte write to the address location to be read, but instead of transmitting the data after receiving the acknowledge from the PCA9500 the master reissues the start condition and memory slave address with the R/W bit set to one. The PCA9500 will then transmit an acknowledge and use the next eight clock cycles to transmit the data contained in the addressed location. The master ceases the transmission by issuing the stop condition after the eighth bit, omitting the ninth clock cycle acknowledge.

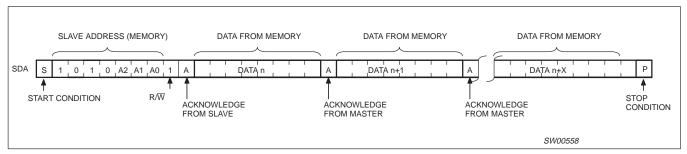

#### Sequential Read (see Figure 13)

The PCA9500 sequential read is an extension of either the current address read or random read. If the master doesn't issue a stop condition after it has received the eighth data bit, but instead issues an acknowledge, the PCA9500 will increment the address counter and use the next eight cycles to transmit the data from that location. The master can continue this process to read the contents of the entire memory. Upon reaching address 255 the counter will return to address 0 and continue transmitting data until a stop condition is received. The master ceases the transmission by issuing the stop condition after the eighth bit, omitting the ninth clock cycle acknowledge.

Figure 11. Current Address Read

Figure 12. Random Read

Figure 13. Sequential Read

# 8-bit I<sup>2</sup>C and SMBus I/O port with 2-kbit EEPROM

PCA9500

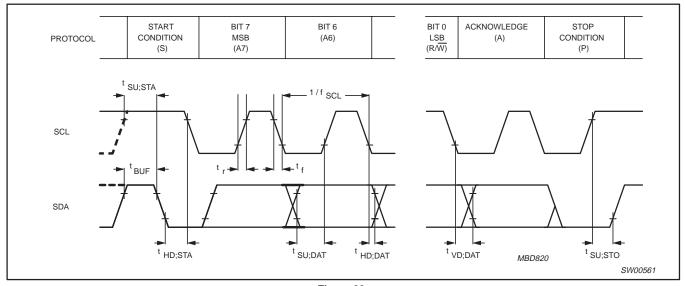

#### CHARACTERISTICS OF THE I<sup>2</sup>C-BUS

The I<sup>2</sup>C-bus is for 2-way, 2-line communication between different ICs or modules. The two lines are a serial data line (SDA) and a serial clock line (SCL). Both lines must be connected to a positive supply via a pull-up resistor when connected to the output stages of a device. Data transfer may be initiated only when the bus is not busy.

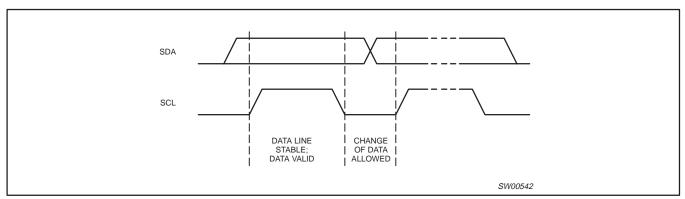

#### Bit transfer

One data bit is transferred during each clock phase. The data on the SDA line must remain stable during the HIGH period of the clock pulse as changes in the data line at this time will be interpreted as control signals (See Figure 14).

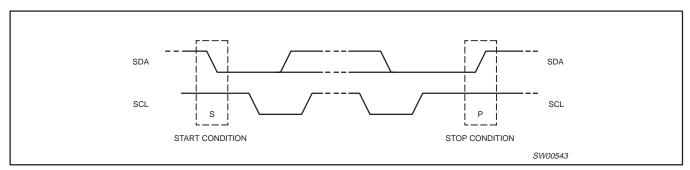

#### Start and Stop conditions

Both data and clock lines remain HIGH when the bus is not busy. A HIGH-to-LOW transition of the data line, while the clock is HIGH is defined as the Start condition (S). A LOW-to-HIGH transition of the data line while the clock is HIGH is defined as the Stop condition (P) (see Figure 15).

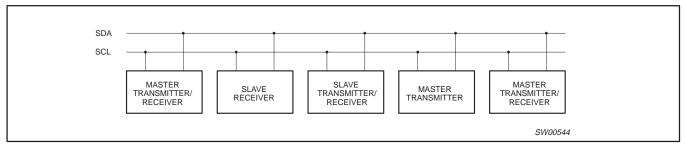

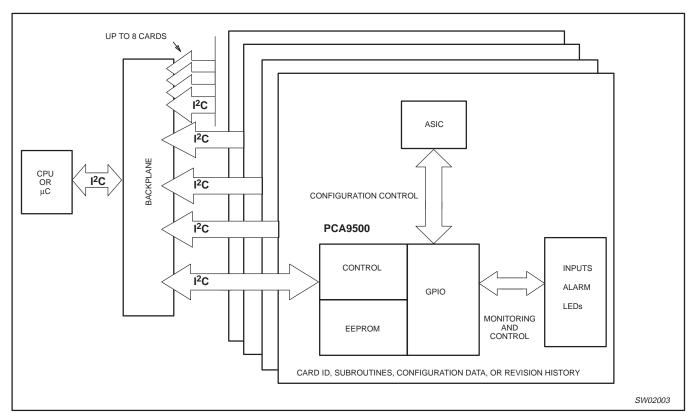

#### System configuration

A device generating a message is a "transmitter", a device receiving is the "receiver". The device that controls the message is the "master" and the devices which are controlled by the master are the "slaves" (see Figure 16).

Figure 14. Bit transfer

Figure 15. Definition of start and stop conditions

Figure 16. System configuration

### 8-bit I<sup>2</sup>C and SMBus I/O port with 2-kbit EEPROM

PCA9500

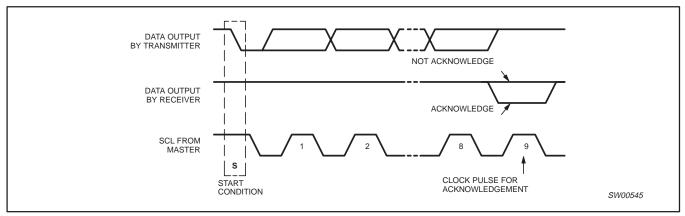

#### Acknowledge (see Figure 17)

The number of data bytes transferred between the start and the stop conditions from transmitter to receiver is not limited. Each byte of eight bits is followed by one acknowledge bit. The acknowledge bit is a HIGH level put on the bus by the transmitter whereas the master generates an extra acknowledge related clock pulse.

A slave receiver which is addressed must generate an acknowledge after the reception of each byte. Also a master must generate an acknowledge after the reception of each byte that has been clocked

out of the slave transmitter. The device that acknowledges has to pull down the SDA line during the acknowledge clock pulse, so that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse, set-up and hold times must be taken into account.

A master receiver must signal an end of data to the transmitter by not generating an acknowledge on the last byte that has been clocked out of the slave. In this event the transmitter must leave the data line HIGH to enable the master to generate a stop condition.

Figure 17. Acknowledgment on the I<sup>2</sup>C-bus

### 8-bit I<sup>2</sup>C and SMBus I/O port with 2-kbit EEPROM

PCA9500

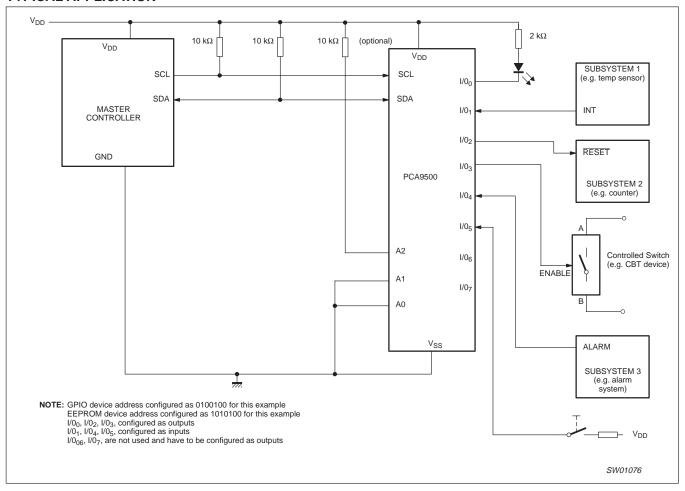

#### TYPICAL APPLICATION

#### **Applications**

- Board version tracking and configuration

- Board health monitoring and status reporting

- Multi-card systems in Telecom, Networking, and Base Station Infrastructure Equipment

- Field recall and troubleshooting functions for installed boards

- General-purpose integrated I/O with memory

- Drop in replacement for PCF8574 with integrated 2-kbit EEPROM

- Bus master sees GPIO and EEPROM as two separate devices

- Three hardware address pins allow up to 8 PCA9500s to be located in the same I<sup>2</sup>C/SMBus

Figure 18. Typical application

A central processor/controller typically located on the system main board can use the 400 kHz I<sup>2</sup>C/SMBus to poll the PCA9500 devices located on the system cards for status or version control type of information. The PCA9500 may be programmed at manufacturing to store information regarding board build, firmware version,

manufacturer identification, configuration option data... Alternately, these devices can be used as convenient interface for board configuration, thereby utilizing the I<sup>2</sup>C/SMBus as an intra-system communication bus.

# 8-bit $I^2C$ and SMBus I/O port with 2-kbit EEPROM

PCA9500

#### **TYPICAL APPLICATION**

Figure 19. Typical application

# 8-bit $I^2C$ and SMBus I/O port with 2-kbit EEPROM

PCA9500

#### **ABSOLUTE MAXIMUM RATINGS**

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied.

| SYMBOL           | PARAMETER                          | MIN                   | MAX  | UNIT |

|------------------|------------------------------------|-----------------------|------|------|

| V <sub>CC</sub>  | Supply voltage                     | -0.5                  | 4.0  | V    |

| VI               | Input voltage                      | V <sub>SS</sub> - 0.5 | 5.5  | V    |

| I <sub>I</sub>   | DC input current                   | -20                   | 20   | mA   |

| Io               | DC output current                  | -25                   | 25   | mA   |

| I <sub>DD</sub>  | Supply current                     | -100                  | 100  | mA   |

| I <sub>SS</sub>  | Supply current                     | -100                  | 100  | mA   |

| P <sub>tot</sub> | Total power dissipation            | _                     | 400  | mW   |

| P <sub>O</sub>   | Total power dissipation per output | _                     | 100  | mW   |

| T <sub>stg</sub> | Storage temperature                | -65                   | +150 | °C   |

| T <sub>amb</sub> | Operating temperature              | -40                   | +85  | °C   |

#### DC ELECTRICAL CHARACTERISTICS

$T_{amb}$  = -40 to +85 °C unless otherwise specified;  $V_{CC}$  = 3.3 V

| SYMBOL                | PARAMETER                               | CONDITIONS                 | MIN                | TYP | MAX                | UNIT |

|-----------------------|-----------------------------------------|----------------------------|--------------------|-----|--------------------|------|

| Supply                |                                         |                            |                    |     | •                  | •    |

| V <sub>DD</sub>       | Supply voltage                          |                            | 2.5                | 3.3 | 3.6                | V    |

| I <sub>DDQ</sub>      | Standby current                         | A0, A1, A2, WC = HIGH      | _                  | _   | 60                 | μΑ   |

| I <sub>DD1</sub>      | Supply current read                     |                            | _                  | _   | 1                  | mA   |

| I <sub>DD2</sub>      | Supply current write                    |                            | _                  | _   | 2                  | mA   |

| V <sub>POR</sub>      | Power-on reset voltage                  |                            | _                  | _   | 2.4                | V    |

| Input SCL; i          | nput, output SDA                        |                            |                    | •   | •                  |      |

| V <sub>IL</sub>       | LOW-level input voltage                 |                            | -0.5               | _   | 0.3V <sub>DD</sub> | V    |

| V <sub>IH</sub>       | HIGH-level input voltage                |                            | 0.7V <sub>DD</sub> | _   | 5.5                | V    |

| I <sub>OL</sub>       | LOW-level output current                | V <sub>OL</sub> = 0.4 V    | 3                  | _   | _                  | mA   |

| ILI                   | Input leakage current                   | $V_I = V_{DD}$ or $V_{SS}$ | -1                 | _   | 1                  | μΑ   |

| C <sub>I</sub>        | Input capacitance                       | $V_I = V_{SS}$             | _                  | _   | 7                  | pF   |

| I/O Expande           | r Port                                  |                            |                    |     | •                  |      |

| V <sub>IL</sub>       | LOW-level input voltage                 |                            | -0.5               | _   | 0.3V <sub>DD</sub> | V    |

| V <sub>IH</sub>       | HIGH-level input voltage                |                            | 0.7V <sub>DD</sub> | _   | 5.5                | V    |

| I <sub>IHL(max)</sub> | Input current through protection diodes |                            | -400               | _   | 400                | μА   |

| I <sub>OL</sub>       | LOW-level output current                | V <sub>OL</sub> = 1 V      | 10                 | 25  | _                  | mA   |

| I <sub>OH</sub>       | HIGH-level output current               | $V_{OH} = V_{SS}$          | 30                 | 100 | 300                | μΑ   |

| I <sub>OHt</sub>      | Transient pull-up current               |                            | _                  | 2   | _                  | mA   |

| Cl                    | Input capacitance                       |                            | _                  | _   | 10                 | pF   |

| Co                    | Output capacitance                      |                            | _                  | _   | 10                 | pF   |

| Address Inp           | outs (A0, A1, A2), WC input             | •                          |                    | •   | •                  |      |

| V <sub>IL</sub>       | LOW-level input voltage                 |                            | -0.5               | _   | 0.3V <sub>DD</sub> | V    |

| V <sub>IH</sub>       | HIGH-level input voltage                |                            | 0.7V <sub>DD</sub> | _   | 5.5                | V    |

| l                     | Input leakage current                   | $V_I = V_{DD}$             | -1                 | _   | 1                  | μΑ   |

| ILI                   | Input leakage (pull-up) current         | $V_I = V_{SS}$             | 10                 | 25  | 100                | μΑ   |

#### NOTES:

<sup>1.</sup> Each I/O must be externally limited to a maximum of 25 mA and the device must be limited to a maximum current of 100 mA.

# 8-bit $I^2C$ and SMBus I/O port with 2-kbit EEPROM

PCA9500

#### **NON-VOLATILE STORAGE SPECIFICATIONS**

| PARAMETER                          | SPECIFICATION          |

|------------------------------------|------------------------|

| Memory cell data retention         | 10 years minimum       |

| Number of memory cell write cycles | 100,000 cycles minimum |

#### I<sup>2</sup>C-BUS TIMING CHARACTERISTICS

| SYMBOL                    | PARAMETER                    | MIN. | TYP. | MAX. | UNIT |

|---------------------------|------------------------------|------|------|------|------|

| I <sup>2</sup> C-bus timi | ng (see Figure 20; Note 2)   |      |      |      |      |

| f <sub>SCL</sub>          | SCL clock frequency          | _    | _    | 400  | kHz  |

| t <sub>SW</sub>           | tolerable spike width on bus | _    | _    | 50   | ns   |

| t <sub>BUF</sub>          | bus free time                | 1.3  |      | _    | μs   |

| t <sub>SU;STA</sub>       | START condition set-up time  | 0.6  |      | _    | μs   |

| t <sub>HD;STA</sub>       | START condition hold time    | 0.6  |      | _    | μs   |

| t <sub>r</sub>            | SCL and SDA rise time        | _    | _    | 0.3  | μs   |

| t <sub>f</sub>            | SCL and SDA fall time        | _    | _    | 0.3  | μs   |

| t <sub>SU;DAT</sub>       | data set-up time             | 250  | _    | _    | ns   |

| t <sub>HD;DAT</sub>       | data hold time               | 0    | _    | _    | ns   |

| t <sub>VD;DAT</sub>       | SCL LOW to data out valid    | _    |      | 1.0  | μs   |

| t <sub>SU;STO</sub>       | STOP condition set-up time   | 0.6  | _    | _    | μs   |

#### NOTE:

#### PORT TIMING CHARACTERISTICS

| SYMBOL          | PARAMETER                                      | MIN | TYP | MAX | UNIT |

|-----------------|------------------------------------------------|-----|-----|-----|------|

| t <sub>pv</sub> | Output data valid; C <sub>L</sub> ≤ 100 pF     | _   | _   | 4   | μs   |

| t <sub>ps</sub> | Input data setup time; C <sub>L</sub> ≤ 100 pF | 0   | _   | _   | μs   |

| t <sub>ph</sub> | Input data hold time; C <sub>L</sub> ≤ 100 pF  | 4   | _   | _   | μs   |

Figure 20.

<sup>2.</sup> All the timing values are valid within the operating supply voltage and ambient temperature range and refer to  $V_{IL}$  and  $V_{IH}$  with an input voltage swing of  $V_{SS}$  to  $V_{DD}$ .

### 8-bit I<sup>2</sup>C and SMBus I/O port with 2-kbit EEPROM

PCA9500

#### **POWER-UP TIMING**

| SYMBOL             | PARAMETER                   | MAX. | UNIT |

|--------------------|-----------------------------|------|------|

| t <sub>PUR</sub> 1 | Power-up to Read Operation  | 1    | ms   |

| t <sub>PUW</sub> 1 | Power-up to Write Operation | 5    | ms   |

#### NOTE:

#### WRITE CYCLE LIMITS

| SYMBOL            | PARAMETER        | MIN. | TYP. <sup>(5)</sup> | MAX. | UNIT |

|-------------------|------------------|------|---------------------|------|------|

| t <sub>WR</sub> 1 | Write Cycle Time | _    | 5                   | 10   | ms   |

#### NOTE:

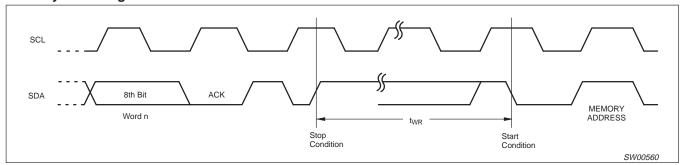

#### **Write Cycle Timing**

Figure 21.

<sup>1.</sup> t<sub>PUR</sub> and t<sub>PUW</sub> are the delays required from the time V<sub>CC</sub> is stable until the specified operation can be initiated. These parameters are guaranteed by design.

<sup>1.</sup>  $t_{WR}$  is the maximum time that the device requires to perform the internal write operation.

# 8-bit I<sup>2</sup>C and SMBus I/O port with 2-kbit EEPROM

PCA9500

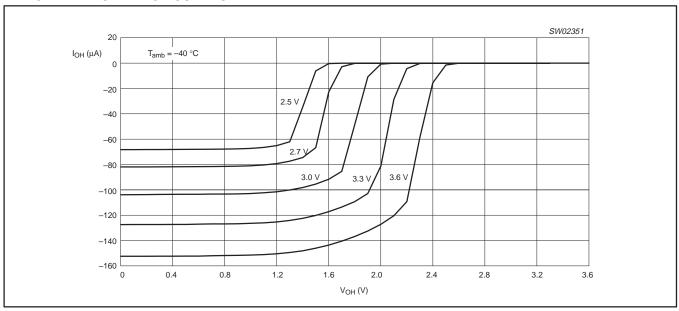

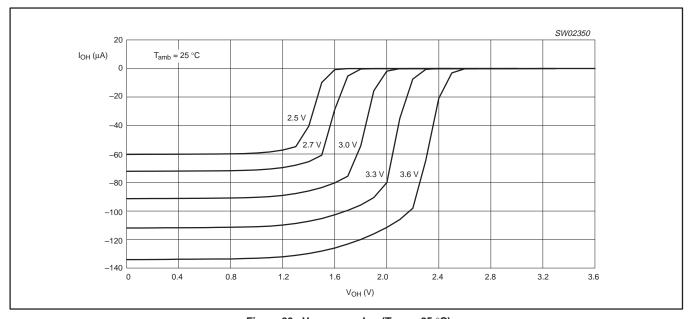

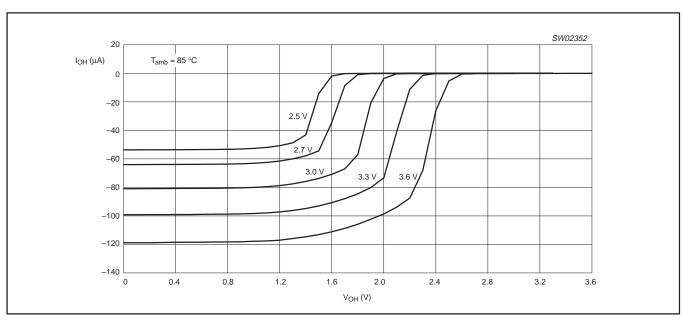

#### **TYPICAL PERFORMANCE CURVES**

Figure 22.  $V_{OH}$  versus  $I_{OH}$  ( $T_{amb}$  = -40 °C)

Figure 23.  $V_{OH}$  versus  $I_{OH}$  ( $T_{amb}$  = 25 °C)

# 8-bit I<sup>2</sup>C and SMBus I/O port with 2-kbit EEPROM

PCA9500

Figure 24.  $V_{OH}$  versus  $I_{OH}$  ( $T_{amb}$  = 85  $^{\circ}$ C)

#### NOTE:

Rapid fall off in  $V_{OH}$  at current inception is due to a diode that provides 5 V overvoltage protection for the GPIO I/O pins. When the GPIO I/O are being used as inputs, the internal current source  $V_{OH}$  should be evaluated to determine if external pull-up resistors are required to provide sufficient  $V_{IH}$  threshold noise margin.

### 8-bit I<sup>2</sup>C and SMBus I/O port with 2-kbit EEPROM

PCA9500

#### SOLDERING

#### Introduction

There is no soldering method that is ideal for all IC packages. Wave soldering is often preferred when through-hole and surface mounted components are mixed on one printed-circuit board. However, wave soldering is not always suitable for surface mounted ICs, or for printed-circuits with high population densities. In these situations reflow soldering is often used.

This text gives a very brief insight to a complex technology. A more in-depth account of soldering ICs can be found in our *IC Package Databook* (order code 9398 652 90011).

#### DIP

#### Soldering by dipping or by wave

The maximum permissible temperature of the solder is 260  $^{\circ}$ C; solder at this temperature must not be in contact with the joint for more than 5 seconds. The total contact time of successive solder waves must not exceed 5 seconds.

The device may be mounted up to the seating plane, but the temperature of the plastic body must not exceed the specified maximum storage temperature (T<sub>stg</sub> max). If the printed-circuit board has been pre-heated, forced cooling may be necessary immediately after soldering to keep the temperature within the permissible limit.

#### Repairing soldered joints

Apply a low voltage soldering iron (less than 24 V) to the lead(s) of the package, below the seating plane or not more than 2 mm above it. If the temperature of the soldering iron bit is less than 300  $^{\circ}$ C it may remain in contact for up to 10 seconds. If the bit temperature is between 300 and 400 $^{\circ}$ C, contact may be up to 5 seconds.

#### SO and SSOP

#### Reflow soldering

Reflow soldering techniques are suitable for all SO and SSOP packages.

Reflow soldering requires solder paste (a suspension of fine solder particles, flux and binding agent) to be applied to the printed-circuit board by screen printing, stencilling or pressure-syringe dispensing before package placement.

Several techniques exist for reflowing; for example, thermal conduction by heated belt. Dwell times vary between 50 and 300 seconds depending on heating method. Typical reflow temperatures range from 215 to 250  $^{\circ}\text{C}$ .

Preheating is necessary to dry the paste and evaporate the binding agent. Preheating duration: 45 minutes at 45 °C.

#### Wave soldering

Wave soldering is not recommended for SSOP packages. This is because of the likelihood of solder bridging due to closely-spaced leads and the possibility of incomplete solder penetration in multi-lead devices.

If wave soldering cannot be avoided, the following conditions must be observed:

- A double-wave (a turbulent wave with high upward pressure followed by a smooth laminar wave) soldering technique should be used.

- The longitudinal axis of the package footprint must be parallel to the solder flow and must incorporate solder thieves at the downstream end.

Even with these conditions, only consider wave soldering SSOP packages that have a body width of 4.4 mm, that is SSOP16 (SOT369-1) or SSOP20 (SOT266-1).

During placement and before soldering, the package must be fixed with a droplet of adhesive. The adhesive can be applied by screen printing, pin transfer or syringe dispensing. The package can be soldered after the adhesive is cured.

Maximum permissible solder temperature is 260  $^{\circ}$ C, and maximum duration of package immersion in solder is 10 seconds, if cooled to less than 150  $^{\circ}$ C within 6 seconds. Typical dwell time is 4 seconds at 250  $^{\circ}$ C.

A mildly-activated flux will eliminate the need for removal of corrosive residues in most applications.

#### Repairing soldered joints

Fix the component by first soldering two diagonally opposite end leads. Use only a low voltage soldering iron (less than 24 V) applied to the flat part of the lead. Contact time must be limited to 10 seconds at up to 300 °C. When using a dedicated tool, all other leads can be soldered in one operation within 2 to 5 seconds between 270 and 320 °C.

# 8-bit I<sup>2</sup>C and SMBus I/O port with 2-kbit EEPROM

PCA9500

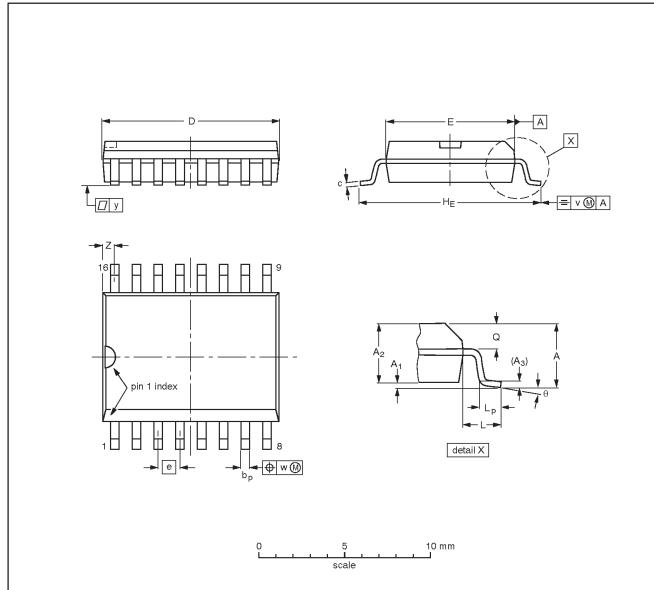

#### SO16: plastic small outline package; 16 leads; body width 7.5 mm

SOT162-1

#### DIMENSIONS (inch dimensions are derived from the original mm dimensions)

| UNIT   | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | A <sub>3</sub> | bp             | С              | D <sup>(1)</sup> | E <sup>(1)</sup> | е    | HE             | L     | Lp             | Q          | ٧    | w    | у     | z <sup>(1)</sup> | θ  |

|--------|-----------|----------------|----------------|----------------|----------------|----------------|------------------|------------------|------|----------------|-------|----------------|------------|------|------|-------|------------------|----|

| mm     | 2.65      | 0.3<br>0.1     | 2.45<br>2.25   | 0.25           | 0.49<br>0.36   | 0.32<br>0.23   | 10.5<br>10.1     | 7.6<br>7.4       | 1.27 | 10.65<br>10.00 | 1.4   | 1.1<br>0.4     | 1.1<br>1.0 | 0.25 | 0.25 | 0.1   | 0.9<br>0.4       | 8° |

| inches | 0.1       | 0.012<br>0.004 | 0.096<br>0.089 | 0.01           | 0.019<br>0.014 | 0.013<br>0.009 | 0.41<br>0.40     | 0.30<br>0.29     | 0.05 | 0.419<br>0.394 | 0.055 | 0.043<br>0.016 |            | 0.01 | 0.01 | 0.004 | 0.035<br>0.016   | O° |

#### Note

1. Plastic or metal protrusions of 0.15 mm (0.006 inch) maximum per side are not included.

| OUTLINE  |        | REFER  | RENCES | EUROPEAN   | ISSUE DATE                       |

|----------|--------|--------|--------|------------|----------------------------------|

| VERSION  | IEC    | JEDEC  | JEITA  | PROJECTION | 1330E DATE                       |

| SOT162-1 | 075E03 | MS-013 |        |            | <del>-99-12-27</del><br>03-02-19 |

# 8-bit I<sup>2</sup>C and SMBus I/O port with 2-kbit EEPROM

PCA9500

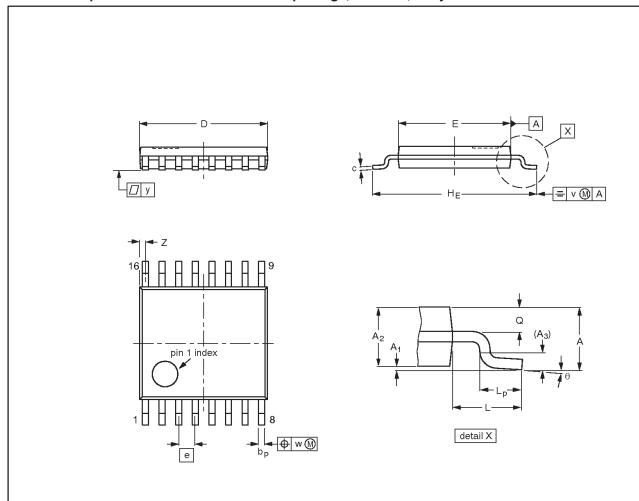

TSSOP16: plastic thin shrink small outline package; 16 leads; body width 4.4 mm

SOT403-1

#### **DIMENSIONS (mm are the original dimensions)**

| UN | IIT | A<br>max. | Α1           | A <sub>2</sub> | A <sub>3</sub> | bp           | С          | D <sup>(1)</sup> | E <sup>(2)</sup> | е    | HE         | L | Lp           | Q          | v   | w    | у   | Z <sup>(1)</sup> | θ        |

|----|-----|-----------|--------------|----------------|----------------|--------------|------------|------------------|------------------|------|------------|---|--------------|------------|-----|------|-----|------------------|----------|

| m  | m   | 1.1       | 0.15<br>0.05 | 0.95<br>0.80   | 0.25           | 0.30<br>0.19 | 0.2<br>0.1 | 5.1<br>4.9       | 4.5<br>4.3       | 0.65 | 6.6<br>6.2 | 1 | 0.75<br>0.50 | 0.4<br>0.3 | 0.2 | 0.13 | 0.1 | 0.40<br>0.06     | 8°<br>0° |

#### Notes

- 1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

- 2. Plastic interlead protrusions of 0.25 mm maximum per side are not included.

| OUTLINE<br>VERSION | REFERENCES |        |       |  | EUROPEAN   | ISSUE DATE                        |

|--------------------|------------|--------|-------|--|------------|-----------------------------------|

|                    | IEC        | JEDEC  | JEITA |  | PROJECTION | ISSUE DATE                        |

| SOT403-1           |            | MO-153 |       |  |            | <del>-99-12-27-</del><br>03-02-18 |

### 8-bit I<sup>2</sup>C and SMBus I/O port with 2-kbit EEPROM

PCA9500

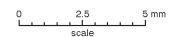

HVQFN16: plastic thermal enhanced very thin quad flat package; no leads; 16 terminals; body  $4 \times 4 \times 0.85$  mm

SOT629-1

#### Note

1. Plastic or metal protrusions of 0.075 mm maximum per side are not included.

| OUTLINE<br>VERSION | REFERENCES |        |       |  | EUROPEAN   | ISSUE DATE                       |

|--------------------|------------|--------|-------|--|------------|----------------------------------|

|                    | IEC        | JEDEC  | JEITA |  | PROJECTION | ISSUE DATE                       |

| SOT629-1           |            | MO-220 |       |  |            | <del>-01-08-08</del><br>02-10-22 |

# 8-bit $I^2C$ and SMBus I/O port with 2-kbit EEPROM

PCA9500

#### **REVISION HISTORY**

| Rev | Date     | Description                                                                                                                     |  |

|-----|----------|---------------------------------------------------------------------------------------------------------------------------------|--|

| _3  | 20040930 | Product data sheet (9397 750 14134). Supersedes data of 2003 Jun 27 (9397 750 11682).                                           |  |

|     |          | Modifications:                                                                                                                  |  |

|     |          | ● Figure 19: resistor values changed to 10 kΩ                                                                                   |  |

|     |          | "DC characteristics" table on page : add Table note 1.                                                                          |  |

|     |          | Added "Typical performance curves" section                                                                                      |  |

| _2  | 20030627 | Product data (9397 750 11682); ECN 853-2369 30018 dated 11 June 2003.<br>Supersedes data of 2002 September 09 (9397 750 10326). |  |

| _1  | 20020927 | Product data (9397 750 10326); ECN: 853-2369 28875 (2002 Sep 27)                                                                |  |

### 8-bit I<sup>2</sup>C and SMBus I/O port with 2-kbit EEPROM

PCA9500

Purchase of Philips I<sup>2</sup>C components conveys a license under the Philips' I<sup>2</sup>C patent to use the components in the I<sup>2</sup>C system provided the system conforms to the I<sup>2</sup>C specifications defined by Philips. This specification can be ordered using the code 9398 393 40011.

#### **Data sheet status**

| Level | Data sheet status <sup>[1]</sup> | Product<br>status <sup>[2]</sup> [3] | Definitions                                                                                                                                                                                                                                                                                    |

|-------|----------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I     | Objective data sheet             | Development                          | This data sheet contains data from the objective specification for product development.  Philips Semiconductors reserves the right to change the specification in any manner without notice.                                                                                                   |

| II    | Preliminary data sheet           | Qualification                        | This data sheet contains data from the preliminary specification. Supplementary data will be published at a later date. Philips Semiconductors reserves the right to change the specification without notice, in order to improve the design and supply the best possible product.             |

| III   | Product data sheet               | Production                           | This data sheet contains data from the product specification. Philips Semiconductors reserves the right to make changes at any time in order to improve the design, manufacturing and supply. Relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). |

- [1] Please consult the most recently issued data sheet before initiating or completing a design.

- [2] The product status of the device(s) described in this data sheet may have changed since this data sheet was published. The latest information is available on the Internet at URL http://www.semiconductors.philips.com.

- [3] For data sheets describing multiple type numbers, the highest-level product status determines the data sheet status.

#### **Definitions**

**Short-form specification** — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 60134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

Application information — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### **Disclaimers**

Life support — These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

Right to make changes — Philips Semiconductors reserves the right to make changes in the products—including circuits, standard cells, and/or software—described or contained herein in order to improve design and/or performance. When the product is in full production (status 'Production'), relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

#### **Contact information**

For additional information please visit

http://www.semiconductors.philips.com. Fax: +31 40 27 24825

For sales offices addresses send e-mail to: sales.addresses@www.semiconductors.philips.com

© Koninklijke Philips Electronics N.V. 2004 All rights reserved. Published in the U.S.A.

Date of release: 09-04

Document number: 9397 750 14134

Let's make things better.

Philips Semiconductors