# ZN433J10 / ZN433CJ10

# 10-BIT TRACKING A-D CONVERTER

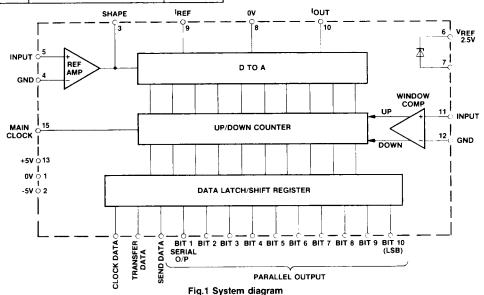

The ZN433 range of tracking A-D converters combine several innovations to provide this function on a fully monolithic silicon integrated circuit. The chip contains a current switching array using a matrix of diffused resistors (no trim required), tracking logic with TTL interfacing, 2.5V precision voltage reference with reference amplifier, and fast window comparator with good overload recovery.

The tracking principle ensures continuous up to date conversion data. This is suitable for single channel conversion, e.g. digital transducers, and often obviates the need for sample and hold.

#### **FEATURES**

- ±½ LSB Linearity Error

- 1 microsecond Conversion Time (Assuming Continuous Tracking)

- Input Range as Desired

- ±5V Supplies, TTL/CMOS Compatible

- Parallel and Serial Outputs

- Bipolar Monolithic Construction

- No Missing Codes over Full Operating Temperature Range

#### 28 TRANSFER DATA ov F 27 SERIAL OUTPUT BIT 1 5v [ 26 BIT 2 REF AMP GROUND BIT 3 24 BIT 4 REE AMP INPUT 23 BIT 5 VREF - 2.48V 22 BIT 6 ov [ 21 BIT 7 ov [ 20 BIT 8 I REF 19 BIT 9 LOUT [ 18 BIT 10 (LSB) COMP INPUT 11 17 SEND DATA COMP GROUND 112 16 DATA CLOCK · 5V 🗍 13 15 MAIN CLOCK NC [ ZN433J10/CJ10 (DC28)

Pin connections - top view

### ORDERING INFORMATION

| Device type | Operating temperature | Package |  |

|-------------|-----------------------|---------|--|

| ZN433J10    | -55°C to +125°C       | DC28    |  |

| ZN433CJ10   | 0°C to +70°C          | DC28    |  |

1-180

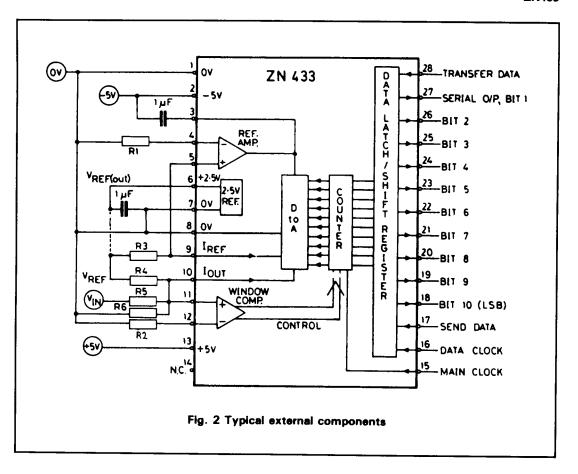

For resistor values, see 'Calculation of External Resistors'. When the internal reference is used,  $V_{REF}$  OUT (pin 6) is connected to R3 and R4 as shown. An external reference may also be used, which for ratiometric operation can vary by  $\pm 20\%$  of nominal.

# **ZN433**

# **ABSOLUTE MAXIMUM RATINGS**

**CHARACTERISTICS** (at  $\pm$  5V supplies and internal reference unless otherwise specified).

| Parameter                                             | t <sub>amb</sub> = + 25°C |            |       | Spec.<br>range | Units | Conds. |         |

|-------------------------------------------------------|---------------------------|------------|-------|----------------|-------|--------|---------|

| , arameter                                            | Min.                      | Тур.       | Max.  | Min.           | Max.  |        | 0011001 |

| Converter<br>Resolution                               | 10                        |            |       | 10             |       | Bits   | Note 1  |

| Non-linearity                                         |                           |            | ± 0.5 |                |       | LSB    |         |

| Differential non-linearity                            |                           | ± 0.5      |       |                |       | LSB    | Note 1  |

| D-A reference<br>current, I <sub>REF</sub><br>(pin 9) | 0.8                       |            | 1.2   | 0.8            | 1.2   | mA     | Note 2  |

| Max. clock rate                                       | 1                         | 1.2        |       | 1              |       | MHz    | Note 3  |

| Nominal analogue input range                          | - 2.5                     |            | + 2.5 |                |       | V      | Note 4  |

| Supply rejection                                      |                           | 0.1        |       |                |       | %/V    |         |

| Gain T.C.<br>(note 5)                                 |                           | 10         |       |                |       | ppm/°C |         |

| Zero T.C.                                             |                           | 7          |       |                |       | ppm/°C |         |

| Supply voltage                                        | ± 4.5                     | ± 5        | ± 5.5 | <u>+</u> 4.5   | ± 5.5 | V      |         |

| Supply current                                        |                           | 50         |       |                |       | mA     |         |

| Power consumption                                     |                           | 500        |       |                |       | mW     |         |

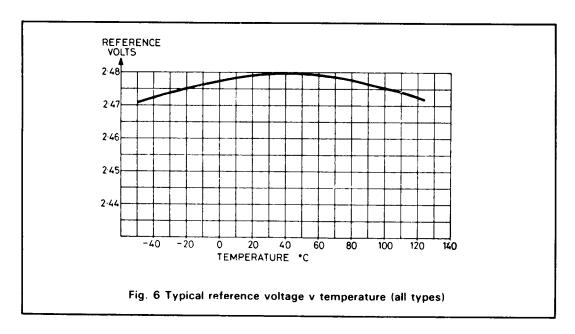

| Internal voltage<br>reference<br>Output voltage       |                           | 2.480      |       |                |       | V      |         |

| Output voltage tolerance (note 6)                     |                           |            | ± 1.5 |                |       | %      |         |

| Slope impedance                                       |                           | 0.75       |       |                |       | Ω      |         |

| Maximum reference load current                        |                           | <u>±</u> 4 |       |                |       | mA     |         |

# **CHARACTERISTICS** (Cont.)

| Parameter                         | t <sub>amb</sub> = +25°C |         |      | Over Spec.<br>Temp. range |      | Units                    | Conditions                                                   |  |

|-----------------------------------|--------------------------|---------|------|---------------------------|------|--------------------------|--------------------------------------------------------------|--|

|                                   | Min.                     | Тур.    | Max. | Min.                      | Max. |                          |                                                              |  |

| Logic<br>High level input voltage | 2.0                      |         |      | 2.0                       |      | V                        |                                                              |  |

| Low level input voltage           |                          |         | 0.8  |                           | 0.8  | V                        |                                                              |  |

| High level input current          |                          | 7<br>50 |      |                           |      | μ <b>Α</b><br>μ <b>Α</b> | $V_S = \pm 5.5V, V_I = 2.4V$<br>$V_S = \pm 5.5V, V_I = 5.5V$ |  |

| Low level input current           |                          | 1       |      |                           |      | μА                       | $V_S = \pm 5.5V, V_1 = 0.4V$                                 |  |

| High level output voltage         | 2.4                      |         |      | 2.4                       |      | V                        | $I_{load} = -40\mu A$                                        |  |

| Low level output voltage          |                          |         | 0.4  |                           | 0.4  | ٧                        | $I_{load} = 1.6 mA$                                          |  |

#### **NOTES**

- 1. No missing codes over full temperature range.

- 2. The full-scale D-A output current lout = 4 times IREF. For optimum performance IREF = 1.0mA.

- 3. For main clock waveform see Fig.5. Input signals which do not change by more than 1 LSB/ $\mu$ s may be tracked continuously without the need for a sample and hold. This corresponds to a full-scale bandwidth of 300Hz. Higher frequencies may be tracked if the amplitude is reduced, e.g. the half full-scale bandwidth is 600Hz.

- 4. Single polarity and other input ranges may be provided by different input resistor values.

- 5. Excluding reference.

- 6. For typical temperature performance see Fig.6.

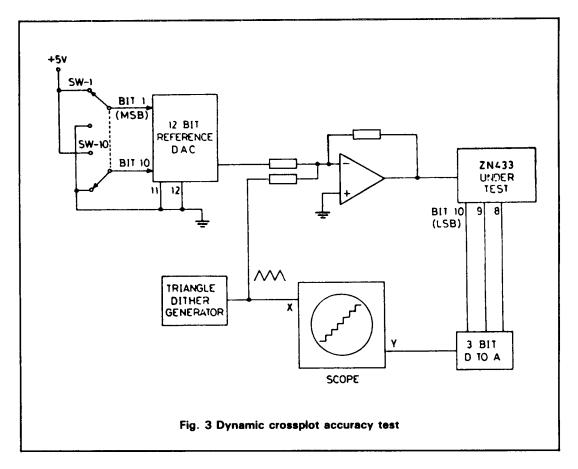

#### **TEST CIRCUIT**

Switches SW-1 to SW-10 are set to the appropriate digital code to select the point on the charactristic to be displayed. For example, code 10000 00000 would select half full-scale, i.e. the major transition.

The output from the dither generator (suggested peak to peak amplitude =  $\pm 4 \times LSB$ ) is used as the X deflection for the scope and is also superimposed on the analogue output from the

reference DAC in the summing amplifier. The resulting analogue signal including dither is used as  $V_{\text{IN}}$  for the ZN433 under test.

Bit 10, 9 and 8 outputs are fed to the inputs of a 3-bit DAC of at least 6-bit accuracy and the analogue output used as the Y deflection of the scope. Differential non-linearity is shown by horizontal lines which are longer or shorter than the rest.

1-184

#### **CALCULATION OF EXTERNAL RESISTORS**

- 1.  $R_3$ ,  $R_4$ ,  $R_5$  can affect gain and offset stability and thus require to be of high quality.

- 2.  $R_1$  and  $R_2$  are to allow for the bias current of the reference amplifier and comparator which both operate in a virtual earth mode. Thus:  $R_1 = R_2$

And  $R_2$  = parallel combination of  $R_4$ ,  $R_5$ , and  $R_6$ .

3. I<sub>REF</sub> should be 1.0mA, though it may be varied from 0.8 to 1.2mA.

$$R_3 = \frac{V_{REF}}{1.0mA}$$

Iout FS is four times IREF, i.e., 4mA (Iout for zero reading is 0mA).

4. Analysing the network yields the following:

$$\begin{aligned} R_4 &= \frac{-V_{REF} \ R_5}{V_{in} \ min} \\ R_5 &= \frac{V_{in} \ max - V_{in} \ min}{I_{outFS}} \end{aligned}$$

Where  $V_{in}$  max is the voltage for the logic output to be all 1's.  $V_{in}$  min is the voltage for the logic output to be all 0's.

- 5.  $R_6$  should be chosen such that the parallel combination of  $R_4$ ,  $R_5$  and  $R_6$  is about 625 $\Omega$  as this determines the D-A time constant and hence conversion time.

- 6. The following is a table of values to give examples of the above equations.

| V <sub>in</sub> max | V <sub>in</sub> min | V <sub>REF</sub> | R <sub>1</sub> 1 | R <sub>2</sub> <sup>1</sup> | R <sub>3</sub> | R <sub>4</sub> | R <sub>5</sub> | R <sub>6</sub> <sup>1</sup> |

|---------------------|---------------------|------------------|------------------|-----------------------------|----------------|----------------|----------------|-----------------------------|

| + 2.5               | - 2.5               | 2.5              | 2.5kΩ            | 625Ω                        | 2.5kΩ          | 1.25kΩ         | 1.25kΩ         | 00                          |

| + 2.5               | - 2.5               | 5*               | 5kΩ              | 625Ω                        | 5kΩ            | 2.5kΩ          | 1.25kΩ         | 2.5kΩ                       |

| + 2.5               | 0                   | 2.5              | 2.5kΩ            | 625Ω                        | 2.5kΩ          | <b>∞</b>       | 625Ω           | 000                         |

| + 5                 | o                   | 2.5              | 2.5kΩ            | 625Ω                        | 2.5kΩ          | <b>∞</b>       | 1.25kΩ         | 1.25kΩ                      |

| + 4                 | <b>- 2</b>          | 2.5              | 2.5kΩ            | 625Ω                        | 2.5kΩ          | 1.875kΩ        | 1.5kΩ          | 2.5kΩ                       |

| + 4                 | - 2                 | 12*              | 12kΩ             | 625Ω                        | 12kΩ           | 1.875kΩ        | 1.5kΩ.         | 2.5kΩ                       |

| + 10                | - 10                | 2.5              | 2.5kΩ            | 625Ω                        | 2.5kΩ          | 1.25kΩ         | 5kΩ            | 1.67kΩ                      |

Note 1 Nearest prefered value may be used for R<sub>1</sub>, R<sub>2</sub> and R<sub>6</sub>.

7. For setting up  $R_4$  will adjust the offset.  $R_3$  will adjust the gain.

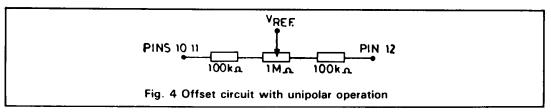

For unipolar operation where  $R_4$  approaches  $\infty$  and a zero adjustment is required, the following offset circuit is suggested in place of  $R_4$  (Typical values only).

<sup>\*</sup>Note 2 External reference.

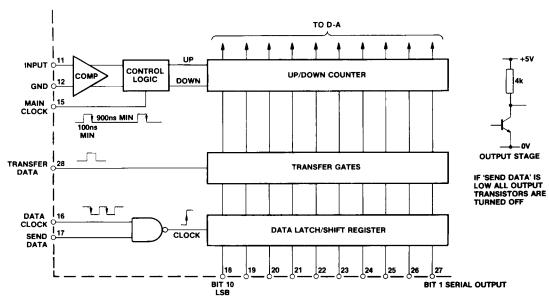

Fig.5 Logic system

#### **NOTES ON LOGIC DIAGRAM**

- 1. The Window comparator and control logic determine whether the counter will clock up or down or keep the same value on an active (negative going) edge of the main clock.

- 2. Parallel data from the up/down counter will be loaded into the output data latch/shift register when the TRANSFER DATA input is HIGH. TRANSFER DATA should not be taken HIGH until 150ns after the MAIN CLOCK edge and should go LOW before the next MAIN CLOCK edge. The minimum TRANSFER DATA pulse width is 50ns.

- If TRANSFER DATA is held permanently HIGH then the counter outputs will appear directly at the bit outputs.

- 3. Serial output data (MSB first) can be obtained from the MSB output (pin 27) by applying a DATA CLOCK (pin 16, 1MHz maximum, 100ns minimum pulse width).

- 4. A LOW on SEND DATA (pin 17) disables the DATA CLOCK and turns off all the output transistors so that all the bit outputs are HIGH (see diagram of output).

1-186

#### LOGIC CODING

Table 1 Unipolar operation

| Analogue input<br>Notes 1, 2 | Digital output code<br>MSB LSB |

|------------------------------|--------------------------------|

| FS - 1LSB                    | 1111111111                     |

| FS – 2LSB                    | 1111111110                     |

| ¾FS                          | 1100000000                     |

| ½FS + 1LSB                   | 100000001                      |

| ½ FS                         | 1000000000                     |

| ½FS − 1LSB                   | 011111111                      |

| ¼FS                          | 0100000000                     |

| 1LSB                         | 000000001                      |

| 0                            | 000000000                      |

Table 2 Bipolar operation

| Analogue input<br>Notes 1, 2 | Digital output code<br>MSB LSB |

|------------------------------|--------------------------------|

| + (FS – 1LSB)                | 1111111111                     |

| + (FS - 2LSB)                | 1111111110                     |

| + (½FS)                      | 1100000000                     |

| + (1LSB)                     | 100000001                      |

| 0                            | 1000000000                     |

| – (1LSB)                     | 011111111                      |

| - (½FS)                      | 0100000000                     |

| - (FS 1LSB)                  | 000000001                      |

| - FS                         | 000000000                      |

#### Notes:

- 1. Analogue inputs shown are nominal centre values of code.

- 2. "FS" is full-scale.

# OFFSET AND GAIN SETTING

For unipolar operation, supply an input of  $\frac{1}{2}$  LSB for transition 0000000000 to 000000001, and of (full-scale -  $\frac{1}{2}$  LSB) for transition 1111111111 to 111111110.

For bipolar operation, supply an input of - (full-scale - ½LSB) for transition 0000000000 to 0000000001, and of (full-scale - 1½LSB) for transition 1111111111 to 1111111110.