# Bidirectional 3.3 V Universal LVD Transceiver (G10™)

**Datasheet**

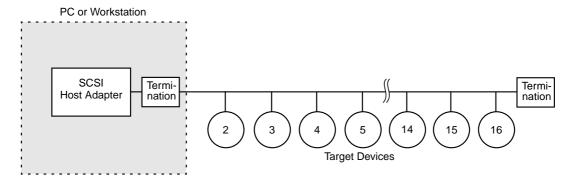

LSI Logic's bidirectional transceiver for SCSI is used to transmit and receive data on a SCSI-2, SCSI-3 10 MHz, SCSI-3 ULTRA, or SCSI-3 ULTRA-2 single-ended or differential bus. The bus operates at rates up to 40 MHz, with a cable length up to 25 m and maximum stub lengths of 0.1 m. SCSI bus termination is assumed to be external to the SCSI device

This transceiver can operate with SCSI-2, SCSI-3 10-MHz interfaces, SCSI-3 Fast-20, or SCSI-3 Fast-40 interfaces. Typically, the single-ended or differential operating mode is controlled by a "DIFFSENSE" receiver, a description of which is included in this datasheet. This transceiver is implemented in G10 technology.

This transceiver conforms to the *Information Technology - SCSI-3*Parallel Interface Specification SPI-2 Project 1142D.

Figure 1 SCSI Bus Interface

# **Features and Benefits**

- ♦ Complies with SCSI-3 SPI-2 Parallel Interface Specification

- ♦ Complies with the American National Standard for Information Systems SCSI-3 Fast-20

- Reduces engineering effort of designing an interconnect to SCSI bus

- Has V/I characteristics that meet the SCSI bus drive requirements

- Provides for direct silicon interconnect to a SCSI transmission line

- On-chip 48 mA drivers

- ♦ 3.3 V V<sub>DD</sub> (5-volt-tolerant)

- Bidirectional I/O transceiver that provides maximum flexibility in I/O path design

- Available in the G10 cell-based product families (0.35-micron drawn gate length, 0.29-micron effective channel length)

- Transfer rates up to 40 MHz

- Active negation SE driver

# **Specifications**

The following subsections provide the specifications for the SCSI bidirectional universal LVD 3.3 V transceivers.

Figure 2 shows the schematic symbol for the bidirectional universal LVD transceiver.

**Single-Ended Portion** TN -Signal -EN -IOM Α -Input ZI -Protection POM -PIM NEG -В-DIFF -Signal + TNDIFF -ЮP **ENDIFF** -

Figure 2 Bidirectional Universal LVD Transceiver Logic Diagram

Name: BDLVDSCSIF

POP -

ZIDIFF -

**Description:** SCSI 3.3 V bidirectional transceiver used with the SCSI-2,

SCSI-3 10 MHz, SCSI-3 FAST-20, and SCSI-3 FAST-40

Differential

Portion

Input Protection

Buses

Coding Syntax: U(IOM, IOP, ZI, ZIDIFF, PORN, POP) =

BDLVDSCSIF (IOM, IOP, A, B, EN, NEG, TN, ENDIFF,

TNDIFF, PIM, PIP, DIFF, IDDTN, HTPLG)

Silicon Dimensions: 285.6 µm x 226.8 µm

- PIP

# **Cell Placement Restrictions**

The following cells are designed to be used with G10 technology:

pvdd2\_lvdscsi: To supply vdd2

♦ apvdd\_lvdscsi: To supply analog V<sub>DD</sub>

♦ apvss\_lvdscsi: To supply analog V<sub>SS</sub>

pvdd\_lvdscsi: To supply 3.3 V to the I/O

♦ pvss2 lvdscsi: To supply vss2

♦ dvdd\_lvdscsi: Dummy cell for differential SCSI cells

dvddil\_lvdscsi: Left dummy interface cell

dvddir\_lvdscsi: Right dummy interface cell

The first five cells in this list supply vdd2, avdd, avss, 3.3 V I/O, and vss2 to the SCSI buffers. The dvdd\_lvdscsi, dvddil\_lvdscsi, and dvddir\_lvdscsi cells provide a protection diode between vddlvdscsi and vssio. Adhere to the following guidelines when placing these cells:

- 1. At least one dummy cell must be placed at both ends of the SCSI section.

- There must be at least one pvdd\_lvdscsi, apvdd\_lvdscsi, and apvss\_lvdscsi cell per five SCSI buffers; one V<sub>SS</sub> per two SCSI buffers.

# **Recommended Operating Conditions**

Table 1 provides the recommended operating conditions for the bidirectional SCSI I/O Transceiver.

Table 1 Recommended Operating Conditions

| Symbol          | Parameter            | Minimum | Typical | Maximum | Unit |

|-----------------|----------------------|---------|---------|---------|------|

| V <sub>DD</sub> | DC Supply Voltage    | 3.14    | 3.3     | 3.46    | V    |

| T <sub>j</sub>  | Junction Temperature | 0       | 30      | 125     | °C   |

Table 2 provides the loading characteristics for the control portion of the bidirectional transceiver. Values are in standard loads.

Table 2 Bidirectional Universal LVD Transceiver's Loading Characteristic<sup>1</sup>

| Α   | В   | EN  | TN  | ENDIFF | TNDIFF | NEG | HTPLG | DIFF | IDDTN | PIM  | PIP |

|-----|-----|-----|-----|--------|--------|-----|-------|------|-------|------|-----|

| 3.5 | 1.2 | 0.8 | 1.5 | 2.2    | 3.1    | 0.9 | 0.9   | 9.8  | 5.5   | 13.9 | 1.6 |

<sup>1.</sup> One standard load = 0.0151775 pF.

Table 3 provides the AC timing for the bidirectional transceiver's input portion. These specifications are valid only for the commercial operating range: junction temperature = 0  $^{\circ}$ C to 125  $^{\circ}$ C,  $V_{DD}$  = 3.3 V ±5%.

Table 3 Bidirectional Universal LVD Transceiver's AC Delay Characteristics for Transmitters (ns)

|                |        | (     | Capacitanc | e Load (pF | ·)   |

|----------------|--------|-------|------------|------------|------|

| Delay Path     | Output | 15    | 50         | 85         | 100  |

| A to IOM       | tpLH   | 3.98  | 4.77       | 5.48       | 5.77 |

|                | tpHL   | 3.79  | 4.58       | 5.19       | 5.42 |

|                | tpZL   | 6.87  | 7.66       | 8.36       | 8.64 |

|                | tpLZ   | 10.18 | 9.95       | 9.74       | 9.67 |

| EN to IOM      | tpZH   | 2.61  | 4.14       | 5.91       | 6.67 |

|                | tpZL   | 6.93  | 7.72       | 8.42       | 8.70 |

|                | tpLZ   | 10.20 | 9.97       | 9.76       | 9.69 |

|                | tpHZ   | 1.49  | 1.49       | 1.49       | 1.49 |

| TN to IOM      | tpZH   | 2.41  | 4.19       | 5.96       | 6.72 |

|                | tpZL   | 6.79  | 7.59       | 8.29       | 8.57 |

|                | tpLZ   | 10.11 | 9.88       | 9.67       | 9.59 |

|                | tpHZ   | 1.38  | 1.38       | 1.38       | 1.38 |

| (Sheet 1 of 2) |        |       |            |            |      |

Table 3 Bidirectional Universal LVD Transceiver's AC Delay Characteristics for Transmitters (ns), Continued

|                |        |      | Capacitanc | e Load (pF | =)    |

|----------------|--------|------|------------|------------|-------|

| Delay Path     | Output | 15   | 50         | 85         | 100   |

| ENDIFF to IOM  | tpZH   | 1.68 | 3.08       | 4.25       | 4.69  |

|                | tpZL   | 5.08 | 7.27       | 9.60       | 10.60 |

|                | tpLZ   | 3.97 | 3.97       | 3.97       | 3.96  |

|                | tpHZ   | 5.51 | 5.51       | 5.51       | 5.51  |

| TNDIFF to IOM  | tpZH   | 1.71 | 3.10       | 4.24       | 4.67  |

|                | tpZL   | 5.00 | 7.22       | 9.56       | 10.56 |

|                | tpLZ   | 3.89 | 3.89       | 3.88       | 3.88  |

|                | tpHZ   | 5.43 | 5.43       | 5.43       | 5.43  |

| A to IOP       | tpLH   | 4.80 | 5.36       | 5.88       | 6.11  |

|                | tpHL   | 5.45 | 6.04       | 6.66       | 6.93  |

| ENDIFF to IOP  | tpZH   | 2.58 | 3.90       | 4.72       | 5.04  |

|                | tpZL   | 4.62 | 7.35       | 9.98       | 11.12 |

|                | tpLZ   | 8.74 | 8.74       | 8.75       | 8.75  |

|                | tpHZ   | 8.74 | 8.74       | 8.75       | 8.75  |

| TNDIFF to IOP  | tpZH   | 2.60 | 3.84       | 4.65       | 4.96  |

|                | tpZL   | 4.58 | 7.32       | 9.96       | 11.11 |

|                | tpLZ   | 8.66 | 8.66       | 8.67       | 8.67  |

|                | tpHZ   | 8.66 | 8.66       | 8.66       | 8.67  |

| (Sheet 2 of 2) |        |      |            |            |       |

# Note:

- V<sub>DD</sub>, = 3.3 V, 25 °C.

AC Timing measurements are made with T<sub>f</sub>, T<sub>f</sub> (0.5 V-2.3 V, 2.3 V-0.5 V) less than 6 ns.

Table 4 provides the AC timing for the receiver portion of the bidirectional transceiver. These specifications are valid only for the commercial operating range: junction temperature =  $0 \, ^{\circ}$ C to  $125 \, ^{\circ}$ C,  $V_{DD} = 3.3 \, V \pm 5\%$ .

Table 4 Bidirectional Universal LVD Transceiver's AC Delay Characteristics for Receivers (ns)

|               |        | Standard Load (pF) |      |      |      |      |      |  |

|---------------|--------|--------------------|------|------|------|------|------|--|

| Delay Path    | Output | 0                  | 2    | 4    | 8    | 12   | 16   |  |

| IOM to ZI     | tpLH   | 0.55               | 0.58 | 0.61 | 0.67 | 0.72 | 0.78 |  |

|               | tpHL   | 0.28               | 0.31 | 0.34 | 0.39 | 0.43 | 0.43 |  |

| IOM to ZIDIFF | tpLH   | 1.64               | 1.67 | 1.70 | 1.74 | 1.78 | 1.81 |  |

|               | tpHL   | 1.91               | 1.95 | 1.98 | 2.03 | 2.07 | 2.11 |  |

| IOP to ZIDIFF | tpLH   | 1.68               | 1.71 | 1.73 | 1.78 | 1.81 | 1.85 |  |

|               | tpHL   | 1.88               | 1.91 | 1.94 | 1.99 | 2.03 | 2.08 |  |

# SCSI Bidirectional LVD Transceiver, Single-Ended Mode

Input Portion of Bidirectional LVD Single-Ended Transceiver

Table 5 provides the truth table for the input portion.

Table 5 Bidirectional Transceiver's Input Portion Truth Table (Diff = 0), Single-Ended Mode

| ЮМ | IOM PIM |   | POM |  |

|----|---------|---|-----|--|

| 0  | Х       | 0 | 1   |  |

| 1  | 0       | 1 | 1   |  |

| 1  | 1       | 1 | 0   |  |

Table 6 lists the DC characteristics for the bidirectional transceiver's input portion. These specifications are valid only for the commercial operating range: junction temperature = 0 °C to 125 °C,  $V_{DD} = 3.3$  V  $\pm 5\%$ .

Table 6 Bidirectional LVD Single-Ended Transceiver's Input Portion DC Characteristics for 3.3 V Signaling

| Symbol              | Parameter                           | Test Condition                                                                     | Min  | Тур  | Max   | Units |

|---------------------|-------------------------------------|------------------------------------------------------------------------------------|------|------|-------|-------|

| V <sub>DD</sub>     | Supply Voltage                      |                                                                                    | 3.14 | 3.30 | 3.46  | V     |

| $V_{ih}$            | Input High Voltage <sup>1</sup>     | Signal FALSE State                                                                 | 1.9  | _    | 5.25  | V     |

| V <sub>il</sub>     | Input Low Voltage                   | Referenced to V <sub>SS</sub><br>Signal TRUE State                                 | -0.5 | _    | 1.0   | V     |

| V <sub>ik</sub>     | Input Clamp Voltage                 | $V_{DD}$ = Min; $I_i$ = -20 mA                                                     | _    | _    | -0.75 | V     |

| $V_{th}$            | Threshold, High to Low              |                                                                                    | 1.00 | _    | 1.30  | V     |

| V <sub>tl</sub>     | Threshold, Low to High              |                                                                                    | 1.60 | _    | 1.90  | V     |

| $V_{th}$ – $V_{tl}$ | Hysteresis                          |                                                                                    | 300  | 600  | _     | mV    |

| I <sub>il</sub>     | Low Level Input<br>Current          | V <sub>i</sub> = 0.5 V, Power ON or Power<br>OFF, except during Hot Plug           | _    | _    | ±10   | μА    |

| l <sub>ih</sub>     | High Level Input<br>Current         | V <sub>i</sub> = 2.7 V, Power ON or OFF, except during Hot Plug                    | -    | _    | ±10   | μА    |

| lih.hp              | Hot Plug High Level<br>Current Peak | Transient duration to 10% of peak = 20 μs. Applies during physical insertion only. | -    | -    | +1.5  | mA    |

| C <sub>p</sub>      | Pin Capacitance                     | Package included                                                                   | 2.6  | 3.0  | 3.4   | pF    |

| R <sub>i</sub>      | Input Resistance                    |                                                                                    | _    | 20   | _     | mΩ    |

| Tj                  | Junction Temperature                |                                                                                    | 0    | _    | 125   | °C    |

| I <sub>lu</sub>     | Latch-up Current                    | -2 V < V <sub>pin</sub> < +8 V                                                     | _    | _    | ±100  | mA    |

| ESD                 | Electrostatic Discharge             | MIL-STD-883C, Method 3015.7, 100 pF at 1.5 k $\Omega$                              | 2001 | _    | _     | V     |

<sup>1.</sup> Absolute maximum of 8.0 V.

Table 7 is the truth table for the output portion of the single-ended transceiver.

Table 7 Bidirectional LVD Single-Ended Output Portion Truth Table

| NEG | Α | В | TN | EN | IOM    | IOP |

|-----|---|---|----|----|--------|-----|

| 0   | Х | 0 | Х  | 1  | High Z | 0   |

| 0   | Х | 0 | 0  | Х  | High Z | 0   |

| 0   | 0 | 0 | 1  | 0  | 0      | 0   |

| 0   | 1 | 0 | 1  | 0  | 1      | 0   |

| 1   | Х | 0 | Х  | 1  | High Z | 0   |

| 1   | Х | 0 | 0  | Х  | High Z | 0   |

| 1   | 0 | 0 | 1  | 0  | 0      | 0   |

| 1   | 1 | 0 | 1  | 0  | High Z | 0   |

| Х   | Х | 1 | Х  | Х  | Х      | 1   |

Table 8 provides the DC characteristics of the bidirectional LVD single-ended output portion of the transceiver.

Table 8 Bidirectional LVD Single-Ended Transceiver's Output Portion DC Characteristics for 3.3 V Signaling

| Symbol          | Parameter                           | Test Condition                                                                                    | Min  | Тур  | Max  | Units |

|-----------------|-------------------------------------|---------------------------------------------------------------------------------------------------|------|------|------|-------|

| V <sub>ol</sub> | Output Low Voltage                  | When I <sub>oh</sub> = 48 mA Signal TRUE State                                                    | 0.0  | _    | 0.5  | V     |

| V <sub>oh</sub> | Output High Voltage                 | When I <sub>oh</sub> = -7 mA Signal FALSE State                                                   | 2.0  | _    | 3.24 | V     |

| I <sub>oh</sub> | Output Current                      | When V <sub>oh</sub> = 2 V                                                                        | 7.5  | 19.2 | 19.5 | mA    |

| l <sub>il</sub> | Low Level Input<br>Current          | High Z State: V <sub>i</sub> = 0.5 V,<br>Power ON or OFF,<br>except during Hot Plug               | _    | _    | ±10  | μΑ    |

| l <sub>ih</sub> | High Level Input<br>Current         | High Z State: V <sub>i</sub> = 2.7 V,<br>Power ON or OFF,<br>except during Hot Plug               | _    | _    | ±10  | μΑ    |

| lih.hp          | Hot Plug High Level<br>Current Peak | High Z State: Transient duration to 10% of peak = 20 μs. This applies to physical insertion only. | _    | _    | 1.5  | mA    |

| C <sub>p</sub>  | Pin Capacitance                     | Package included                                                                                  | 2.6  | 3.0  | 3.4  | pF    |

| l <sub>l</sub>  | Output Leakage                      | High Z State, V <sub>DD</sub> = max                                                               | _    | _    | ±10  | μΑ    |

| V <sub>DD</sub> | Supply Voltage                      | V <sub>ol</sub> and High Z only                                                                   | 3.14 | 3.30 | 3.46 | V     |

| Tj              | Junction<br>Temperature             |                                                                                                   | 0    | -    | 125  | °C    |

| I <sub>lu</sub> | Latch-up Current                    | -2 V < V <sub>pin</sub> < +8 V                                                                    | _    | _    | ±100 | mA    |

| ESD             | Electrostatic<br>Discharge          | MIL-STD-883C, Method 3015.7, 100 pF at 1.5 kΩ                                                     | 2001 | _    | _    | V     |

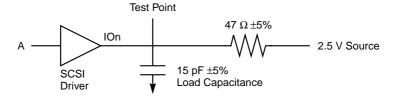

Figure 3 shows the timing test circuit for the single-ended output portion of the bidirectional transceiver.

Figure 3 SCSI Output Timing (Rise Time) Test Circuit

# Input Portion of Bidirectional LVD Transceiver, Differential Mode

Table 9 shows the truth table for the input portion of the bidirectional LVD transceiver.

Table 9 Bidirectional LVD Transceiver's Input Portion Truth Table, Differential Mode (Diff = 1)

| IOM       | IOP       | ZDIFF  | РОМ    | PIM | POP    | PIP |

|-----------|-----------|--------|--------|-----|--------|-----|

| Х         | Х         | Unspec | 1      | 0   | Unspec | Х   |

| 1         | Х         | Unspec | 0      | 1   | Unspec | Х   |

| 0         | Х         | Unspec | 1      | 1   | Unspec | Х   |

| Х         | Х         | Unspec | Unspec | Х   | 1      | 0   |

| Х         | 1         | Unspec | Unspec | Х   | 0      | 1   |

| Х         | 0         | Unspec | Unspec | Х   | 1      | 1   |

| IOP > IOM | IOP > IOM | 1      | 1      | 0   | Unspec | Х   |

| IOP > IOM | IOP > IOM | 1      | Unspec | 1   | Unspec | Х   |

| IOP > IOM | IOP > IOM | 1      | Unspec | Х   | 1      | 0   |

| IOP > IOM | IOP > IOM | 1      | Unspec | Х   | Unspec | 1   |

| IOM > IOP | IOM > IOP | 0      | 1      | 0   | Unspec | Х   |

| IOM > IOP | IOM > IOP | 0      | Unspec | 1   | Unspec | Х   |

| IOM > IOP | IOM > IOP | 0      | Unspec | Х   | 1      | 0   |

| IOM > IOP | IOM > IOP | 0      | Unspec | Х   | Unspec | 1   |

# Note:

- 1. X = don't care.

- 2. Unspec = Unspecified, an indeterminate output is acceptable.

- 3. IOM > IOP or IOM < IOP means that it is larger by the minimum sensitivity specified in the DC compliancy test table (Table 10).

Table 10 shows the DC compliancy specification for input levels to the differential transceiver.

Table 10 DC Compliancy Test Table

| V <sub>iom</sub> | V <sub>iop</sub> | V <sub>is</sub> | V <sub>icm</sub> | zidiff |

|------------------|------------------|-----------------|------------------|--------|

| 0.715            | 0.685            | 0.03            | 0.70             | 0      |

| 0.685            | 0.715            | -0.03           | 0.70             | 1      |

| 1.815            | 1.785            | 0.03            | 1.8              | 0      |

| 1.785            | 1.815            | -0.03           | 1.8              | 1      |

| 3.6              | 0                | 3.6             | 1.8              | 0      |

| 0                | 3.6              | -3.6            | 1.8              | 1      |

| 3.955            | -0.355           | 4.310           | 1.8              | 0      |

| -0.355           | 3.955            | -4.310          | 1.8              | 1      |

Table 11 lists the DC characteristics for the input portion of the bidirectional transceiver. These specifications are valid only for the commercial operating range: junction temperature = 0  $^{\circ}$ C to 125  $^{\circ}$ C,  $V_{DD} = 3.3 \ V \pm 5\%$ .

Table 11 Bidirectional Transceiver's Input DC Characteristics (Differential)

| Symbol           | Parameter                                    | Test Condition                                                | Min   | Тур  | Max   | Units |

|------------------|----------------------------------------------|---------------------------------------------------------------|-------|------|-------|-------|

| V <sub>DD</sub>  | Supply Voltage                               |                                                               | 3.14  | 3.30 | 3.46  | V     |

| C <sub>p</sub>   | Pin Capacitance                              | Package included                                              | 2.6   | 3.0  | 3.4   | pF    |

| V <sub>ist</sub> | V <sub>is</sub> Threshold to detect a 1 or 0 | Measured with 0.7 V < V <sub>icm</sub> < 1.8 V; see Figure 4. | -     | _    | 30    | mV    |

| V <sub>id</sub>  | Differential Input Voltage                   | Max values of V <sub>is</sub>                                 | -4.31 | _    | +4.31 | V     |

| Tj               | Junction Temperature                         |                                                               | 0     | _    | 125   | °C    |

| I <sub>lu</sub>  | Latch-up Current                             | -2 V < V <sub>pin</sub> < +8 V                                | -     | _    | ±100  | mA    |

| ESD              | Electrostatic Discharge                      | MIL-STD-883C,<br>Method 3015.7,<br>100 pF at 1.5 k $\Omega$   | 2001  | -    | _     | V     |

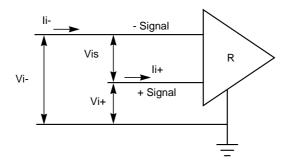

Figure 4 shows the voltage and current definitions for the receiver portion of the bidirectional transceiver.

Figure 4 Receiver Voltage and Current Definitions

Table 12 is the truth table for the output of the bidirectional LVD in Differential Mode.

Table 12 Bidirectional LVD Output Portion Truth Table, Differential Mode (Diff = 1)

| TNDIFF | ENDIFF | Α            | IOM    | IOP    |  |

|--------|--------|--------------|--------|--------|--|

| Х      | 1      | X High Z Hig |        | High Z |  |

| 0      | Х      | Х            | High Z | High Z |  |

| 1      | 0      | 0            | LOW    | HIGH   |  |

| 1      | 0      | 1            | HIGH   | LOW    |  |

1. On a SCSI bus, a HIGH is negated, and a LOW is asserted.

Table 13 lists the DC characteristics for the output portion of the bidirectional transceiver. These specifications are valid only for the commercial operating range: junction temperature = 0 °C to 125 °C,  $V_{DD} = 3.3 \ V \pm 5\%$ .

Table 13 Bidirectional Transceiver's Output DC Characteristics (Differential)

| Symbol                                | Parameter                                  | Test Condition                                                                              | Min                  | Тур  | Max                      | Units       |

|---------------------------------------|--------------------------------------------|---------------------------------------------------------------------------------------------|----------------------|------|--------------------------|-------------|

| $V_{DD}$                              | Supply Voltage                             |                                                                                             | 3.14                 | 3.30 | 3.46                     | V           |

| Tj                                    | Junction Temperature                       |                                                                                             | 0                    | _    | 125                      | °C          |

| I <sub>lu</sub>                       | Latch-up Current                           | -2 V < V <sub>pin</sub> < +8 V                                                              | _                    | _    | ±100                     | mA          |

| C <sub>p</sub>                        | Pin Capacitance                            | Package included                                                                            | 2.6                  | 3.0  | 3.4                      | pF          |

| V <sub>A</sub>   =<br>  IOP<br>- IOM  | Differential Output<br>Voltages (asserted) | V1 = 0.957 V, V2 = 0.535 V and<br>V1 = 1.949 V, V2 = 1.527 V; see<br>Figure 5 and Figure 6. | 270                  | _    | 780                      | mV          |

| Vn   =<br>  IOP<br>- IOM              | Differential Output<br>Voltage (negated)   | V1 = 0.957 V, V2 = 0.535 V and<br>V1 = 1.949 V, V2 = 1.527 V; see<br>Figure 5 and Figure 6. | 260                  | _    | 640                      | mV          |

| V <sub>A</sub>                        | Differential Output<br>Voltage (asserted)  | For all combinations of V1 and V2 above; see Figures 5 and 6.                               | 0.69<br>* Vn<br> +50 | _    | 1.45 *  <br>Vn  <br>- 65 | mV          |

| V <sub>cm</sub>                       | Offset Voltage (asserted)                  |                                                                                             | 0.7                  | _    | 1.8                      | V           |

| V <sub>cm*</sub>                      | Offset Voltage (negated)                   |                                                                                             | 0.7                  | _    | 1.8                      | V           |

| V <sub>cm</sub><br>- V <sub>cm*</sub> | Difference in State<br>Offset Voltage      |                                                                                             | _                    | _    | 50                       | mV          |

| lo-s<br>lo+s                          | Driver Short Circuit<br>Current            |                                                                                             | _                    | _    | <24                      | mA          |

| Vo-oc<br>Vo+oc                        | Driver Open Circuit<br>Voltage             |                                                                                             | 0                    | _    | 3.6                      | V           |

| T <sub>r</sub> / T <sub>f</sub>       | Differential Driver Rise and Fall Times    | V1 = 1.375 V, V2 = 0.807 V and<br>V1 = 1.693 V, V2 = 1.125 V                                | 1                    | _    | _                        | ns          |

| V <sub>cm</sub><br>(pk-pk)            | Dynamic Output Signal<br>Balance           |                                                                                             | _                    | _    | 120                      | mV<br>pk-pk |

| i-  <br>  i+                          | Driver /Receiver Output / Input Currents   | V <sub>DD</sub> = 0 V or V <sub>DD</sub> = 3.15 - 3.45 V                                    | _                    | _    | 20                       | μА          |

| ESD                                   | Electrostatic Discharge                    | MIL-STD-883C, Method 3015.7, 100 pF at 1.5 kΩ                                               | 2001                 | _    | _                        | V           |

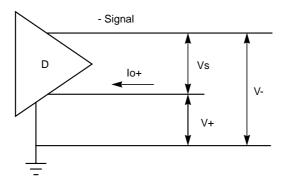

Figure 5 shows the voltage and current definitions for the driver portion of the bidirectional transceiver.

Figure 5 Driver Voltage and Current Definitions

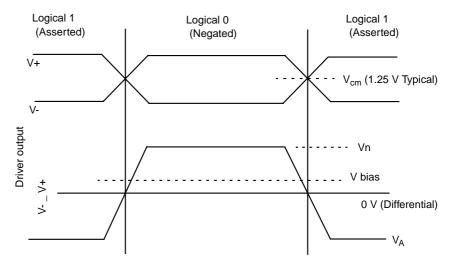

Figure 6 shows the bidirectional transceiver's signalling sense.

Figure 6 LVD SCSI Signalling Sense

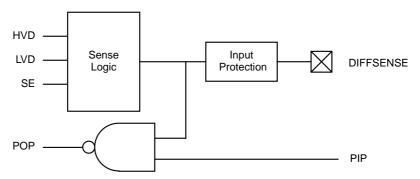

# **DIFFSENSE** Receiver

Name: DIFFSENS

**Description:** The LVD SCSI DIFFSENSE Receiver detects the

voltage level on the SCSI bus DIFFSENSE line and informs the device of the transmission mode used by the bus (see Figure 7). It is capable of detecting single-

ended, LVD SCSI, and HV differential modes.

Coding Syntax: Z(HVD, LVD, SE) = DIFFSENS(IDDTN, DSIN)

**Silicon Dimensions:** 96.6 μm x 81.2 μm

Figure 7 LVD SCSI DIFFSENSE Receiver Logic Diagram

Table 14 provides the operating characteristics for the DIFFSENSE receiver.

Table 14 DIFFSENSE Operating Truth Table

| DIFFSENSE<br>Input Voltage | PIP | SE | HVD | LVD | POP       |

|----------------------------|-----|----|-----|-----|-----------|

| -0.5 V to 0.6 V            | Х   | 1  | 0   | 0   | 1         |

| 0.7 V to 1.9 V             | Х   | 0  | 0   | 1   | Undefined |

| 2.2 V to 5.5 V             | 0   | 0  | 1   | 0   | 1         |

| 2.2 V to 5.5 V             | 1   | 0  | 1   | 0   | 0         |

Table 15 DIFFSENSE DC Characteristics

| Symbol          | Parameter               | Min  | Тур  | Max  | Units | Test Condition                                      |

|-----------------|-------------------------|------|------|------|-------|-----------------------------------------------------|

| V <sub>DD</sub> | Supply Voltage          | 3.14 | 3.30 | 3.46 | V     |                                                     |

| C <sub>p</sub>  | Input Capacitance       | _    | 4.5  | _    | pF    | Package Included                                    |

| T <sub>j</sub>  | Junction Temperature    | 0    | _    | 125  | °C    |                                                     |

| I <sub>lu</sub> | Latch-up Current        | _    | _    | ±100 | mA    | -2 V < V <sub>pin</sub> < + 8 V                     |

| ESD             | Electrostatic Discharge | 2001 | _    | _    | V     | MIL-STD-883C,<br>Method 3015.7,<br>100 pF at 1.5 kΩ |

# **Power On Reset Cell**

Name: SCSIPOR

**Description:** Provides power-up timing to the output and bidirectional

cells. This cell must be used; only one is needed for all

I/O transceivers.

**Coding Syntax:** U(HTPLG) = SCSIPOR(); for 3.3  $V_{DD}$

Silicon Dimensions: 226.8 µm high, 144.2 µm wide

Figure 8 shows the schematic symbol for the power on reset cell.

Figure 8 Power On Reset Cell

# **Notes**

# **Notes**

LSI Logic Corporation Corporate Headquarters Tel: 408.433.8000 Fax: 408.433.8989

#### NORTH AMERICA

#### California

Irvine

♦ Tel: 714.553.5600 Fax: 714.474.8101

> San Diego Tel: 619.613.8300 Fax: 619.613.8350

> Silicon Valley Sales Office Tel: 408.433.8000 Fax: 408.954.3353 Design Center

♦ Tel: 408.433.8000 Fax: 408.433.7695

## Colorado

Boulder Tel: 303.447.3800 Fax: 303.541.0641

Florida Boca Raton Tel: 561.989.3236 Fax: 561.989.3237

## Illinois Schaumburg

♦ Tel: 847.995.1600 Fax: 847.995.1622

#### Kentucky Bowling Green Tel: 502.793.0010

Fax: 502.793.0010 Maryland

Bethesda Tel: 301.897.5800 Fax: 301.897.8389

#### Massachusetts Waltham

♦ Tel: 617.890.0180 Fax: 617.890.6158

# Minnesota

Minneapolis ◆ Tel: 612.921.8300 Fax: 612.921.8399

#### New Jersey Edison

◆ Tel: 732.549.4500 Fax: 732.549.4802

#### New York New York

Tel: 716.223.8820 Fax: 716.223.8822

# **North Carolina**

Raleigh Tel: 919.783.8833 Fax: 919.783.8909

# Oregon

Beaverton Tel: 503.645.0589 Fax: 503.645.6612

#### Texas Austin

Tel: 512.388.7294 Fax: 512.388.4171

#### Dallas

◆ Tel: 972.788.2966 Fax: 972.233.9234

# Houston

Tel: 281.379.7800 Fax: 281.379.7818

## Washington

Issaquah Tel: 425.837.1733 Fax: 425.837.1734

#### Canada Ontario Ottawa

♦ Tel: 613.592.1263 Fax: 613.592.3253

#### Toronto

♦ Tel: 416.620.7400 Fax: 416.620.5005

#### Quebec Montreal

♦ Tel: 514.694.2417 Fax: 514.694.2699

#### INTERNATIONAL

## Australia Reptechnic Pty Ltd

New South Wales

Tel: 612.9953.9844

Fax: 612.9953.9683

## Denmark LSI Logic Development Centre

Ballerup Tel: 45.44.86.55.55 Fax: 45.44.86.55.56

# France LSI Logic S.A. Immeuble Europa

♦ Tel: 33.1.34.63.13.13 Fax: 33.1.34.63.13.19

#### Germany LSI Logic GmbH Munich

Tel: 49.89.4.58.33.0 Fax: 49.89.4.58.33.108

## Stuttgart

Tel: 49.711.13.96.90 Fax: 49.711.86.61.428

# Hong Kong AVT Industrial Ltd

Hong Kong Tel: 852.2428.0008 Fax: 852.2401.2105

#### India LogiCAD India Private Ltd

Bangalore Tel: 91.80.526.2500 Fax: 91.80.338.6591

## Israel LSI Logic

Ramat Hasharon

◆ Tel: 972.3.5.403741

Fax: 972.3.5.403747

Netanya

◆ Tel: 972.9.657190 Fax: 972.9.657194

#### Italy LSI Logic S.P.A.

Milano

♦ Tel: 39.39.687371

Fax: 39.39.6057867

## Japan LSI Logic K.K.

Tokyo

◆ Tel: 81.3.5463.7821 Fax: 81.3.5463.7820

#### Osaka

◆ Tel: 81.6.947.5281 Fax: 81.6.947.5287

#### Korea LSI Logic Corporation of Korea Ltd.

Seoul Tel: 82.2.528.3400 Fax: 82.2.528.2250

## Singapore LSI Logic Pte Ltd

Singapore ◆ Tel: 65.334.9061 Fax: 65.334.4749

#### Spain LSI Logic S.A. Madrid

♦ Tel: 34.1.556.07.09 Fax: 34.1.556.75.65

#### Sweden LSI Logic AB Stockholm

◆ Tel: 46.8.444.15.00 Fax: 46.8.750.66.47

# Switzerland LSI Logic Sulzer AG

Brugg/Biel Tel: 41.32.536363 Fax: 41.32.536367

#### Taiwan LSI Logic Asia-Pacific Taipei

◆ Tel: 886.2.718.7828 Fax: 886.2.718.8869

# Cheng Fong Technology Corporation

Tel: 886.2.910.1180 Fax: 886.2.910.1175

#### Jeilin Technology Corporation, Ltd. Tel: 886.2.248.4828 Fax: 886.2.242.4397

#### Lumax International Corporation, Ltd Tel: 886.2.788.3656 Fax: 886.2.788.3568

# Macro-Vision Technology Inc.

Tel: 886.2.698.3350 Fax: 886.2.698.3348

## United Kingdom LSI Logic Europe Ltd Bracknell

♦ Tel: 44.1344.426544 Fax: 44.1344.481039

♦ Sales Offices with Design Resource Centers

To receive product literature, call us at 1-800-574-4286 (U.S. and Canada); +32.11.300.531 (Europe); 408.433.7700 (outside U.S., Canada, and Europe) and ask for Department JDS; or visit us at http://www.lsilogic.com

# ISO 9000 Certified

This document is preliminary. As such, it contains data derived from functional simulations and performance estimates. LSI Logic has not verified the functional descriptions or electrical and mechanical specifications using production parts.

LSI Logic logo design is a registered trademark and G10 is a trademark of LSI Logic Corporation. All other brand and product names may be trademarks of their respective companies. LSI Logic Corporation reserves the right to make changes to any products and services herein at any time without notice. LSI Logic does not assume any responsibility or liability arising out of the application or use of any product or service described herein, except as expressly agreed to in writing by LSI Logic; nor does the purchase, lease, or use of a product or service from LSI Logic convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual property rights of LSI Logic or of third parties.

Printed in USA Order No. B15058.A Doc. No. DB08-000079-01